Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |  |

|----------------------------|----------------------------------------------------------------------|--|

| Product Status             | Active                                                               |  |

| Core Processor             | STM8                                                                 |  |

| Core Size                  | 8-Bit                                                                |  |

| Speed                      | 16MHz                                                                |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                              |  |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                       |  |

| Number of I/O              | 30                                                                   |  |

| Program Memory Size        | 16KB (16K x 8)                                                       |  |

| Program Memory Type        | FLASH                                                                |  |

| EEPROM Size                | 1K x 8                                                               |  |

| RAM Size                   | 2K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |  |

| Data Converters            | A/D 22x12b; D/A 1x12b                                                |  |

| Oscillator Type            | Internal                                                             |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |  |

| Mounting Type              | Surface Mount                                                        |  |

| Package / Case             | 32-LQFP                                                              |  |

| Supplier Device Package    | 32-LQFP (7x7)                                                        |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151k4t3 |  |

# **Contents**

| 1 | Intro | uction                                                | 9  |

|---|-------|-------------------------------------------------------|----|

| 2 | Desc  | iption                                                | 11 |

|   | 2.1   | Device overview                                       | 12 |

|   | 2.2   | Ultra-low-power continuum                             | 13 |

| 3 | Func  | ional overview                                        | 14 |

|   | 3.1   | Low-power modes                                       | 15 |

|   | 3.2   | Central processing unit STM8                          | 16 |

|   |       | 3.2.1 Advanced STM8 Core                              | 16 |

|   |       | 3.2.2 Interrupt controller                            | 16 |

|   | 3.3   | Reset and supply management                           | 17 |

|   |       | 3.3.1 Power supply scheme                             | 17 |

|   |       | 3.3.2 Power supply supervisor                         | 17 |

|   |       | 3.3.3 Voltage regulator                               | 17 |

|   | 3.4   | Clock management                                      | 18 |

|   | 3.5   | Low power real-time clock                             | 19 |

|   | 3.6   | LCD (Liquid crystal display)                          | 20 |

|   | 3.7   | Memories                                              | 20 |

|   | 3.8   | DMA 2                                                 | 20 |

|   | 3.9   | Analog-to-digital converter                           | 20 |

|   | 3.10  | Digital-to-analog converter (DAC)                     | 21 |

|   | 3.11  | Ultra-low-power comparators                           | 21 |

|   | 3.12  | System configuration controller and routing interface | 21 |

|   | 3.13  | Touch sensing                                         | 21 |

|   | 3.14  | Timers                                                | 22 |

|   |       | 3.14.1 TIM1 - 16-bit advanced control timer           | 22 |

|   |       | 3.14.2 16-bit general purpose timers                  | 23 |

|   |       | 3.14.3 8-bit basic timer                              | 23 |

|   | 3.15  | Watchdog timers                                       | 23 |

|   |       | 3.15.1 Window watchdog timer                          | 23 |

|   |       | 3.15.2 Independent watchdog timer                     | 23 |

| 3.17 Communication interfaces 3.17.1 SPI 3.17.2 PC 3.17.3 USART 3.18 Infrared (IR) interface 3.19 Development support  4 Pinout and pin description 4.1 System configuration options  5 Memory and register map 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.5 Memory characteristics           |                                 |         |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------|---|

| 3.17.2 PC 3.17.3 USART 3.18 Infrared (IR) interface 3.19 Development support  4 Pinout and pin description 4.1 System configuration options  5 Memory and register map 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings 9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics              |                                 |         |   |

| 3.17.3 USART  3.18 Infrared (IR) interface 3.19 Development support  4 Pinout and pin description 4.1 System configuration options  5 Memory and register map 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics |                                 |         |   |

| 3.18 Infrared (IR) interface 3.19 Development support  4 Pinout and pin description 4.1 System configuration options  5 Memory and register map 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics               |                                 |         |   |

| 3.19 Development support  4 Pinout and pin description 4.1 System configuration options  5 Memory and register map 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                 | 25                              | 3.18    |   |

| 4 Pinout and pin description 4.1 System configuration options  5 Memory and register map 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                           |                                 |         |   |

| 4.1 System configuration options  Memory and register map  5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters  9.1 Parameter conditions  9.1.1 Minimum and maximum values  9.1.2 Typical values  9.1.3 Typical curves  9.1.4 Loading capacitor  9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.2 Absolute maximum ratings  9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                | 00                              | 3.19    |   |

| 5 Memory and register map 5.1 Memory mapping 5.2 Register map 6 Interrupt vector mapping 7 Option bytes 8 Unique ID 9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage 9.2 Absolute maximum ratings 9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                |                                 | Pinout  | 4 |

| 5.1 Memory mapping 5.2 Register map  6 Interrupt vector mapping  7 Option bytes  8 Unique ID  9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                    |                                 | 4.1     |   |

| 5.2 Register map  Interrupt vector mapping  Option bytes  Unique ID  Electrical parameters  9.1 Parameter conditions  9.1.1 Minimum and maximum values  9.1.2 Typical values  9.1.3 Typical curves  9.1.4 Loading capacitor  9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                    |                                 | Memo    | 5 |

| 6 Interrupt vector mapping 7 Option bytes 8 Unique ID 9 Electrical parameters 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                            |                                 | 5.1     |   |

| 7 Option bytes  8 Unique ID  9 Electrical parameters  9.1 Parameter conditions  9.1.1 Minimum and maximum values  9.1.2 Typical values  9.1.3 Typical curves  9.1.4 Loading capacitor  9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                                                          |                                 | 5.2     |   |

| 8 Unique ID  9 Electrical parameters  9.1 Parameter conditions  9.1.1 Minimum and maximum values  9.1.2 Typical values  9.1.3 Typical curves  9.1.4 Loading capacitor  9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                                                                          | 57                              | Interru | 6 |

| 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                          | 59                              | Option  | 7 |

| 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                          |                                 | Uniqu   | 8 |

| 9.1 Parameter conditions 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                          | 63                              | Flectri | 9 |

| 9.1.1 Minimum and maximum values 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings 9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                    |                                 |         |   |

| 9.1.2 Typical values 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings 9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                     |                                 |         |   |

| 9.1.3 Typical curves 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions 9.3.1 General operating conditions 9.3.2 Embedded reset and power control block characteristics 9.3.3 Supply current characteristics 9.3.4 Clock and timing characteristics 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                         |                                 |         |   |

| 9.1.4 Loading capacitor 9.1.5 Pin input voltage  9.2 Absolute maximum ratings  9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |         |   |

| 9.2 Absolute maximum ratings  9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |         |   |

| 9.3 Operating conditions  9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |         |   |

| 9.3.1 General operating conditions  9.3.2 Embedded reset and power control block characteristics  9.3.3 Supply current characteristics  9.3.4 Clock and timing characteristics  9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 | 9.2     |   |

| 9.3.2 Embedded reset and power control block characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 | 9.3     |   |

| 9.3.3 Supply current characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ıs                              |         |   |

| 9.3.4 Clock and timing characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | control block characteristics67 |         |   |

| 9.3.5 Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | cs68                            |         |   |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | stics82                         |         |   |

| 0.2.C. I/O support injection about training                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                              |         |   |

| 9.3.6 I/O current injection characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | teristics89                     |         |   |

| 9.3.7 I/O port pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89                              |         |   |

### 1 Introduction

This document describes the features, pinout, mechanical data and ordering information of the medium-density STM8L151x4/6 and STM8L152x4/6 devices (STM8L151Cx/Kx/Gx, STM8L152Cx/Kx microcontrollers with a 16-Kbyte or 32-Kbyte Flash memory density). These devices are referred to as medium-density devices in the STM8L15x and STM8L16x reference manual (RM0031) and in the STM8L Flash programming manual (PM0054).

For more details on the whole STMicroelectronics ultra-low-power family please refer to Section 2.2: Ultra-low-power continuum on page 13.

For information on the debug module and SWIM (single wire interface module), refer to the STM8 SWIM communication protocol and debug module user manual (UM0470). For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

The medium-density devices provide the following benefits:

- Integrated system

- Up to 32 Kbyte of medium-density embedded Flash program memory

- 1 Kbyte of data EEPROM

- Internal high speed and low-power low speed RC

- Embedded reset

- Ultra-low power consumption

- 195  $\mu$ A/MHz + 440  $\mu$ A (consumption)

- 0.9 μA with LSI in Active-halt mode

- Clock gated system and optimized power management

- Capability to execute from RAM for Low power wait mode and Low power run mode

- Advanced features

- Up to 16 MIPS at 16 MHz CPU clock frequency

- Direct memory access (DMA) for memory-to-memory or peripheral-to-memory access

- Short development cycles

- Application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals

- Wide choice of development tools

All devices offer 12-bit ADC, DAC, two comparators, Real-time clock three 16-bit timers, one 8-bit timer as well as standard communication interface such as SPI, I2C and USART. A 4x28-segment LCD is available on the medium-density STM8L152xx line. *Table 2: Medium-density STM8L151x4/6 and STM8L152x4/6 low-power device features and peripheral counts* and *Section 3: Functional overview* give an overview of the complete range of peripherals proposed in this family.

Figure 1 on page 14 shows the general block diagram of the device family.

Note: ADC1 can be served by DMA1.

### 3.10 Digital-to-analog converter (DAC)

- 12-bit DAC with output buffer

- Synchronized update capability using TIM4

- DMA capability

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub> for better resolution

Note: DAC can be served by DMA1.

### 3.11 Ultra-low-power comparators

The medium-density STM8L151x4/6 and STM8L152x4/6 embed two comparators (COMP1 and COMP2) sharing the same current bias and voltage reference. The voltage reference can be internal or external (coming from an I/O).

- One comparator with fixed threshold (COMP1).

- One comparator rail to rail with fast or slow mode (COMP2). The threshold can be one

of the following:

- DAC output

- External I/O

- Internal reference voltage or internal reference voltage sub multiple (1/4, 1/2, 3/4)

The two comparators can be used together to offer a window function. They can wake up from Halt mode.

## 3.12 System configuration controller and routing interface

The system configuration controller provides the capability to remap some alternate functions on different I/O ports. TIM4 and ADC1 DMA channels can also be remapped.

The highly flexible routing interface allows application software to control the routing of different I/Os to the TIM1 timer input captures. It also controls the routing of internal analog signals to ADC1, COMP1, COMP2, DAC and the internal reference voltage V<sub>REFINT</sub>. It also provides a set of registers for efficiently managing the charge transfer acquisition sequence (Section 3.13: Touch sensing).

## 3.13 Touch sensing

Medium-density STM8L151x4/6 and STM8L152x4/6 devices provide a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect finger presence near an electrode which is protected from direct touch by a dielectric (example, glass, plastic). The capacitive variation introduced by a finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the electrode capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. In medium-density STM8L151x4/6

#### 3.14.2 16-bit general purpose timers

- 16-bit autoreload (AR) up/down-counter

- 7-bit prescaler adjustable to fixed power of 2 ratios (1...128)

- 2 individually configurable capture/compare channels

- PWM mode

- Interrupt capability on various events (capture, compare, overflow, break, trigger)

- Synchronization with other timers or external signals (external clock, reset, trigger and enable)

#### 3.14.3 8-bit basic timer

The 8-bit timer consists of an 8-bit up auto-reload counter driven by a programmable prescaler. It can be used for timebase generation with interrupt generation on timer overflow or for DAC trigger generation.

### 3.15 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

### 3.15.1 Window watchdog timer

The window watchdog (WWDG) is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

### 3.15.2 Independent watchdog timer

The independent watchdog peripheral (IWDG) can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the internal LSI RC clock source, and thus stays active even in case of a CPU clock failure.

### 3.16 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

Table 9. General hardware register map (continued)

| Address   | Block | Register label | Register name                            | Reset<br>status |

|-----------|-------|----------------|------------------------------------------|-----------------|

| 0x00 5430 |       |                | Reserved area (1 byte)                   | 0x00            |

| 0x00 5431 |       | RI_ICR1        | Timer input capture routing register 1   | 0x00            |

| 0x00 5432 |       | RI_ICR2        | Timer input capture routing register 2   | 0x00            |

| 0x00 5433 |       | RI_IOIR1       | I/O input register 1                     | undefined       |

| 0x00 5434 |       | RI_IOIR2       | I/O input register 2                     | undefined       |

| 0x00 5435 |       | RI_IOIR3       | I/O input register 3                     | undefined       |

| 0x00 5436 |       | RI_IOCMR1      | I/O control mode register 1              | 0x00            |

| 0x00 5437 | RI    | RI_IOCMR2      | I/O control mode register 2              | 0x00            |

| 0x00 5438 | KI    | RI_IOCMR3      | I/O control mode register 3              | 0x00            |

| 0x00 5439 |       | RI_IOSR1       | I/O switch register 1                    | 0x00            |

| 0x00 543A |       | RI_IOSR2       | I/O switch register 2                    | 0x00            |

| 0x00 543B |       | RI_IOSR3       | I/O switch register 3                    | 0x00            |

| 0x00 543C |       | RI_IOGCR       | I/O group control register               | 0x3F            |

| 0x00 543D |       | RI_ASCR1       | Analog switch register 1                 | 0x00            |

| 0x00 543E |       | RI_ASCR2       | Analog switch register 2                 | 0x00            |

| 0x00 543F |       | RI_RCR         | Resistor control register 1              | 0x00            |

| 0x00 5440 |       | COMP_CSR1      | Comparator control and status register 1 | 0x00            |

| 0x00 5441 |       | COMP_CSR2      | Comparator control and status register 2 | 0x00            |

| 0x00 5442 | COMP  | COMP_CSR3      | Comparator control and status register 3 | 0x00            |

| 0x00 5443 |       | COMP_CSR4      | Comparator control and status register 4 | 0x00            |

| 0x00 5444 |       | COMP_CSR5      | Comparator control and status register 5 | 0x00            |

<sup>1.</sup> These registers are not impacted by a system reset. They are reset at power-on.

# 8 Unique ID

STM8 devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while

using and combining this unique ID with software cryptographic primitives and

protocols before programming the internal memory.

- To activate secure boot processes

Table 14. Unique ID registers (96 bits)

| Adduses | Content          |             |             |   | Uniq | ue ID bits | 3 |   |   |

|---------|------------------|-------------|-------------|---|------|------------|---|---|---|

| Address | description      | 7           | 6           | 5 | 4    | 3          | 2 | 1 | 0 |

| 0x4926  | X co-ordinate on |             |             |   | U_   | ID[7:0]    |   |   |   |

| 0x4927  | the wafer        |             |             |   | U_I  | ID[15:8]   |   |   |   |

| 0x4928  | Y co-ordinate on |             |             |   | U_II | D[23:16]   |   |   |   |

| 0x4929  | the wafer        | U_ID[31:24] |             |   |      |            |   |   |   |

| 0x492A  | Wafer number     |             |             |   | U_II | D[39:32]   |   |   |   |

| 0x492B  |                  |             |             |   | U_II | D[47:40]   |   |   |   |

| 0x492C  |                  |             |             |   | U_II | D[55:48]   |   |   |   |

| 0x492D  |                  |             |             |   | U_II | D[63:56]   |   |   |   |

| 0x492E  | Lot number       | U_ID[71:64] |             |   |      |            |   |   |   |

| 0x492F  |                  | U_ID[79:72] |             |   |      |            |   |   |   |

| 0x4930  |                  | U_ID[87:80] |             |   |      |            |   |   |   |

| 0x4931  |                  |             | U_ID[95:88] |   |      |            |   |   |   |

62/142 DocID15962 Rev 15

## 9.3 Operating conditions

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}$ .

### 9.3.1 General operating conditions

Table 18. General operating conditions

| Symbol                             | Parameter                                                                                                     | Co                                                         | onditions                                   | Min.                | Max.               | Unit |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------|---------------------|--------------------|------|

| f <sub>SYSCLK</sub> <sup>(1)</sup> | System clock frequency                                                                                        | 1.65 V ≤V <sub>DD</sub> < 3.6 V                            |                                             | 0                   | 16                 | MHz  |

| V <sub>DD</sub>                    | Standard operating voltage                                                                                    | -                                                          |                                             | 1.65 <sup>(2)</sup> | 3.6                | V    |

| V                                  | Analog operating                                                                                              | ADC and DAC not used                                       | Must be at the same                         | 1.65 <sup>(2)</sup> | 3.6                | V    |

| $V_{DDA}$                          | voltage                                                                                                       | ADC or DAC used                                            | potential as V <sub>DD</sub>                | 1.8                 | 3.6                | V    |

|                                    |                                                                                                               | L                                                          | _QFP48                                      | -                   | 288                |      |

| _ (3)                              |                                                                                                               | UF                                                         | FQFPN48                                     | -                   | 169                |      |

|                                    | Power dissipation at                                                                                          | L                                                          | _QFP32                                      | -                   | 288                |      |

|                                    | T <sub>A</sub> = 85 °C for suffix 6 devices                                                                   | UFQFPN32                                                   |                                             | -                   | 169                |      |

|                                    |                                                                                                               | UFQFPN28                                                   |                                             | -                   | 169                |      |

|                                    |                                                                                                               | W                                                          | /LCSP28                                     | -                   | 286                | mW   |

| P <sub>D</sub> <sup>(3)</sup>      |                                                                                                               | LQFP48                                                     |                                             | -                   | 77                 | HIVV |

|                                    | Power dissipation at T <sub>A</sub> = 125 °C for suffix 3 devices and at T <sub>A</sub> = 105 °C for suffix 7 | sipation at UFQFPN48                                       |                                             | -                   | 156                |      |

|                                    |                                                                                                               | LQFP32                                                     |                                             | -                   | 85                 |      |

|                                    |                                                                                                               | UFQFPN32                                                   |                                             | -                   | 131                |      |

|                                    | devices                                                                                                       | UFQFPN28                                                   |                                             | -                   | 42                 |      |

|                                    |                                                                                                               | WLCSP28                                                    |                                             | -                   | 71                 |      |

|                                    |                                                                                                               | 1.65 V ≤V <sub>DD</sub> <                                  | 3.6 V (6 suffix version)                    | -40                 | 85                 |      |

| $T_A$                              | Temperature range                                                                                             | 1.65 V ≤V <sub>DD</sub> <                                  | 3.6 V (7 suffix version)                    | -40                 | 105                | °C   |

|                                    |                                                                                                               | 1.65 V ≤V <sub>DD</sub> < 3.6 V (3 suffix version)         |                                             | -40                 | 125                |      |

| ТЈ                                 |                                                                                                               | -40 °C ≤T <sub>A</sub> < 85 °C<br>(6 suffix version)       |                                             | -40                 | 105 <sup>(4)</sup> |      |

|                                    | Junction temperature range                                                                                    | -40 °C $\leq$ T <sub>A</sub> $<$ 105 °C (7 suffix version) |                                             | -40                 | 110 <sup>(4)</sup> | °C   |

|                                    |                                                                                                               |                                                            | ≤ T <sub>A</sub> < 125 °C<br>iffix version) | -40                 | 130                |      |

<sup>1.</sup>  $f_{SYSCLK} = f_{CPU}$

47/

66/142 DocID15962 Rev 15

<sup>2. 1.8</sup> V at power-up, 1.65 V at power-down if BOR is disabled

<sup>3.</sup> To calculate  $P_{Dmax}(T_A)$ , use the formula  $P_{Dmax}=(T_{Jmax}-T_A)/\Theta_{JA}$  with  $T_{Jmax}$  in this table and  $\Theta_{JA}$  in "Thermal characteristics" table.

<sup>4.</sup>  $T_{Jmax}$  is given by the test limit. Above this value the product behavior is not guaranteed.

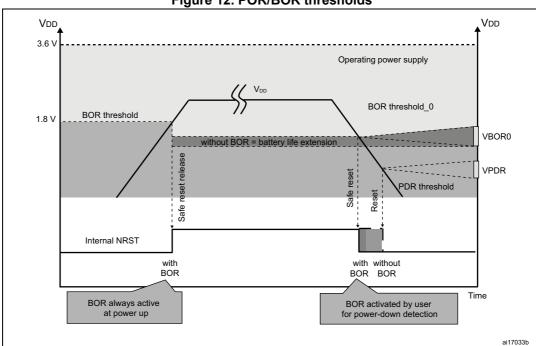

## 9.3.2 Embedded reset and power control block characteristics

Table 19. Embedded reset and power control block characteristics

| Symbol            | Parameter                      | Conditions                                         | Min                 | Тур  | Max              | Unit   |

|-------------------|--------------------------------|----------------------------------------------------|---------------------|------|------------------|--------|

|                   | V <sub>DD</sub> rise time rate | BOR detector enabled                               | 0 <sup>(1)</sup>    | -    | ∞ <sup>(1)</sup> | .ue.\/ |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate | BOR detector enabled                               | 20 <sup>(1)</sup>   | -    | ∞ <sup>(1)</sup> | μs/V   |

| t                 | Reset release delay            | V <sub>DD</sub> rising<br>BOR detector<br>enabled  | -                   | 3    | -                | ms     |

| t <sub>TEMP</sub> | Treset release delay           | V <sub>DD</sub> rising<br>BOR detector<br>disabled | -                   | 1    | -                | 1115   |

| $V_{PDR}$         | Power-down reset threshold     | Falling edge                                       | 1.30 <sup>(2)</sup> | 1.50 | 1.65             | V      |

| V                 | Brown-out reset threshold 0    | Falling edge                                       | 1.67                | 1.70 | 1.74             |        |

| $V_{BOR0}$        | (BOR_TH[2:0]=000)              | Rising edge                                        | 1.69                | 1.75 | 1.80             |        |

| V                 | Brown-out reset threshold 1    | Falling edge                                       | 1.87                | 1.93 | 1.97             |        |

| $V_{BOR1}$        | (BOR_TH[2:0]=001)              | Rising edge                                        | 1.96                | 2.04 | 2.07             |        |

| V                 | Brown-out reset threshold 2    | Falling edge                                       | 2.22                | 2.3  | 2.35             | V      |

| $V_{BOR2}$        | (BOR_TH[2:0]=010)              | Rising edge                                        | 2.31                | 2.41 | 2.44             | V      |

| \/                | Brown-out reset threshold 3    | Falling edge                                       | 2.45                | 2.55 | 2.60             |        |

| $V_{BOR3}$        | (BOR_TH[2:0]=011)              | Rising edge                                        | 2.54                | 2.66 | 2.7              |        |

| V                 | Brown-out reset threshold 4    | Falling edge                                       | 2.68                | 2.80 | 2.85             |        |

| $V_{BOR4}$        | (BOR_TH[2:0]=100)              | Rising edge                                        | 2.78                | 2.90 | 2.95             |        |

| V                 | PVD threshold 0                | Falling edge                                       | 1.80                | 1.84 | 1.88             |        |

| $V_{PVD0}$        | F VD tillesiloid 0             | Rising edge                                        | 1.88                | 1.94 | 1.99             |        |

| V                 | PVD threshold 1                | Falling edge                                       | 1.98                | 2.04 | 2.09             |        |

| V <sub>PVD1</sub> | F VD tillesilota i             | Rising edge                                        | 2.08                | 2.14 | 2.18             |        |

| V                 | PVD threshold 2                | Falling edge                                       | 2.2                 | 2.24 | 2.28             |        |

| V <sub>PVD2</sub> | F VD tillesiloid 2             | Rising edge                                        | 2.28                | 2.34 | 2.38             |        |

| V                 | DVD throshold 3                | Falling edge                                       | 2.39                | 2.44 | 2.48             | V      |

| V <sub>PVD3</sub> | PVD threshold 3                | Rising edge                                        | 2.47                | 2.54 | 2.58             | V      |

| V                 | PVD threshold 4                | Falling edge                                       | 2.57                | 2.64 | 2.69             |        |

| V <sub>PVD4</sub> | า งก แแรงแดน 4                 | Rising edge                                        | 2.68                | 2.74 | 2.79             |        |

| \/-               | DVD threshold 5                | Falling edge                                       | 2.77                | 2.83 | 2.88             |        |

| V <sub>PVD5</sub> | PVD threshold 5                | Rising edge                                        | 2.87                | 2.94 | 2.99             |        |

| V                 | PVD threshold 6                | Falling edge                                       | 2.97                | 3.05 | 3.09             |        |

| $V_{PVD6}$        | L งก แแ <i>ค</i> ยแดเต อ       | Rising edge                                        | 3.08                | 3.15 | 3.20             |        |

- 1. Data guaranteed by design.

- 2. Data based on characterization results.

Figure 12. POR/BOR thresholds

### 9.3.3 Supply current characteristics

#### **Total current consumption**

The MCU is placed under the following conditions:

- I All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- I All peripherals are disabled except if explicitly mentioned.

In the following table, data is based on characterization results, unless otherwise specified. Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

Table 20. Total current consumption in Run mode

|                                       | Para                |                                     |                                                      | arrent consum                       | _     |       |                      | Max                  |                       |      |

|---------------------------------------|---------------------|-------------------------------------|------------------------------------------------------|-------------------------------------|-------|-------|----------------------|----------------------|-----------------------|------|

| Symbol                                | meter               |                                     | Conditions <sup>(</sup>                              | 1)                                  | Тур   | 55 °C | 85 °C <sup>(2)</sup> | 105°C <sup>(3)</sup> | 125 °C <sup>(4)</sup> | Unit |

|                                       |                     |                                     |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.39  | 0.47  | 0.49                 | 0.52                 | 0.55                  |      |

|                                       |                     |                                     |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.48  | 0.56  | 0.58                 | 0.61                 | 0.65                  |      |

|                                       |                     |                                     | HSI RC osc.<br>(16 MHz) <sup>(6)</sup>               | f <sub>CPU</sub> = 4 MHz            | 0.75  | 0.84  | 0.86                 | 0.91                 | 0.99                  |      |

|                                       |                     |                                     | (10 1/11/12)                                         | f <sub>CPU</sub> = 8 MHz            | 1.10  | 1.20  | 1.25                 | 1.31                 | 1.40                  |      |

| I <sub>DD(RUN)</sub> currer<br>in run |                     | All peripherals                     |                                                      | f <sub>CPU</sub> = 16 MHz           | 1.85  | 1.93  | 2.12 <sup>(8)</sup>  | 2.29 <sup>(8)</sup>  | 2.36 <sup>(8)</sup>   |      |

|                                       | Supply              | OFF,                                |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.05  | 0.06  | 0.09                 | 0.11                 | 0.12                  |      |

|                                       | current             | code<br>executed                    | HSE external                                         | f <sub>CPU</sub> = 1 MHz            | 0.18  | 0.19  | 0.20                 | 0.22                 | 0.23                  | mA   |

|                                       | mode <sup>(5)</sup> | from RAM,<br>V <sub>DD</sub> from   | clock                                                | f <sub>CPU</sub> = 4 MHz            | 0.55  | 0.62  | 0.64                 | 0.71                 | 0.77                  |      |

|                                       |                     | 1.65 V to                           | (f <sub>CPU</sub> =f <sub>HSE</sub> ) <sup>(7)</sup> | f <sub>CPU</sub> = 8 MHz            | 0.99  | 1.20  | 1.21                 | 1.22                 | 1.24                  |      |

|                                       |                     | 3.6 V                               |                                                      | f <sub>CPU</sub> = 16 MHz           | 1.90  | 2.22  | 2.23 <sup>(8)</sup>  | 2.24 <sup>(8)</sup>  | 2.28 <sup>(8)</sup>   |      |

|                                       |                     |                                     | LSI RC osc.<br>(typ. 38 kHz)                         | f <sub>CPU</sub> = f <sub>LSI</sub> | 0.040 | 0.045 | 0.046                | 0.048                | 0.050                 |      |

|                                       |                     |                                     | LSE external clock (32.768 kHz)                      | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.035 | 0.040 | 0.048 <sup>(8)</sup> | 0.050                | 0.062                 |      |

|                                       |                     |                                     |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.43  | 0.55  | 0.56                 | 0.58                 | 0.62                  |      |

|                                       |                     |                                     |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.60  | 0.77  | 0.80                 | 0.82                 | 0.87                  |      |

|                                       |                     |                                     | HSI RC<br>osc. <sup>(9)</sup>                        | f <sub>CPU</sub> = 4 MHz            | 1.11  | 1.34  | 1.37                 | 1.39                 | 1.43                  |      |

|                                       |                     |                                     |                                                      | f <sub>CPU</sub> = 8 MHz            | 1.90  | 2.20  | 2.23                 | 2.31                 | 2.40                  |      |

|                                       |                     | All                                 |                                                      | f <sub>CPU</sub> = 16 MHz           | 3.8   | 4.60  | 4.75                 | 4.87                 | 4.88                  |      |

|                                       | Supply              | peripherals<br>OFF, code            |                                                      | f <sub>CPU</sub> = 125 kHz          | 0.30  | 0.36  | 0.39                 | 0.44                 | 0.47                  |      |

| I <sub>DD(RUN)</sub>                  | current             | executed                            |                                                      | f <sub>CPU</sub> = 1 MHz            | 0.40  | 0.50  | 0.52                 | 0.55                 | 0.56                  | mA   |

| DD(NON)                               | in Run<br>mode      | from Flash,<br>V <sub>DD</sub> from | clock<br>(f <sub>CPU</sub> =f <sub>HSE</sub> )       | f <sub>CPU</sub> = 4 MHz            | 1.15  | 1.31  | 1.40                 | 1.45                 | 1.48                  |      |

|                                       |                     | 1.65 V to<br>3.6 V                  | (7)                                                  | f <sub>CPU</sub> = 8 MHz            | 2.17  | 2.33  | 2.44                 | 2.56                 | 2.77                  |      |

|                                       |                     | 3.6 V                               |                                                      | f <sub>CPU</sub> = 16 MHz           | 4.0   | 4.46  | 4.52                 | 4.59                 | 4.77                  |      |

|                                       |                     |                                     | LSI RC osc.                                          | f <sub>CPU</sub> = f <sub>LSI</sub> | 0.110 | 0.123 | 0.130                | 0.140                | 0.150                 |      |

|                                       |                     |                                     | LSE ext.<br>clock<br>(32.768<br>kHz) <sup>(10)</sup> | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.100 | 0.101 | 0.104                | 0.119                | 0.122                 |      |

<sup>1.</sup> All peripherals OFF,  $\rm V_{DD}$  from 1.65 V to 3.6 V, HSI internal RC osc.,  $\rm f_{CPU} = f_{SYSCLK}$

<sup>4.</sup> For devices with suffix 3

<sup>2.</sup> For devices with suffix 6

<sup>3.</sup> For devices with suffix 7

#### **Output driving current**

Subject to general operating conditions for V<sub>DD</sub> and T<sub>A</sub> unless otherwise specified.

Table 39. Output driving current (high sink ports)

| I/O<br>Type | Symbol                         | Parameter                                                              | Conditions                                           | Min                   | Max  | Unit     |

|-------------|--------------------------------|------------------------------------------------------------------------|------------------------------------------------------|-----------------------|------|----------|

| High sink   |                                | V <sub>OL</sub> <sup>(1)</sup> Output low level voltage for an I/O pin | $I_{IO}$ = +2 mA,<br>$V_{DD}$ = 3.0 V                | -                     | 0.45 | V        |

|             | V <sub>OL</sub> <sup>(1)</sup> |                                                                        | I <sub>IO</sub> = +2 mA,<br>V <sub>DD</sub> = 1.8 V  | -                     | 0.45 | >        |

|             |                                |                                                                        | I <sub>IO</sub> = +10 mA,<br>V <sub>DD</sub> = 3.0 V | -                     | 0.7  | ٧        |

| High        |                                |                                                                        | I <sub>IO</sub> = -2 mA,<br>V <sub>DD</sub> = 3.0 V  | V <sub>DD</sub> -0.45 | -    | <b>\</b> |

|             | V <sub>OH</sub> <sup>(2)</sup> |                                                                        | I <sub>IO</sub> = -1 mA,<br>V <sub>DD</sub> = 1.8 V  | V <sub>DD</sub> -0.45 | -    | ٧        |

|             |                                |                                                                        | I <sub>IO</sub> = -10 mA,<br>V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> -0.7  | -    | V        |

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

Table 40. Output driving current (true open drain ports)

| I/O<br>Type | Symbol                                                      | Parameter                                 | Conditions                                          | Min | Max  | Unit     |

|-------------|-------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------|-----|------|----------|

| drain       | V <sub>OL</sub> (1) Output low level voltage for an I/O pin | Output low lovel veltage for an I/O nin   | $I_{IO}$ = +3 mA,<br>$V_{DD}$ = 3.0 V               | -   | 0.45 | V        |

| Open        |                                                             | Output low level voltage for all I/O pill | I <sub>IO</sub> = +1 mA,<br>V <sub>DD</sub> = 1.8 V | -   | 0.45 | <b>V</b> |

The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

Table 41. Output driving current (PA0 with high sink LED driver capability)

| I/O<br>Type | Symbol                         | Parameter                               | Conditions                                           | Min | Max  | Unit |

|-------------|--------------------------------|-----------------------------------------|------------------------------------------------------|-----|------|------|

| 民           | V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin | I <sub>IO</sub> = +20 mA,<br>V <sub>DD</sub> = 2.0 V | -   | 0.45 | V    |

<sup>1.</sup> The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in *Table 16* and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

<sup>2.</sup> The  $I_{\text{IO}}$  current sourced must always respect the absolute maximum rating specified in *Table 16* and the sum of  $I_{\text{IO}}$  (I/O ports and control pins) must not exceed  $I_{\text{VDD}}$ .

#### I<sup>2</sup>C - Inter IC control interface

Subject to general operating conditions for  $V_{DD}$ ,  $f_{SYSCLK}$ , and  $T_A$  unless otherwise specified.

The STM8L  $I^2C$  interface (I2C1) meets the requirements of the Standard  $I^2C$  communication protocol described in the following table with the restriction mentioned below:

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

Table 44. I2C characteristics

| Symbol                  | Parameter                               | _                  | d mode<br>C        | Fast mo            | Unit               |     |

|-------------------------|-----------------------------------------|--------------------|--------------------|--------------------|--------------------|-----|

|                         |                                         | Min <sup>(2)</sup> | Max <sup>(2)</sup> | Min <sup>(2)</sup> | Max <sup>(2)</sup> |     |

| t <sub>w(SCLL)</sub>    | SCL clock low time                      | 4.7                | -                  | 1.3                | -                  | 116 |

| t <sub>w(SCLH)</sub>    | SCL clock high time                     | 4.0                | -                  | 0.6                | -                  | μs  |

| t <sub>su(SDA)</sub>    | SDA setup time                          | 250                | -                  | 100                | -                  |     |

| t <sub>h(SDA)</sub>     | SDA data hold time                      | 0                  | -                  | 0                  | 900                |     |

| t <sub>r(SDA)</sub>     | SDA and SCL rise time                   | -                  | 1000               | -                  | 300                | ns  |

| t <sub>f(SDA)</sub>     | SDA and SCL fall time                   | -                  | 300                | -                  | 300                |     |

| t <sub>h(STA)</sub>     | START condition hold time               | 4.0                | -                  | 0.6                | -                  |     |

| t <sub>su(STA)</sub>    | Repeated START condition setup time     | 4.7                | -                  | 0.6                | -                  | μs  |

| t <sub>su(STO)</sub>    | STOP condition setup time               | 4.0                | -                  | 0.6                | -                  | μs  |

| t <sub>w(STO:STA)</sub> | STOP to START condition time (bus free) | 4.7                | -                  | 1.3                | -                  | μs  |

| C <sub>b</sub>          | Capacitive load for each bus line       | -                  | 400                |                    | 400                | pF  |

<sup>1.</sup>  $f_{SYSCLK}$  must be at least equal to 8 MHz to achieve max fast  $I^2C$  speed (400 kHz).

Note:

For speeds around 200 kHz, the achieved speed can have  $a\pm 5\%$  tolerance For other speed ranges, the achieved speed can have  $a\pm 2\%$  tolerance The above variations depend on the accuracy of the external components used.

100/142 DocID15962 Rev 15

<sup>2.</sup> Data based on standard I<sup>2</sup>C protocol requirement, not tested in production.

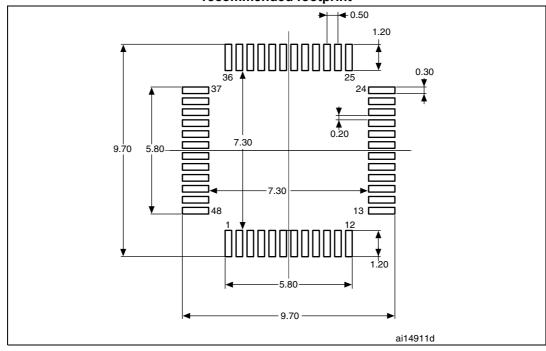

Figure 44. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

57

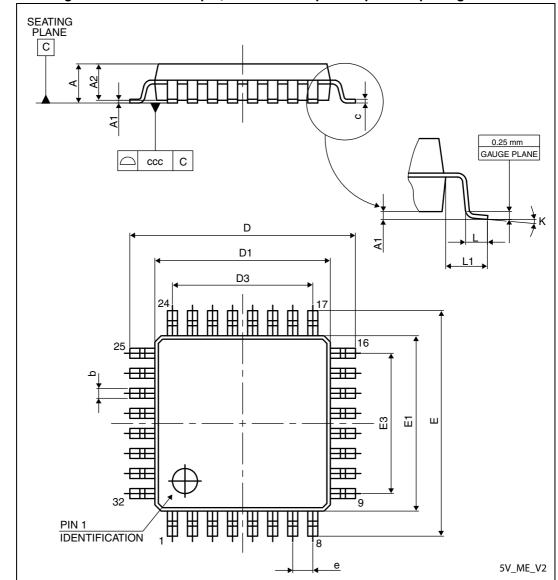

## 10.4 LQFP32 package information

Figure 49. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

Samples to run qualification activity.

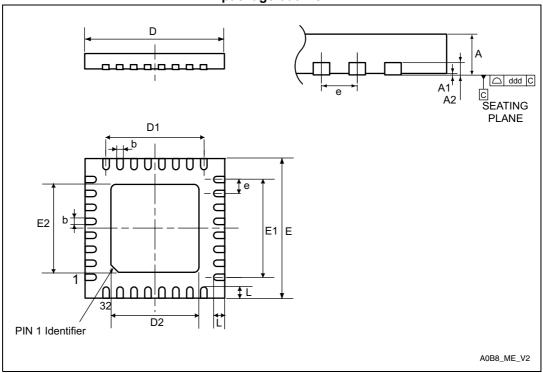

# 10.5 UFQFPN32 package information

Figure 52. UFQFPN32 - 32-pin, 5 x 5 mm, 0.5 mm pitch ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

577

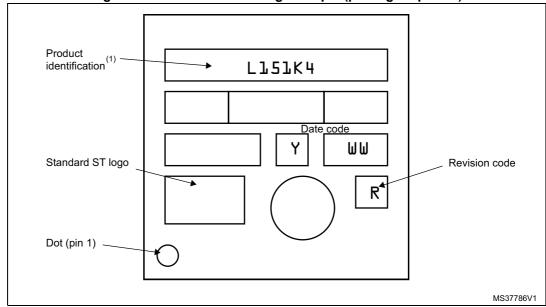

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 54. UFQFPN32 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

1. Values in inches are converted from mm and rounded to 4 decimal digits.

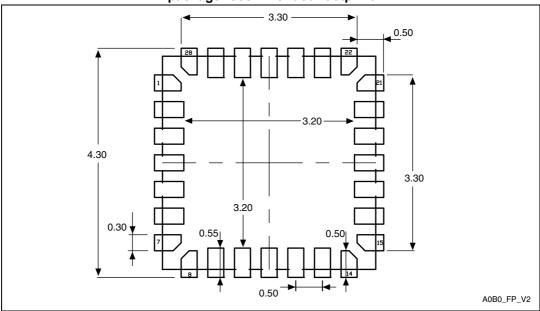

Figure 56. UFQFPN28 - 28-lead, 4 x 4 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

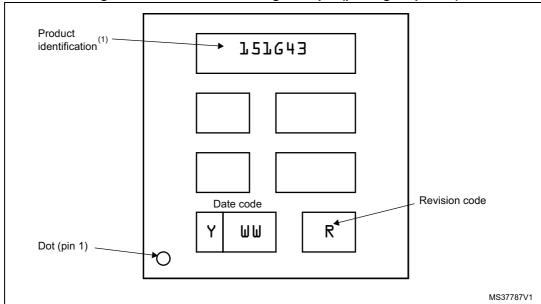

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location. Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 57. UFQFPN28 marking example (package top view)

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

### 10.8 Thermal characteristics

The maximum chip junction temperature ( $T_{Jmax}$ ) must never exceed the values given in *Table 18: General operating conditions on page 66.*

The maximum chip-junction temperature, T<sub>Jmax</sub>, in degree Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

#### Where:

- T<sub>Amax</sub> is the maximum ambient temperature in ° C

- Θ<sub>IA</sub> is the package junction-to-ambient thermal resistance in ° C/W

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax}$  ( $P_{Dmax} = P_{INTmax} + P_{I/Omax}$ )

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- P<sub>I/Omax</sub> represents the maximum power dissipation on output pins Where:

$$P_{I/Omax} = \Sigma \ (V_{OL} * I_{OL}) + \Sigma ((V_{DD} - V_{OH}) * I_{OH}),$$

taking into account the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

Table 68. Thermal characteristics<sup>(1)</sup>

| Symbol            | Parameter                                                | Value | Unit |

|-------------------|----------------------------------------------------------|-------|------|

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient LQFP 48- 7 x 7 mm    | 65    | °C/W |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient UFQFPN 48- 7 x 7mm   | 32    | °C/W |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient LQFP 32 - 7 x 7 mm   | 59    | °C/W |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient UFQFPN 32 - 5 x 5 mm | 38    | °C/W |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient UFQFPN28 - 4 x 4 mm  | 118   | °C/W |

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient WLCSP28              | 70    | °C/W |

Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.