Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                         |

| Number of I/O              | 30                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1K x 8                                                                 |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 22x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151k6t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Reset and supply management

#### 3.3.1 Power supply scheme

The device requires a 1.65 V to 3.6 V operating supply voltage ( $V_{DD}$ ). The external power supply pins must be connected as follows:

- V<sub>SS1</sub>; V<sub>DD1</sub> = 1.8 to 3.6 V, down to 1.65 V at power down: external power supply for I/Os and for the internal regulator. Provided externally through V<sub>DD1</sub> pins, the corresponding ground pin is V<sub>SS1</sub>.

- $V_{SSA;} V_{DDA} = 1.8$  to 3.6 V, down to 1.65 V at power down: external power supplies for analog peripherals (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC1 is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD1}$  and  $V_{SS1}$ , respectively.

- V<sub>SS2</sub>; V<sub>DD2</sub> = 1.8 to 3.6 V, down to 1.65 V at power down: external power supplies for I/Os. V<sub>DD2</sub> and V<sub>SS2</sub> must be connected to V<sub>DD1</sub> and V<sub>SS1</sub>, respectively.

- V<sub>REF+</sub>; V<sub>REF-</sub> (for ADC1): external reference voltage for ADC1. Must be provided externally through V<sub>REF+</sub> and V<sub>REF-</sub> pin.

- V<sub>REF+</sub> (for DAC): external voltage reference for DAC must be provided externally through V<sub>REF+</sub>.

#### 3.3.2 Power supply supervisor

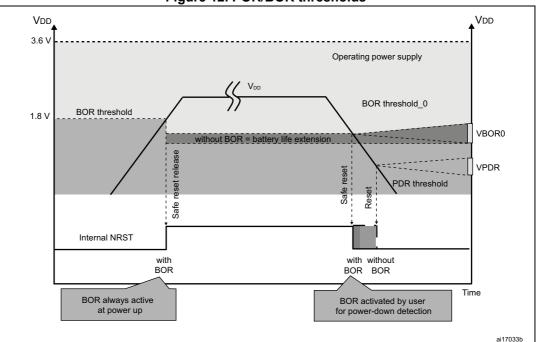

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR), coupled with a brownout reset (BOR) circuitry. At power-on, BOR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V BOR threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently (in which case, the V<sub>DD</sub> min value at power down is 1.65 V).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Halt mode, it is possible to automatically switch off the internal reference voltage (and consequently the BOR) in Halt mode. The device remains under reset when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.3.3 Voltage regulator

The medium-density STM8L151x4/6 and STM8L152x4/6 embeds an internal voltage regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes:

- Main voltage regulator mode (MVR) for Run, Wait for interrupt (WFI) and Wait for event (WFE) modes.

- Low power voltage regulator mode (LPVR) for Halt, Active-halt, Low power run and Low power wait modes.

When entering Halt or Active-halt modes, the system automatically switches from the MVR to the LPVR in order to reduce current consumption.

## 3.17 Communication interfaces

### 3.17.1 SPI

The serial peripheral interface (SPI1) provides half/ full duplex synchronous serial communication with external devices.

- Maximum speed: 8 Mbit/s (f<sub>SYSCLK</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on 2 lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- Hardware CRC calculation

- Slave/master selection input pin

Note: SPI1 can be served by the DMA1 Controller.

## 3.17.2 l<sup>2</sup>C

The I<sup>2</sup>C bus interface (I<sup>2</sup>C1) provides multi-master capability, and controls all I<sup>2</sup>C busspecific sequencing, protocol, arbitration and timing.

- Master, slave and multi-master capability

- Standard mode up to 100 kHz and fast speed modes up to 400 kHz.

- 7-bit and 10-bit addressing modes.

- SMBus 2.0 and PMBus support

- Hardware CRC calculation

Note:  $l^2C1$  can be served by the DMA1 Controller.

## 3.17.3 USART

The USART interface (USART1) allows full duplex, asynchronous communications with external devices requiring an industry standard NRZ asynchronous serial data format. It offers a very wide range of baud rates.

- 1 Mbit/s full duplex SCI

- SPI1 emulation

- High precision baud rate generator

- SmartCard emulation

- IrDA SIR encoder decoder

- Single wire half duplex mode

Note: USART1 can be served by the DMA1 Controller.

# 3.18 Infrared (IR) interface

The medium-density STM8L151x4/6 and STM8L152x4/6 devices contain an infrared interface which can be used with an IR LED for remote control functions. Two timer output compare channels are used to generate the infrared remote control signals.

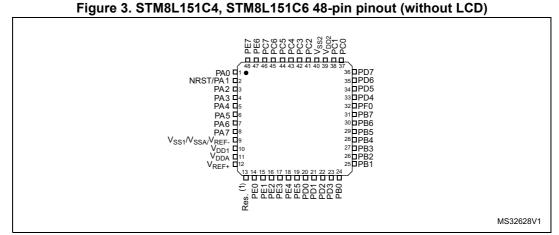

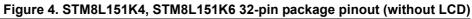

#### Pinout and pin description 4

Reserved. Must be tied to V<sub>DD</sub>. 1.

1. Example given for the UFQFPN32 package. The pinout is the same for the LQFP32 package.

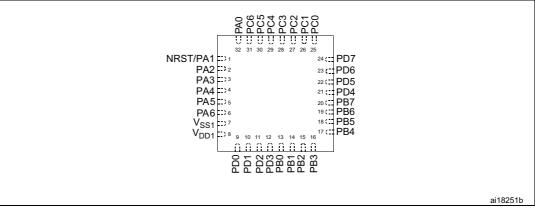

#### Figure 5. STM8L151Gx UFQFPN28 package pinout

DocID15962 Rev 15

| nı              | Pin<br>umb      | er       |         |                                                                                                       |      |           |                         | Input            | t              | o                | utpu | ıt |                                |                                                                                                                                              |

|-----------------|-----------------|----------|---------|-------------------------------------------------------------------------------------------------------|------|-----------|-------------------------|------------------|----------------|------------------|------|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48/UFQFPN48 | LQFP32/UFQFPN32 | UFQFPN28 | WLCSP28 | Pin name                                                                                              | Type | I/O level | floating                | wpu              | Ext. interrupt | High sink/source | OD   | РР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                |

| -               | 5               | 5        | D4      | PA5/TIM3_BKIN/<br><i>[TIM3_ETRJ<sup>(4)</sup>/</i><br>LCD_COM1 <sup>(2)</sup> /ADC1_IN1/<br>COMP1_INP | I/O  | TT<br>(3) | x                       | x                | x              | HS               | х    | х  | Port A5                        | Timer 3 - break input /<br>[ <i>Timer 3 - external</i><br><i>trigger</i> ] / LCD_COM 1 /<br>ADC1 input 1 /<br>Comparator 1 positive<br>input |

| 7               | 6               | -        | -       | PA6/[ <i>ADC1_TRIG</i> ] <sup>(4)</sup> /<br>LCD_COM2 <sup>(2)</sup> /ADC1_IN0/<br>COMP1_INP          | I/O  | TT<br>(3) | x                       | x                | х              | HS               | х    | х  | Port A6                        | [ADC1 - trigger] /<br>LCD_COM2 /<br>ADC1 input 0 /<br>Comparator 1 positive<br>input                                                         |

| 8               | -               | -        | -       | PA7/LCD_SEG0 <sup>(2)(5)</sup>                                                                        | I/O  | FT        | Х                       | Х                | Х              | HS               | Х    | Х  | Port A7                        | LCD segment 0                                                                                                                                |

| 24              | 13              | 12       | E3      | PB0 <sup>(6)</sup> /TIM2_CH1/<br>LCD_SEG10 <sup>(2)</sup> /<br>ADC1_IN18/COMP1_INP                    | I/O  | TT<br>(3) | <b>X</b> <sup>(6)</sup> | X <sup>(6)</sup> | x              | HS               | х    | x  | Port B0                        | Timer 2 - channel 1 /<br>LCD segment 10 /<br>ADC1_IN18 /<br>Comparator 1 positive<br>input                                                   |

| 25              | 14              | 13       | G1      | PB1/TIM3_CH1/<br>LCD_SEG11 <sup>(2)/</sup><br>ADC1_IN17/COMP1_INP                                     | I/O  | TT<br>(3) | x                       | x                | x              | HS               | x    | x  | Port B1                        | Timer 3 - channel 1 /<br>LCD segment 11 /<br>ADC1_IN17 /<br>Comparator 1 positive<br>input                                                   |

| 26              | 15              | 14       | F2      | PB2/ TIM2_CH2/<br>LCD_SEG12 <sup>(2)/</sup><br>ADC1_IN16/COMP1_INP                                    | I/O  | TT<br>(3) | x                       | x                | х              | HS               | х    | х  | Port B2                        | Timer 2 - channel 2 /<br>LCD segment 12 /<br>ADC1_IN16/<br>Comparator 1 positive<br>input                                                    |

| 27              | -               | -        |         | PB3/TIM2_ETR/<br>LCD_SEG13 <sup>(2)/</sup><br>ADC1_IN15/COMP1_INP                                     | I/O  | TT<br>(3) | x                       | x                | х              | HS               | х    | х  | Port B3                        | Timer 2 - external trigger<br>/ LCD segment 13<br>/ADC1_IN15 /<br>Comparator 1 positive<br>input                                             |

## Table 5. Medium-density STM8L151x4/6, STM8L152x4/6 pin description (continued)

| n               | Pin<br>umb      |          |         | . Mealum-density STM                                                                                                 |      |           |          | Input |                |                  | utpu |    |                                |                                                                                                                                                                      |

|-----------------|-----------------|----------|---------|----------------------------------------------------------------------------------------------------------------------|------|-----------|----------|-------|----------------|------------------|------|----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP48/UFQFPN48 | LQFP32/UFQFPN32 | UFQFPN28 | WLCSP28 | Pin name                                                                                                             | Type | I/O level | floating | ndw   | Ext. interrupt | High sink/source | OD   | ЪР | Main function<br>(after reset) | Default alternate<br>function                                                                                                                                        |

| -               | _               | 9        | G2      | PD1/TIM1_CH3/[ <i>TIM3_ET<br/>R</i> ] <sup>(4)</sup> /LCD_COM3 <sup>(2)</sup> /<br>ADC1_IN21/COMP2_INP/<br>COMP1_INP | I/O  | TT<br>(3) | x        | x     | x              | HS               | x    | x  | Port D1                        | Timer 1 channel 3 /<br>[ <i>Timer 3 - external</i><br><i>trigger</i> ] / LCD_COM3/<br>ADC1_IN21 /<br>Comparator 2 positive<br>input / Comparator 1<br>positive input |

| 22              | 11              | 10       |         | PD2/TIM1_CH1<br>/LCD_SEG8 <sup>(2)</sup> /<br>ADC1_IN20/COMP1_INP                                                    | I/O  | TT<br>(3) | x        | x     | х              | HS               | x    | х  | Port D2                        | Timer 1 - channel 1 /<br>LCD segment 8 /<br>ADC1_IN20 /<br>Comparator 1 positive<br>input                                                                            |

| 23              | 12              | 1        |         | PD3/ TIM1_ETR/<br>LCD_SEG9 <sup>(2)</sup> /ADC1_IN1<br>9/COMP1_INP                                                   | I/O  | TT<br>(3) | x        | x     | x              | HS               | x    | х  | Port D3                        | Timer 1 - external trigger<br>/ LCD segment 9 /<br>ADC1_IN19 /<br>Comparator 1 positive<br>input                                                                     |

| -               | -               | 11       | F3      | PD3/ TIM1_ETR/<br>LCD_SEG9 <sup>(2)/</sup><br>ADC1_IN19/TIM1_BKIN/<br>COMP1_INP/<br>RTC_CALIB                        | I/O  | TT<br>(3) | x        | x     | х              | HS               | x    | х  | Port D3                        | Timer 1 - external trigger<br>/ LCD segment 9 /<br>ADC1_IN19 / Timer 1<br>break input / RTC<br>calibration / Comparator<br>1 positive input                          |

| 33              | 21              | 20       | C1      | PD4/TIM1_CH2<br>/LCD_SEG18 <sup>(2)/</sup><br>ADC1_IN10/COMP1_INP                                                    | I/O  | TT<br>(3) | x        | x     | x              | HS               | x    | х  | Port D4                        | Timer 1 - channel 2 /<br>LCD segment 18 /<br>ADC1_IN10/<br>Comparator 1 positive<br>input                                                                            |

| 34              | 22              | -        |         | PD5/TIM1_CH3<br>/LCD_SEG19 <sup>(2)</sup> /<br>ADC1_IN9/COMP1_INP                                                    | I/O  | TT<br>(3) | x        | x     | х              | HS               | x    | х  | Port D5                        | Timer 1 - channel 3 /<br>LCD segment 19 /<br>ADC1_IN9/ Comparator<br>1 positive input                                                                                |

| 35              | 23              | _        | _       | PD6/TIM1_BKIN<br>/LCD_SEG20 <sup>(2)</sup> /<br>ADC1_IN8/RTC_CALIB/<br>/VREFINT/<br>COMP1_INP                        | I/O  | TT<br>(3) | x        | x     | х              | HS               | x    | х  | Port D6                        | Timer 1 - break input /<br>LCD segment 20 /<br>ADC1_IN8 / RTC<br>calibration / Internal<br>voltage reference output<br>/ Comparator 1 positive<br>input              |

## Table 5. Medium-density STM8L151x4/6, STM8L152x4/6 pin description (continued)

| Address                      | Block | Register label           | Register name                                           | Reset<br>status |  |  |

|------------------------------|-------|--------------------------|---------------------------------------------------------|-----------------|--|--|

| 0x00 5055<br>to<br>0x00 506F |       | Reserved area (27 bytes) |                                                         |                 |  |  |

| 0x00 5070                    |       | DMA1_GCSR                | DMA1 global configuration & status<br>register          | 0xFC            |  |  |

| 0x00 5071                    |       | DMA1_GIR1                | DMA1 global interrupt register 1                        | 0x00            |  |  |

| 0x00 5072 to<br>0x00 5074    |       |                          | Reserved area (3 bytes)                                 |                 |  |  |

| 0x00 5075                    |       | DMA1_C0CR                | DMA1 channel 0 configuration register                   | 0x00            |  |  |

| 0x00 5076                    |       | DMA1_C0SPR               | DMA1 channel 0 status & priority register               | 0x00            |  |  |

| 0x00 5077                    |       | DMA1_C0NDTR              | DMA1 number of data to transfer register<br>(channel 0) | 0x00            |  |  |

| 0x00 5078                    |       | DMA1_C0PARH              | DMA1 peripheral address high register<br>(channel 0)    | 0x52            |  |  |

| 0x00 5079                    |       | DMA1_C0PARL              | DMA1 peripheral address low register<br>(channel 0)     | 0x00            |  |  |

| 0x00 507A                    | DMA1  |                          | Reserved area (1 byte)                                  |                 |  |  |

| 0x00 507B                    |       | DMA1_C0M0ARH             | DMA1 memory 0 address high register<br>(channel 0)      | 0x00            |  |  |

| 0x00 507C                    |       | DMA1_C0M0ARL             | DMA1 memory 0 address low register<br>(channel 0)       | 0x00            |  |  |

| 0x00 507D to<br>0x00 507E    |       |                          | Reserved area (2 bytes)                                 |                 |  |  |

| 0x00 507F                    |       | DMA1_C1CR                | DMA1 channel 1 configuration register                   | 0x00            |  |  |

| 0x00 5080                    |       | DMA1_C1SPR               | DMA1 channel 1 status & priority register               | 0x00            |  |  |

| 0x00 5081                    |       | DMA1_C1NDTR              | DMA1 number of data to transfer register<br>(channel 1) | 0x00            |  |  |

| 0x00 5082                    |       | DMA1_C1PARH              | DMA1 peripheral address high register<br>(channel 1)    | 0x52            |  |  |

| 0x00 5083                    |       | DMA1_C1PARL              | DMA1 peripheral address low register<br>(channel 1)     | 0x00            |  |  |

Table 9. General hardware register map (continued)

| Table 9. General hardware register map (continued) |            |                         |                                           |                 |  |  |  |

|----------------------------------------------------|------------|-------------------------|-------------------------------------------|-----------------|--|--|--|

| Address                                            | Block      | Register label          | Register name                             | Reset<br>status |  |  |  |

| 0x00 50A0                                          |            | EXTI_CR1                | External interrupt control register 1     | 0x00            |  |  |  |

| 0x00 50A1                                          |            | EXTI_CR2                | External interrupt control register 2     | 0x00            |  |  |  |

| 0x00 50A2                                          |            | EXTI_CR3                | External interrupt control register 3     | 0x00            |  |  |  |

| 0x00 50A3                                          | ITC - EXTI | EXTI_SR1                | External interrupt status register 1      | 0x00            |  |  |  |

| 0x00 50A4                                          |            | EXTI_SR2                | External interrupt status register 2      | 0x00            |  |  |  |

| 0x00 50A5                                          |            | EXTI_CONF1              | External interrupt port select register 1 | 0x00            |  |  |  |

| 0x00 50A6                                          |            | WFE_CR1                 | WFE control register 1                    | 0x00            |  |  |  |

| 0x00 50A7                                          | WFE        | WFE_CR2                 | WFE control register 2                    | 0x00            |  |  |  |

| 0x00 50A8                                          |            | WFE_CR3                 | WFE control register 3                    | 0x00            |  |  |  |

| 0x00 50A9<br>to<br>0x00 50AF                       |            | Reserved area (7 bytes) |                                           |                 |  |  |  |

| 0x00 50B0                                          | RST        | RST_CR                  | Reset control register                    | 0x00            |  |  |  |

| 0x00 50B1                                          | - KOT      | RST_SR                  | Reset status register                     | 0x01            |  |  |  |

| 0x00 50B2                                          | PWR        | PWR_CSR1                | Power control and status register 1       | 0x00            |  |  |  |

| 0x00 50B3                                          |            | PWR_CSR2                | Power control and status register 2       | 0x00            |  |  |  |

| 0x00 50B4<br>to<br>0x00 50BF                       |            | R                       | Reserved area (12 bytes)                  |                 |  |  |  |

| 0x00 50C0                                          |            | CLK_DIVR                | Clock master divider register             | 0x03            |  |  |  |

| 0x00 50C1                                          |            | CLK_CRTCR               | Clock RTC register                        | 0x00            |  |  |  |

| 0x00 50C2                                          |            | CLK_ICKR                | Internal clock control register           | 0x11            |  |  |  |

| 0x00 50C3                                          |            | CLK_PCKENR1             | Peripheral clock gating register 1        | 0x00            |  |  |  |

| 0x00 50C4                                          |            | CLK_PCKENR2             | Peripheral clock gating register 2        | 0x80            |  |  |  |

| 0x00 50C5                                          |            | CLK_CCOR                | Configurable clock control register       | 0x00            |  |  |  |

| 0x00 50C6                                          |            | CLK_ECKR                | External clock control register           | 0x00            |  |  |  |

| 0x00 50C7                                          | CLK        | CLK_SCSR                | System clock status register              | 0x01            |  |  |  |

| 0x00 50C8                                          |            | CLK_SWR                 | System clock switch register              | 0x01            |  |  |  |

| 0x00 50C9                                          |            | CLK_SWCR                | Clock switch control register             | 0bxxxx0000      |  |  |  |

| 0x00 50CA                                          |            | CLK_CSSR                | Clock security system register            | 0x00            |  |  |  |

| 0x00 50CB                                          | 1          | CLK_CBEEPR              | Clock BEEP register                       | 0x00            |  |  |  |

| 0x00 50CC                                          | 1          | CLK_HSICALR             | HSI calibration register                  | 0xxx            |  |  |  |

| 0.00.5000                                          | 1          | CLK_HSITRIMR            | HSI clock calibration trimming register   | 0x00            |  |  |  |

| 0x00 50CD                                          |            |                         |                                           |                 |  |  |  |

| 0x00 50CD<br>0x00 50CE                             | -          | CLK_HSIUNLCKR           | HSI unlock register                       | 0x00            |  |  |  |

| Table 9. General | hardware | register ma | ap ( | (continued) |

|------------------|----------|-------------|------|-------------|

| Address                   | Block | Register label           | Register name                          | Reset<br>status |  |

|---------------------------|-------|--------------------------|----------------------------------------|-----------------|--|

| 0x00 5280                 |       | TIM3_CR1                 | TIM3 control register 1                | 0x00            |  |

| 0x00 5281                 |       | TIM3_CR2                 | TIM3 control register 2                | 0x00            |  |

| 0x00 5282                 |       | TIM3_SMCR                | TIM3 Slave mode control register       | 0x00            |  |

| 0x00 5283                 |       | TIM3_ETR                 | TIM3 external trigger register         | 0x00            |  |

| 0x00 5284                 |       | TIM3_DER                 | TIM3 DMA1 request enable register      | 0x00            |  |

| 0x00 5285                 |       | TIM3_IER                 | TIM3 interrupt enable register         | 0x00            |  |

| 0x00 5286                 |       | TIM3_SR1                 | TIM3 status register 1                 | 0x00            |  |

| 0x00 5287                 |       | TIM3_SR2                 | TIM3 status register 2                 | 0x00            |  |

| 0x00 5288                 |       | TIM3_EGR                 | TIM3 event generation register         | 0x00            |  |

| 0x00 5289                 |       | TIM3_CCMR1               | TIM3 Capture/Compare mode register 1   | 0x00            |  |

| 0x00 528A                 |       | TIM3_CCMR2               | TIM3 Capture/Compare mode register 2   | 0x00            |  |

| 0x00 528B                 | ТІМЗ  | TIM3_CCER1               | TIM3 Capture/Compare enable register 1 | 0x00            |  |

| 0x00 528C                 |       | TIM3_CNTRH               | TIM3 counter high                      | 0x00            |  |

| 0x00 528D                 |       | TIM3_CNTRL               | TIM3 counter low                       | 0x00            |  |

| 0x00 528E                 |       | TIM3_PSCR                | TIM3 prescaler register                | 0x00            |  |

| 0x00 528F                 |       | TIM3_ARRH                | TIM3 Auto-reload register high         | 0xFF            |  |

| 0x00 5290                 |       | TIM3_ARRL                | TIM3 Auto-reload register low          | 0xFF            |  |

| 0x00 5291                 |       | TIM3_CCR1H               | TIM3 Capture/Compare register 1 high   | 0x00            |  |

| 0x00 5292                 |       | TIM3_CCR1L               | TIM3 Capture/Compare register 1 low    | 0x00            |  |

| 0x00 5293                 |       | TIM3_CCR2H               | TIM3 Capture/Compare register 2 high   | 0x00            |  |

| 0x00 5294                 |       | TIM3_CCR2L               | TIM3 Capture/Compare register 2 low    | 0x00            |  |

| 0x00 5295                 |       | TIM3_BKR                 | TIM3 break register                    | 0x00            |  |

| 0x00 5296                 |       | TIM3_OISR                | TIM3 output idle state register        | 0x00            |  |

| 0x00 5297 to<br>0x00 52AF |       | Reserved area (25 bytes) |                                        |                 |  |

|          |           | -        | -        |     |             |  |

|----------|-----------|----------|----------|-----|-------------|--|

| Table 9. | General h | nardware | reaister | map | (continued) |  |

# 6 Interrupt vector mapping

| IRQ<br>No. | Source<br>block                 | Description                                                                                            | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |

|------------|---------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|

| -          | RESET                           | Reset                                                                                                  | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8000         |

| -          | TRAP                            | Software interrupt                                                                                     | -                           | -                                     | -                                    | -                                                   | 0x00 8004         |

| 0          |                                 |                                                                                                        | Reserved                    |                                       |                                      |                                                     | 0x00 8008         |

| 1          | FLASH                           | FLASH end of programing/<br>write attempted to<br>protected page interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 800C         |

| 2          | DMA1 0/1                        | DMA1 channels 0/1 half<br>transaction/transaction<br>complete interrupt                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8010         |

| 3          | DMA1 2/3                        | DMA1 channels 2/3 half<br>transaction/transaction<br>complete interrupt                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8014         |

| 4          | RTC                             | RTC alarm A/<br>wakeup                                                                                 | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8018         |

| 5          | EXTI E/F/<br>PVD <sup>(2)</sup> | External interrupt port E/F<br>PVD interrupt                                                           | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 801C         |

| 6          | EXTIB/G                         | External interrupt port B/G                                                                            | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8020         |

| 7          | EXTID/H                         | External interrupt port D/H                                                                            | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8024         |

| 8          | EXTI0                           | External interrupt 0                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8028         |

| 9          | EXTI1                           | External interrupt 1                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 802C         |

| 10         | EXTI2                           | External interrupt 2                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8030         |

| 11         | EXTI3                           | External interrupt 3                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8034         |

| 12         | EXTI4                           | External interrupt 4                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8038         |

| 13         | EXTI5                           | External interrupt 5                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 803C         |

| 14         | EXTI6                           | External interrupt 6                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8040         |

| 15         | EXTI7                           | External interrupt 7                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8044         |

| 16         | LCD                             | LCD interrupt                                                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8048         |

| 17         | CLK/TIM1/<br>DAC                | CLK system clock switch/<br>CSS interrupt/<br>TIM 1 break/DAC                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 804C         |

| 18         | COMP1/<br>COMP2/<br>ADC1        | COMP1 interrupt<br>COMP2 interrupt<br>ACD1 end of conversion/<br>analog watchdog/<br>overrun interrupt | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8050         |

#### Table 11. Interrupt mapping

- 1. Data guaranteed by design.

- 2. Data based on characterization results.

#### Figure 12. POR/BOR thresholds

## 9.3.3 Supply current characteristics

#### **Total current consumption**

The MCU is placed under the following conditions:

- I All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- I All peripherals are disabled except if explicitly mentioned.

In the following table, data is based on characterization results, unless otherwise specified. Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

In the following table, data is based on characterization results, unless otherwise specified.

| Symbol              | Parameter                          |                       | Conditions <sup>(1)</sup>         |                         |      | Max  | Unit |

|---------------------|------------------------------------|-----------------------|-----------------------------------|-------------------------|------|------|------|

|                     |                                    |                       |                                   | $T_A$ = -40 °C to 25 °C | 0.9  | 2.1  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 55 °C  | 1.2  | 3    |      |

|                     |                                    |                       | LCD OFF <sup>(2)</sup>            | T <sub>A</sub> = 85 °C  | 1.5  | 3.4  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 105 °C | 2.6  | 6.6  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 125 °C | 5.1  | 12   |      |

|                     |                                    |                       |                                   | $T_A$ = -40 °C to 25 °C | 1.4  | 3.1  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 55 °C  | 1.5  | 3.3  |      |

|                     | Supply current in Active-halt mode | LSI RC<br>(at 38 kHz) |                                   | T <sub>A</sub> = 85 °C  | 1.9  | 4.3  | μΑ   |

|                     |                                    |                       |                                   | T <sub>A</sub> = 105 °C | 2.9  | 6.8  |      |

| I <sub>DD(AH)</sub> |                                    |                       |                                   | T <sub>A</sub> = 125 °C | 5.5  | 13   |      |

| 'DD(AH)             |                                    |                       | LCD ON<br>(1/4 duty/<br>external  | $T_A$ = -40 °C to 25 °C | 1.9  | 4.3  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 55 °C  | 1.95 | 4.4  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 85 °C  | 2.4  | 5.4  |      |

|                     |                                    |                       | V <sub>LCD</sub> ) <sup>(4)</sup> | T <sub>A</sub> = 105 °C | 3.4  | 7.6  |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 125 °C | 6.0  | 15   |      |

|                     |                                    |                       |                                   | $T_A$ = -40 °C to 25 °C | 3.9  | 8.75 |      |

|                     |                                    |                       | LCD ON<br>(1/4 duty/              | T <sub>A</sub> = 55 °C  | 4.15 | 9.3  |      |

|                     |                                    |                       | internal                          | T <sub>A</sub> = 85 °C  | 4.5  | 10.2 |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 105 °C | 5.6  | 13.5 |      |

|                     |                                    |                       |                                   | T <sub>A</sub> = 125 °C | 6.8  | 16.3 |      |

## Table 24. Total current consumption and timing in Active-halt mode at $V_{DD}$ = 1.65 V to 3.6 V

#### HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

$R_m$ : Motional resistance (see crystal specification),  $L_m$ : Motional inductance (see crystal specification),  $C_m$ : Motional capacitance (see crystal specification), Co: Shunt capacitance (see crystal specification), CL\_1=C\_{L2}=C: Grounded external capacitance  $g_m >> g_{mcrit}$

#### LSE crystal/ceramic resonator oscillator

The LSE clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol              | Parameter                                  | Conditions                    | Min              | Тур    | Мах                | Unit |  |

|---------------------|--------------------------------------------|-------------------------------|------------------|--------|--------------------|------|--|

| f <sub>LSE</sub>    | Low speed external oscillator<br>frequency | -                             | -                | 32.768 | -                  | kHz  |  |

| R <sub>F</sub>      | Feedback resistor                          | ∆V = 200 mV                   | -                | 1.2    | -                  | MΩ   |  |

| C <sup>(1)</sup>    | Recommended load capacitance (2)           | -                             | -                | 8      | -                  | pF   |  |

|                     |                                            | -                             | -                | -      | 1.4 <sup>(3)</sup> | μA   |  |

| 1                   | LSE oscillator power consumption           | V <sub>DD</sub> = 1.8 V       | -                | 450    | -                  |      |  |

| IDD(LSE)            |                                            | V <sub>DD</sub> = 3 V         | -                | 600    | -                  | nA   |  |

|                     |                                            | V <sub>DD</sub> = 3.6 V       | -                | 750    | -                  |      |  |

| 9 <sub>m</sub>      | Oscillator transconductance                | -                             | 3 <sup>(3)</sup> | -      | -                  | µA/V |  |

| $t_{SU(LSE)}^{(4)}$ | Startup time                               | $V_{\text{DD}}$ is stabilized | -                | 1      | -                  | S    |  |

| Table 32. LSE | oscillator | characteristics |

|---------------|------------|-----------------|

|---------------|------------|-----------------|

1. C=C<sub>L1</sub>=C<sub>L2</sub> is approximately equivalent to 2 x crystal C<sub>LOAD</sub>.

The oscillator selection can be optimized in terms of supply current using a high quality resonator with a small R<sub>m</sub> value. Refer to crystal manufacturer for more details.

3. Data guaranteed by design.

t<sub>SU/LSE</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

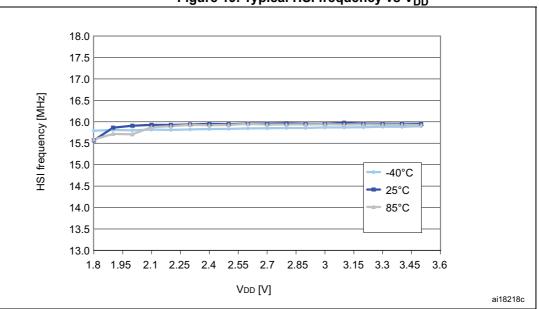

Figure 19. Typical HSI frequency vs V<sub>DD</sub>

#### Low speed internal RC oscillator (LSI)

In the following table, data is based on characterization results, not tested in production.

| Symbol               | Parameter <sup>(1)</sup>                      | Conditions <sup>(1)</sup>    | Min | Тур | Max                | Unit |

|----------------------|-----------------------------------------------|------------------------------|-----|-----|--------------------|------|

| f <sub>LSI</sub>     | Frequency                                     | -                            | 26  | 38  | 56                 | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time                    | -                            | -   | -   | 200 <sup>(2)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator frequency drift <sup>(3)</sup> | 0 °C ≤T <sub>A</sub> ≤ 85 °C | -12 | -   | 11                 | %    |

Table 34. LSI oscillator characteristics

1.  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125  $^\circ C$  unless otherwise specified.

2. Guaranteed by design.

3. This is a deviation for an individual part, once the initial frequency has been measured.

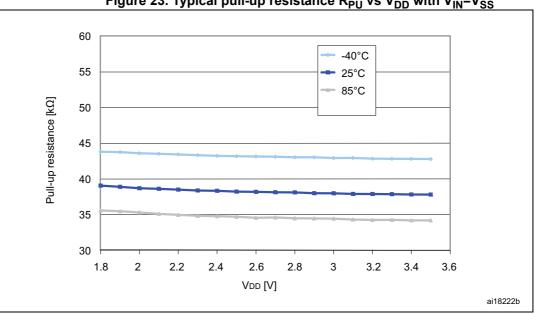

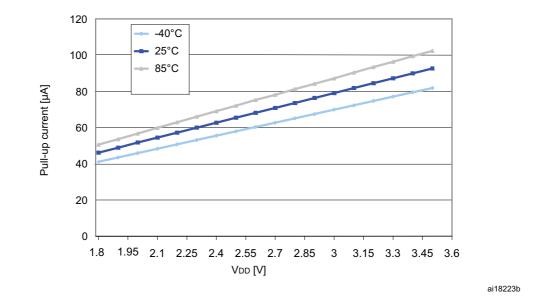

Figure 23. Typical pull-up resistance  $R_{PU}$  vs  $V_{DD}$  with  $V_{IN}$ = $V_{SS}$

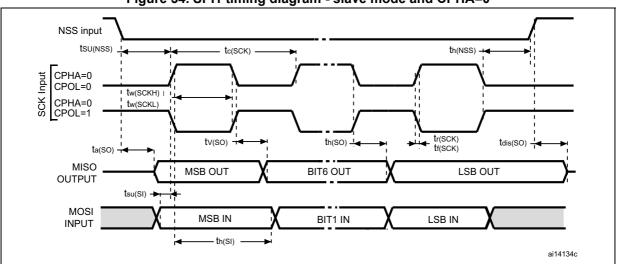

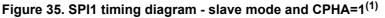

Figure 34. SPI1 timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

## 9.3.10 Embedded reference voltage

In the following table, data is based on characterization results, not tested in production, unless otherwise specified.

| Symbol                                   | Parameter Conditions                                                                           |                                 | Min                  | Тур   | Max.                 | Unit   |

|------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------|----------------------|-------|----------------------|--------|

| I <sub>REFINT</sub>                      | Internal reference voltage<br>consumption                                                      | -                               | -                    | 1.4   | -                    | μA     |

| T <sub>S_VREFINT</sub> <sup>(1)(2)</sup> | ADC sampling time when reading the internal reference voltage                                  | -                               | -                    | 5     | 10                   | μs     |

| I <sub>BUF</sub> <sup>(2)</sup>          | Internal reference voltage buffer consumption (used for ADC)                                   | -                               | -                    | 13.5  | 25                   | μA     |

| V <sub>REFINT out</sub>                  | Reference voltage output                                                                       | -                               | 1.202 <sup>(3)</sup> | 1.224 | 1.242 <sup>(3)</sup> | V      |

| I <sub>LPBUF</sub> <sup>(2)</sup>        | Internal reference voltage low<br>power buffer consumption (used<br>for comparators or output) | -                               | -                    | 730   | 1200                 | nA     |

| I <sub>REFOUT</sub> <sup>(2)</sup>       | Buffer output current <sup>(4)</sup>                                                           | -                               | -                    | -     | 1                    | μA     |

| C <sub>REFOUT</sub>                      | Reference voltage output load                                                                  | -                               | -                    | -     | 50                   | pF     |

|                                          | Internal reference voltage startup time                                                        | -                               | -                    | 2     | 3                    | ms     |

| t <sub>BUFEN</sub> <sup>(2)</sup>        | Internal reference voltage buffer startup time once enabled <sup>(1)</sup>                     | -                               | -                    | -     | 10                   | μs     |

| ACC <sub>VREFINT</sub>                   | Accuracy of V <sub>REFINT</sub> stored in the VREFINT_Factory_CONV byte <sup>(5)</sup>         | -                               | -                    | -     | ± 5                  | mV     |

| STAR                                     | Stability of V <sub>REFINT</sub> over temperature                                              | -40 °C ≤T <sub>A</sub> ≤ 125 °C | -                    | 20    | 50                   | ppm/°C |

| STAB <sub>VREFINT</sub>                  | Stability of V <sub>REFINT</sub> over temperature                                              | 0 °C ≤T <sub>A</sub> ≤ 50 °C    | -                    | -     | 20                   | ppm/°C |

| STAB <sub>VREFINT</sub>                  | Stability of V <sub>REFINT</sub> after 1000<br>hours                                           | -                               | -                    | -     | TBD                  | ppm    |

| Table 46 | Reference | voltage | characteristics |

|----------|-----------|---------|-----------------|

|----------|-----------|---------|-----------------|

1. Defined when ADC output reaches its final value  $\pm 1/2LSB$

2. Data guaranteed by design.

3. Tested in production at V<sub>DD</sub> = 3 V ±10 mV.

4. To guaranty less than 1%  $V_{\mbox{\scriptsize REFOUT}}$  deviation.

5. Measured at  $V_{DD}$  = 3 V ±10 mV. This value takes into account  $V_{DD}$  accuracy and ADC conversion accuracy.

In the following table, data is based on characterization results, not tested in production.

| Symbol     | Parameter                                 | Conditions                                                                            | Тур       | Max       | Unit          |  |

|------------|-------------------------------------------|---------------------------------------------------------------------------------------|-----------|-----------|---------------|--|

| DNL        | Differential non linearity <sup>(1)</sup> | $R_L ≥5 kΩ$ C <sub>L</sub> ≤50 pF<br>DACOUT buffer ON <sup>(2)</sup>                  | 1.5       | 3         |               |  |

| DIL        | Directential non-incarty                  | No load<br>DACOUT buffer OFF                                                          | 1.5       | 3         |               |  |

| INL        | Integral non linearity <sup>(3)</sup>     | $R_L ≥5 kΩ$ C <sub>L</sub> ≤ 50 pF<br>DACOUT buffer ON <sup>(2)</sup>                 | 2         | 4         | 10 hit        |  |

| INL        | Integral nor inteanty                     | No load<br>DACOUT buffer OFF                                                          | 2         | 4         | 12-bit<br>LSB |  |

| Offset     | Offset error <sup>(4)</sup>               | $R_L \ge 5 \text{ k}\Omega \text{ C}_L \le 50 \text{ pF}$<br>DACOUT buffer $ON^{(2)}$ | ±10       | ±25       |               |  |

| Oliset     |                                           | No load<br>DACOUT buffer OFF                                                          | ±5        | ±8        |               |  |

| Offset1    | Offset error at Code 1 <sup>(5)</sup>     | DACOUT buffer OFF                                                                     | ±1.5      | ±5        |               |  |

| Gain error | Gain error <sup>(6)</sup>                 | $R_L ≥5 kΩ$ C <sub>L</sub> ≤ 50 pF<br>DACOUT buffer ON <sup>(2)</sup>                 | +0.1/-0.2 | +0.2/-0.5 | - %           |  |

|            |                                           | No load<br>DACOUT buffer OFF                                                          |           | +0/-0.4   |               |  |

|            |                                           | $R_L \ge 5 \text{ k}\Omega, C_L \le 50 \text{ pF}$                                    | 12        | 30        |               |  |

| TUE        | Total unadjusted error                    | $DACOUT$ buffer $ON^{(2)}$                                                            | 50        | 12-bit    |               |  |

| IUE        |                                           | No load<br>DACOUT buffer OFF                                                          | 8         | 12        | LSB           |  |

| Table | 51.      | DAC | accu | racy |

|-------|----------|-----|------|------|

| IUNIC | <b>v</b> | DAO | accu | IUCY |

1. Difference between two consecutive codes - 1 LSB.

2. For 48-pin packages only. For 28-pin and 32-pin packages, DAC output buffer must be kept off and no load must be applied.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 1023.

4. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

5. Difference between the value measured at Code (0x001) and the ideal value.

6. Difference between the ideal slope of the transfer function and the measured slope computed from Code 0x000 and 0xFFF when buffer is ON, and from Code giving 0.2 V and ( $V_{DDA}$  -0.2) V when buffer is OFF.

In the following table, data is guaranteed by design, not tested in production.

#### Table 52. DAC output on PB4-PB5-PB6<sup>(1)</sup>

| Symbol           | Parameter                                 | Conditions                      | Мах | Unit |  |

|------------------|-------------------------------------------|---------------------------------|-----|------|--|

| R <sub>int</sub> | Internal resistance                       | 2.7 V < V <sub>DD</sub> < 3.6 V | 1.4 |      |  |

|                  |                                           | 2.4 V < V <sub>DD</sub> < 3.6 V | 1.6 | ko   |  |

|                  | between DAC output and PB4-PB5-PB6 output | 2.0 V < V <sub>DD</sub> < 3.6 V | 3.2 | kΩ   |  |

|                  |                                           | 1.8 V < V <sub>DD</sub> < 3.6 V | 8.2 |      |  |

1. 32 or 28-pin packages only. The DAC channel can be routed either on PB4, PB5 or PB6 using the routing interface I/O switch registers.

### 9.3.15 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                            | Conditions                                                                               |           |    |  |  |

|-------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------|----|--|--|

| V <sub>FESD</sub> | Voltage limits to be applied on<br>any I/O pin to induce a functional<br>disturbance | $V_{DD}$ = 3.3 V, $T_A$ = +25 °C,<br>f <sub>CPU</sub> = 16 MHz,<br>conforms to IEC 61000 |           | 3B |  |  |

| V <sub>EETB</sub> | $V_{EFTB}$ $V_{DD}$ and $V_{SS}$ pins to induce a                                    | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C,<br>f <sub>CPU</sub> = 16 MHz,          | Using HSI | 4A |  |  |

|                   |                                                                                      | conforms to IEC 61000 Using HSE                                                          |           | 2B |  |  |

Table 58. EMS data

#### **Electromagnetic interference (EMI)**

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm IEC61967-2 which specifies the board and the loading of each pin.

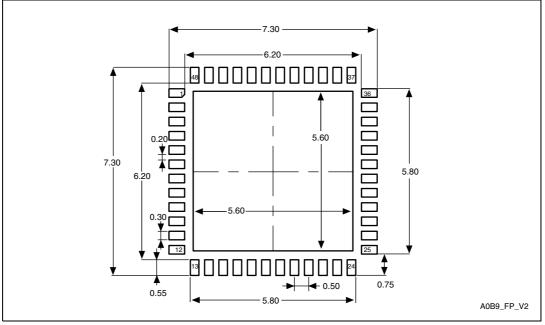

|        | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

# Table 63. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 47. UFQFPN48 - 48-lead, 7 x 7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-Mar-2011 | 6 cont'd | <ul> <li>Modified OPT1 and OPT4 description in <i>Table: Option byte description.</i></li> <li>Updated <i>Section: Electrical parameters</i> "standard I/Os" replaced with "high sink I//Os".</li> <li>Updated R<sub>HN and</sub> R<sub>HN</sub> descriptions in <i>Table: LCD characteristics.</i></li> <li>Added Tape &amp; Reel option to <i>Figure: Medium density STM8L15x ordering information scheme.</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 06-Sep-2011 | 7        | Features: updated bullet point concerning capacitive sensing channels.         Section: Low power modes: updated Wait mode and Halt mode definitions.         Section: Clock management: added 'kHz' to 32.768 in the 'System clock sources bullet point'.         Section: System configuration controller and routing interface: replaced last sentence concerning management of charge transfer acquisition sequence.         Added Section: Touchsensing         Section Development support: updated the Bootloader.         Table: Medium density STM8L15x pin description:         added LQFP32 to second column (same pinout as UFQFPN32); "Timer X - trigger" replaced by "Timer X - external trigger"; added note at the end of this table concerning the slope control of all GPIO pins.         Table: Interrupt mapping: merged footnotes 1 and 2; updated some of the source blocks and descriptions.         Section: Option bytes: replaced PM0051 by PM0054 and UM0320 by UM0470.         Table: Option byte description: replaced the factory default setting (0xAA) for OPT0.         NRST pin: updated text above the Figure; updated Figure: Recommended NRST pin configuration.         Table: Comparator 1 characteristics: added typ value for 'Comparator offset error'; added footnotes 1. and 3.         Table: DAC characteristics: updated max values for the parameter T <sub>S_TEMP</sub> ; added min value for same.         Table: Comparator 2 characteristics: updated t <sub>START</sub> , t <sub>dslow</sub> , t <sub>dfast</sub> , V <sub>offset</sub> , I <sub>COMP2</sub> ; added footnotes 1. and 3.         Table: DAC characteristics: updated max value for DAC_OUT voltage (DACOUT buffer ON). |