# E·XFL

### NXP USA Inc. - DSP56301AG100 Datasheet

Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

### Details

| Product Status          | Obsolete                                                              |

|-------------------------|-----------------------------------------------------------------------|

| Туре                    | Fixed Point                                                           |

| Interface               | Host Interface, SSI, SCI                                              |

| Clock Rate              | 100MHz                                                                |

| Non-Volatile Memory     | ROM (9kB)                                                             |

| On-Chip RAM             | 24kB                                                                  |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 3.30V                                                                 |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                    |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 208-LQFP                                                              |

| Supplier Device Package | 208-TQFP (28x28)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/dsp56301ag100 |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Signals/Connections

The DSP56301 input and output signals are organized into functional groups, as shown in **Table 1-1** and illustrated in **Figure 1-1**. The DSP56301 operates from a 3 V supply; however, some of the inputs can tolerate 5 V. A special notice for this feature is added to the signal descriptions of those inputs.

| Functional Group                             |                            |             | ber of<br>als by<br>ge Type | Detailed Description         |  |

|----------------------------------------------|----------------------------|-------------|-----------------------------|------------------------------|--|

|                                              | TQFP                       | MAP-<br>BGA |                             |                              |  |

| Power (V <sub>CC</sub> ) <sup>1</sup>        |                            | 25          | 45                          | Table 1-2                    |  |

| Ground (GND) <sup>1</sup>                    |                            | 26          | 38                          | Table 1-3                    |  |

| Clock                                        |                            | 2           | 2                           | Table 1-4                    |  |

| PLL                                          |                            |             | 3                           | Table 1-5                    |  |

| Address Bus                                  | 2                          | 24          | 24                          | Table 1-6                    |  |

| Data Bus                                     | Port A <sup>2</sup>        | 24          | 24                          | Table 1-7                    |  |

| Bus Control                                  |                            |             | 15                          | Table 1-8                    |  |

| Interrupt and Mode Control                   |                            |             | 5                           | Table 1-9                    |  |

| Host Interface (HI32) Port B <sup>3</sup>    |                            | 52          | 52                          | Table 1-11                   |  |

| Enhanced Synchronous Serial Interface (ESSI) | Ports C and D <sup>4</sup> | 12          | 12                          | Table 1-12 and<br>Table 1-13 |  |

| Serial Communication Interface (SCI)         | Port E <sup>5</sup>        | 3           | 3                           | Table 1-14                   |  |

| Timer                                        | 1                          | 3           | 3                           | Table 1-15                   |  |

| JTAG/OnCE Port                               |                            | 6           | 6                           | Table 1-16                   |  |

| Table 1-1. | DSP56301 | Functional | Signal | Groupings |

|------------|----------|------------|--------|-----------|

|------------|----------|------------|--------|-----------|

1. The number of available power and ground signals is package-dependent. In the TQFP package specific pins are dedicated internally to device subsystems. In the MAP-BGA package, power and ground connections (except those providing PLL power) connect to internal power and ground planes, respectively.

2. Port A signals define the external memory interface port, including the external address bus, data bus, and control signals.

- 3. Port B signals are the HI32 port signals multiplexed with the GPIO signals.

- 4. Port C and D signals are the two ESSI port signals multiplexed with the GPIO signals.

- 5. Port E signals are the SCI port signals multiplexed with the GPIO signals.

6. Each device also includes several no connect (NC) pins. The number of NC connections is package-dependent: the TQFP has 9 NCs and the MAP-BGA has 20 NCs. Do not connect any line, component, trace, or via to these pins. See **Chapter 3** for details.

als/Connections

| Signal Name | Туре             | State During<br>Reset | Signal Description                                                                                                                                                                   |

|-------------|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HTRDY       | Input/<br>Output | Tri-stated            | Host Target Ready<br>When the HI32 is programmed to interface with a PCI bus and the HI function<br>is selected, this is the Host Target Ready signal.                               |

| HDBEN       | Output           |                       | Host Data Bus Enable<br>When HI32 is programmed to interface with a universal, non-PCI bus and the<br>HI function is selected, this is the Host Data Bus Enable signal.              |

| PB20        | Input or Output  |                       | <b>Port B 20</b><br>When the HI32 is configured as GPIO through the DCTR, this signal is individually programmed through the HI32 DIRH.                                              |

|             |                  |                       | This input is 5 V tolerant.                                                                                                                                                          |

| HIRDY       | Input/<br>Output | Tri-stated            | Host Initiator Ready<br>When the HI32 is programmed to interface with a PCI bus and the HI function<br>is selected, this is the Host Initiator Ready signal.                         |

| HDBDR       | Output           |                       | Host Data Bus Direction<br>When HI32 is programmed to interface with a universal, non-PCI bus and the<br>HI function is selected, this is the Host Data Bus Direction signal.        |

| PB21        | Input or Output  |                       | <b>Port B 21</b><br>When the HI32 is configured as GPIO through the DCTR, this signal is individually programmed through the HI32 DIRH.                                              |

|             |                  |                       | This input is 5 V tolerant.                                                                                                                                                          |

| HDEVSEL     | Input/<br>Output | Tri-stated            | Host Device Select<br>When the HI32 is programmed to interface with a PCI bus and the HI function<br>is selected, this is the Host Device Select signal.                             |

| HSAK        | Output           |                       | <b>Host Select Acknowledge</b><br>When HI32 is programmed to interface with a universal, non-PCI bus and the<br>HI function is selected, this is the Host Select Acknowledge signal. |

| PB22        | Input or Output  |                       | <b>Port B 22</b><br>When the HI32 is configured as GPIO through the DCTR, this signal is individually programmed through the HI32 DIRH.                                              |

|             |                  |                       | This input is 5 V tolerant.                                                                                                                                                          |

| HLOCK       | Input            | Tri-stated            | Host Lock<br>When the HI32 is programmed to interface with a PCI bus and the HI function<br>is selected, this is the Host Lock signal.                                               |

| HBS         | Input            |                       | Host Bus Strobe<br>When HI32 is programmed to interface with a universal, non-PCI bus and the<br>HI function is selected, this is the Host Bus Strobe Schmitt-trigger signal.        |

| PB23        | Input or Output  |                       | <b>Port B 23</b><br>When the HI32 is configured as GPIO through the DCTR, this signal is individually programmed through the HI32 DIRH.                                              |

|             |                  |                       | This input is 5 V tolerant.                                                                                                                                                          |

### Table 1-11. Host Interface (Continued)

| Signal Name | Туре            | State During<br>Reset | Signal Description                                                                                                                                                                                                           |

|-------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRD1        | Input/Output    | Input                 | Serial Receive Data<br>Receives serial data and transfers it to the ESSI receive shift register. SRD1 is<br>an input when data is being received.                                                                            |

| PD4         | Input or Output |                       | <b>Port D 4</b><br>The default configuration following reset is GPIO. For PD4, signal direction is controlled through PRR1. The signal can be configured as an ESSI signal SRD1 through PCR1.<br>This input is 5 V tolerant. |

| STD1        | Input/Output    | Input                 | <b>Serial Transmit Data</b><br>Transmits data from the serial transmit shift register. STD1 is an output when data is being transmitted.                                                                                     |

| PD5         | Input or Output |                       | <b>Port D 5</b><br>The default configuration following reset is GPIO. For PD5, signal direction is controlled through PRR1. The signal can be configured as an ESSI signal STD1 through PCR1.                                |

|             |                 |                       | This input is 5 V tolerant.                                                                                                                                                                                                  |

Table 1-13.

Enhanced Synchronous Serial Interface 1 (ESSI1) (Continued)

### 1.10 Serial Communication Interface (SCI)

The Serial Communication interface (SCI) provides a full duplex port for serial communication with other DSPs, microprocessors, or peripherals such as modems.

| Signal Name | Туре            | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                  |

|-------------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXD         | Input           | Input                 | Serial Receive Data<br>Receives byte-oriented serial data and transfers it to the SCI receive shift<br>register.                                                                                                                                                                                                                    |

| PE0         | Input or Output |                       | <ul> <li>Port E 0</li> <li>The default configuration following reset is GPIO. When configured as PE0, signal direction is controlled through the SCI Port Directions Register (PRR). The signal can be configured as an SCI signal RXD through the SCI Port Control Register (PCR).</li> <li>This input is 5 V tolerant.</li> </ul> |

| TXD         | Output          | Input                 | Serial Transmit Data<br>Transmits data from SCI transmit data register.                                                                                                                                                                                                                                                             |

| PE1         | Input or Output |                       | <b>Port E 1</b><br>The default configuration following reset is GPIO. When configured as PE1, signal direction is controlled through the SCI PRR. The signal can be configured as an SCI signal TXD through the SCI PCR.<br>This input is 5 V tolerant.                                                                             |

Table 1-14.

Serial Communication Interface (SCI)

als/Connections

| Signal Name | Туре            | State During<br>Reset | Signal Description                                                                                                                                                                                                                       |

|-------------|-----------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK        | Input/Output    | Input                 | Serial Clock<br>Provides the input or output clock used by the transmitter and/or the receiver.                                                                                                                                          |

| PE2         | Input or Output |                       | Port E 2<br>The default configuration following reset is GPIO. For PE2, signal direction is<br>controlled through the SCI PRR. The signal can be configured as an SCI<br>signal SCLK through the SCI PCR.<br>This input is 5 V tolerant. |

Table 1-14. Serial Communication Interface (SCI) (Continued)

### 1.11 Timers

The DSP56301 has three identical and independent timers. Each can use internal or external clocking, interrupt the DSP56301 after a specified number of events (clocks), or signal an external device after counting a specific number of internal events.

| Table 1-15. | Triple Timer Signals |

|-------------|----------------------|

|-------------|----------------------|

| Signal Name | Туре            | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIO0        | Input or Output | Input                 | Timer 0 Schmitt-Trigger Input/OutputAs an external event counter or in Measurement mode, TIO0 is input. In<br>Watchdog, Timer, or Pulse Modulation mode, TIO0 is output.The default mode after reset is GPIO input. This can be changed to output or<br>configured as a Timer Input/Output through the Timer 0 Control/Status<br>Register (TCSR0).This input is 5 V tolerant. |

| TIO1        | Input or Output | Input                 | Timer 1 Schmitt-Trigger Input/OutputAs an external event counter or in Measurement mode, TIO1 is input. InWatchdog, Timer, or Pulse Modulation mode, TIO1 is output.The default mode after reset is GPIO input. This can be changed to output orconfigured as a Timer Input/Output through the Timer 1 Control/StatusRegister (TCSR1).This input is 5 V tolerant.             |

| TIO2        | Input or Output | Input                 | Timer 2 Schmitt-Trigger Input/OutputAs an external event counter or in Measurement mode, TIO2 is input. InWatchdog, Timer, or Pulse Modulation mode, TIO2 is output.The default mode after reset is GPIO input. This can be changed to output orconfigured as a Timer Input/Output through the Timer 2 Control/StatusRegister (TCSR2).This input is 5 V tolerant.             |

| Characteristics                                                                                                                                              | Symbol                                                  | Min                           | т                                | ур                                  | Max                               | Unit           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|----------------------------------|-------------------------------------|-----------------------------------|----------------|

| Input high voltage<br>• D[0–23], BG, BB, TA<br>• MOD <sup>1</sup> /IRQ <sup>1</sup> , RESET, PINIT/NMI and all<br>JTAG/ESSI/SCI/Timer/HI32 pins              | V <sub>IH</sub><br>V <sub>IHP</sub>                     | 2.0<br>2.0                    | -                                | _                                   | V <sub>CC</sub><br>5.25           | V<br>V         |

| • EXTAL <sup>8</sup>                                                                                                                                         | V <sub>IHX</sub>                                        | $0.8 \times V_{CC}$           | -                                |                                     | V <sub>CC</sub>                   | V              |

| Input low voltage<br>• D[0–23], BG, BB, TA, MOD <sup>1</sup> /IRQ <sup>1</sup> , RESET, PINIT<br>• All JTAG/ESSI/SCI/Timer/HI32 pins<br>• EXTAL <sup>8</sup> | V <sub>IL</sub><br>V <sub>ILP</sub><br>V <sub>ILX</sub> | -0.3<br>-0.3<br>-0.3          | -                                | _                                   | $0.8 \\ 0.8 \\ 0.2 \times V_{CC}$ | V<br>V<br>V    |

| Input leakage current                                                                                                                                        | I <sub>IN</sub>                                         | -10                           | -                                | _                                   | 10                                | μA             |

| High impedance (off-state) input current (@ 2.4 V / 0.4 V)                                                                                                   | I <sub>TSI</sub>                                        | -10                           | -                                | _                                   | 10                                | μA             |

| Output high voltage<br>• TTL $(I_{OH} = -0.4 \text{ mA})^{5,7}$<br>• CMOS $(I_{OH} = -10 \mu \text{A})^5$                                                    | V <sub>OH</sub>                                         | 2.4<br>V <sub>CC</sub> – 0.01 | -                                | _                                   |                                   | V<br>V         |

| Output low voltage<br>• TTL ( $I_{OL}$ = 1.6 mA, open-drain pins $I_{OL}$ = 6.7 mA) <sup>5,7</sup><br>• CMOS ( $I_{OL}$ = 10 $\mu$ A) <sup>5</sup>           | V <sub>OL</sub>                                         |                               | -                                |                                     | 0.4<br>0.01                       | V<br>V         |

| Internal supply current <sup>2</sup> :<br>• In Normal mode<br>• In Wait mode <sup>3</sup><br>• In Stop mode <sup>4</sup>                                     | I <sub>CCI</sub><br>Iccw<br>Iccs                        |                               | <b>80 MHz</b><br>102<br>6<br>100 | <b>100 MHz</b><br>127<br>7.5<br>100 |                                   | mA<br>mA<br>μA |

| PLL supply current                                                                                                                                           |                                                         | -                             |                                  | 1                                   | 2.5                               | mA             |

| Input capacitance <sup>5</sup>                                                                                                                               | C <sub>IN</sub>                                         | _                             | -                                | _                                   | 10                                | pF             |

| Table 2-3. | DC Electrical Chara | acteristics <sup>6</sup> (Continued) | ) |

|------------|---------------------|--------------------------------------|---|

|------------|---------------------|--------------------------------------|---|

Notes: 1. Refers to MODA/IRQA, MODB/IRQB, MODC/IRQC, and MODD/IRQD pins.

2. Power Consumption Considerations on page 4-3 provides a formula to compute the estimated current requirements in Normal mode. To obtain these results, all inputs must be terminated (that is, not allowed to float). Measurements are based on synthetic intensive DSP benchmarks (see Appendix A). The power consumption numbers in this specification are 90 percent of the measured results of this benchmark. This reflects typical DSP applications. Typical internal supply current is measured with V<sub>CC</sub> = 3.0 V at T<sub>J</sub> = 100°C.

- 3. To obtain these results, all inputs must be terminated (that is, not allowed to float).

- 4. To obtain these results, all inputs that are not disconnected at Stop mode must be terminated (that is, not allowed to float). PLL and XTAL signals are disabled during Stop state.

- 5. Periodically sampled and not 100 percent tested.

- 6.  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ;  $T_{J} = -40^{\circ}\text{C}$  to +100 °C,  $C_{L} = 50 \text{ pF}$

- 7. This characteristic does not apply to XTAL and PCAP.

- Driving EXTAL to the low V<sub>IHX</sub> or the high V<sub>ILX</sub> value may cause additional power consumption (DC current). To minimize power consumption, the minimum V<sub>IHX</sub> should be no lower than

- $0.9 \times V_{CC}$  and the maximum  $V_{ILX}$  should be no higher than  $0.1 \times V_{CC}.$

80 MHz 100 MHz No. Characteristics Symbol Min Max Min Max Frequency of EXTAL (EXTAL Pin Frequency) Ef 1 0 80.0 MHz 100.0 MHz 0 The rise and fall time of this external clock should be 3 ns maximum. EXTAL input high<sup>1, 2</sup> 2 With PLL disabled (46.7%–53.3% duty cycle<sup>6</sup>) 4.67 ns 5.84 ns ETH ∞  $\infty$ With PLL enabled (42.5%-57.5% duty cycle<sup>6</sup>) 5.31 ns 4.25 ns 157.0 μs 157.0 μs EXTAL input low<sup>1, 2</sup> 3 With PLL disabled (46.7%-53.3% duty cycle<sup>6</sup>) ET 5.84 ns 4.67 ns  $\infty$  $\infty$ With PLL enabled (42.5%-57.5% duty cycle<sup>6</sup>) 5.31 ns 157.0 μs 4.25 ns 157.0 μs EXTAL cycle time<sup>2</sup> 4 With PLL disabled ET<sub>C</sub> 12.50 ns 10.00 ns  $\infty$  $\infty$ With PLL enabled 12.50 ns 273.1 µs 10.00 ns 273.1 µs 5 CLKOUT change from EXTAL fall with PLL disabled 4.3 ns 11.0 ns 4.3 ns 11.0 ns 6 a. CLKOUT rising edge from EXTAL rising edge with PLL enabled (MF 0.0 ns 1.8 ns 0.0 ns 1.8 ns = 1 or 2 or 4, PDF = 1, Ef > 15 MHz)<sup>3,5</sup> b. CLKOUT falling edge from EXTAL falling edge with PLL enabled (MF 0.0 ns 1.8 ns 0.0 ns 1.8 ns  $\leq$  4, PDF  $\neq$  1, Ef / PDF > 15 MHz)<sup>3,5</sup> 7 Instruction cycle time =  $I_{CYC} = T_C^4$ (see Table 2-4) (46.7%-53.3% duty cycle) With PLL disabled 25.0 ns 20.0 ns ICYC With PLL enabled 12.50 ns 8.53 µs 10.00 ns 8.53 μs Notes: 1. Measured at 50 percent of the input transition The maximum value for PLL enabled is given for minimum VCO frequency (see Table 2-6) and maximum MF. 2. 3. Periodically sampled and not 100 percent tested 4. The maximum value for PLL enabled is given for minimum VCO frequency and maximum DF. 5. The skew is not guaranteed for any other MF value.

### Table 2-5.Clock Operation

6. The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time required for correction operation, however, remains the same at lower operating frequencies; therefore, when a lower clock frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time requirements are met.

### 2.5.3 Phase Lock Loop (PLL) Characteristics

|                     |                     |                                                                          | 100 MHz                                               |                                                                                                                                         |  |

|---------------------|---------------------|--------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Min                 | Мах                 | Min                                                                      | Мах                                                   | Unit                                                                                                                                    |  |

| 30                  | 160                 | 30                                                                       | 200                                                   | MHz                                                                                                                                     |  |

| (MF × 580) –<br>100 | (MF × 780) –<br>140 | (MF × 580) – 100                                                         | (MF × 780) – 140                                      | pF<br>pF                                                                                                                                |  |

|                     | 30<br>(MF × 580) –  | 30         160           (MF × 580) -<br>100         (MF × 780) -<br>140 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | 30         160         30         200           (MF $\times$ 580) - 100         (MF $\times$ 780) - 140         (MF $\times$ 780) - 140 |  |

$(680 \times MF) - 120$ , for MF  $\leq$  4, or

$1100 \times MF$ , for MF > 4.

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80 MHz                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                             | 100 MHz                                                                                                                                                                                          |                                                                                                                                                                                                                |                                                                                                    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| No.   | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Expression                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min                                                                                                                                                                                                                                                                                   | Max                                                                                                                                                                                                                                         | Min                                                                                                                                                                                              | Max                                                                                                                                                                                                            | Unit                                                                                               |

| 28    | DMA Request Rate <ul> <li>Data read from HI32, ESSI, SCI</li> <li>Data write to HI32, ESSI, SCI</li> <li><u>Timer</u></li> <li><u>IRQ</u>, NMI (edge trigger)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $6 \times T_{C}$ $7 \times T_{C}$ $2 \times T_{C}$ $3 \times T_{C}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                       | 75.0<br>87.5<br>25.0<br>37.5                                                                                                                                                                                                                |                                                                                                                                                                                                  | 60.0<br>70.0<br>20.0<br>30.0                                                                                                                                                                                   | ns<br>ns<br>ns<br>ns                                                                               |

| 29    | Delay from IRQA, IRQB, IRQC, IRQD, NMI assertion to external memory (DMA source) access address out valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $4.25 \times T_{C} + 2.0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55.1                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                           | 44.5                                                                                                                                                                                             | -                                                                                                                                                                                                              | ns                                                                                                 |

| Notes | <ol> <li>When using fast interrupts and IRQA, IRQB, IRQC prevent multiple interrupt service. To avoid these t when using fast interrupts. Long interrupts are rec</li> <li>This timing depends on several settings:         <ul> <li>For PLL disable, using internal oscillator (PLL CC Bit 17 = 0), a stabilization delay is required to assust Stop delay (Operating Mode Register Bit 6 = 0) protit is not recommended, and these specifications dd</li> <li>For PLL disable, using internal oscillator (PCTL E stabilization delay is required and recovery is mini</li> <li>For PLL disable, using external clock (PCTL Bit 17 error PLL disable, using external clock (PCTL Bit PCTL Bit 17 and Operating Mode Register Bit 6 se</li> <li>For PLL enable, if PCTL Bit 17 is 0, the PLL is strate proceedure duration, PLL Lock Cycle parallel with the stop delay counter, and stop record completes count or PLL lock procedure completion</li> <li>PLC value for PLL disable is 0.</li> <li>The maximum value for ET<sub>C</sub> is 4096 (maximum 14096/66 MHz = 62 µs). During the stabilization pervary as well.</li> </ul> </li> <li>Periodically sampled and not 100 percent tested.</li> <li>Value depends on clock source:         <ul> <li>For an internal oscillator, RESET duration is mear reflects the crystal oscillator stabilization is mear reflects the crystal oscillator stabilization time after and other components connected to the oscillator</li> <li>When the V<sub>CC</sub> is valid, but the other "required RE device circuitry is in an uninitialized state that can minimize this state to the shortest possible duration</li> <li>MCC = 3.3 V ± 0.3 V; T<sub>J</sub> = -40°C to +100°C, C<sub>L</sub> = §</li> <li>WS = number of wait states (measured in clock cy</li> <li>Use the expression to compute a maximum value.</li> </ul> </li> </ol> | iming restrictions, the deassel<br>ommended when using Level-<br>ontrol Register (PCTL) Bit 16 =<br>ure that the oscillator is stable<br>ovides the proper delay. While<br>o not guarantee timings for that<br>Bit 16 = 0) and oscillator enable<br>mal (Operating Mode Register<br>16 = 1), no stabilization delay is<br>ettings.<br>nutdown during Stop. Recover<br>s (PLC), may be in the range of<br>very ends when the last of the<br>n.<br>MF) divided by the desired inter<br>riod, T <sub>C</sub> , T <sub>H</sub> , and T <sub>L</sub> is not con<br>this measured while RESET is<br>asured while RESET is asserter<br>r power-up. This number is aff<br>and reflects worst case condit<br>ESET duration" conditions (as<br>result in significant power con<br>n.<br>50 pF.<br>rcles, number of T <sub>C</sub> ). | rted Edge-<br>sensitive r<br>= 0) and os<br>before pro<br>Operating<br>at case.<br>ed during f<br>r Bit 6 setti<br>s required<br>ing from S<br>of 0 to 100<br>se two even<br>ernal frequ<br>stant, and<br>asserted, N<br>ed and V <sub>CC</sub><br>ected both<br>ions.<br>specified a | triggered n<br>node.<br>cillator dis<br>grams are<br>Mode Reg<br>Stop (PCT<br>ng is ignor<br>and recov<br>top require<br>0 cycles. T<br>ents occurs<br>ency (that<br>their width<br>/ <sub>CC</sub> is valid.<br>to y the spe<br>above) hav | abled dur<br>executed<br>jister Bit (<br>L Bit 17=<br>ed).<br>ery time i<br>es the PL<br>his proce<br>s. The stc<br>is, for 66<br>may var<br>d, and the<br>he speci<br>ecification<br>re not bee | ecommend<br>ring Stop (<br>d. Resettir<br>6 = 1 can l<br>a), no<br>is defined<br>L to get lo<br>edure occion<br>p delay c<br>MHz it is<br>y, so timin<br>e EXTAL in<br>fied timing<br>ns of the c<br>en yet me | ded<br>(PCTL<br>ng the<br>be set,<br>by the<br>cked.<br>urs in<br>ounter<br>ng may<br>nput is<br>g |

| Table 2-7. | Reset, Stop, | Mode Select, | and Interrupt | Timing <sup>6</sup> | (Continued) |

|------------|--------------|--------------|---------------|---------------------|-------------|

|------------|--------------|--------------|---------------|---------------------|-------------|

DSP56301 Technical Data, Rev. 10

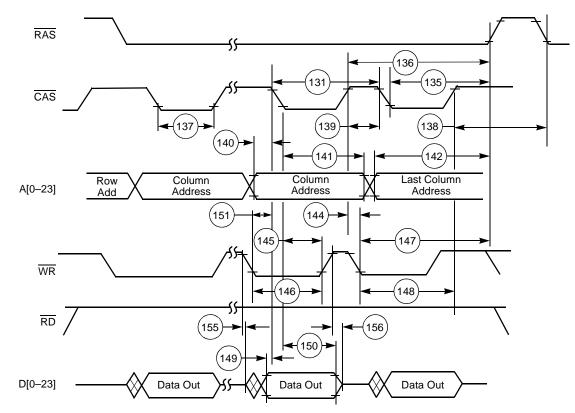

Figure 2-15. DRAM Page Mode Write Accesses

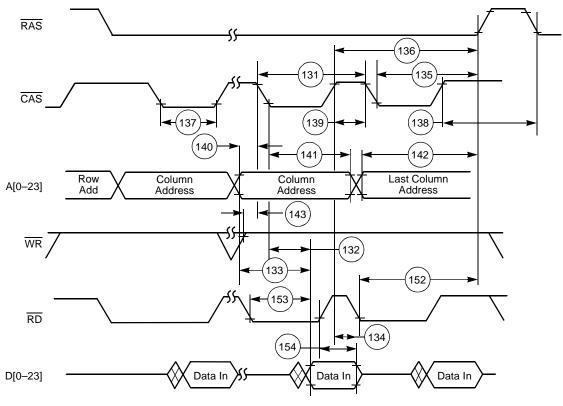

Figure 2-16. DRAM Page Mode Read Accesses

| N -                                                                                                                                                                | Characteristics <sup>3</sup>                  |                  | <b>F</b>                                                                                                               | 80 MHz |       | 100 MHz |          | 11       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|--------|-------|---------|----------|----------|--|

| No.                                                                                                                                                                |                                               | Symbol           | Expression                                                                                                             | Min    | Max   | Min     | Мах      | Unit     |  |

| 187                                                                                                                                                                | RAS assertion to data not valid (write)       | t <sub>DHR</sub> | $7.75 	imes T_C - 4.0$                                                                                                 | 92.9   |       | 73.5    | _        | ns       |  |

| 188                                                                                                                                                                | WR assertion to CAS assertion                 | t <sub>WCS</sub> | $6.5	imes T_C - 4.3$                                                                                                   | 77.0   | _     | 60.7    |          | ns       |  |

| 189                                                                                                                                                                | CAS assertion to RAS assertion (refresh)      | t <sub>CSR</sub> | $1.5 	imes T_C - 4.0$                                                                                                  | 14.8   | _     | 11.0    | _        | ns       |  |

| 190                                                                                                                                                                | RAS deassertion to CAS assertion (refresh)    | t <sub>RPC</sub> | $2.75\times T_C-4.0$                                                                                                   | 30.4   | _     | 23.5    | _        | ns       |  |

| 191                                                                                                                                                                | RD assertion to RAS deassertion               | t <sub>ROH</sub> | $11.5\times T_C-4.0$                                                                                                   | 139.8  | _     | 111.0   |          | ns       |  |

| 192                                                                                                                                                                | RD assertion to data valid                    | t <sub>GA</sub>  | $\begin{array}{c} \textbf{80 MHz:} \\ 10 \times T_{C} - 6.5 \\ \textbf{100 MHz:} \\ 10 \times T_{C} - 7.0 \end{array}$ | _      | 118.5 | _       | <br>93.0 | ns<br>ns |  |

| 193                                                                                                                                                                | RD deassertion to data not valid <sup>3</sup> | t <sub>GZ</sub>  |                                                                                                                        | 0.0    | _     | 0.0     | —        | ns       |  |

| 194                                                                                                                                                                | 4 WR assertion to data active                 |                  | $0.75 	imes T_C - 1.5$                                                                                                 | 9.1    |       | 6.0     | _        | ns       |  |

| 195                                                                                                                                                                | 195 WR deassertion to data high impedance     |                  | $0.25 	imes T_{C}$                                                                                                     | _      | 3.1   | —       | 2.5      | ns       |  |

| <ul> <li>Notes: 1. The number of wait states for an out-of-page access is specified in the DCR.</li> <li>2. The refresh period is specified in the DCR.</li> </ul> |                                               |                  |                                                                                                                        |        |       |         |          |          |  |

DRAM Out-of-Page and Refresh Timings, Eleven Wait States<sup>1, 2</sup> (Continued) Table 2-13.

$\overline{RD}$  deassertion always occurs after CAS deassertion; therefore, the restricted timing is t<sub>OFF</sub> and not t<sub>GZ</sub>. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for read cycles. 3.

4.

| Table 2-14. | DRAM Out-of-Page and Refresh Timings | , Fifteen Wait States <sup>1, 2</sup> |

|-------------|--------------------------------------|---------------------------------------|

|-------------|--------------------------------------|---------------------------------------|

| No. | Characteristics <sup>3</sup>                       | Symbol           | Funnancian                                                                                    | 80 MHz |      | 100 MHz |           | Unit     |

|-----|----------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|--------|------|---------|-----------|----------|

| NO. |                                                    | Symbol           | Expression                                                                                    | Min    | Max  | Min     | Мах       | Unit     |

| 157 | Random read or write cycle time                    | t <sub>RC</sub>  | $16 	imes T_C$                                                                                | 200.0  | _    | 160.0   | —         | ns       |

| 158 | RAS assertion to data valid (read)                 | t <sub>RAC</sub> | <b>80 MHz</b> :<br>$8.25 \times T_{C} - 6.5$<br><b>100 MHz</b> :<br>$8.25 \times T_{C} - 5.7$ | _      | 96.6 | _       | —<br>76.8 | ns       |

| 159 | CAS assertion to data valid (read)                 | <sup>t</sup> CAC | <b>80 MHz</b> :<br>4.75 × T <sub>C</sub> – 6.5<br><b>100 MHz</b> :                            |        | 52.9 | _       | _         | ns<br>ns |

|     |                                                    |                  | $4.75 	imes T_C - 5.7$                                                                        | _      |      | _       | 41.8      | ns       |

| 160 | Column address valid to data valid (read)          | t <sub>AA</sub>  | 80 MHz:<br>5.5 × T <sub>C</sub> − 6.5<br>100 MHz:                                             | _      | 62.3 | _       | _         | ns       |

|     |                                                    |                  | $5.5	imes T_C - 5.7$                                                                          | _      | -    | -       | 49.3      | ns       |

| 161 | CAS deassertion to data not valid (read hold time) | t <sub>OFF</sub> | 0.0                                                                                           | 0.0    | —    | 0.0     | —         | ns       |

| 162 | RAS deassertion to RAS assertion                   | t <sub>RP</sub>  | $6.25 	imes T_C - 4.0$                                                                        | 74.1   | _    | 58.5    | _         | ns       |

| 163 | RAS assertion pulse width                          | t <sub>RAS</sub> | $9.75\times T_C-4.0$                                                                          | 117.9  | _    | 93.5    |           | ns       |

| 164 | CAS assertion to RAS deassertion                   | t <sub>RSH</sub> | $6.25\times T_C-4.0$                                                                          | 74.1   | _    | 58.5    |           | ns       |

| 165 | RAS assertion to CAS deassertion                   | t <sub>CSH</sub> | $8.25 	imes T_C - 4.0$                                                                        | 99.1   | _    | 78.5    | _         | ns       |

| 166 | CAS assertion pulse width                          | t <sub>CAS</sub> | $4.75\times T_C-4.0$                                                                          | 55.4   | _    | 43.5    |           | ns       |

| 167 | RAS assertion to CAS assertion                     | t <sub>RCD</sub> | $3.5 	imes T_C \pm 2$                                                                         | 41.8   | 45.8 | 33.0    | 37.0      | ns       |

| 168 | RAS assertion to column address valid              | t <sub>RAD</sub> | $2.75\times T_{C}\pm 2.0$                                                                     | 32.4   | 36.4 | 25.5    | 29.5      | ns       |

| 169 | CAS deassertion to RAS assertion                   | t <sub>CRP</sub> | $7.75\times T_C-4.0$                                                                          | 92.9   | _    | 73.5    | —         | ns       |

#### **AC Electrical Characteristics**

| No. | Characteristics <sup>3</sup>                                | C                |                                                                               |       | MHz   | 100   | MHz        |          |

|-----|-------------------------------------------------------------|------------------|-------------------------------------------------------------------------------|-------|-------|-------|------------|----------|

|     |                                                             | Symbol           | Expression                                                                    | Min   | Мах   | Min   | Max        | Uni      |

| 170 | CAS deassertion pulse width                                 | t <sub>CP</sub>  | $6.25 	imes T_{C} - 6.0$                                                      | 74.1  | _     | 56.5  | _          | ns       |

| 171 | Row address valid to RAS assertion                          | t <sub>ASR</sub> | $6.25 	imes T_C - 4.0$                                                        | 74.1  | _     | 58.5  | —          | ns       |

| 172 | RAS assertion to row address not valid                      | t <sub>RAH</sub> | $2.75	imes T_{C}-4.0$                                                         | 30.4  | _     | 23.5  | —          | ns       |

| 173 | Column address valid to CAS assertion                       | t <sub>ASC</sub> | $0.75 	imes T_C - 4.0$                                                        | 5.4   | _     | 3.5   | _          | ns       |

| 174 | CAS assertion to column address not valid                   | t <sub>CAH</sub> | $6.25 	imes T_C - 4.0$                                                        | 74.1  | _     | 58.5  | _          | ns       |

| 175 | RAS assertion to column address not valid                   | t <sub>AR</sub>  | $9.75 	imes T_{C} - 4.0$                                                      | 117.9 |       | 93.5  | _          | ns       |

| 176 | Column address valid to RAS deassertion                     | t <sub>RAL</sub> | $7 \times T_C - 4.0$                                                          | 83.5  |       | 66.0  | _          | ns       |

| 177 | WR deassertion to CAS assertion                             | t <sub>RCS</sub> | $5 	imes T_{C} - 3.8$                                                         | 58.7  | _     | 46.2  | _          | ns       |

| 178 | $\overline{CAS}$ deassertion to $\overline{WR}^4$ assertion | t <sub>RCH</sub> | 1.75 × T <sub>C</sub> – 3.7                                                   | 18.2  | _     | 13.8  | _          | ns       |

| 179 | $\overline{RAS}$ deassertion to $\overline{WR}^4$ assertion | t <sub>RRH</sub> | <b>80 MHz</b> :<br>0.25 × T <sub>C</sub> – 2.6<br><b>100 MHz</b> :            | 0.5   | _     | _     | _          | ns       |

|     |                                                             |                  | $0.25 	imes T_C - 2.0$                                                        |       | _     | 0.5   |            | ns       |

| 180 | CAS assertion to WR deassertion                             | t <sub>WCH</sub> | $6 	imes T_C - 4.2$                                                           | 70.8  |       | 55.8  |            | ns       |

| 181 | RAS assertion to WR deassertion                             | t <sub>WCR</sub> | $9.5 	imes T_C - 4.2$                                                         | 114.6 |       | 90.8  | —          | ns       |

| 182 | WR assertion pulse width                                    | t <sub>WP</sub>  | $15.5 	imes T_{C} - 4.5$                                                      | 189.3 | —     | 150.5 |            | ns       |

| 183 | WR assertion to RAS deassertion                             | t <sub>RWL</sub> | $15.75 	imes T_{C} - 4.3$                                                     | 192.6 |       | 153.2 |            | ns       |

| 184 | WR assertion to CAS deassertion                             | t <sub>CWL</sub> | $14.25 	imes T_{C} - 4.3$                                                     | 173.8 |       | 138.2 | —          | ns       |

| 185 | Data valid to CAS assertion (write)                         | t <sub>DS</sub>  | $8.75 \times T_C - 4.0$                                                       | 105.4 | _     | 83.5  | —          | ns       |

| 186 | CAS assertion to data not valid (write)                     | t <sub>DH</sub>  | $6.25 	imes T_C - 4.0$                                                        | 74.1  | _     | 58.5  | _          | ns       |

| 187 | RAS assertion to data not valid (write)                     | t <sub>DHR</sub> | $9.75	imes T_C - 4.0$                                                         | 117.9 |       | 93.5  | —          | ns       |

| 188 | $\overline{WR}$ assertion to $\overline{CAS}$ assertion     | t <sub>WCS</sub> | $9.5	imes T_C - 4.3$                                                          | 114.5 | —     | 90.7  | —          | ns       |

| 189 | CAS assertion to RAS assertion (refresh)                    | t <sub>CSR</sub> | $1.5 	imes T_C - 4.0$                                                         | 14.8  | _     | 11.0  | -          | ns       |

| 190 | RAS deassertion to CAS assertion (refresh)                  | t <sub>RPC</sub> | $4.75 	imes T_C - 4.0$                                                        | 55.4  | _     | 43.5  | -          | ns       |

| 191 | RD assertion to RAS deassertion                             | t <sub>ROH</sub> | $15.5 	imes T_{C} - 4.0$                                                      | 189.8 | _     | 151.0 | —          | ns       |

| 192 | RD assertion to data valid                                  | t <sub>GA</sub>  | 80 MHz:<br>14 × T <sub>C</sub> − 6.5<br>100 MHz:<br>14 × T <sub>C</sub> − 5.7 | _     | 168.5 | _     | —<br>134.3 | ns<br>ns |

| 193 | RD deassertion to data not valid <sup>3</sup>               | t <sub>GZ</sub>  | 0                                                                             | 0.0   |       | 0.0   | _          | ns       |

| 194 | WR assertion to data active                                 | -62              | 0.75 × T <sub>C</sub> – 1.5                                                   | 9.1   | _     | 6.0   | _          | ns       |

| 195 | WR deassertion to data high impedance                       |                  | 0.25 × T <sub>C</sub>                                                         |       | 3.1   |       | 2.5        | ns       |

| Table 2-14. | DRAM Out-of-Page and Refresh Timings, Fifteen Wait States <sup>1</sup> | <sup>, 2</sup> (Continued) |

|-------------|------------------------------------------------------------------------|----------------------------|

|-------------|------------------------------------------------------------------------|----------------------------|

2.

The refresh period is specified in the DCR. RD deassertion always occurs after CAS deassertion; therefore, the restricted timing is  $t_{OFF}$  and not  $t_{GZ}$ . Either  $t_{RCH}$  or  $t_{RRH}$  must be satisfied for read cycles. 3.

4.

### 2.5.5.3 Synchronous Timings (SRAM)

| Table 2-15. External Bus Synchronous Timings (SRAM Ac | ccess) <sup>3</sup> |

|-------------------------------------------------------|---------------------|

|-------------------------------------------------------|---------------------|

| Na  | Characteristics                                           | Expression <sup>1,2</sup>                                                     | 80   | MHz  | 100 | MHz      | 11       |

|-----|-----------------------------------------------------------|-------------------------------------------------------------------------------|------|------|-----|----------|----------|

| No. |                                                           | Expression ",*                                                                | Min  | Max  | Min | Max      | Unit     |

| 196 | CLKOUT high to BS assertion                               | $0.25 	imes T_{C}$ +5.2/–0.5                                                  | 2.6  | 8.3  | 2.0 | 7.7      | ns       |

| 197 | CLKOUT high to $\overline{BS}$ deassertion                | 0.75 × T <sub>C</sub> +4.2/–1.0                                               | 8.4  | 13.6 | 6.5 | 11.7     | ns       |

| 198 | CLKOUT high to address, and AA valid <sup>4</sup>         | $0.25 \times T_{C} + 2.5$                                                     | _    | 5.6  | _   | 5.0      | ns       |

| 199 | CLKOUT high to address, and AA invalid <sup>4</sup>       | $0.25 	imes T_{C} - 0.7$                                                      | 2.4  | _    | 1.8 | _        | ns       |

| 200 | TA valid to CLKOUT high (setup time)                      |                                                                               | 5.8  | —    | 4.0 | _        | ns       |

| 201 | CLKOUT high to $\overline{TA}$ invalid (hold time)        |                                                                               | 0.0  | —    | 0.0 | _        | ns       |

| 202 | CLKOUT high to data out active                            | $0.25 	imes T_{C}$                                                            | 3.1  | _    | 2.5 | _        | ns       |

| 203 | CLKOUT high to data out valid                             | 80 MHz:<br>$0.25 \times T_{C} + 4.5$<br>100 MHz:<br>$0.25 \times T_{C} + 4.0$ | _    | 7.6  | _   | —<br>6.5 | ns<br>ns |

| 204 | CLKOUT high to data out invalid                           | 0.25 × T <sub>C</sub>                                                         | 3.1  | _    | 2.5 | _        | ns       |

| 205 | CLKOUT high to data out high impedance                    | 80 MHz:<br>0.25 × T <sub>C</sub> + 0.5<br>100 MHz:<br>0.25 × T <sub>C</sub>   | _    | 3.6  | _   | <br>2.5  | ns<br>ns |

| 206 | Data in valid to CLKOUT high (setup)                      |                                                                               | 5.0  | _    | 4.0 | _        | ns       |

| 207 | CLKOUT high to data in invalid (hold)                     |                                                                               | 0.0  | _    | 0.0 | _        | ns       |

| 208 | CLKOUT high to RD assertion                               | maximum:<br>0.75 × T <sub>C</sub> + 2.5                                       | 10.4 | 11.9 | 6.7 | 10.0     | ns<br>ns |

| 209 | CLKOUT high to RD deassertion                             |                                                                               | 0.0  | 4.5  | 0.0 | 4.0      | ns       |

| 210 | CLKOUT high to $\overline{\rm WR}$ assertion <sup>2</sup> | $0.5 \times T_{C} + 4.3$<br>[WS = 1 or WS ≥ 4]                                | 7.6  | 10.6 | 4.5 | 9.3      | ns       |

|     |                                                           | $[2 \le WS \le 3]$                                                            | 1.3  | 4.8  | 0.0 | 4.3      | ns       |

| 211 | CLKOUT high to WR deassertion                             |                                                                               | 0.0  | 4.3  | 0.0 | 3.8      | ns       |

External bus synchronous limitings should be used only for reference to the Clock and *hot* for relative timings.

T198 and T199 are valid for Address Trace mode if the ATE bit in the Operating Mode Register is set. Use the status of BR (See T212) to determine whether the access referenced by A[0–23] is internal or external in this mode.

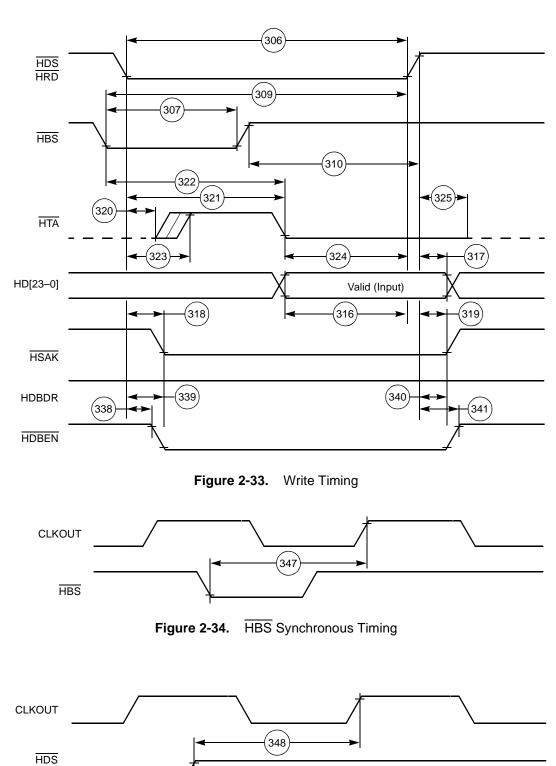

Figure 2-35. Data Strobe Synchronous Timing

DSP56301 Technical Data, Rev. 10

HRD HWR

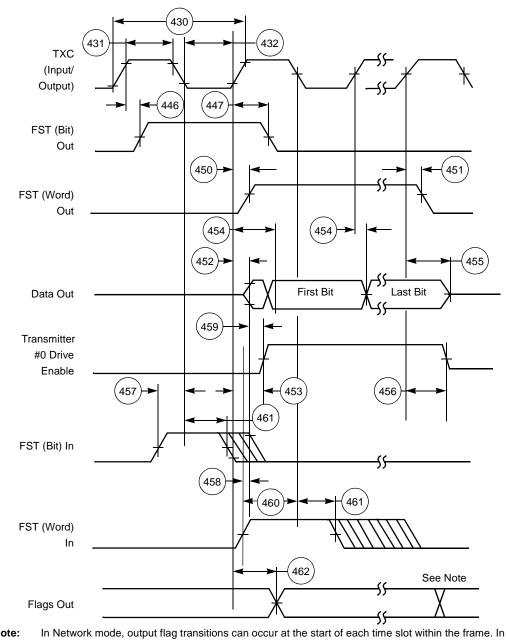

Figure 2-40. ESSI Transmitter Timing

## Packaging

This section provides information on the available packages for the DSP56301, including diagrams of the package pinouts and tables showing how the signals discussed in **Section 1** are allocated for each package. The DSP56301 is available in two package types:

- 208-pin Thin Quad Flat Pack (TQFP)

- 252-pin Molded Array Process-Ball Grid Array (MAP-BGA)

- **Note:** Both packages are available in lead-bearing and lead-free versions. Switching a design from a lead-bearing package device to a lead-free package device may require a change in the board manufacturing process. The lead-free package requires a higher solder flow temperature than the lead-bearing device. Refer to *Lead-Free BGA Solder Joint Assembly Evaluation* (EB635) for manufacturing considerations when incorporating lead-free package devices into a design.

aging

| Table 3-2. | DSP56301 TQFP Signal  | Identification by Name | (Continued) |

|------------|-----------------------|------------------------|-------------|

|            | Der ober i der orgnar | achunouton by Name     | (Continued) |

| Signal Name      | Pin<br>No. | Signal Name | Pin<br>No. | Signal Name | Pin<br>No. |

|------------------|------------|-------------|------------|-------------|------------|

| GND <sub>N</sub> | 19         | HAD14       | 152        | HAEN        | 149        |

| GND <sub>P</sub> | 13         | HAD15       | 151        | HBE0        | 163        |

| GND <sub>Q</sub> | 27         | HAD16       | 127        | HBE1        | 150        |

| GND <sub>Q</sub> | 78         | HAD17       | 126        | HBE2        | 128        |

| GND <sub>Q</sub> | 132        | HAD18       | 125        | HBE3        | 117        |

| GND <sub>Q</sub> | 183        | HAD19       | 124        | HBS         | 140        |

| GND <sub>Q</sub> | 183        | HAD2        | 171        | HC0         | 163        |

| GND <sub>S</sub> | 180        | HAD20       | 121        | HC1         | 150        |

| GND <sub>S</sub> | 194        | HAD21       | 120        | HC2         | 128        |

| HA0              | 163        | HAD22       | 119        | HC3         | 117        |

| HA1              | 150        | HAD23       | 118        | HCLK        | 148        |

| HA10             | 164        | HAD24       | 116        | HD0         | 162        |

| HA2              | 128        | HAD25       | 115        | HD1         | 161        |

| HA3              | 173        | HAD26       | 114        | HD10        | 125        |

| HA4              | 172        | HAD27       | 113        | HD11        | 124        |

| HA5              | 171        | HAD28       | 110        | HD12        | 121        |

| HA6              | 170        | HAD29       | 109        | HD13        | 120        |

| HA7              | 167        | HAD3        | 170        | HD14        | 119        |

| HA8              | 166        | HAD30       | 108        | HD15        | 118        |

| HA9              | 165        | HAD31       | 107        | HD16        | 116        |

| HAD0             | 173        | HAD4        | 167        | HD17        | 115        |

| HAD1             | 172        | HAD5        | 166        | HD18        | 114        |

| HAD10            | 160        | HAD6        | 165        | HD19        | 113        |

| HAD11            | 159        | HAD7        | 164        | HD2         | 160        |

| HAD12            | 154        | HAD8        | 162        | HD20        | 110        |

| HAD13            | 153        | HAD9        | 161        | HD21        | 109        |

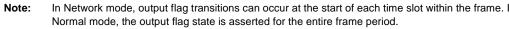

## 3.3 MAP-BGA Package Description

aging

Top and bottom views of the MAP-BGA package are shown in Figure 3-4 and Figure 3-5 with their pin-outs.

Figure 3-4. DSP56301 Molded Array Process-Ball Grid Array (MAP-BGA), Top View

aging

| Table 3-4. DS | SP56301 MAP-BGA | Signal Identific | ation by Name |

|---------------|-----------------|------------------|---------------|

|---------------|-----------------|------------------|---------------|

| Signal Name | Pin<br>No. | Signal Name | Pin<br>No. | Signal Name | Pin<br>No. |

|-------------|------------|-------------|------------|-------------|------------|

| A0          | T10        | AA2         | R7         | D22         | E15        |

| A1          | N9         | AA3         | P8         | D23         | D16        |

| A10         | T13        | BB          | R6         | D3          | K14        |

| A11         | R13        | BCLK        | Т3         | D4          | K16        |

| A12         | P12        | BCLK        | R9         | D5          | J14        |

| A13         | T14        | BG          | P7         | D6          | K15        |

| A14         | R14        | BL          | N4         | D7          | J16        |