Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status     Active       Core Processor     ARM® Cortex®-M0       Core Size     32-Bit Single-Core       Speed     48MHz       Connectivity     HDMI-CEC, I²C, IrDA, LINbus, SPI, UART/USART |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Core Size32-Bit Single-CoreSpeed48MHz                                                                                                                                                               |  |

| Speed 48MHz                                                                                                                                                                                         |  |

|                                                                                                                                                                                                     |  |

| Connectivity HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                                                                                                              |  |

|                                                                                                                                                                                                     |  |

| Peripherals DMA, I <sup>2</sup> S, POR, PWM, WDT                                                                                                                                                    |  |

| Number of I/O 38                                                                                                                                                                                    |  |

| Program Memory Size 64KB (64K x 8)                                                                                                                                                                  |  |

| Program Memory Type FLASH                                                                                                                                                                           |  |

| EEPROM Size -                                                                                                                                                                                       |  |

| RAM Size 8K x 8                                                                                                                                                                                     |  |

| Voltage - Supply (Vcc/Vdd)1.65V ~ 3.6V                                                                                                                                                              |  |

| Data ConvertersA/D 13x12b; D/A 1x12b                                                                                                                                                                |  |

| Oscillator Type Internal                                                                                                                                                                            |  |

| Operating Temperature -40°C ~ 85°C (TA)                                                                                                                                                             |  |

| Mounting Type Surface Mount                                                                                                                                                                         |  |

| Package / Case     48-UFQFN Exposed Pad                                                                                                                                                             |  |

| Supplier Device Package48-UFQFPN (7x7)                                                                                                                                                              |  |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f058c8u6                                                                                                                  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |      | 6.3.15    | 12-bit ADC characteristics                  |

|---|------|-----------|---------------------------------------------|

|   |      | 6.3.16    | DAC electrical specifications74             |

|   |      | 6.3.17    | Comparator characteristics                  |

|   |      | 6.3.18    | Temperature sensor characteristics          |

|   |      | 6.3.19    | V <sub>BAT</sub> monitoring characteristics |

|   |      | 6.3.20    | Timer characteristics                       |

|   |      | 6.3.21    | Communication interfaces                    |

| 7 | Pack | age info  | ormation                                    |

|   | 7.1  | UFBGA     | A64 package information                     |

|   | 7.2  | LQFP6     | 4 package information                       |

|   | 7.3  | UFQFF     | PN48 package information                    |

|   | 7.4  | WLCS      | P36 package information                     |

|   | 7.5  | Therma    | al characteristics                          |

|   |      | 7.5.1     | Reference document                          |

|   |      | 7.5.2     | Selecting the product temperature range     |

| 8 | Orde | ering inf | ormation                                    |

| 9 | Revi | sion his  | tory                                        |

## 3.14.2 General-purpose timers (TIM2, 3, 14, 15, 16, 17)

There are six synchronizable general-purpose timers embedded in the STM32F058C8/R8/T8 devices (see *Table 6* for differences). Each general-purpose timer can be used to generate PWM outputs, or as simple time base.

### TIM2, TIM3

STM32F058C8/R8/T8 devices feature two synchronizable 4-channel general-purpose timers. TIM2 is based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. TIM3 is based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They feature 4 independent channels each for input capture/output compare, PWM or one-pulse mode output. This gives up to 12 input captures/output compares/PWMs on the largest packages.

The TIM2 and TIM3 general-purpose timers can work together or with the TIM1 advancedcontrol timer via the Timer Link feature for synchronization or event chaining.

TIM2 and TIM3 both have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

Their counters can be frozen in debug mode.

#### TIM14

This timer is based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM14 features one single channel for input capture/output compare, PWM or one-pulse mode output.

Its counter can be frozen in debug mode.

#### TIM15, TIM16 and TIM17

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.14.3 Basic timer TIM6

This timer is mainly used for DAC trigger generation. It can also be used as a generic 16-bit time base.

## 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop mode. It can be used

either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

## 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

## 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset.

The RTC is an independent BCD timer/counter. Its main features are the following:

- calendar with subseconds, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- automatic correction for 28, 29 (leap year), 30, and 31 day of the month

- programmable alarm with wake up from Stop mode capability

- on-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize the RTC with a master clock

- digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- two anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop mode on tamper event detection

- timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop mode on timestamp event detection

- reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s) and Fast mode (up to 400 kbit/s) and, I2C1 also supports Fast Mode Plus (up to 1 Mbit/s) with extra output drive.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |  |  |  |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |  |  |  |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |  |  |  |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |  |  |  |

Table 7. Comparison of I<sup>2</sup>C analog and digital filters

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to Table 8 for the differences between I2C1 and I2C2.

| Table 8. STM32F058C8/R8/T8 I <sup>2</sup> C | implementation |

|---------------------------------------------|----------------|

|---------------------------------------------|----------------|

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | Х    | Х    |

| Standard mode (up to 100 kbit/s)                             | X    | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with extra output drive I/Os | Х    | -    |

| Independent clock                                            | X    | -    |

| Pin    | num     | ber             |         |                                      |          | e             |       | Pin functi                                                | ons                  |  |  |

|--------|---------|-----------------|---------|--------------------------------------|----------|---------------|-------|-----------------------------------------------------------|----------------------|--|--|

| LQFP64 | UFBGA64 | <b>UFQFPN48</b> | WLCSP36 | Pin name<br>(function upon<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                       | Additional functions |  |  |

| 56     | A4      | 40              | A3      | PB4                                  | I/O      | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TSC_G5_IO2,<br>EVENTOUT | -                    |  |  |

| 57     | C4      | 41              | E6      | PB5                                  | I/O      | FT            | -     | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA, TIM16_BKIN,<br>TIM3_CH2 | -                    |  |  |

| 58     | D3      | 42              | C4      | PB6                                  | I/O      | FTf           | -     | I2C1_SCL, USART1_TX,<br>TIM16_CH1N, TSC_G5_IO3            | -                    |  |  |

| 59     | C3      | 43              | A4      | PB7                                  | I/O      | FTf           | -     | I2C1_SDA, USART1_RX,<br>TIM17_CH1N, TSC_G5_IO4            | -                    |  |  |

| 60     | B4      | 44              | B4      | BOOT0                                | Ι        | В             | -     | Boot memory s                                             | election             |  |  |

| 61     | В3      | 45              | -       | PB8                                  | I/O      | FTf           | (5)   | I2C1_SCL, CEC,<br>TIM16_CH1, TSC_SYNC                     | -                    |  |  |

| 62     | A3      | 46              | -       | PB9                                  | I/O      | FTf           | (5)   | I2C1_SDA, IR_OUT,<br>TIM17_CH1, EVENTOUT                  | -                    |  |  |

| 63     | D5      | 47              | D6      | VSS                                  | S        | -             | -     | Ground                                                    |                      |  |  |

| 64     | E5      | 48              | A5      | VDD                                  | S        | -             | -     | Digital power                                             | supply               |  |  |

Table 12. Pin definitions (continued)

PC13, PC14 and PC15 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF. 1.

- These GPIOs must not be used as current sources (e.g. to drive an LED).

2. After the first RTC domain power-up, PC13, PC14 and PC15 operate as GPIOs. Their function then depends on the content of the RTC registers which are not reset by the main reset. For details on how to manage these GPIOs, refer to the RTC domain and RTC register descriptions in the reference manual.

3. Distinct VSSA pin is not available on WLCSP36 package. The pin number corresponds to the VSS pin to which VSSA pad of the silicon die is connected.

4. This pin is powered by  $V_{DDA}$

5. On the WLCSP36 package, PB8, PB9, PB10, PB11, PB12, PB13, PB14 and PB15 must be set to defined levels by software, as their corresponding pads on the silicon die are left unconnected. Apply the same recommendations as for unconnected pins.

6. After reset, these pins are configured as SWDIO and SWCLK alternate functions, and the internal pull-up on the SWDIO pin and the internal pull-down on the SWCLK pin are activated.

| Table 14. Alternate functions selected through GPIOB_AFR registers for port B |                     |           |            |            |  |  |  |  |  |

|-------------------------------------------------------------------------------|---------------------|-----------|------------|------------|--|--|--|--|--|

| Pin name                                                                      | AF0                 | AF1       | AF2        | AF3        |  |  |  |  |  |

| PB0                                                                           | EVENTOUT            | TIM3_CH3  | TIM1_CH2N  | TSC_G3_IO2 |  |  |  |  |  |

| PB1                                                                           | TIM14_CH1           | TIM3_CH4  | TIM1_CH3N  | TSC_G3_IO3 |  |  |  |  |  |

| PB3                                                                           | SPI1_SCK, I2S1_CK   | EVENTOUT  | TIM2_CH2   | TSC_G5_IO1 |  |  |  |  |  |

| PB4                                                                           | SPI1_MISO, I2S1_MCK | TIM3_CH1  | EVENTOUT   | TSC_G5_IO2 |  |  |  |  |  |

| PB5                                                                           | SPI1_MOSI, I2S1_SD  | TIM3_CH2  | TIM16_BKIN | I2C1_SMBA  |  |  |  |  |  |

| PB6                                                                           | USART1_TX           | I2C1_SCL  | TIM16_CH1N | TSC_G5_IO3 |  |  |  |  |  |

| PB7                                                                           | USART1_RX           | I2C1_SDA  | TIM17_CH1N | TSC_G5_IO4 |  |  |  |  |  |

| PB8                                                                           | CEC                 | I2C1_SCL  | TIM16_CH1  | TSC_SYNC   |  |  |  |  |  |

| PB9                                                                           | IR_OUT              | I2C1_SDA  | TIM17_CH1  | EVENTOUT   |  |  |  |  |  |

| PB10                                                                          | CEC                 | I2C2_SCL  | TIM2_CH3   | TSC_SYNC   |  |  |  |  |  |

| PB11                                                                          | EVENTOUT            | I2C2_SDA  | TIM2_CH4   | TSC_G6_IO1 |  |  |  |  |  |

| PB12                                                                          | SPI2_NSS            | EVENTOUT  | TIM1_BKIN  | TSC_G6_IO2 |  |  |  |  |  |

| PB13                                                                          | SPI2_SCK            |           | TIM1_CH1N  | TSC_G6_IO3 |  |  |  |  |  |

| PB14                                                                          | SPI2_MISO           | TIM15_CH1 | TIM1_CH2N  | TSC_G6_IO4 |  |  |  |  |  |

| PB15                                                                          | SPI2_MOSI           | TIM15_CH2 | TIM1_CH3N  | TIM15_CH1N |  |  |  |  |  |

DocID023402 Rev 4

34/104

STM32F058C8 STM32F058R8 STM32F058T8

5

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 1.8$  V and  $V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

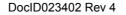

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 8*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 9.

| Symbol                               | Ratings                                                                      | Max.                 | Unit |

|--------------------------------------|------------------------------------------------------------------------------|----------------------|------|

| ΣI <sub>VDD</sub>                    | Total current into sum of all VDD power lines (source) <sup>(1)</sup>        | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>       | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>              | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>             | -100                 |      |

| 1                                    | Output current sunk by any I/O and control pin                               | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                             | -25                  |      |

| ΣI                                   | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup> | 80                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all I/Os and control $pins^{(2)}$     | -80                  | mA   |

|                                      | Injected current on POR, B, FT and FTf pins                                  | -5/+0 <sup>(4)</sup> |      |

| ا <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                           | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                  | ± 5                  | 1    |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>      | ± 25                 | 1    |

#### Table 17. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. A positive injection is induced by  $V_{IN} > V_{DDIOx}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 16: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

On these I/Os, a positive injection is induced by V<sub>IN</sub> > V<sub>DDA</sub>. Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 52: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 18. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |  |

|------------------|------------------------------|-------------|------|--|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |  |

| TJ               | Maximum junction temperature | 150         | °C   |  |

|                 |                                       | _                     |                   | All peripherals enabled |       |                      |                  |      | All peripherals disabled |          |                  |      |  |

|-----------------|---------------------------------------|-----------------------|-------------------|-------------------------|-------|----------------------|------------------|------|--------------------------|----------|------------------|------|--|

| Symbol          | Parameter                             | Conditions            | f <sub>HCLK</sub> | Turn                    | N     | lax @ T <sub>/</sub> | A <sup>(1)</sup> | Tura | N                        | lax @ T, | A <sup>(1)</sup> | Unit |  |

|                 |                                       |                       |                   | Тур                     | 25 °C | 85 °C                | 105 °C           | Тур  | 25 °C                    | 85 °C    | 105 °C           |      |  |

|                 |                                       | HSE                   | 48 MHz            | 12.5                    | 13.7  | 14.4                 | 14.9             | 2.7  | 2.9                      | 3.0      | 3.2              |      |  |

|                 | Supply<br>current in<br>Sleep<br>mode | bypass,<br>PLL on     | 32 MHz            | 8.8                     | 9.3   | 9.7                  | 10.1             | 1.8  | 2.0                      | 2.2      | 2.3              |      |  |

|                 |                                       |                       | 24 MHz            | 6.8                     | 7.3   | 7.7                  | 8.1              | 1.5  | 1.5                      | 1.6      | 1.7              |      |  |

|                 |                                       | Supply                | HSE 8 MHz         | 8 MHz                   | 2.2   | 2.6                  | 2.8              | 3.0  | 0.5                      | 0.6      | 0.6              | 0.6  |  |

| I <sub>DD</sub> |                                       | bypass,<br>PLL off    | 1 MHz             | 0.3                     | 0.4   | 0.4                  | 0.5              | 0.1  | 0.2                      | 0.2      | 0.2              | mA   |  |

|                 |                                       | -                     | ode               | 48 MHz                  | 12.6  | 13.8                 | 14.5             | 15.1 | 2.8                      | 2.9      | 3.1              | 3.3  |  |

|                 |                                       | HSI clock,<br>PLL on  | 32 MHz            | 8.8                     | 9.5   | 9.8                  | 10.2             | 1.9  | 2.1                      | 2.2      | 2.4              |      |  |

|                 |                                       |                       | 24 MHz            | 6.9                     | 7.4   | 7.8                  | 8.1              | 1.5  | 1.6                      | 1.7      | 1.8              |      |  |

|                 |                                       | HSI clock,<br>PLL off | 8 MHz             | 2.3                     | 2.7   | 2.9                  | 3.1              | 0.5  | 0.6                      | 0.7      | 0.8              |      |  |

Table 22. Typical and maximum current consumption from V<sub>DD</sub> at 1.8 V (continued)

1. Data based on characterization results, not tested in production unless otherwise specified.

| Symbol           |                                                          |                             |                   | VDDA = 2.4 V |       |         |        |      | VDDA = 3.6 V |         |        |      |  |

|------------------|----------------------------------------------------------|-----------------------------|-------------------|--------------|-------|---------|--------|------|--------------|---------|--------|------|--|

|                  | Parameter                                                | Conditions<br>(1)           | f <sub>HCLK</sub> | Tum          | M     | ax @ TA | (2)    | Turn | М            | ax @ TA | (2)    | Unit |  |

|                  |                                                          |                             |                   | Тур          | 25 °C | 85 °C   | 105 °C | Тур  | 25 °C        | 85 °C   | 105 °C |      |  |

|                  |                                                          |                             | 48 MHz            | 148          | 169   | 179     | 183    | 162  | 183          | 195     | 198    |      |  |

|                  | Supply<br>current in<br>Run or<br>Sleep<br>mode,<br>code | e,                          | 32 MHz            | 103          | 121   | 126     | 128    | 111  | 129          | 135     | 138    | -    |  |

|                  |                                                          |                             | 24 MHz            | 81           | 96    | 100     | 103    | 87   | 102          | 106     | 108    |      |  |

|                  |                                                          |                             | 8 MHz             | 1.0          | 3.0   | 3.0     | 3.0    | 2.0  | 3.0          | 3.0     | 4.0    |      |  |

| I <sub>DDA</sub> |                                                          |                             | 1 MHz             | 1.0          | 2.0   | 2.0     | 2.0    | 2.0  | 2.0          | 3.0     | 3.0    | μA   |  |

|                  | executing                                                | ing<br>ash<br>y or Internal | 48 MHz            | 218          | 240   | 251     | 255    | 242  | 263          | 275     | 278    |      |  |

|                  | from Flash<br>memory or<br>RAM                           |                             | 32 MHz            | 172          | 191   | 199     | 202    | 191  | 209          | 215     | 218    |      |  |

|                  |                                                          |                             | 24 MHz            | 150          | 168   | 173     | 175    | 166  | 183          | 190     | 192    |      |  |

|                  |                                                          |                             |                   | 8 MHz        | 70    | 80      | 82     | 83   | 82           | 91      | 94     | 95   |  |

1. Current consumption from the VDDA supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, IDDA is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

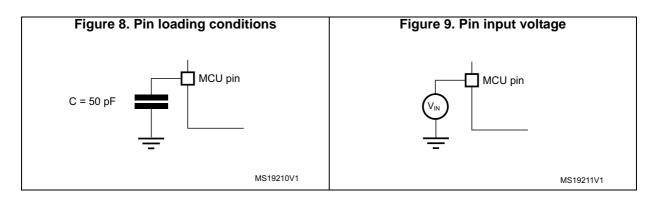

Figure 12. High-speed external clock source AC timing diagram

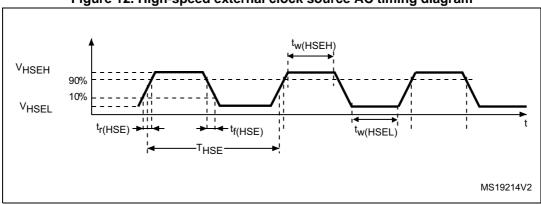

## Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.13. However, the recommended clock input waveform is shown in *Figure 13*.

| Symbol                                       | Parameter <sup>(1)</sup>                       | Min                    | Тур    | Max                    | Unit |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------|------------------------|--------|------------------------|------|--|--|--|--|--|

| f <sub>LSE_ext</sub>                         | User external clock source frequency           | -                      | 32.768 | 1000                   | kHz  |  |  |  |  |  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage          | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |  |  |  |  |  |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage           | $V_{SS}$               | -      | 0.3 V <sub>DDIOx</sub> | v    |  |  |  |  |  |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time                      | 450                    | -      | -                      | ns   |  |  |  |  |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | t <sub>r(LSE)</sub> OSC32 IN rise or fall time |                        | -      | 50                     | 115  |  |  |  |  |  |

Table 31. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

Figure 13. Low-speed external clock source AC timing diagram

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (for example control registers)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                          | Monitored<br>frequency band | Max vs. [f <sub>HSE</sub> /f <sub>HCLK</sub> ]<br>8/48 MHz | Unit |

|------------------|------------|-------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|------|

|                  |            | $V_{DD}$ = 1.8 V, $T_A$ = 25 °C,<br>LQFP64 package<br>compliant with<br>IEC 61967-2 | 0.1 to 30 MHz               | 0                                                          |      |

| 6                | Deeklevel  |                                                                                     | 30 to 130 MHz               | 22                                                         | dBµV |

| S <sub>EMI</sub> | Peak level |                                                                                     | 130 MHz to 1 GHz            | 16                                                         |      |

|                  |            |                                                                                     | EMI Level                   | 3.5                                                        | -    |

Table 41. EMI characteristics

## 6.3.11 Electrical sensitivity characteristics

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

## **Electrostatic discharge (ESD)**

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

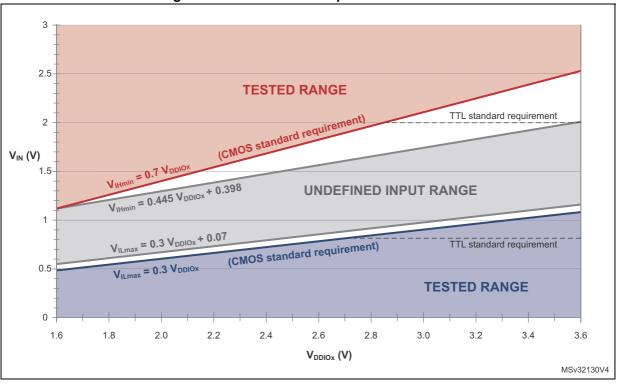

Figure 18. TC and TTa I/O input characteristics

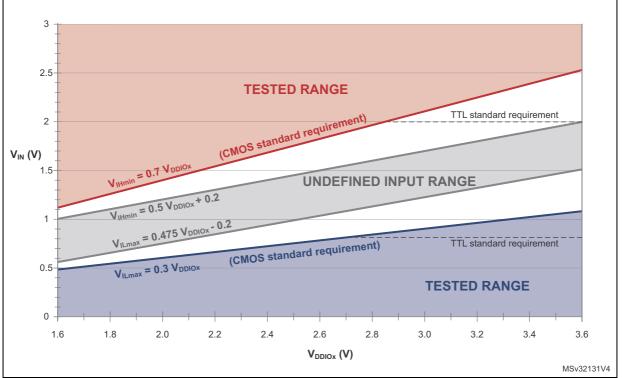

Figure 19. Five volt tolerant (FT and FTf) I/O input characteristics

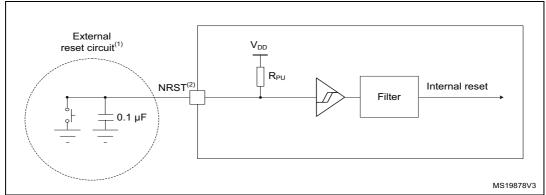

## 6.3.14 NRST and NPOR pin characteristics

#### **NRST** pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 19: General operating conditions*.

| Symbol                 | Parameter Conditions Min                        |                                   | Тур                                         | Мах | Unit                                     |    |  |  |  |

|------------------------|-------------------------------------------------|-----------------------------------|---------------------------------------------|-----|------------------------------------------|----|--|--|--|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                    | -                                 | -                                           | -   | 0.3 V <sub>DD</sub> +0.07 <sup>(1)</sup> | V  |  |  |  |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                   | -                                 | 0.445 V <sub>DD</sub> +0.398 <sup>(1)</sup> | -   | -                                        | v  |  |  |  |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis      | -                                 | -                                           | 200 | -                                        | mV |  |  |  |

| R <sub>PU</sub>        | Weak pull-up equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                          | 40  | 55                                       | kΩ |  |  |  |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                       | -                                 | -                                           | -   | 100 <sup>(1)</sup>                       | ns |  |  |  |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                   | _                                 | 700 <sup>(1)</sup>                          | -   | _                                        | ns |  |  |  |

#### Table 48. NRST pin characteristics

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series

resistance is minimal (~10% order).

Figure 21. Recommended NRST pin protection

- 1. The external capacitor protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 48: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

#### NPOR pin characteristics

The NPOR pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor to the  $V_{DDA}$ ,  $R_{PU}$ .

Unless otherwise specified, the parameters given in *Table 49* below are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 19: General operating conditions*.

| Г |                 |                                                                  |                   |                    |      |  |  |  |  |  |

|---|-----------------|------------------------------------------------------------------|-------------------|--------------------|------|--|--|--|--|--|

|   | Symbol          | Parameter                                                        | Min               | Max                | Unit |  |  |  |  |  |

|   | t <sub>AF</sub> | Maximum width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |  |  |  |  |  |

Table 60. I<sup>2</sup>C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

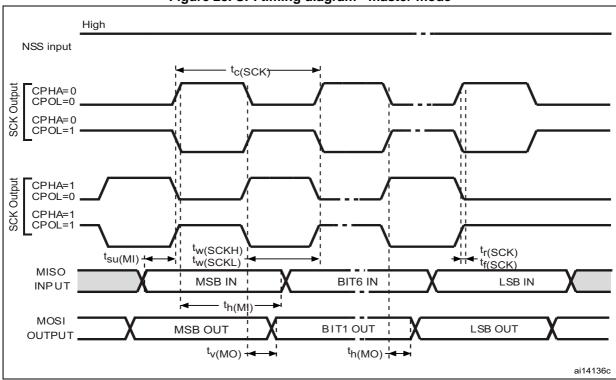

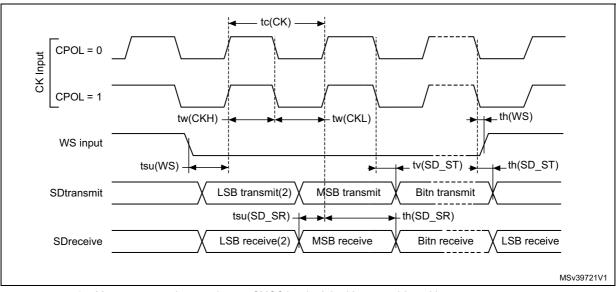

## SPI/I<sup>2</sup>S characteristics

Unless otherwise specified, the parameters given in *Table 61* for SPI or in *Table 62* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and supply voltage conditions summarized in *Table 19: General operating conditions*.

Refer to Section 6.3.13: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                                 | Conditions                                            | Min         | Max         | Unit  |

|----------------------------------------------|-------------------------------------------|-------------------------------------------------------|-------------|-------------|-------|

| f <sub>SCK</sub>                             |                                           | Master mode                                           |             | 18          | MHz   |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                       | Slave mode                                            | -           | 18          | IVITZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time              | Capacitive load: C = 15 pF                            | -           | 6           | ns    |

| t <sub>su(NSS)</sub>                         | NSS setup time                            | Slave mode                                            | 4Tpclk      | -           |       |

| t <sub>h(NSS)</sub>                          | NSS hold time                             | Slave mode                                            | 2Tpclk + 10 | -           |       |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                     | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | Tpclk/2 -2  | Tpclk/2 + 1 |       |

| t <sub>su(MI)</sub>                          | t <sub>su(MI)</sub> Data input setup time | Master mode                                           | 4           | -           |       |

|                                              |                                           | Slave mode                                            | 5           | -           |       |

| t <sub>h(MI)</sub>                           | Data input hold time                      | Master mode                                           | 4           | -           |       |

| t <sub>h(SI)</sub>                           |                                           | Slave mode                                            | 5           | -           | ns    |

| $t_{a(SO)}^{(2)}$                            | Data output access time                   | Slave mode, f <sub>PCLK</sub> = 20 MHz                | 0           | 3Tpclk      |       |

| t <sub>dis(SO)</sub> <sup>(3)</sup>          | Data output disable time                  | Slave mode                                            | 0           | 18          |       |

| t <sub>v(SO)</sub>                           | Data output valid time                    | Slave mode (after enable edge)                        | -           | 22.5        |       |

| t <sub>v(MO)</sub>                           | Data output valid time                    | Master mode (after enable edge)                       | -           | 6           |       |

| t <sub>h(SO)</sub>                           | Data output hold time                     | Slave mode (after enable edge)                        | 11.5        | -           |       |

| t <sub>h(MO)</sub>                           |                                           | Master mode (after enable edge)                       | 2           | -           |       |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle       | Slave mode                                            | 25          | 75          | %     |

| Table | 61. | SPI | characteristics( | 1) |

|-------|-----|-----|------------------|----|

|-------|-----|-----|------------------|----|

1. Data based on characterization results, not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

Figure 28. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

| Table | 62. | l <sup>2</sup> S | characteristics <sup>(1)</sup> |

|-------|-----|------------------|--------------------------------|

|-------|-----|------------------|--------------------------------|

| Symbol               | Parameter                                     | Conditions                                               | Min   | Мах   | Unit |

|----------------------|-----------------------------------------------|----------------------------------------------------------|-------|-------|------|

| f <sub>CK</sub>      | I <sup>2</sup> S clock frequency              | Master mode (data: 16 bits, Audio<br>frequency = 48 kHz) | 1.597 | 1.601 | MHz  |

| 1/t <sub>c(CK)</sub> |                                               | Slave mode                                               | 0     | 6.5   |      |

| t <sub>r(CK)</sub>   | I <sup>2</sup> S clock rise time              | Conscitive load C = 15 pE                                | -     | 10    |      |

| t <sub>f(CK)</sub>   | I <sup>2</sup> S clock fall time              | Capacitive load C <sub>L</sub> = 15 pF                   | -     | 12    |      |

| t <sub>w(CKH)</sub>  | I <sup>2</sup> S clock high time              | Master f <sub>PCLK</sub> = 16 MHz, audio                 | 306   | -     |      |

| t <sub>w(CKL)</sub>  | I <sup>2</sup> S clock low time               | frequency = 48 kHz                                       | 312   | -     |      |

| t <sub>v(WS)</sub>   | WS valid time                                 | Master mode                                              | 2     | -     | ns   |

| t <sub>h(WS)</sub>   | WS hold time                                  | Master mode                                              | 2     | -     |      |

| t <sub>su(WS)</sub>  | WS setup time                                 | Slave mode                                               | 7     | -     |      |

| t <sub>h(WS)</sub>   | WS hold time                                  | Slave mode                                               | 0     | -     |      |

| DuCy(SCK)            | I <sup>2</sup> S slave input clock duty cycle | Slave mode                                               | 25    | 75    | %    |

| Symbol                               | Parameter              | Conditions         | Min | Мах | Unit |  |  |  |

|--------------------------------------|------------------------|--------------------|-----|-----|------|--|--|--|

| t <sub>su(SD_MR)</sub>               | Data input setup time  | Master receiver    | 6   | -   |      |  |  |  |

| t <sub>su(SD_SR)</sub>               |                        | Slave receiver     | 2   | -   |      |  |  |  |

| t <sub>h(SD_MR)</sub> <sup>(2)</sup> | Data input hold time   | Master receiver    | 4   | -   |      |  |  |  |

| t <sub>h(SD_SR)</sub> <sup>(2)</sup> |                        | Slave receiver     | 0.5 | -   |      |  |  |  |

| t <sub>v(SD_MT)</sub> <sup>(2)</sup> | Data output valid time | Master transmitter | -   | 4   | ns   |  |  |  |

| t <sub>v(SD_ST)</sub> <sup>(2)</sup> |                        | Slave transmitter  | -   | 31  |      |  |  |  |

| t <sub>h(SD_MT)</sub>                | Data output hold time  | Master transmitter | 0   | -   | ]    |  |  |  |

| t <sub>h(SD_ST)</sub>                |                        | Slave transmitter  | 13  | -   |      |  |  |  |

Table 62. I<sup>2</sup>S characteristics<sup>(1)</sup> (continued)

1. Data based on design simulation and/or characterization results, not tested in production.

2. Depends on  $f_{PCLK}$ . For example, if  $f_{PCLK}$  = 8 MHz, then  $T_{PCLK}$  = 1/ $f_{PLCLK}$  = 125 ns.

#### Figure 29. I<sup>2</sup>S slave timing diagram (Philips protocol)

1. Measurement points are done at CMOS levels: 0.3 ×  $V_{\text{DDIOx}}$  and 0.7 ×  $V_{\text{DDIOx}}$

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

|        | Table 63. OFBGA64 package mechanical data (continued) |             |       |        |                       |        |  |  |  |

|--------|-------------------------------------------------------|-------------|-------|--------|-----------------------|--------|--|--|--|

| Cumhal |                                                       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |  |

| Symbol | Min                                                   | Тур         | Max   | Min    | Тур                   | Max    |  |  |  |

| А      | 0.460                                                 | 0.530       | 0.600 | 0.0181 | 0.0209                | 0.0236 |  |  |  |

| b      | 0.170                                                 | 0.280       | 0.330 | 0.0067 | 0.0110                | 0.0130 |  |  |  |

| D      | 4.850                                                 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |  |  |  |

| D1     | 3.450                                                 | 3.500       | 3.550 | 0.1358 | 0.1378                | 0.1398 |  |  |  |

| E      | 4.850                                                 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |  |  |  |

| E1     | 3.450                                                 | 3.500       | 3.550 | 0.1358 | 0.1378                | 0.1398 |  |  |  |

| е      | -                                                     | 0.500       | -     | -      | 0.0197                | -      |  |  |  |

| F      | 0.700                                                 | 0.750       | 0.800 | 0.0276 | 0.0295                | 0.0315 |  |  |  |

| ddd    | -                                                     | -           | 0.080 | -      | -                     | 0.0031 |  |  |  |

| eee    | -                                                     | -           | 0.150 | -      | -                     | 0.0059 |  |  |  |

| fff    | -                                                     | -           | 0.050 | -      | -                     | 0.0020 |  |  |  |

#### Table 63. UFBGA64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

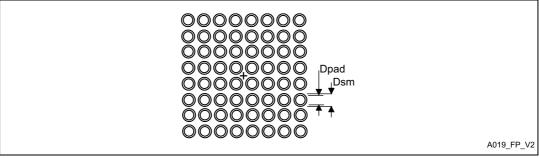

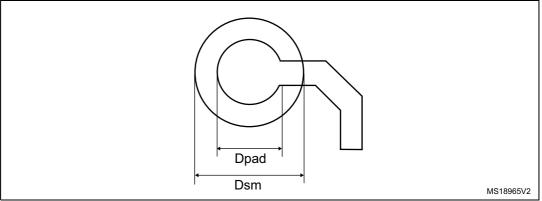

#### Figure 32. Recommended footprint for UFBGA64 package

#### Table 64. UFBGA64 recommended PCB design rules

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|--|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |  |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |  |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |  |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |  |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |  |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |  |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |  |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |  |  |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |  |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |  |  |

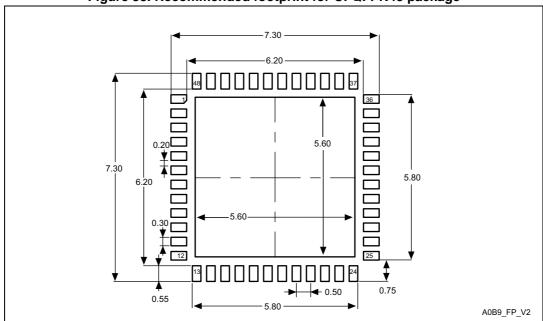

### Table 66. UFQFPN48 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 38. Recommended footprint for UFQFPN48 package

1. Dimensions are expressed in millimeters.

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Max   | Min                   | Тур    | Мах    |

| F      | -           | 0.3025 | -     | -                     | 0.0119 | -      |

| G      | -           | 0.3515 | -     | -                     | 0.0138 | -      |

| aaa    | -           | -      | 0.100 | -                     | -      | 0.0039 |

| bbb    | -           | -      | 0.100 | -                     | -      | 0.0039 |

| CCC    | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ddd    | -           | -      | 0.050 | -                     | -      | 0.0020 |

| eee    | -           | -      | 0.050 | -                     | -      | 0.0020 |

Table 67. WLCSP36 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

#### Figure 41. Recommended pad footprint for WLCSP36 package

#### Table 68. WLCSP36 recommended PCB design rules

| Dimension      | Recommended values                            |  |  |

|----------------|-----------------------------------------------|--|--|

| Pitch          | 0.4 mm                                        |  |  |

| Dpad           | 260 μm max. (circular)<br>220 μm recommended  |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed |  |  |

#### IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved