Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f058r8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introd | duction                               |                                                   |  |  |  |  |  |

|---|--------|---------------------------------------|---------------------------------------------------|--|--|--|--|--|

| 2 | Desci  | ription .                             |                                                   |  |  |  |  |  |

| 3 | Funct  | tional o                              | verview                                           |  |  |  |  |  |

|   | 3.1    | ARM <sup>®</sup> -0                   | Cortex <sup>®</sup> -M0 core                      |  |  |  |  |  |

|   | 3.2    | Memories                              |                                                   |  |  |  |  |  |

|   | 3.3    | Boot mo                               | odes                                              |  |  |  |  |  |

|   | 3.4    | Cyclic re                             | edundancy check calculation unit (CRC)            |  |  |  |  |  |

|   | 3.5    |                                       | nanagement                                        |  |  |  |  |  |

|   |        | 3.5.1                                 | Power supply schemes                              |  |  |  |  |  |

|   |        | 3.5.2                                 | Power-on reset                                    |  |  |  |  |  |

|   |        | 3.5.3                                 | Low-power modes                                   |  |  |  |  |  |

|   | 3.6    | Clocks                                | and startup                                       |  |  |  |  |  |

|   | 3.7    | Genera                                | I-purpose inputs/outputs (GPIOs)                  |  |  |  |  |  |

|   | 3.8    | Direct memory access controller (DMA) |                                                   |  |  |  |  |  |

|   | 3.9    | Interrup                              | ts and events                                     |  |  |  |  |  |

|   |        | 3.9.1                                 | Nested vectored interrupt controller (NVIC)       |  |  |  |  |  |

|   |        | 3.9.2                                 | Extended interrupt/event controller (EXTI)        |  |  |  |  |  |

|   | 3.10   | Analog-                               | to-digital converter (ADC) 16                     |  |  |  |  |  |

|   |        | 3.10.1                                | Temperature sensor                                |  |  |  |  |  |

|   |        | 3.10.2                                | Internal voltage reference (V <sub>REFINT</sub> ) |  |  |  |  |  |

|   |        | 3.10.3                                | V <sub>BAT</sub> battery voltage monitoring       |  |  |  |  |  |

|   | 3.11   | Digital-t                             | o-analog converter (DAC) 18                       |  |  |  |  |  |

|   | 3.12   | Compar                                | rators (COMP) 18                                  |  |  |  |  |  |

|   | 3.13   | Touch s                               | ensing controller (TSC) 18                        |  |  |  |  |  |

|   | 3.14   | Timers a                              | and watchdogs                                     |  |  |  |  |  |

|   |        | 3.14.1                                | Advanced-control timer (TIM1)                     |  |  |  |  |  |

|   |        | 3.14.2                                | General-purpose timers (TIM2, 3, 14, 15, 16, 17)  |  |  |  |  |  |

|   |        | 3.14.3                                | Basic timer TIM6                                  |  |  |  |  |  |

|   |        | 3.14.4                                | Independent watchdog (IWDG) 21                    |  |  |  |  |  |

|   |        | 3.14.5                                | System window watchdog (WWDG)22                   |  |  |  |  |  |

|   |        | 3.14.6                                | SysTick timer                                     |  |  |  |  |  |

# 3.4 Cyclic redundancy check calculation unit (CRC)

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a CRC-32 (Ethernet) polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 3.5 **Power management**

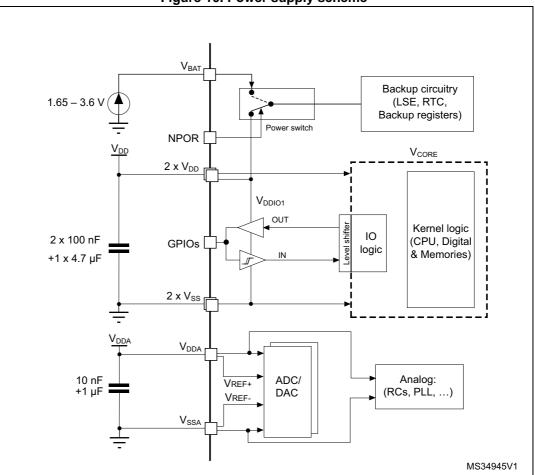

### 3.5.1 Power supply schemes

- V<sub>DD</sub> = V<sub>DDIO1</sub> = 1.8 V ± 8%: external power supply for I/Os (V<sub>DDIO1</sub>) and digital logic. It is provided externally through VDD pins.

- $V_{DDA}$  = from  $V_{DD}$  to 3.6 V: external analog power supply for ADC, DAC, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC or DAC are used). It is provided externally through VDDA pin. The  $V_{DDA}$  voltage level must be always greater or equal to the  $V_{DD}$  voltage level and must be established first.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 10: Power supply scheme*.

### 3.5.2 Power-on reset

To guarantee a proper power-on reset, the NPOR pin must be held low until  $V_{DD}$  is stable. When  $V_{DD}$  is stable, the reset state can be exited either by:

- putting the NPOR pin in high impedance (NPOR pin has an internal pull-up), or by

- forcing the pin to high level by connecting it to V<sub>DDA</sub>

### 3.5.3 Low-power modes

The STM32F058C8/R8/T8 microcontrollers support two low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### • Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

Stop mode achieves very low power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The device can be woken up from Stop mode by any of the EXTI lines. The EXTI line source can be one of the 16 external lines, RTC, I2C1 USART1, COMPx or the CEC.

The CEC, USART1 and I2C1 peripherals can be configured to enable the HSI RC oscillator so as to get clock for processing incoming data.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# 3.8 Direct memory access controller (DMA)

The 5-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

# 3.9 Interrupts and events

# 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 54 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature

# 3.14 Timers and watchdogs

The STM32F058C8/R8/T8 devices include up to six general-purpose timers, one basic timer and an advanced control timer.

Table 6 compares the features of the different timers.

| Timer<br>type      | Timer          | Counter resolution | Counter<br>type                                 | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |  |

|--------------------|----------------|--------------------|-------------------------------------------------|----------------------------|------------------------------|-----------------------------|--------------------------|--|--|--|--|

| Advanced control   | TIM1           | 16-bit             | Up, down,<br>up/down                            | integer from<br>1 to 65536 | Yes                          | 4                           | 3                        |  |  |  |  |

|                    | TIM2 32-       |                    | 2-bit Up, down, integer from up/down 1 to 65536 |                            | Yes                          | 4                           | -                        |  |  |  |  |

|                    | TIM3           | 16-bit             | Up, down,<br>up/down                            | integer from<br>1 to 65536 | Yes                          | 4                           | -                        |  |  |  |  |

| General<br>purpose | TIM14          | 16-bit             | Up                                              | integer from<br>1 to 65536 | No                           | 1                           | -                        |  |  |  |  |

|                    | TIM15          | 16-bit             | Up                                              | integer from<br>1 to 65536 | Yes                          | 2                           | 1                        |  |  |  |  |

|                    | TIM16<br>TIM17 | 16-bit             | Up                                              | integer from<br>1 to 65536 | Yes                          | 1                           | 1                        |  |  |  |  |

| Basic              | TIM6           | 16-bit             | Up                                              | integer from<br>1 to 65536 | Yes                          | -                           | -                        |  |  |  |  |

| Table 6. | Timer | feature | comparison |  |

|----------|-------|---------|------------|--|

|----------|-------|---------|------------|--|

# 3.14.1 Advanced-control timer (TIM1)

The advanced-control timer (TIM1) can be seen as a three-phase PWM multiplexed on six channels. It has complementary PWM outputs with programmable inserted dead times. It can also be seen as a complete general-purpose timer. The four independent channels can be used for:

- input capture

- output compare

- PWM generation (edge or center-aligned modes)

- one-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

The counter can be frozen in debug mode.

Many features are shared with those of the standard timers which have the same architecture. The advanced control timer can therefore work together with the other timers via the Timer Link feature for synchronization or event chaining.

The RTC clock sources can be:

- a 32.768 kHz external crystal

- a resonator or oscillator

- the internal low-power RC oscillator (typical frequency of 40 kHz)

- the high-speed external clock divided by 32

# 3.16 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to two I<sup>2</sup>C interfaces (I2C1 and I2C2) can operate in multimaster or slave modes. Both can support Standard mode (up to 100 kbit/s) and Fast mode (up to 400 kbit/s) and, I2C1 also supports Fast Mode Plus (up to 1 Mbit/s) with extra output drive.

Both support 7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (two addresses, one with configurable mask). They also include programmable analog and digital noise filters.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |

Table 7. Comparison of I<sup>2</sup>C analog and digital filters

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to Table 8 for the differences between I2C1 and I2C2.

| Table 8. STM32F058C8/R8/T8 I <sup>2</sup> C | implementation |

|---------------------------------------------|----------------|

|---------------------------------------------|----------------|

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | Х    | Х    |

| Standard mode (up to 100 kbit/s)                             | X    | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with extra output drive I/Os | Х    | -    |

| Independent clock                                            | X    | -    |

# 4 Pinouts and pin descriptions

|         |    |                            |        |       |       | 1.0.0  | <b>9</b> ° P |        |        |  |

|---------|----|----------------------------|--------|-------|-------|--------|--------------|--------|--------|--|

| Top vie | ew | 1                          | 2      | 3     | 4     | 5      | 6            | 7      | 8      |  |

|         | 0  |                            |        |       |       |        |              |        |        |  |

| А       |    | PC14-<br>OSC32             | (PC13) | (PB9) | (PB4) | (PB3)  | (PA15)       | (PA14) | (PA13) |  |

| В       |    | ,PC15-<br>OSC32)<br>OSC32) | VBAT   | (PB8) | воото | (PD2)  | (PC11)       | (PC10) | (PA12) |  |

| С       |    | (OSC_)                     | (PF4)  | РВ7   | (PB5) | (PC12) | (PA10)       | PA9    | (PA11) |  |

| D       |    | (PF1-<br>(OSC_)<br>QUT     | (PF5)  | (PB6) | (vss) | vss    | (PF6)        | PA8    | (PC9)  |  |

| E       |    |                            | (PC1)  | PC0   |       | VDD    | (PF7)        | PC7    | PC8    |  |

| F       |    | (VSSA)                     | PC2    | (PA2) | (PA5) | (PB0)  | PC6          | (PB15) | (PB14) |  |

| G       |    | (PC3)                      | (PA0)  | (PA3) | (PA6) | (PB1)  |              | (PB10) | (PB13) |  |

| н       |    |                            | (PA1)  | (PA4) | (PA7) | PC4    | PC5          | (PB11) | (PB12) |  |

|         |    |                            |        |       |       |        |              |        |        |  |

|         |    |                            |        |       | UFB   | GA64   |              |        |        |  |

|         |    |                            |        |       |       |        |              |        |        |  |

Figure 3. UFBGA64 package pinout

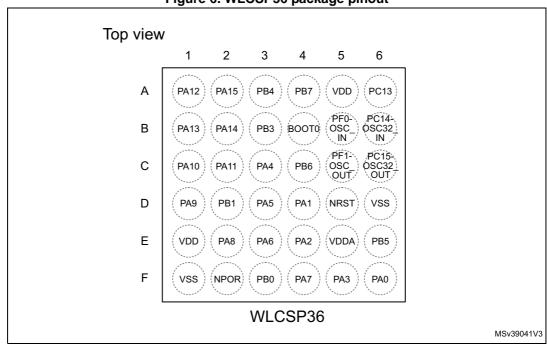

Figure 6. WLCSP36 package pinout

1. The above figure shows the package in top view, changing from bottom view in the previous document versions.

| Na        | me                     | Abbreviation                                                                                      | tion Definition                                                                                  |  |  |  |  |

|-----------|------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin r     | name                   |                                                                                                   | specified in brackets below the pin name, the pin function during and ame as the actual pin name |  |  |  |  |

|           |                        | S                                                                                                 | Supply pin                                                                                       |  |  |  |  |

| Pin       | type                   | I                                                                                                 | Input-only pin                                                                                   |  |  |  |  |

|           |                        | I/O                                                                                               | Input / output pin                                                                               |  |  |  |  |

|           |                        | FT                                                                                                | 5 V-tolerant I/O                                                                                 |  |  |  |  |

|           |                        | FTf                                                                                               | 5 V-tolerant I/O, FM+ capable                                                                    |  |  |  |  |

|           |                        | TTa 3.3 V-tolerant I/O directly connected to ADC                                                  |                                                                                                  |  |  |  |  |

| I/O str   | ucture                 | POR External power on reset pin with embedded weak pull-up resisted powered from V <sub>DDA</sub> |                                                                                                  |  |  |  |  |

|           |                        | TC                                                                                                | Standard 3.3 V I/O                                                                               |  |  |  |  |

|           |                        | В                                                                                                 | Dedicated BOOT0 pin                                                                              |  |  |  |  |

|           |                        | RST                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor                                      |  |  |  |  |

| Notes     |                        | Unless otherwise specified by a note, all I/Os are set as floating inputs during and afte reset.  |                                                                                                  |  |  |  |  |

| Pin       | Alternate<br>functions | Functions selected                                                                                | Functions selected through GPIOx_AFR registers                                                   |  |  |  |  |

| functions | Additional functions   | Functions directly                                                                                | Functions directly selected/enabled through peripheral registers                                 |  |  |  |  |

| Table 11. Legend/abbreviations used in | tho | ninout table |

|----------------------------------------|-----|--------------|

| Table 11. Legenu/abbieviations used in | uie | pinoul lable |

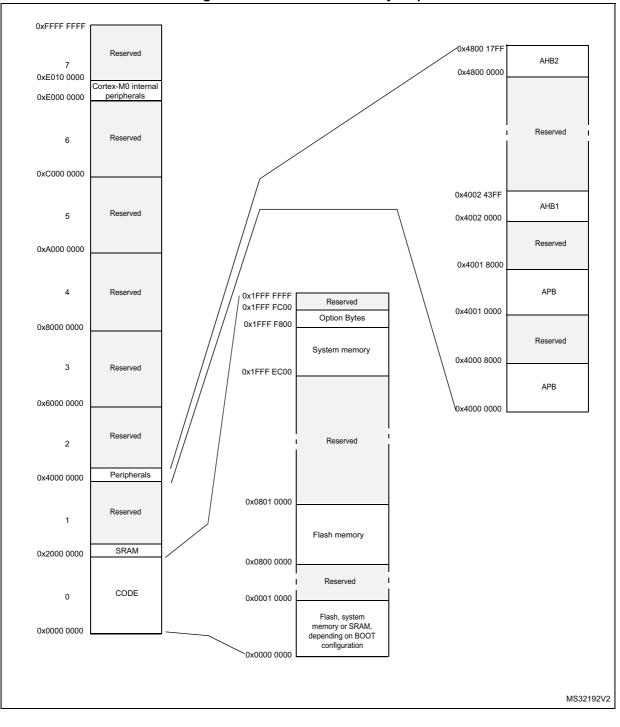

# 5 Memory mapping

| Bus | Boundary address          | Size | Peripheral |

|-----|---------------------------|------|------------|

|     | 0x4000 7C00 - 0x4000 7FFF | 1 KB | Reserved   |

|     | 0x4000 7800 - 0x4000 7BFF | 1 KB | CEC        |

|     | 0x4000 7400 - 0x4000 77FF | 1 KB | DAC        |

|     | 0x4000 7000 - 0x4000 73FF | 1 KB | PWR        |

|     | 0x4000 5C00 - 0x4000 6FFF | 5 KB | Reserved   |

|     | 0x4000 5800 - 0x4000 5BFF | 1 KB | I2C2       |

|     | 0x4000 5400 - 0x4000 57FF | 1 KB | I2C1       |

|     | 0x4000 4800 - 0x4000 53FF | 3 KB | Reserved   |

|     | 0x4000 4400 - 0x4000 47FF | 1 KB | USART2     |

|     | 0x4000 3C00 - 0x4000 43FF | 2 KB | Reserved   |

| APB | 0x4000 3800 - 0x4000 3BFF | 1 KB | SPI2       |

| AFD | 0x4000 3400 - 0x4000 37FF | 1 KB | Reserved   |

|     | 0x4000 3000 - 0x4000 33FF | 1 KB | IWDG       |

|     | 0x4000 2C00 - 0x4000 2FFF | 1 KB | WWDG       |

|     | 0x4000 2800 - 0x4000 2BFF | 1 KB | RTC        |

|     | 0x4000 2400 - 0x4000 27FF | 1 KB | Reserved   |

|     | 0x4000 2000 - 0x4000 23FF | 1 KB | TIM14      |

|     | 0x4000 1400 - 0x4000 1FFF | 3 KB | Reserved   |

|     | 0x4000 1000 - 0x4000 13FF | 1 KB | TIM6       |

|     | 0x4000 0800 - 0x4000 0FFF | 2 KB | Reserved   |

|     | 0x4000 0400 - 0x4000 07FF | 1 KB | TIM3       |

|     | 0x4000 0000 - 0x4000 03FF | 1 KB | TIM2       |

| Table | 15. STM32F058C8/R8/T8 p | peripheral | register | boundary | addresses | (continued) |

|-------|-------------------------|------------|----------|----------|-----------|-------------|

|       |                         |            |          |          |           |             |

# 6.1.6 Power supply scheme

Figure 10. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

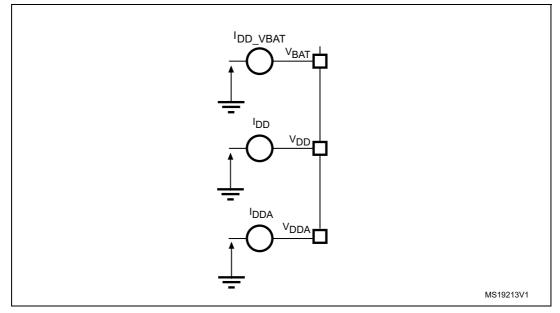

# 6.1.7 Current consumption measurement

### Figure 11. Current consumption measurement scheme

### **Electrical characteristics**

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                 | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур                        | Unit  |      |    |

|-----------------|-------------|---------------------------------------------------------------------------|----------------------------------------------|----------------------------|-------|------|----|

|                 |             |                                                                           | 2 MHz                                        | 0.09                       |       |      |    |

|                 |             |                                                                           | 4 MHz                                        | 0.17                       |       |      |    |

|                 |             | V <sub>DDIOx</sub> = 1.8 V 8 MHz<br>C <sub>EXT</sub> = 0 pF               |                                              | 8 MHz                      | 0.34  |      |    |

|                 |             | $C_{EXT} = 0 \text{ pr}$ $C = C_{INT} + C_{EXT} + C_S$                    | 18 MHz                                       | 0.79                       |       |      |    |

|                 |             |                                                                           | 36 MHz                                       | 1.50                       |       |      |    |

|                 |             |                                                                           | 48 MHz                                       | 2.06                       |       |      |    |

|                 |             |                                                                           | 2 MHz                                        | 0.13                       |       |      |    |

|                 |             |                                                                           | 4 MHz                                        | 0.26                       |       |      |    |

|                 |             | $V_{\text{DDIOx}} = 1.8 \text{ V}$                                        | 8 MHz                                        | 0.50                       |       |      |    |

|                 |             | $C_{EXT} = 10 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$                | 18 MHz                                       | 1.18                       |       |      |    |

|                 |             |                                                                           | 36 MHz                                       | 2.27                       |       |      |    |

|                 |             |                                                                           | 48 MHz                                       | 3.03                       |       |      |    |

| L               | I/O current | $V_{DDIOx} = 1.8 V$<br>$C_{EXT} = 22 pF$<br>$C = C_{INT} + C_{EXT} + C_S$ | 2 MHz                                        | 0.18                       | mA    |      |    |

| I <sub>SW</sub> | consumption |                                                                           | V <sub>DDIOx</sub> = 1.8 V                   | V <sub>DDIOx</sub> = 1.8 V | 4 MHz | 0.36 | ША |

|                 |             |                                                                           | 8 MHz                                        | 0.69                       |       |      |    |

|                 |             |                                                                           | 18 MHz                                       | 1.60                       |       |      |    |

|                 |             |                                                                           | 36 MHz                                       | 3.27                       |       |      |    |

|                 |             |                                                                           | 2 MHz                                        | 0.23                       |       |      |    |

|                 |             | V <sub>DDIOx</sub> = 1.8 V                                                | 4 MHz                                        | 0.45                       | 1     |      |    |

|                 |             | C <sub>EXT</sub> = 33 pF                                                  | 8 MHz                                        | 0.87                       |       |      |    |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                             | 18 MHz                                       | 2.0                        |       |      |    |

|                 |             |                                                                           | 36 MHz                                       | 3.7                        |       |      |    |

|                 |             |                                                                           | 2 MHz                                        | 0.29                       |       |      |    |

|                 |             | V <sub>DDIOx</sub> = 1.8 V<br>C <sub>EXT</sub> = 47 pF                    | 4 MHz                                        | 0.55                       |       |      |    |

|                 |             | $C_{EXT} = 47 \text{ pr}$<br>$C = C_{INT} + C_{EXT} + C_S$                | 8 MHz                                        | 1.09                       |       |      |    |

|                 |             |                                                                           | 18 MHz                                       | 2.43                       |       |      |    |

Table 27. Switching output I/O current consumption

1.  $C_S = 5 \text{ pF}$  (estimated value).

# Low-speed internal (LSI) RC oscillator

| Table 36. LSI osc | illator characteristics <sup>(1)</sup> |

|-------------------|----------------------------------------|

|-------------------|----------------------------------------|

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μΑ   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

# 6.3.8 PLL characteristics

The parameters given in *Table 37* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 19: General operating conditions*.

| Symbol                | Parameter                      |                   | Unit |                    |     |  |

|-----------------------|--------------------------------|-------------------|------|--------------------|-----|--|

| Symbol                | Farameter                      | Min               | Тур  | Max                |     |  |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0  | 24 <sup>(2)</sup>  | MHz |  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -    | 60 <sup>(2)</sup>  | %   |  |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -    | 48                 | MHz |  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -    | 200 <sup>(2)</sup> | μs  |  |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | -    | 300 <sup>(2)</sup> | ps  |  |

Table 37. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

# 6.3.9 Memory characteristics

### **Flash memory**

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

Table 38. Flash memory characteristics

| Symbol             | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| I                  | Supply current          | Write mode                       | -   | -    | 10                 | mA   |

| IDD                |                         | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

| Symbol                | Ratings                                               | Conditions                                                  | Packages | Class | Maximum<br>value <sup>(1)</sup> | Unit |  |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------|----------|-------|---------------------------------|------|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | $T_A = +25 \degree C$ , conforming<br>to JESD22-A114        | All      | 2     | 2000                            | V    |  |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | T <sub>A</sub> = +25 °C, conforming<br>to ANSI/ESD STM5.3.1 | All      | C3    | 250                             | V    |  |

Table 42. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

### Static latch-up

Two complementary static tests are required on six parts to assess the latch-up performance:

- A supply overvoltage is applied to each power supply pin.

- A current injection is applied to each input, output and configurable I/O pin.

These tests are compliant with EIA/JESD 78A IC latch-up standard.

### Table 43. Electrical sensitivities

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

# 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DDIOx}$  (for standard, 3.3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of the -5  $\mu$ A/+0  $\mu$ A range) or other functional failure (for example reset occurrence or oscillator frequency deviation).

The characterization results are given in Table 44.

Negative induced leakage current is caused by negative injection and positive induced leakage current is caused by positive injection.

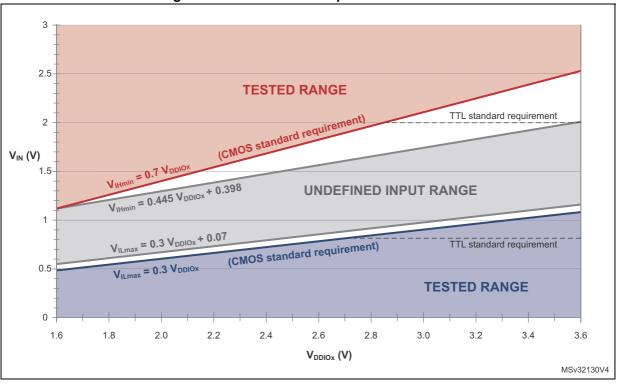

Figure 18. TC and TTa I/O input characteristics

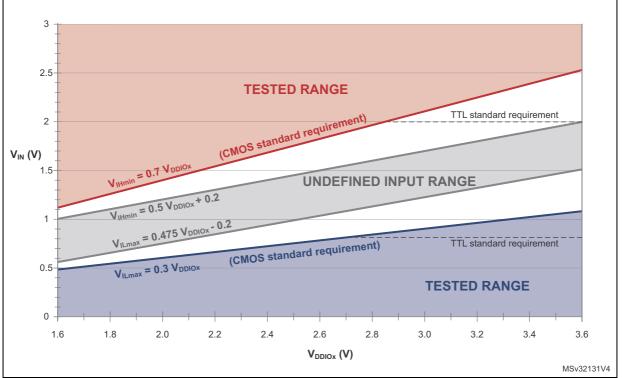

Figure 19. Five volt tolerant (FT and FTf) I/O input characteristics

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур                   | Max    |

| E3     | -     | 7.500       | -     | -      | 0.2953                | -      |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |

| ссс    | -     | -           | 0.080 | -      | -                     | 0.0031 |

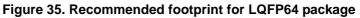

Table 65. LQFP64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

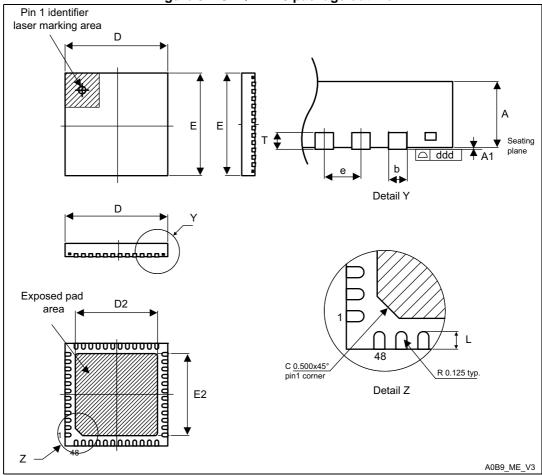

# 7.3 UFQFPN48 package information

UFQFPN48 is a 48-lead, 7x7 mm, 0.5 mm pitch, ultra-thin fine-pitch quad flat package.

Figure 37. UFQFPN48 package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

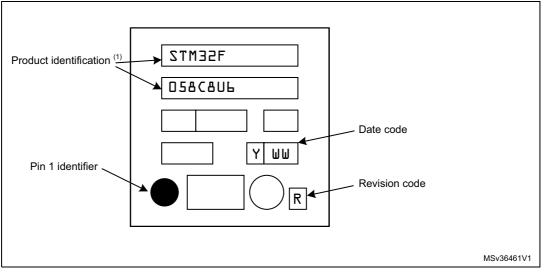

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 39. UFQFPN48 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| 0h.e.l | Sumbol |        |       |     |        |        | inches <sup>(1)</sup> |  |

|--------|--------|--------|-------|-----|--------|--------|-----------------------|--|

| Symbol | Min    | Тур    | Max   | Min | Тур    | Мах    |                       |  |

| F      | -      | 0.3025 | -     | -   | 0.0119 | -      |                       |  |

| G      | -      | 0.3515 | -     | -   | 0.0138 | -      |                       |  |

| aaa    | -      | -      | 0.100 | -   | -      | 0.0039 |                       |  |

| bbb    | -      | -      | 0.100 | -   | -      | 0.0039 |                       |  |

| CCC    | -      | -      | 0.100 | -   | -      | 0.0039 |                       |  |

| ddd    | -      | -      | 0.050 | -   | -      | 0.0020 |                       |  |

| eee    | -      | -      | 0.050 | -   | -      | 0.0020 |                       |  |

Table 67. WLCSP36 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

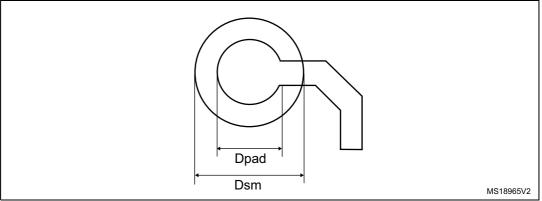

### Figure 41. Recommended pad footprint for WLCSP36 package

#### Table 68. WLCSP36 recommended PCB design rules

| Dimension      | Recommended values                            |

|----------------|-----------------------------------------------|

| Pitch          | 0.4 mm                                        |

| Dpad           | 260 μm max. (circular)<br>220 μm recommended  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |

| PCB pad design | Non-solder mask defined via underbump allowed |

### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} + 8 \times 20 \text{ mA} \times 1.3 \text{ V} = 272 \text{ mW}$

This gives: P<sub>INTmax</sub> = 175 mW and P<sub>IOmax</sub> = 272 mW:

```

P<sub>Dmax</sub> = 175 + 272 = 447 mW

```

Using the values obtained in *Table* 69  $T_{Jmax}$  is calculated as follows:

For LQFP64, 45 °C/W

T<sub>.lmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.115 °C = 102.115 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ) see *Table 19: General operating conditions*.

In this case, parts must be ordered at least with the temperature range suffix 6 (see *Section 8: Ordering information*).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

Suffix 6:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 105\text{-}20.115 = 84.885 ^{\circ}C$ Suffix 7:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 125\text{-}20.115 = 104.885 ^{\circ}C$

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 100 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 20 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OI</sub> = 8 mA, V<sub>OI</sub> = 0.4 V

P<sub>INTmax</sub> = 20 mA × 3.5 V= 70 mW

$P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$

This gives: P<sub>INTmax</sub> = 70 mW and P<sub>IOmax</sub> = 64 mW:

$P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus: P<sub>Dmax</sub> = 134 mW

Using the values obtained in *Table* 69 T<sub>Jmax</sub> is calculated as follows:

- For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 100 °C + (45 °C/W × 134 mW) = 100 °C + 6.03 °C = 106.03 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Ordering information*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.