Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | HCS12                                                                   |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 25MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | PWM, WDT                                                                |

| Number of I/O              | 91                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                           |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 112-LQFP                                                                |

| Supplier Device Package    | 112-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12db128bcpv |

# MC9S12DT128B Device User Guide V01.09 Semiconductor, Inc.

| \$01C0 -   | \$01FF   | Reserved                                    | 41  |

|------------|----------|---------------------------------------------|-----|

| \$0200 -   | \$023F   | Reserved                                    | 41  |

| \$0240 -   | \$027F   | PIM (Port Integration Module)               | 42  |

| \$0280 -   | \$02BF   | CAN4 (Motorola Scalable CAN - MSCAN)        | 44  |

| \$02C0 -   | \$02FF   | Reserved                                    | 45  |

| \$0300 -   | \$035F   | Byteflight                                  | 45  |

| \$0360 -   | \$03FF   | Reserved                                    | 47  |

| Table 1-3  | Assigne  | ed Part ID Numbers                          | 47  |

| Table 1-4  | Memory   | y size registers                            | 47  |

| Table 2-1  | Signal F | Properties                                  | 52  |

| Table 2-2  |          | 2DT128B Power and Ground Connection Summary |     |

| Table 4-1  |          | Selection                                   |     |

| Table 4-2  |          | Selection Based on PE7                      |     |

| Table 4-3  | _        | Regulator VREGEN                            |     |

| Table 5-1  |          | t Vector Locations                          |     |

| Table 22-1 | •        | ted External Component Values               |     |

| Table A-1  |          | e Maximum Ratings                           |     |

| Table A-2  |          | nd Latch-up Test Conditions                 |     |

| Table A-3  |          | nd Latch-Up Protection Characteristics      |     |

| Table A-4  | -        | ng Conditions                               |     |

| Table A-5  |          | ll Package Characteristics                  |     |

| Table A-6  |          | Characteristics                             |     |

| Table A-7  |          | Current Characteristics                     |     |

| Table A-8  | -        | perating Characteristics                    |     |

| Table A-9  |          | ectrical Characteristics                    |     |

|            |          | onversion Performance                       |     |

|            |          | iming Characteristics                       |     |

|            |          | eliability Characteristics                  |     |

|            |          | Regulator Recommended Load Capacitances     |     |

|            | •        | Characteristics                             |     |

|            |          | tor Characteristics                         |     |

|            |          | aracteristics                               |     |

|            |          | N Wake-up Pulse Characteristics             |     |

|            |          | ster Mode Timing Characteristics            |     |

|            |          | ave Mode Timing Characteristics             |     |

| Table A-20 | Expand   | ded Bus Timing Characteristics              | 119 |

# MC9S12DT128B Device User Guide \_\_\_ V01.09

## 1.4 Block Diagram

**Figure 1-1** shows a block diagram of the MC9S12DT128B device.

# Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide — V01.09

#### \$00A0 - \$00C7

### **PWM (Pulse Width Modulator 8 Bit 8 Channel)**

| Address        | Name          |                 | Bit 7    | Bit 6 | Bit 5    | Bit 4     | Bit 3 | Bit 2  | Bit 1   | Bit 0       |

|----------------|---------------|-----------------|----------|-------|----------|-----------|-------|--------|---------|-------------|

| \$00C2         | PWMDTY6       | Read:<br>Write: | Bit 7    | 6     | 5        | 4         | 3     | 2      | 1       | Bit 0       |

| \$00C3         | PWMDTY7       | Read:<br>Write: | Bit 7    | 6     | 5        | 4         | 3     | 2      | 1       | Bit 0       |

| 00004          | D14/140D14    | Read:           | 514445   | 51444 |          | 5,4,4,1,4 | 0     | PWM7IN | 5044470 | D14/447E414 |

| \$00C4         | \$00C4 PWMSDN | Write:          | e: PWMIF | PWMIE | PWMRSTRT | PWMLVL    |       |        | PWM7INL | PWM7ENA     |

| <b>\$000</b> 5 | Decembed      | Read:           | 0        | 0     | 0        | 0         | 0     | 0      | 0       | 0           |

| \$00C5         | Reserved      | Write:          |          |       |          |           |       |        |         |             |

| <b>\$000</b>   | Reserved      | Read:           | 0        | 0     | 0        | 0         | 0     | 0      | 0       | 0           |

| \$00C6         | Reserved      | Write:          |          |       |          |           |       |        |         |             |

| ¢0007          | Pager and     | Read:           | 0        | 0     | 0        | 0         | 0     | 0      | 0       | 0           |

| \$00C7         | Reserved      | Write:          |          |       |          |           |       |        |         |             |

#### \$00C8 - \$00CF

## **SCI0 (Asynchronous Serial Interface)**

| Address            | Name      |                 | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 |

|--------------------|-----------|-----------------|-------|---------|-------|-------|-------|--------|-------|-------|

| <sub>ተ</sub> ለሰር የ | SCI0BDH   | Read:           | 0     | 0       | 0     | SBR12 | SBR11 | SBR10  | SBR9  | CDDo  |

| \$00C8             | SCIUDDH   | Write:          |       |         |       | SDR1Z | SDKII | SBKIU  | SDK9  | SBR8  |

| \$00C9             | SCI0BDL   | Read:<br>Write: | SBR7  | SBR6    | SBR5  | SBR4  | SBR3  | SBR2   | SBR1  | SBR0  |

| \$00CA             | SCI0CR1   | Read:<br>Write: | LOOPS | SCISWAI | RSRC  | М     | WAKE  | ILT    | PE    | PT    |

| \$00CB             | SCI0CR2   | Read:<br>Write: | TIE   | TCIE    | RIE   | ILIE  | TE    | RE     | RWU   | SBK   |

| <sub>ተ</sub>       | SCI0SR1   | Read:           | TDRE  | TC      | RDRF  | IDLE  | OR    | NF     | FE    | PF    |

| \$00CC             | SCIUSKI   | Write:          |       |         |       |       |       |        |       |       |

| ¢000D              | SCI0SR2   | Read:           | 0     | 0       | 0     | 0     | 0     | DDI/42 | TVDID | RAF   |

| \$00CD             | SC105R2   | Write:          |       |         |       |       |       | BRK13  | TXDIR |       |

| <b>\$000</b> F     | CCIODDIII | Read:           | R8    | то.     | 0     | 0     | 0     | 0      | 0     | 0     |

| \$00CE             | SCI0DRH   | Write:          |       | T8      |       |       |       |        |       |       |

| ¢00CE              | CCIODDI   | Read:           | R7    | R6      | R5    | R4    | R3    | R2     | R1    | R0    |

| \$00CF             | SCI0DRL   | Write:          | T7    | T6      | T5    | T4    | T3    | T2     | T1    | T0    |

#### \$00D0 - \$00D7

### **SCI1 (Asynchronous Serial Interface)**

| Address | Name    |        | Bit 7 | Bit 6   | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0 |

|---------|---------|--------|-------|---------|--------|--------|------------|--------|--------|-------|

| \$00D0  | SCI1BDH | Read:  | 0     | 0       | 0      | SBR12  | SBR11      | SBR10  | SBR9   | SBR8  |

| ΨΟΟΡΟ   | OOMBBIT | Write: |       |         |        | ODITIZ | 5          | ODICIO | OBINO  | OBINO |

| \$00D1  | SCI1BDL | Read:  | SBR7  | SBR6    | SBR5   | SBR4   | SBR3       | SBR2   | SBR1   | SBR0  |

| ΨΟΟΒΙ   | CONBBE  | Write: | ODIT  | OBINO   | OBINO  | ODICI  | 001        | ODINZ  | OBITT  | OBITO |

| \$00D2  | SCI1CR1 | Read:  | LOOPS | SCISWAI | RSRC   | М      | WAKE       | ILT    | PE     | PT    |

| ΨΟΟΒΣ   | CONTORN | Write: | 20010 | COICVV  | 110110 | 171    | VV/ (I \ L | 151    | ' -    | ' '   |

| \$00D3  | SCI1CR2 | Read:  | TIE   | TCIE    | RIE    | ILIE   | TE         | RE     | RWU    | SBK   |

| ΨΟΟΡΟ   | OOHORZ  | Write: | 111   | TOIL    | IXIL   | ILIL   | 1 L        | IXL    | 11,000 | ODIC  |

| \$00D4  | SCI1SR1 | Read:  | TDRE  | TC      | RDRF   | IDLE   | OR         | NF     | FE     | PF    |

| φ00D4   | SCHSKI  | Write: |       |         |        |        |            |        |        |       |

# MC9S12DT128B Device User Guide V01.09 Semiconductor, Inc.

#### \$0100 - \$010F

#### Flash Control Register (fts128k2)

| Address  | Name                                    |                 | Bit 7  | Bit 6                                 | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|----------|-----------------------------------------|-----------------|--------|---------------------------------------|--------|--------|-------|--------|--------|--------|

| \$0100   | FCLKDIV                                 | Read:<br>Write: | FDIVLD | PRDIV8                                | FDIV5  | FDIV4  | FDIV3 | FDIV2  | FDIV1  | FDIV0  |

| \$0101   | FSEC                                    | Read:           | KEYEN  | NV6                                   | NV5    | NV4    | NV3   | NV2    | SEC1   | SEC0   |

| φυτυτ    | FSEC                                    | Write:          |        |                                       |        |        |       |        |        |        |

| \$0102   | FTSTMOD                                 | Read:           | 0      | 0                                     | 0      | WRALL  | 0     | 0      | 0      | 0      |

| *****    |                                         | Write:          | -      |                                       |        |        | •     | •      |        |        |

| \$0103   | FCNFG                                   | Read:           | CBEIE  | CCIE                                  | KEYACC | 0      | 0     | 0      | BKSEL1 | BKSEL0 |

|          |                                         | Write:          |        |                                       |        |        |       |        |        |        |

| \$0104   | FPROT                                   | Read:<br>Write: | FPOPEN | NV6                                   | FPHDIS | FPHS1  | FPHS0 | FPLDIS | FPLS1  | FPLS0  |

| \$0105   | FSTAT                                   | Read:           | CBEIF  | CCIF                                  | PVIOL  | ACCERR | 0     | BLANK  | 0      | 0      |

| φ0105    | FSIAI                                   | Write:          | CDEIF  |                                       | PVIOL  | ACCERR |       | DLAINN |        |        |

| \$0106   | FCMD                                    | Read:           | 0      | CMDB6                                 | CMDB5  | 0      | 0     | CMDB2  | 0      | CMDB0  |

| φοτοσ    | TONIB                                   | Write:          |        | OWIDDO                                | ONIDBO |        |       | OWIDDZ |        | OWIDBO |

| \$0107   | Reserved for                            | Read:           | 0      | 0                                     | 0      | 0      | 0     | 0      | 0      | 0      |

| φοιοι    | Factory Test                            | Write:          |        |                                       |        |        |       |        |        |        |

| \$0108   | FADDRHI                                 | Read:           | 0      | Bit 14                                | 13     | 12     | 11    | 10     | 9      | Bit 8  |

| φοισσ    | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Write:          |        |                                       |        |        |       |        |        |        |

| \$0109   | FADDRLO                                 | Read:<br>Write: | Bit 7  | 6                                     | 5      | 4      | 3     | 2      | 1      | Bit 0  |

|          |                                         | Read:           |        |                                       |        |        |       |        |        |        |

| \$010A   | FDATAHI                                 | Write:          | Bit 15 | 14                                    | 13     | 12     | 11    | 10     | 9      | Bit 8  |

| \$010B   | FDATALO                                 | Read:           | Bit 7  | 6                                     | 5      | 4      | 3     | 2      | 1      | Bit 0  |

| ψυτυΒ    | IDAIALO                                 | Write:          | DIL 1  | · · · · · · · · · · · · · · · · · · · | 3      | 4      | 3     |        | I      | DIL U  |

| \$010C - | Reserved                                | Read:           | 0      | 0                                     | 0      | 0      | 0     | 0      | 0      | 0      |

| \$010F   | i (esei veu                             | Write:          |        |                                       |        |        |       |        |        |        |

## \$0110 - \$011B

### **EEPROM Control Register (eets2k)**

| Address | Name            |                 | Bit 7  | Bit 6   | Bit 5   | Bit 4  | Bit 3 | Bit 2   | Bit 1 | Bit 0   |

|---------|-----------------|-----------------|--------|---------|---------|--------|-------|---------|-------|---------|

| \$0110  | ECLKDIV         | Read:<br>Write: | EDIVLD | PRDIV8  | EDIV5   | EDIV4  | EDIV3 | EDIV2   | EDIV1 | EDIV0   |

| \$0111  | \$0111 Reserved |                 | 0      | 0       | 0       | 0      | 0     | 0       | 0     | 0       |

| φυτιτ   | Reserved        | Write:          |        |         |         |        |       |         |       |         |

| \$0112  | Reserved for    | Read:           | 0      | 0       | 0       | 0      | 0     | 0       | 0     | 0       |

| φυτιΖ   | Factory Test    | Write:          |        |         |         |        |       |         |       |         |

| \$0113  | ECNFG           | Read:           | CBEIE  | CCIE    | 0       | 0      | 0     | 0       | 0     | 0       |

| φυτισ   | III3 ECINFG     |                 | CBEIL  | CCIE    |         |        |       |         |       |         |

| \$0114  | EPROT           | Read:<br>Write: | EPOPEN | NV6     | NV5     | NV4    | EPDIS | EP2     | EP1   | EP0     |

| \$0115  | ESTAT           | Read:           | CBEIF  | CCIF    | PVIOL   | ACCERR | 0     | BLANK   | 0     | 0       |

| φυτισ   | ESTAI           | Write:          | CBEIF  |         | FVIOL   | ACCERN |       | DLAINK  |       |         |

| \$0116  | ECMD            | Read:           | 0      | CMDB6   | CMDB5   | 0      | 0     | CMDB2   | 0     | CMDB0   |

| φυτιο   | ECIVID          | Write:          |        | CIVIDBO | CIVIDES |        |       | CIVIDB2 |       | CIVIDBO |

| \$0117  | Reserved for    | Read:           | 0      | 0       | 0       | 0      | 0     | 0       | 0     | 0       |

| φυτιτ   | Factory Test    | Write:          |        |         |         |        |       |         |       |         |

| ¢0110   | EADDRHI         | Read:           | 0      | 0       | 0       | 0      | 0     | 0       | Dit 0 | Di+ 0   |

| \$0118  | EADDKHI         | Write:          |        |         |         |        |       |         | Bit 9 | Bit 8   |

## 2.3 Detailed Signal Descriptions

#### 2.3.1 EXTAL, XTAL — Oscillator Pins

EXTAL and XTAL are the crystal driver and external clock pins. On reset all the device clocks are derived from the EXTAL input frequency. XTAL is the crystal output.

#### 2.3.2 RESET — External Reset Pin

An active low bidirectional control signal, it acts as an input to initialize the MCU to a known start-up state, and an output when an internal MCU function causes a reset.

#### 2.3.3 TEST — Test Pin

This input only pin is reserved for test.

**NOTE:** The TEST pin must be tied to VSS in all applications.

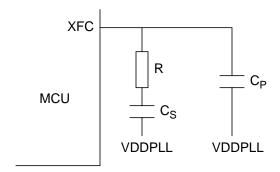

#### 2.3.4 XFC — PLL Loop Filter Pin

PLL loop filter. Please ask your Motorola representative for the interactive application note to compute PLL loop filter elements. Any current leakage on this pin must be avoided.

Figure 2-3 PLL Loop Filter Connections

## 2.3.5 BKGD / TAGHI / MODC — Background Debug, Tag High, and Mode Pin

The BKGD/TAGHI/MODC pin is used as a pseudo-open-drain pin for the background debug communication. In MCU expanded modes of operation when instruction tagging is on, an input low on this pin during the falling edge of E-clock tags the high half of the instruction word being read into the instruction queue. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODC bit at the rising edge of RESET. This pin has a permanently enabled pull-up device.

## MC9S12DT128B Device User Guide Semiconductor, Inc.

**Table 4-3 Voltage Regulator VREGEN**

| VREGEN Description |                                                                                              |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------|--|--|--|--|

| 1                  | Internal Voltage Regulator enabled                                                           |  |  |  |  |

| 0                  | Internal Voltage Regulator disabled, VDD1,2 and VDDPLL must be supplied externally with 2.5V |  |  |  |  |

## 4.3 Security

The device will make available a security feature preventing the unauthorized read and write of the memory contents. This feature allows:

- Protection of the contents of FLASH,

- Protection of the contents of EEPROM,

- Operation in single-chip mode, No BDM possible

- Operation from external memory with internal FLASH and EEPROM disabled.

The user must be reminded that part of the security must lie with the user's code. An extreme example would be user's code that dumps the contents of the internal program. This code would defeat the purpose of security. At the same time the user may also wish to put a back door in the user's program. An example of this is the user downloads a key through the SCI which allows access to a programming routine that updates parameters stored in EEPROM.

### 4.3.1 Securing the Microcontroller

Once the user has programmed the FLASH and EEPROM (if desired), the part can be secured by programming the security bits located in the FLASH module. These non-volatile bits will keep the part secured through resetting the part and through powering down the part.

The security byte resides in a portion of the Flash array.

Check the Flash Block User Guide for more details on the security configuration.

## 4.3.2 Operation of the Secured Microcontroller

### 4.3.2.1 Normal Single Chip Mode

This will be the most common usage of the secured part. Everything will appear the same as if the part was not secured with the exception of BDM operation. The BDM operation will be blocked.

### 4.3.2.2 Executing from External Memory

The user may wish to execute from external space with a secured microcontroller. This is accomplished by resetting directly into expanded mode. The internal FLASH and EEPROM will be disabled. BDM operations will be blocked.

## Freescale Semiconductor, Inc. MC9S12D7128B Device User Guide — V01.09

**NOTE:**

For devices assembled in 80-pin QFP packages all non-bonded out pins should be configured as outputs after reset in order to avoid current drawn from floating inputs. Refer to **Table 2-1** for affected pins.

#### **5.3.2 Memory**

Refer to **Table 1-1** for locations of the memories depending on the operating mode after reset.

The RAM array is not automatically initialized out of reset.

## Freescale Semiconductor, Inc. MC9S12D7128B Device User Guide — V01.09

Consult the EETS2K Block User Guide for information about the EEPROM module.

## **Section 18 RAM Block Description**

This module supports single-cycle misaligned word accesses without wait states.

## **Section 19 MSCAN Block Description**

There are three MSCAN modules (CAN4, CAN1 and CAN0) implemented on the MC9S12DT128B. Consult the MSCAN Block User Guide for information about the Motorola Scalable CAN Module.

## Section 20 Port Integration Module (PIM) Block Description

Consult the PIM\_9DTB128 Block User Guide for information about the Port Integration Module.

## Section 21 Voltage Regulator (VREG) Block Description

Consult the VREG Block User Guide for information about the dual output linear voltage regulator.

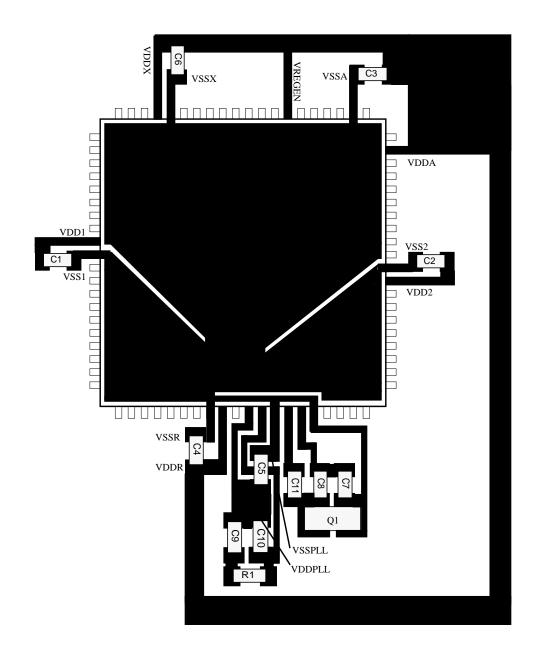

Figure 22-2 Recommended PCB Layout for 80QFP Colpitts Oscillator

## **Appendix A Electrical Characteristics**

#### A.1 General

This introduction is intended to give an overview on several common topics like power supply, current injection etc.

#### A.1.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate.

P:

Those parameters are guaranteed during production testing on each individual device.

C:

Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations. They are regularly verified by production monitors.

T:

Those parameters are achieved by design characterization on a small sample size from typical devices. All values shown in the typical column are within this category.

D:

Those parameters are derived mainly from simulations.

## A.1.2 Power Supply

The MC9S12DT128B utilizes several pins to supply power to the I/O ports, A/D converter, oscillator and PLL as well as the digital core.

The VDDA, VSSA pair supplies the A/D converter and the resistor ladder of the internal voltage regulator.

The VDDX, VSSX, VDDR and VSSR pairs supply the I/O pins , VDDR supplies also the internal voltage regulator.

VDD1, VSS1, VDD2 and VSS2 are the supply pins for the digital logic, VDDPLL, VSSPLL supply the oscillator and the PLL.

VSS1 and VSS2 are internally connected by metal.

VDDA, VDDX, VDDR as well as VSSA, VSSX, VSSR are connected by anti-parallel diodes for ESD protection.

## MC9S12DT128B Device User Guide V01.09 Semiconductor, Inc.

NOTE:

In the following context VDD5 is used for either VDDA, VDDR and VDDX; VSS5 is used for either VSSA, VSSR and VSSX unless otherwise noted.

IDD5 denotes the sum of the currents flowing into the VDDA, VDDX and VDDR

pins.

VDD is used for VDD1, VDD2 and VDDPLL, VSS is used for VSS1, VSS2 and

VSSPLL.

IDD is used for the sum of the currents flowing into VDD1 and VDD2.

#### A.1.3 Pins

There are four groups of functional pins.

#### A.1.3.1 5V I/O pins

Those I/O pins have a nominal level of 5V. This class of pins is comprised of all port I/O pins, the analog inputs, BKGD pin and the RESET inputs. The internal structure of all those pins is identical, however some of the functionality may be disabled. E.g. for the analog inputs the output drivers, pull-up and pull-down resistors are disabled permanently.

#### A.1.3.2 Analog Reference

This class is made up by the two VRH and VRL pins.

#### A.1.3.3 Oscillator

The pins XFC, EXTAL, XTAL dedicated to the oscillator have a nominal 2.5V level. They are supplied by VDDPLL.

#### A.1.3.4 TEST

This pin is used for production testing only.

#### **A.1.3.5 VREGEN**

This pin is used to enable the on chip voltage regulator.

## A.1.4 Current Injection

Power supply must maintain regulation within operating  $V_{DD5}$  or  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{in} > V_{DD5}$ ) is greater than  $I_{DD5}$ , the injection current may flow out of VDD5 and could result in external power supply going out of regulation. Insure external VDD5 load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power; e.g. if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

# MC9S12DT128B Device User Guide Semiconductor, Inc.

given. A very good estimate is to take the single chip currents and add the currents due to the external loads.

**Table A-7 Supply Current Characteristics**

|     |           | s are shown in <b>Table A-4</b> unless otherwise noted                                                                                             | 0                 |     | <b>-</b>                                                     |                             | 1    |

|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|--------------------------------------------------------------|-----------------------------|------|

| Num | С         | Rating                                                                                                                                             | Symbol            | Min | Тур                                                          | Max                         | Unit |

| 1   | Р         | Run supply currents Single Chip, Internal regulator enabled                                                                                        | I <sub>DD5</sub>  |     |                                                              | 55                          | mA   |

| 2   | P<br>P    | Wait Supply current  All modules enabled, PLL on only RTI enabled <sup>1</sup>                                                                     | I <sub>DDW</sub>  |     |                                                              | 30<br>5                     | mA   |

| 3   | CPCCPCPCP | Pseudo Stop Current (RTI and COP disabled) 1, 2 -40°C 27°C 70°C 85°C "C" Temp Option 100°C 105°C "V" Temp Option 120°C 125°C "M" Temp Option 140°C | I <sub>DDPS</sub> |     | 370<br>400<br>450<br>550<br>600<br>650<br>800<br>850<br>1200 | 500<br>1600<br>2100<br>5000 | μА   |

| 4   | 0000000   | Pseudo Stop Current (RTI and COP enabled) 1, 2 -40°C 27°C 70°C 85°C 105°C 125°C 140°C                                                              | I <sub>DDPS</sub> |     | 570<br>600<br>650<br>750<br>850<br>1200<br>1500              |                             | μА   |

| 5   | CPCCPCP   | Stop Current <sup>2</sup> -40°C 27°C 70°C 85°C  "C" Temp Option 100°C 105°C "V" Temp Option 120°C 125°C "M" Temp Option 140°C                      | I <sub>DDS</sub>  |     | 12<br>25<br>100<br>130<br>160<br>200<br>350<br>400<br>600    | 100<br>1200<br>1700<br>5000 | μА   |

#### NOTES:

- 1. PLL off, Oscillator in Colpitts Mode

- 2. At those low power dissipation levels  $T_J = T_A$  can be assumed

## MC9S12DT128B Device User Guide Semiconductor, Inc.

#### A.3.1.3 Sector Erase

Erasing a 512 byte Flash sector or a 4 byte EEPROM sector takes:

$$t_{era} \approx 4000 \cdot \frac{1}{f_{NVMOP}}$$

The setup times can be ignored for this operation.

#### A.3.1.4 Mass Erase

Erasing a NVM block takes:

$$t_{mass} \approx 20000 \cdot \frac{1}{f_{NVMOP}}$$

The setup times can be ignored for this operation.

#### A.3.1.5 Blank Check

The time it takes to perform a blank check on the Flash or EEPROM is dependant on the location of the first non-blank word starting at relative address zero. It takes one bus cycle per word to verify plus a setup of the command.

$$t_{check} \approx location \cdot t_{cyc} + 10 \cdot t_{cyc}$$

Table A-11 NVM Timing Characteristics

| Condit | ions | s are shown in <b>Table A-4</b> unless otherwise noted |                     |                    |     |                     |                  |

|--------|------|--------------------------------------------------------|---------------------|--------------------|-----|---------------------|------------------|

| Num    | С    | Rating                                                 | Symbol              | Min                | Тур | Max                 | Unit             |

| 1      | D    | External Oscillator Clock                              | f <sub>NVMOSC</sub> | 0.5                |     | 50 <sup>1</sup>     | MHz              |

| 2      | D    | Bus frequency for Programming or Erase Operations      | f <sub>NVMBUS</sub> | 1                  |     |                     | MHz              |

| 3      | D    | Operating Frequency                                    | f <sub>NVMOP</sub>  | 150                |     | 200                 | kHz              |

| 4      | Р    | Single Word Programming Time                           | t <sub>swpgm</sub>  | 46 <sup>2</sup>    |     | 74.5 <sup>3</sup>   | μs               |

| 5      | D    | Flash Burst Programming consecutive word <sup>4</sup>  | t <sub>bwpgm</sub>  | 20.4 <sup>2</sup>  |     | 31 <sup>3</sup>     | μs               |

| 6      | D    | Flash Burst Programming Time for 32 Words <sup>4</sup> | t <sub>brpgm</sub>  | 678.4 <sup>2</sup> |     | 1035.5 <sup>3</sup> | μs               |

| 7      | Р    | Sector Erase Time                                      | t <sub>era</sub>    | 20 <sup>5</sup>    |     | 26.7 <sup>3</sup>   | ms               |

| 8      | Р    | Mass Erase Time                                        | t <sub>mass</sub>   | 100 <sup>5</sup>   |     | 133 <sup>3</sup>    | ms               |

| 9      | D    | Blank Check Time Flash per block                       | t <sub>check</sub>  | 11 <sup>6</sup>    |     | 32778 <sup>7</sup>  | t <sub>cyc</sub> |

| 10     | D    | Blank Check Time EEPROM per block                      | t <sub>check</sub>  | 11 <sup>6</sup>    |     | 2058 <sup>7</sup>   | t <sub>cyc</sub> |

#### NOTES:

- 1. Restrictions for oscillator in crystal mode apply!

- Minimum Programming times are achieved under maximum NVM operating frequency f<sub>NVMOP</sub> and maximum bus frequency f<sub>bus</sub>.

- f<sub>bus</sub>.

3. Maximum Erase and Programming times are achieved under particular combinations of f<sub>NVMOP</sub> and bus frequency f<sub>bus</sub>.

Refer to formulae in Sections A.3.1.1 A.3.1.5 for guidance.

### A.5 Reset, Oscillator and PLL

This section summarizes the electrical characteristics of the various startup scenarios for Oscillator and Phase-Locked-Loop (PLL).

#### A.5.1 Startup

**Table A-14** summarizes several startup characteristics explained in this section. Detailed description of the startup behavior can be found in the Clock and Reset Generator (CRG) Block User Guide.

**Table A-14 Startup Characteristics**

| Condit | ions | s are shown in Table A-4 unless otherwise noted |                    |      |     |      |                  |

|--------|------|-------------------------------------------------|--------------------|------|-----|------|------------------|

| Num    | С    | Rating                                          | Symbol             | Min  | Тур | Max  | Unit             |

| 1      | Т    | POR release level                               | V <sub>PORR</sub>  |      |     | 2.07 | V                |

| 2      | Т    | POR assert level                                | V <sub>PORA</sub>  | 0.97 |     |      | V                |

| 3      | D    | Reset input pulse width, minimum input time     | PW <sub>RSTL</sub> | 2    |     |      | t <sub>osc</sub> |

| 4      | D    | Startup from Reset                              | n <sub>RST</sub>   | 192  |     | 196  | n <sub>osc</sub> |

| 5      | D    | Interrupt pulse width, IRQ edge-sensitive mode  | PW <sub>IRQ</sub>  | 20   |     |      | ns               |

| 6      | D    | Wait recovery startup time                      | t <sub>WRS</sub>   |      |     | 14   | t <sub>cyc</sub> |

#### A.5.1.1 POR

The release level  $V_{PORR}$  and the assert level  $V_{PORA}$  are derived from the  $V_{DD}$  Supply. They are also valid if the device is powered externally. After releasing the POR reset the oscillator and the clock quality check are started. If after a time  $t_{CQOUT}$  no valid oscillation is detected, the MCU will start using the internal self clock. The fastest startup time possible is given by  $n_{uposc}$ .

#### A.5.1.2 SRAM Data Retention

Provided an appropriate external reset signal is applied to the MCU, preventing the CPU from executing code when VDD5 is out of specification limits, the SRAM contents integrity is guaranteed if after the reset the PORF bit in the CRG Flags Register has not been set.

#### A.5.1.3 External Reset

When external reset is asserted for a time greater than PW<sub>RSTL</sub> the CRG module generates an internal reset, and the CPU starts fetching the reset vector without doing a clock quality check, if there was an oscillation before reset.

#### A.5.1.4 Stop Recovery

Out of STOP the controller can be woken up by an external interrupt. A clock quality check as after POR is performed before releasing the clocks to the system.

# Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide — V01.09

## A.6 MSCAN

#### **Table A-17 MSCAN Wake-up Pulse Characteristics**

| Condit | Conditions are shown in <b>Table A-4</b> unless otherwise noted |                                       |                  |     |     |     |      |  |  |  |

|--------|-----------------------------------------------------------------|---------------------------------------|------------------|-----|-----|-----|------|--|--|--|

| Num    | С                                                               | Rating                                | Symbol           | Min | Тур | Max | Unit |  |  |  |

| 1      | Р                                                               | MSCAN Wake-up dominant pulse filtered | t <sub>WUP</sub> |     |     | 2   | μs   |  |  |  |

| 2      | Р                                                               | MSCAN Wake-up dominant pulse pass     | t <sub>WUP</sub> | 5   |     |     | μs   |  |  |  |

## Freescale Semiconductor, Inc. MC9S12D128B Device User Guide — V01.09

## A.8 External Bus Timing

A timing diagram of the external multiplexed-bus is illustrated in **Figure A-9** with the actual timing values shown on table **Table A-20**. All major bus signals are included in the diagram. While both a data write and data read cycle are shown, only one or the other would occur on a particular bus cycle.

### A.8.1 General Muxed Bus Timing

The expanded bus timings are highly dependent on the load conditions. The timing parameters shown assume a balanced load across all outputs.

## **Appendix B Package Information**

### **B.1** General

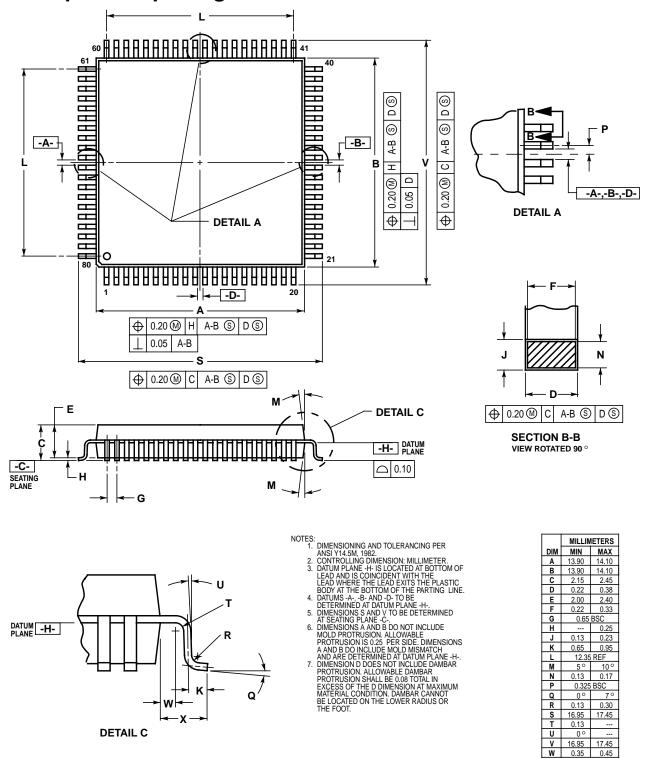

This section provides the physical dimensions of the MC9S12DT128B packages.

## B.3 80-pin QFP package

Figure 1 80-pin QFP Mechanical Dimensions (case no. 841B)