Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HCS12                                                        |

| Core Size                  | 16-Bit                                                       |

| Speed                      | 25MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                           |

| Peripherals                | PWM, WDT                                                     |

| Number of I/O              | 91                                                           |

| Program Memory Size        | 128KB (128K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 2K x 8                                                       |

| RAM Size                   | 8K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                                |

| Data Converters            | A/D 16x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 112-LQFP                                                     |

| Supplier Device Package    | 112-LQFP (20x20)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12dt128bcpv |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide — V01.09

| A.1.3  | Pins                                          |

|--------|-----------------------------------------------|

| A.1.4  | Current Injection                             |

| A.1.5  | Absolute Maximum Ratings                      |

| A.1.6  | ESD Protection and Latch-up Immunity          |

| A.1.7  | Operating Conditions                          |

| A.1.8  | Power Dissipation and Thermal Characteristics |

| A.1.9  | I/O Characteristics                           |

| A.1.10 | Supply Currents                               |

| A.2 AT | D Characteristics                             |

| A.2.1  | ATD Operating Characteristics95               |

| A.2.2  | Factors influencing accuracy95                |

| A.2.3  | ATD accuracy                                  |

| A.3 N∖ | /M, Flash and EEPROM                          |

| A.3.1  | NVM timing                                    |

| A.3.2  | NVM Reliability                               |

|        | Itage Regulator                               |

| A.5 Re | eset, Oscillator and PLL                      |

| A.5.1  | Startup                                       |

| A.5.2  | Oscillator                                    |

| A.5.3  | Phase Locked Loop                             |

|        | SCAN                                          |

| A.7 SF | ข                                             |

| A.7.1  | Master Mode                                   |

| A.7.2  | Slave Mode                                    |

|        | ternal Bus Timing                             |

| A.8.1  | General Muxed Bus Timing                      |

### **Appendix B Package Information**

| B.1 | General              | .121 |

|-----|----------------------|------|

| B.2 | 112-pin LQFP package | 122  |

| B.3 | 80-pin QFP package   | 123  |

#### - Port M[7:6]

PM7:6 must be configured as outputs or their pull resistors must be enabled to avoid floating inputs.

– Port P6

PP6 must be configured as output or its pull resistor must be enabled to avoid a floating input.

- Port S[7:4]

PS7:4 must be configured as outputs or their pull resistors must be enabled to avoid floating inputs.

- PAD[15:8] (ATD1 channels)

Out of reset the ATD1 is disabled preventing current flows in the pins. Do not modify the ATD1 registers!

### **Document References**

The Device User Guide provides information about the MC9S12DT128B device made up of standard HCS12 blocks and the HCS12 processor core.

This document is part of the customer documentation. A complete set of device manuals also includes the HCS12 Core User Guide and all the individual Block User Guides of the implemented modules. In a effort to reduce redundancy all module specific information is located only in the respective Block User Guide. If applicable, special implementation details of the module are given in the block description sections of this document.

See **Table 0-2** for names and versions of the referenced documents throughout the Device User Guide.

| User Guide                                                                | Version | Document Order Number |

|---------------------------------------------------------------------------|---------|-----------------------|

| HCS12_V1.5 Core User Guide                                                | 1.2     | HCS12COREUG           |

| Clock and Reset Generator (CRG) Block User Guide                          | V03     | S12CRGV3/D            |

| Enhanced Capture Timer 16 Bit 8 Channel (ECT_16B8C) Block User Guide      | V01     | S12ECT16B8CV1/D       |

| Analog to Digital Converter 10 Bit 8 Channel (ATD_10B8C) Block User Guide | V02     | S12ATD10B8CV2/D       |

| Inter IC Bus (IIC) Block User Guide                                       | V02     | S12IICV2/D            |

| Asynchronous Serial Interface (SCI) Block User Guide                      | V02     | S12SCIV2/D            |

| Serial Peripheral Interface (SPI) Block User Guide                        | V02     | S12SPIV2/D            |

| Pulse Width Modulator 8 Bit 8 Channel (PWM_8B8C) Block User Guide         | V01     | S12PWM8B8CV1/D        |

| 128K Byte Flash (FTS128K) Block User Guide                                | V01     | S12FTS128KV1/D        |

| 2K Byte EEPROM (EETS2K) Block User Guide                                  | V01     | S12EETS2KV1/D         |

| Byte Level Data Link Controller -J1850 (BDLC) Block User Guide            | V01     | S12BDLCV1/D           |

| Motorola Scalable CAN (MSCAN) Block User Guide                            | V02     | S12MSCANV2/D          |

| Voltage Regulator (VREG) Block User Guide                                 | V01     | S12VREGV1/D           |

| Port Integration Module (PIM_9DT128) Block User Guide                     | V01     | S12PIMDT128V1/D       |

| Byteflight (BF) Block User Guide                                          | V01     | S12BFV1/D             |

**Table 0-2 Document References**

\$00A0 - \$00C7

#### PWM (Pulse Width Modulator 8 Bit 8 Channel)

| Address        | Name      | [               | Bit 7        | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0      |

|----------------|-----------|-----------------|--------------|-------|--------|-------|-------|-------|-------|------------|

| \$00A9         | PWMSCLB   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00AA         | PWMSCNTA  | Read:           | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| Φυυλά          | Test Only | Write:          |              |       |        |       |       |       |       |            |

| \$00AB         | PWMSCNTB  | Read:           | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| \$00/ L        | Test Only | Write:          | <b>D H H</b> |       |        |       |       |       |       | Dit o      |

| \$00AC         | PWMCNT0   | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

|                |           | Write:<br>Read: | 0<br>Bit 7   | 0     | 0<br>5 | 0 4   | 0     | 0     | 0     | 0<br>Bit 0 |

| \$00AD         | PWMCNT1   | Write:          | <u>оп</u>    | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

|                |           | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00AE         | PWMCNT2   | Write:          | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| <b>***</b>     |           | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00AF         | PWMCNT3   | Write:          | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| ¢ооро          |           | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00B0         | PWMCNT4   | Write:          | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| \$00B1         | PWMCNT5   | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| ΨŪŪDI          |           | Write:          | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| \$00B2         | PWMCNT6   | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| <i><b></b></i> |           | Write:          | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| \$00B3         | PWMCNT7   | Read:           | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

|                |           | Write:          | 0            | 0     | 0      | 0     | 0     | 0     | 0     | 0          |

| \$00B4         | PWMPER0   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00B5         | PWMPER1   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00B6         | PWMPER2   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00B7         | PWMPER3   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00B8         | PWMPER4   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00B9         | PWMPER5   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00BA         | PWMPER6   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00BB         | PWMPER7   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00BC         | PWMDTY0   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00BD         | PWMDTY1   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00BE         | PWMDTY2   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00BF         | PWMDTY3   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00C0         | PWMDTY4   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

| \$00C1         | PWMDTY5   | Read:<br>Write: | Bit 7        | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0      |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide - V01.09

#### \$00E8 - \$00EF

#### **BDLC (Byte Level Data Link Controller J1850)**

| Address      | Name     |        | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  |

|--------------|----------|--------|-------|---------|-------|-------|-------|-------|--------|--------|

| \$00E8       | DLCBCR1  | Read:  | IMSG  | CLKS    | 0     | 0     | 0     | 0     | IE     | WCM    |

| <b>WOOLO</b> | DEODOINI | Write: |       | OLINO   |       |       |       |       |        | WOW    |

| \$00E9       | DLCBSVR  | Read:  | 0     | 0       | 13    | 12    | l1    | 10    | 0      | 0      |

| \$00E9       | DECROVIC | Write: |       |         |       |       |       |       |        |        |

| \$00EA       | DLCBCR2  | Read:  | SMRST | DLOOP   | RX4XE | NBFS  | TEOD  | TSIFR | TMIFR1 | TMIFR0 |

| <b>WOLA</b>  | DLCDCRZ  | Write: |       | DLOOI   | NA4AL | NDI 5 | ILOD  |       |        |        |

| \$00EB       | DLCBDR   | Read:  | D7    | D6      | D5    | D4    | D3    | D2    | D1     | D0     |

| <b>WOLD</b>  | DLCDDK   | Write: | וט    | DO      | 5     | D4    | 5     | DZ    |        | 00     |

| \$00EC       | DLCBARD  | Read:  | 0     | RXPOL   | 0     | 0     | BO3   | BO2   | BO1    | BO0    |

| <b>WOLC</b>  | DECOARD  | Write: |       | INAL OF |       |       | 005   | 002   | DOT    | DOU    |

| \$00ED       | DLCBRSR  | Read:  | 0     | 0       | R5    | R4    | R3    | R2    | R1     | R0     |

| <b>JUDED</b> | DLCBRSR  | Write: |       |         | КJ    | Ν4    | N3    | NΖ    |        | ΝU     |

| ¢00EE        |          | Read:  | 0     | 0       | 0     | BDLCE | 0     | 0     | 0      | 0      |

| \$00EE DLCSC | DLUGUK   | Write: |       |         |       | BULCE |       |       |        |        |

| \$00EF       | DLCBSTAT | Read:  | 0     | 0       | 0     | 0     | 0     | 0     | 0      | IDLE   |

| φυυεγ        | DLCBSTAT | Write: |       |         |       |       |       |       |        |        |

\$00F0 - \$00F7

#### **SPI1 (Serial Peripheral Interface)**

| Address | Name     | [               | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1   | Bit 0 |

|---------|----------|-----------------|-------|-------|-------|--------|---------|-------|---------|-------|

| \$00F0  | SPI1CR1  | Read:<br>Write: | SPIE  | SPE   | SPTIE | MSTR   | CPOL    | CPHA  | SSOE    | LSBFE |

| \$00F1  | SPI1CR2  | Read:<br>Write: | 0     | 0     | 0     | MODFEN | BIDIROE | 0     | SPISWAI | SPC0  |

| \$00F2  | SPI1BR   | Read:<br>Write: | 0     | SPPR2 | SPPR1 | SPPR0  | 0       | SPR2  | SPR1    | SPR0  |

| \$00F3  | SPI1SR   | Read:<br>Write: | SPIF  | 0     | SPTEF | MODF   | 0       | 0     | 0       | 0     |

| \$00F4  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

| \$00F5  | SPI1DR   | Read:<br>Write: | Bit7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit0  |

| \$00F6  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

| \$00F7  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

#### \$00F8 - \$00FF

#### Reserved

| Address           | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$00F8 - Reserved | Read:    | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |

| \$00FF            | Reserved | Write: |       |       |       |       |       |       |       |       |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide - V01.09

\$0140 - \$017F

### CAN0 (Motorola Scalable CAN - MSCAN)

| Address               | Name                     |                 | Bit 7                                    | Bit 6  | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1  | Bit 0  |

|-----------------------|--------------------------|-----------------|------------------------------------------|--------|---------|----------|----------|-----------|--------|--------|

| \$0146                | CAN0TFLG                 | Read:           | 0                                        | 0      | 0       | 0        | 0        | TXE2      | TXE1   | TXE0   |

|                       |                          | Write:<br>Read: | 0                                        | 0      | 0       | 0        | 0        |           |        |        |

| \$0147                | CAN0TIER                 | Write:          | 0                                        | 0      | 0       | 0        | 0        | TXEIE2    | TXEIE1 | TXEIE0 |

| \$0148                | <b>CAN0TARQ</b>          | Read:           | 0                                        | 0      | 0       | 0        | 0        | ABTRQ2    | ABTRQ1 | ABTRQ0 |

| φ01 <del>4</del> 0    | CANUTARQ                 | Write:          |                                          |        |         |          |          |           |        |        |

| \$0149                | CAN0TAAK                 | Read:<br>Write: | 0                                        | 0      | 0       | 0        | 0        | ABTAK2    | ABTAK1 | ABTAK0 |

|                       |                          | Read:           | 0                                        | 0      | 0       | 0        | 0        |           |        |        |

| \$014A                | CAN0TBSEL                | Write:          | •                                        |        |         |          | •        | TX2       | TX1    | TX0    |

| \$014B                | CAN0IDAC                 | Read:           | 0                                        | 0      | IDAM1   | IDAM0    | 0        | IDHIT2    | IDHIT1 | IDHIT0 |

| ψοτιΒ                 |                          | Write:          |                                          |        |         |          |          |           |        |        |

| \$014C                | Reserved                 | Read:<br>Write: | 0                                        | 0      | 0       | 0        | 0        | 0         | 0      | 0      |

| <b>A</b> A 4 <b>A</b> |                          | Read:           | 0                                        | 0      | 0       | 0        | 0        | 0         | 0      | 0      |

| \$014D                | Reserved                 | Write:          |                                          |        |         |          |          |           |        |        |

| \$014E                | <b>CAN0RXERR</b>         | Read:           | RXERR7                                   | RXERR6 | RXERR5  | RXERR4   | RXERR3   | RXERR2    | RXERR1 | RXERR0 |

| <b>,</b> -            |                          | Write:<br>Read: | TXERR7                                   | TXERR6 | TXERR5  | TXERR4   | TXERR3   | TXERR2    | TXERR1 | TXERR0 |

| \$014F                | CAN0TXERR                | Write:          |                                          | INERRO | IVERKO  | IAERR4   | IVERKS   | INERRZ    | IVERKI | IAERRU |

| \$0150 -              | CAN0IDAR0 -              | Read:           | AC7                                      | AC6    | AC5     | AC4      | AC3      | AC2       | AC1    | AC0    |

| \$0153                | CAN0IDAR3                | Write:          | AC7                                      | ACO    | ACS     | AC4      | AC3      | ACZ       | ACT    | ACU    |

| \$0154 -<br>\$0157    | CAN0IDMR0 -<br>CAN0IDMR3 | Read:<br>Write: | AM7                                      | AM6    | AM5     | AM4      | AM3      | AM2       | AM1    | AM0    |

| \$0158 -              | CAN0IDAR4 -<br>CAN0IDAR7 | Read:           | AC7                                      | AC6    | AC5     | AC4      | AC3      | AC2       | AC1    | AC0    |

| \$015B<br>\$015C -    | CANOIDAR7<br>CANOIDMR4 - | Write:<br>Read: |                                          |        |         |          |          |           |        |        |

| \$015C -              | CANOIDMR7                | Write:          | AM7                                      | AM6    | AM5     | AM4      | AM3      | AM2       | AM1    | AM0    |

| \$0160 -              | CAN0RXFG                 | Read:           |                                          | FOF    | REGROUN | D RECEIV | E BUFFER | see Table | 1-2    |        |

| \$016F                |                          | Write:          |                                          |        |         |          |          |           |        |        |

| \$0170 -<br>\$017F    | CAN0TXFG                 | Read:<br>Write: | FOREGROUND TRANSMIT BUFFER see Table 1-2 |        |         |          |          |           |        |        |

#### Table 1-2 Detailed MSCAN Foreground Receive and Transmit Buffer Layout

|         |             | ,      |       |       |       |       |       |       |       |       |

|---------|-------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| Address | Name        |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|         | Extended ID | Read:  | ID28  | ID27  | ID26  | ID25  | ID24  | ID23  | ID22  | ID21  |

| \$xxx0  | Standard ID | Read:  | ID10  | ID9   | ID8   | ID7   | ID6   | ID5   | ID4   | ID3   |

|         | CANxRIDR0   | Write: |       |       |       |       |       |       |       |       |

|         | Extended ID | Read:  | ID20  | ID19  | ID18  | SRR=1 | IDE=1 | ID17  | ID16  | ID15  |

| \$xxx1  | Standard ID | Read:  | ID2   | ID1   | ID0   | RTR   | IDE=0 |       |       |       |

|         | CANxRIDR1   | Write: |       |       |       |       |       |       |       |       |

|         | Extended ID | Read:  | ID14  | ID13  | ID12  | ID11  | ID10  | ID9   | ID8   | ID7   |

| \$xxx2  | Standard ID | Read:  |       |       |       |       |       |       |       |       |

|         | CANxRIDR2   | Write: |       |       |       |       |       |       |       |       |

|         | Extended ID | Read:  | ID6   | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   | RTR   |

| \$xxx3  | Standard ID | Read:  |       |       |       |       |       |       |       |       |

|         | CANxRIDR3   | Write: |       |       |       |       |       |       |       |       |

| \$xxx4- | CANxRDSR0 - | Read:  | DB7   | DB6   | DB5   | DB4   | DB3   | DB2   | DB1   | DB0   |

| \$xxxB  | CANxRDSR7   | Write: |       |       |       |       |       |       |       |       |

|         |             |        |       |       |       |       |       |       |       |       |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide - V01.09

#### \$0180 - \$01BF

#### CAN1 (Motorola Scalable CAN - MSCAN)

| Address            | Name                     | [               | Bit 7                                   | Bit 6  | Bit 5   | Bit 4    | Bit 3     | Bit 2               | Bit 1  | Bit 0  |  |

|--------------------|--------------------------|-----------------|-----------------------------------------|--------|---------|----------|-----------|---------------------|--------|--------|--|

| \$0185             | CAN1RIER                 | Read:<br>Write: | WUPIE                                   | CSCIE  | RSTATE1 | RSTATE0  | TSTATE1   | TSTATE0             | OVRIE  | RXFIE  |  |

| \$0186             | CAN1TFLG                 | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | TXE2                | TXE1   | TXE0   |  |

| \$0187             | CAN1TIER                 | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | TXEIE2              | TXEIE1 | TXEIE0 |  |

| \$0188             | CAN1TARQ                 | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | ABTRQ2              | ABTRQ1 | ABTRQ0 |  |

| \$0189             | CAN1TAAK                 | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | ABTAK2              | ABTAK1 | ABTAK0 |  |

| \$018A             | CAN1TBSEL                | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | TX2                 | TX1    | TX0    |  |

| \$018B             | CAN1IDAC                 | Read:<br>Write: | 0                                       | 0      | IDAM1   | IDAM0    | 0         | IDHIT2              | IDHIT1 | IDHIT0 |  |

| \$018C             | Reserved                 | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | 0                   | 0      | 0      |  |

| \$018D             | Reserved                 | Read:<br>Write: | 0                                       | 0      | 0       | 0        | 0         | 0                   | 0      | 0      |  |

| \$018E             | CAN1RXERR                | Read:<br>Write: | RXERR7                                  | RXERR6 | RXERR5  | RXERR4   | RXERR3    | RXERR2              | RXERR1 | RXERR0 |  |

| \$018F             | CAN1TXERR                | Read:<br>Write: | TXERR7                                  | TXERR6 | TXERR5  | TXERR4   | TXERR3    | TXERR2              | TXERR1 | TXERR0 |  |

| \$0190 -<br>\$0193 | CAN1IDAR0 -<br>CAN1IDAR3 | Read:<br>Write: | AC7                                     | AC6    | AC5     | AC4      | AC3       | AC2                 | AC1    | AC0    |  |

| \$0194 -<br>\$0197 | CAN1IDMR0 -<br>CAN1IDMR3 | Read:<br>Write: | AM7                                     | AM6    | AM5     | AM4      | AM3       | AM2                 | AM1    | AM0    |  |

| \$0198 -<br>\$019B | CAN1IDAR4 -<br>CAN1IDAR7 | Read:<br>Write: | AC7                                     | AC6    | AC5     | AC4      | AC3       | AC2                 | AC1    | AC0    |  |

| \$019C -<br>\$019F | CAN1IDMR4 -<br>CAN1IDMR7 | Read:<br>Write: | AM7                                     | AM6    | AM5     | AM4      | AM3       | AM2                 | AM1    | AM0    |  |

| \$01A0 -<br>\$01AF | CANORXFG                 | Read:<br>Write: | FOREGROUND RECEIVE BUFFER see Table 1-2 |        |         |          |           |                     |        |        |  |

| \$01B0 -<br>\$01BF | CAN0TXFG                 | Read:<br>Write: |                                         | FOR    | EGROUNI | D TRANSM | IT BUFFEI | R see <b>Tabl</b> e | e 1-2  |        |  |

#### \$01C0 - \$01FF

#### Reserved

| Address           | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$01C0 - Deserved | Read:    | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |

| \$01FF            | Reserved | Write: |       |       |       |       |       |       |       |       |

#### \$0200 - \$023F

#### Reserved

| Address  | Name     | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$020C - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$023F   | Reserveu | Write: |       |       |       |       |       |       |       |       |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide — V01.09

#### \$0240 - \$027F

#### **PIM (Port Integration Module)**

| Address  | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0259   | PTIP     | Read:           | PTIP7 | PTIP6 | PTIP5 | PTIP4 | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

| ψ0200    | 1 111    | Write:          |       |       |       |       |       |       |       |       |

| \$025A   | DDRP     | Read:<br>Write: | DDRP7 | DDRP7 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| \$025B   | RDRP     | Read:<br>Write: | RDRP7 | RDRP6 | RDRP5 | RDRP4 | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| \$025C   | PERP     | Read:<br>Write: | PERP7 | PERP6 | PERP5 | PERP4 | PERP3 | PERP2 | PERP1 | PERP0 |

| \$025D   | PPSP     | Read:<br>Write: | PPSP7 | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSS0 |

| \$025E   | PIEP     | Read:<br>Write: | PIEP7 | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| \$025F   | PIFP     | Read:<br>Write: | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| \$0260   | PTH      | Read:<br>Write: | PTH7  | PTH6  | PTH5  | PTH4  | PTH3  | PTH2  | PTH1  | PTH0  |

| \$0261   | PTIH     | Read:<br>Write: | PTIH7 | PTIH6 | PTIH5 | PTIH4 | PTIH3 | PTIH2 | PTIH1 | PTIH0 |

| \$0262   | DDRH     | Read:<br>Write: | DDRH7 | DDRH7 | DDRH5 | DDRH4 | DDRH3 | DDRH2 | DDRH1 | DDRH0 |

| \$0263   | RDRH     | Read:<br>Write: | RDRH7 | RDRH6 | RDRH5 | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |

| \$0264   | PERH     | Read:<br>Write: | PERH7 | PERH6 | PERH5 | PERH4 | PERH3 | PERH2 | PERH1 | PERH0 |

| \$0265   | PPSH     | Read:<br>Write: | PPSH7 | PPSH6 | PPSH5 | PPSH4 | PPSH3 | PPSH2 | PPSH1 | PPSH0 |

| \$0266   | PIEH     | Read:<br>Write: | PIEH7 | PIEH6 | PIEH5 | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| \$0267   | PIFH     | Read:<br>Write: | PIFH7 | PIFH6 | PIFH5 | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

| \$0268   | PTJ      | Read:<br>Write: | PTJ7  | PTJ6  | 0     | 0     | 0     | 0     | PTJ1  | PTJ0  |

| \$0269   | PTIJ     | Read:<br>Write: | PTIJ7 | PTIJ6 | 0     | 0     | 0     | 0     | PTIJ1 | PTIJ0 |

| \$026A   | DDRJ     | Read:<br>Write: | DDRJ7 | DDRJ7 | 0     | 0     | 0     | 0     | DDRJ1 | DDRJ0 |

| \$026B   | RDRJ     | Read:<br>Write: | RDRJ7 | RDRJ6 | 0     | 0     | 0     | 0     | RDRJ1 | RDRJ0 |

| \$026C   | PERJ     | Read:<br>Write: | PERJ7 | PERJ6 | 0     | 0     | 0     | 0     | PERJ1 | PERJ0 |

| \$026D   | PPSJ     | Read:<br>Write: | PPSJ7 | PPSJ6 | 0     | 0     | 0     | 0     | PPSJ1 | PPSJ0 |

| \$026E   | PIEJ     | Read:<br>Write: | PIEJ7 | PIEJ6 | 0     | 0     | 0     | 0     | PIEJ1 | PIEJ0 |

| \$026F   | PIFJ     | Read:<br>Write: | PIFJ7 | PIFJ6 | 0     | 0     | 0     | 0     | PIFJ1 | PIFJ0 |

| \$0270 - | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$027F   |          | Write:          |       |       |       |       |       |       |       |       |

### 2.3.21 PH6 / KWH6 — Port H I/O Pin 6

PH6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

### 2.3.22 PH5 / KWH5 — Port H I/O Pin 5

PH5 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

### 2.3.23 PH4 / KWH4 -- Port H I/O Pin 2

PH4 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

### 2.3.24 PH3 / KWH3 / SS1 — Port H I/O Pin 3

PH3 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 1 (SPI1).

### 2.3.25 PH2 / KWH2 / SCK1 — Port H I/O Pin 2

PH2 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as serial clock pin SCK of the Serial Peripheral Interface 1 (SPI1).

### 2.3.26 PH1 / KWH1 / MOSI1 - Port H I/O Pin 1

PH1 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as master output (during master mode) or slave input pin (during slave mode) MOSI of the Serial Peripheral Interface 1 (SPI1).

### 2.3.27 PH0 / KWH0 / MISO1 — Port H I/O Pin 0

PH0 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as master input (during master mode) or slave output (during slave mode) pin MISO of the Serial Peripheral Interface 1 (SPI1).

### 2.3.28 PJ7 / KWJ7 / TXCAN4 / SCL - PORT J I/O Pin 7

PJ7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the transmit pin TXCAN for the Motorola Scalable Controller Area Network controller 4 (CAN4) or the serial clock pin SCL of the IIC module.

### 2.3.29 PJ6 / KWJ6 / RXCAN4 / SDA — PORT J I/O Pin 6

PJ6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as the receive pin RXCAN for the Motorola Scalable Controller Area Network controller 4 (CAN4) or the serial data pin SDA of the IIC module.

### 2.3.30 PJ[1:0] / KWJ[1:0] — Port J I/O Pins [1:0]

PJ1 and PJ0 are general purpose input or output pins. They can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

### 2.3.31 PK7 / ECS / ROMCTL - Port K I/O Pin 7

PK7 is a general purpose input or output pin. During MCU expanded modes of operation, this pin is used as the emulation chip select output ( $\overline{\text{ECS}}$ ). During MCU expanded modes of operation, this pin is used to enable the Flash EEPROM memory in the memory map (ROMCTL). At the rising edge of  $\overline{\text{RESET}}$ , the state of this pin is latched to the ROMON bit. For a complete list of modes refer to **4.2 Chip Configuration Summary**.

### 2.3.32 PK[5:0] / XADDR[19:14] — Port K I/O Pins [5:0]

PK5-PK0 are general purpose input or output pins. In MCU expanded modes of operation, these pins provide the expanded address XADDR[19:14] for the external bus.

### 2.3.33 PM7 / BF\_PSLM / TXCAN4 — Port M I/O Pin 7

PM7 is a general purpose input or output pin. It can be configured as the slot mismatch output pulse pin of Byteflight. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controllers 4 (CAN4).

### 2.3.34 PM6 / BF\_PERR / RXCAN4 — Port M I/O Pin 6

PM6 is a general purpose input or output pin. It can be configured as the illegal pulse or message format error output pulse pin of Byteflight. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controllers 4 (CAN4).

### 2.3.35 PM5 / BF\_PROK / TXCAN0 / TXCAN4 / SCK0 — Port M I/O Pin 5

PM5 is a general purpose input or output pin. It can be configured as the reception OK output pulse pin of Byteflight. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controllers 0 or 4 (CAN0 or CAN4). It can be configured as the serial clock pin SCK of the Serial Peripheral Interface 0 (SPI0).

### 2.4.4 VDDA, VSSA — Power Supply Pins for ATD and VREG

VDDA, VSSA are the power supply and ground input pins for the voltage regulator and the analog to digital converter. It also provides the reference for the internal voltage regulator. This allows the supply voltage to the ATD and the reference voltage to be bypassed independently.

### 2.4.5 VRH, VRL — ATD Reference Voltage Input Pins

VRH and VRL are the reference voltage input pins for the analog to digital converter.

### 2.4.6 VDDPLL, VSSPLL — Power Supply Pins for PLL

Provides operating voltage and ground for the Oscillator and the Phased-Locked Loop. This allows the supply voltage to the Oscillator and PLL to be bypassed independently. This 2.5V voltage is generated by the internal voltage regulator.

**NOTE:** No load allowed except for bypass capacitors.

### 2.4.7 VREGEN — On Chip Voltage Regulator Enable

Enables the internal 5V to 2.5V voltage regulator. If this pin is tied low, VDD1,2 and VDDPLL must be supplied externally.

## **Section 4 Modes of Operation**

## 4.1 Overview

Eight possible modes determine the operating configuration of the MC9S12DT128B. Each mode has an associated default memory map and external bus configuration controlled by a further pin.

Three low power modes exist for the device.

## 4.2 Chip Configuration Summary

The operating mode out of reset is determined by the states of the MODC, MODB, and MODA pins during reset (**Table 4-1**). The MODC, MODB, and MODA bits in the MODE register show the current operating mode and provide limited mode switching during operation. The states of the MODC, MODB, and MODA pins are latched into these bits on the rising edge of the reset signal. The ROMCTL signal allows the setting of the ROMON bit in the MISC register thus controlling whether the internal Flash is visible in the memory map. ROMON = 1 mean the Flash is visible in the memory map. The state of the ROMCTL pin is latched into the ROMON bit in the MISC register on the rising edge of the reset signal.

| BKGD =<br>MODC | PE6 =<br>MODB | PE5 =<br>MODA | PK7 =<br>ROMCTL | ROMON<br>Bit | Mode Description                                                                                                                    |

|----------------|---------------|---------------|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0              | 0             | 0             | х               | 1            | Special Single Chip, BDM allowed and ACTIVE. BDM is allowed in all other modes but a serial command is required to make BDM active. |

| 0              | 0             | 1             | Х               | 0            | Emulation Expanded Narrow, BDM allowed                                                                                              |

| 0              | 1             | 0             | Х               | 0            | Special Test (Expanded Wide), BDM allowed                                                                                           |

| 0              | 1             | 1             | Х               | 0            | Emulation Expanded Wide, BDM allowed                                                                                                |

| 1              | 0             | 0             | Х               | 1            | Normal Single Chip, BDM allowed                                                                                                     |

| 1              | 0             | 1             | 0               | 0            | Normal Expanded Narrow, RDM allowed                                                                                                 |

| 1              | 0             | 1             | 1               | 1            | Normal Expanded Narrow, BDM allowed                                                                                                 |

| 1              | 1             | 0             | х               | 1            | Special Peripheral; BDM allowed but bus operations would cause bus conflicts (must not be used)                                     |

| 1              | 1             | 1             | 0               | 0            | Normal Expanded Wide. BDM allowed                                                                                                   |

|                | I             |               | 1               | 1            | - Normal Expanded Wide, DDW allowed                                                                                                 |

For further explanation on the modes refer to the Core User Guide.

#### Table 4-2 Clock Selection Based on PE7

| PE7 = XCLKS | Description                               |

|-------------|-------------------------------------------|

| 1           | Colpitts Oscillator selected              |

| 0           | Pierce Oscillator/external clock selected |

## Section 6 HCS12 Core Block Description

Consult the HCS12 Core User Guide for information about the HCS12 core modules, i.e. central processing unit (CPU), interrupt module (INT), module mapping control module (MMC), multiplexed external bus interface (MEBI), breakpoint module (BKP) and background debug mode module (BDM).

## 6.1 Device-specific information

When the BDM section of S12 Core User Guide refers to *alternate clock* this is equivalent to *oscillator clock*.

## Section 7 Clock and Reset Generator (CRG) Block Description

Consult the CRG Block User Guide for information about the Clock and Reset Generator module.

### 7.1 Device-specific information

## 7.1.1 XCLKS

The XCLKS input signal is active low (see 2.3.12 PE7 / NOACC / XCLKS — Port E I/O Pin 7).

## Section 8 Enhanced Capture Timer (ECT) Block Description

Consult the ECT\_16B8C Block User Guide for information about the Enhanced Capture Timer module. When the ECT\_16B8C Block User Guide refers to *freeze mode* this is equivalent to *active BDM mode*.

## Section 9 Analog to Digital Converter (ATD) Block Description

There are two Analog to Digital Converters (ATD1 and ATD0) implemented on the MC9S12DT128B. Consult the ATD\_10B8C Block User Guide for information about each Analog to Digital Converter module. When the ATD\_10B8C Block User Guide refers to *freeze mode* this is equivalent to *active BDM mode*.

## Section 10 Inter-IC Bus (IIC) Block Description

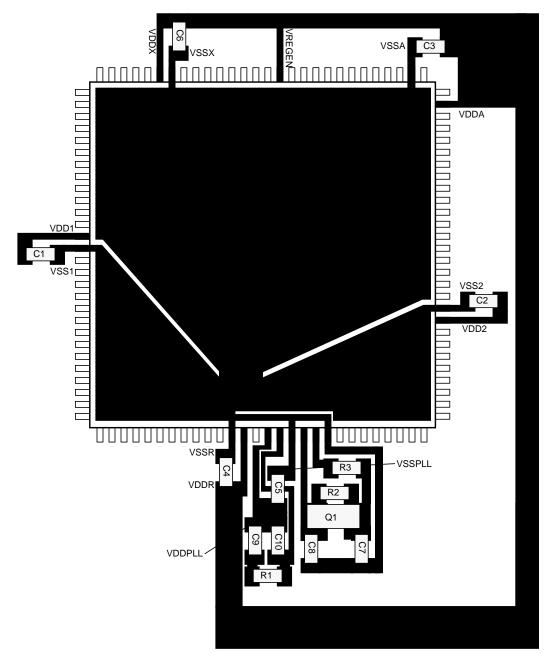

Figure 22-3 Recommended PCB Layout for 112LQFP Pierce Oscillator

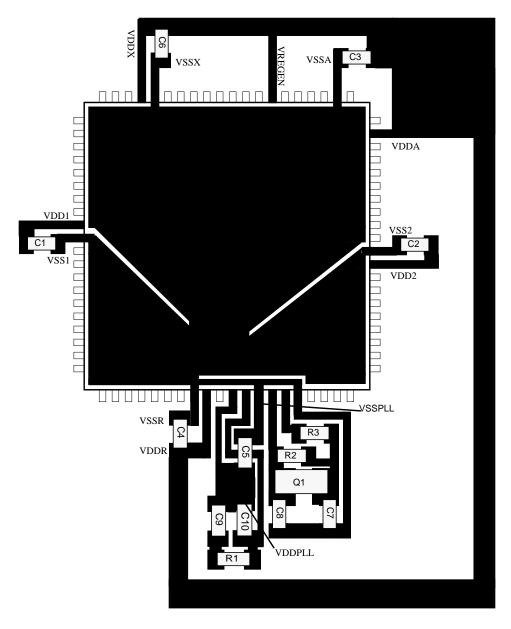

Figure 22-4 Recommended PCB Layout for 80QFP Pierce Oscillator

### A.1.5 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only. A functional operation under or outside those maxima is not guaranteed. Stress beyond those limits may affect the reliability or cause permanent damage of the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., either V<sub>SS5</sub> or V<sub>DD5</sub>).

| Num | Rating                                                                                  | Symbol                           | Min   | Max  | Unit |

|-----|-----------------------------------------------------------------------------------------|----------------------------------|-------|------|------|

| 1   | I/O, Regulator and Analog Supply Voltage                                                | V <sub>DD5</sub>                 | -0.3  | 6.0  | V    |

| 2   | Digital Logic Supply Voltage <sup>2</sup>                                               | V <sub>DD</sub>                  | -0.3  | 3.0  | V    |

| 3   | PLL Supply Voltage <sup>2</sup>                                                         | V <sub>DDPLL</sub>               | -0.3  | 3.0  | V    |

| 4   | Voltage difference VDDX to VDDR and VDDA                                                | $\Delta_{VDDX}$                  | -0.3  | 0.3  | V    |

| 5   | Voltage difference VSSX to VSSR and VSSA                                                | Δ <sub>VSSX</sub>                | -0.3  | 0.3  | V    |

| 6   | Digital I/O Input Voltage                                                               | V <sub>IN</sub>                  | -0.3  | 6.0  | V    |

| 7   | Analog Reference                                                                        | V <sub>RH,</sub> V <sub>RL</sub> | -0.3  | 6.0  | V    |

| 8   | XFC, EXTAL, XTAL inputs                                                                 | V <sub>ILV</sub>                 | -0.3  | 3.0  | V    |

| 9   | TEST input                                                                              | V <sub>TEST</sub>                | -0.3  | 10.0 | V    |

| 10  | Instantaneous Maximum Current<br>Single pin limit for all digital I/O pins <sup>3</sup> | I <sub>D</sub>                   | -25   | +25  | mA   |

| 11  | Instantaneous Maximum Current<br>Single pin limit for XFC, EXTAL, XTAL <sup>4</sup>     | I <sub>DL</sub>                  | -25   | +25  | mA   |

| 12  | Instantaneous Maximum Current<br>Single pin limit for TEST <sup>5</sup>                 | I <sub>DT</sub>                  | -0.25 | 0    | mA   |

| 13  | Storage Temperature Range                                                               | T <sub>stg</sub>                 | - 65  | 155  | °C   |

| Table A-1 | Absolute | Maximum | Ratings <sup>1</sup> |

|-----------|----------|---------|----------------------|

|-----------|----------|---------|----------------------|

NOTES:

1. Beyond absolute maximum ratings device might be damaged.

2. The device contains an internal voltage regulator to generate the logic and PLL supply out of the I/O supply. The absolute maximum ratings apply when the device is powered from an external source.

3. All digital I/O pins are internally clamped to  $V_{SSX}$  and  $V_{DDX}$ ,  $V_{SSR}$  and  $V_{DDR}$  or  $V_{SSA}$  and  $V_{DDA}$ . 4. Those pins are internally clamped to  $V_{SSPLL}$  and  $V_{DDPLL}$ . 5. This pin is clamped low to  $V_{SSPLL}$ , but not clamped high. This pin must be tied low in applications.

### A.1.6 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 Stress test qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model.

### A.2 ATD Characteristics

This section describes the characteristics of the analog to digital converter.

### A.2.1 ATD Operating Characteristics

The Table A-8 shows conditions under which the ATD operates.

The following constraints exist to obtain full-scale, full range results:

$V_{SSA} \le V_{RL} \le V_{IN} \le V_{RH} \le V_{DDA}$ . This constraint exists since the sample buffer amplifier can not drive beyond the power supply levels that it ties to. If the input level goes outside of this range it will effectively be clipped.

| Condit | tions | s are shown in Table A-4 unless otherwise noted                                                                  |                                          |                                         |      |                                         |              |

|--------|-------|------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|------|-----------------------------------------|--------------|

| Num    | С     | Rating                                                                                                           | Symbol                                   | Min                                     | Тур  | Max                                     | Unit         |

| 1      | D     | Reference Potential<br>Low<br>High                                                                               | V <sub>RL</sub><br>V <sub>RH</sub>       | V <sub>SSA</sub><br>V <sub>DDA</sub> /2 |      | V <sub>DDA</sub> /2<br>V <sub>DDA</sub> | V<br>V       |

| 2      | С     | Differential Reference Voltage <sup>1</sup>                                                                      | $V_{RH}-V_{RL}$                          | 4.50                                    | 5.00 | 5.25                                    | V            |

| 3      | D     | ATD Clock Frequency                                                                                              | f <sub>ATDCLK</sub>                      | 0.5                                     |      | 2.0                                     | MHz          |

| 4      | D     | ATD 10-Bit Conversion Period<br>Clock Cycles <sup>2</sup><br>Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub>  |                                          | 14<br>7                                 |      | 28<br>14                                | Cycles<br>μs |

| 5      | D     | ATD 8-Bit Conversion Period<br>Clock Cycles <sup>(2)</sup><br>Conv, Time at 2.0MHz ATD Clock f <sub>ATDCLK</sub> | N <sub>CONV8</sub><br>T <sub>CONV8</sub> | 12<br>6                                 |      | 26<br>13                                | Cycles<br>μs |

| 6      | D     | Stop Recovery Time (V <sub>DDA</sub> =5.0 Volts)                                                                 | t <sub>SR</sub>                          |                                         |      | 20                                      | μs           |

| 7      | Р     | Reference Supply current (Both ATD modules on)                                                                   | I <sub>REF</sub>                         |                                         |      | 0.75                                    | mA           |

| 8      | Р     | Reference Supply current (Only one ATD module on)                                                                | I <sub>REF</sub>                         |                                         |      | 0.375                                   | mA           |

#### Table A-8 ATD Operating Characteristics

NOTES:

1. Full accuracy is not guaranteed when differential voltage is less than 4.50V

2. The minimum time assumes a final sample period of 2 ATD clocks cycles while the maximum time assumes a final sample period of 16 ATD clocks.

### A.2.2 Factors influencing accuracy

Three factors – source resistance, source capacitance and current injection – have an influence on the accuracy of the ATD.

### A.2.2.1 Source Resistance:

Due to the input pin leakage current as specified in **Table A-6** in conjunction with the source resistance there will be a voltage drop from the signal source to the ATD input. The maximum source resistance  $R_S$

# MC9S12DT128B Device User Guide \_\_\_\_\_ VOT.09 Semiconductor, Inc.

specifies results in an error of less than 1/2 LSB (2.5mV) at the maximum leakage current. If device or operating conditions are less than worst case or leakage-induced error is acceptable, larger values of source resistance is allowed.

#### A.2.2.2 Source capacitance

When sampling an additional internal capacitor is switched to the input. This can cause a voltage drop due to charge sharing with the external and the pin capacitance. For a maximum sampling error of the input voltage  $\leq 1LSB$ , then the external filter capacitor,  $C_f \geq 1024 * (C_{INS} - C_{INN})$ .

#### A.2.2.3 Current injection

There are two cases to consider.

- 1. A current is injected into the channel being converted. The channel being stressed has conversion values of 3FF (FF in 8-bit mode) for analog inputs greater than  $V_{RH}$  and 000 for values less than  $V_{RL}$  unless the current is higher than specified as disruptive conditions.

- 2. Current is injected into pins in the neighborhood of the channel being converted. A portion of this current is picked up by the channel (coupling ratio K), This additional current impacts the accuracy of the conversion depending on the source resistance.

The additional input voltage error on the converted channel can be calculated as  $V_{ERR} = K * R_S * I_{INJ}$ , with  $I_{INJ}$  being the sum of the currents injected into the two pins adjacent to the converted channe

| Condit | tion | s are shown in Table A-4 unless otherwise noted     |                                      |      |     |                  |      |

|--------|------|-----------------------------------------------------|--------------------------------------|------|-----|------------------|------|

| Num    | С    | Rating                                              | Symbol                               | Min  | Тур | Max              | Unit |

| 1      | С    | Max input Source Resistance                         | R <sub>S</sub>                       | -    | -   | 1                | KΩ   |

| 2      | т    | Total Input Capacitance<br>Non Sampling<br>Sampling | C <sub>INN</sub><br>C <sub>INS</sub> |      |     | 10<br>22         | pF   |

| 3      | С    | Disruptive Analog Input Current                     | I <sub>NA</sub>                      | -2.5 |     | 2.5              | mA   |

| 4      | С    | Coupling Ratio positive current injection           | K <sub>p</sub>                       |      |     | 10 <sup>-4</sup> | A/A  |

| 5      | С    | Coupling Ratio negative current injection           | K <sub>n</sub>                       |      |     | 10 <sup>-2</sup> | A/A  |

#### Table A-9 ATD Electrical Characteristics

This is very important to notice with respect to timers, serial modules where a pre-scaler will eliminate the effect of the jitter to a large extent.

| Condit | ions | s are shown in Table A-4 unless otherwise noted            |                    |     |      |      |                |

|--------|------|------------------------------------------------------------|--------------------|-----|------|------|----------------|

| Num    | С    | Rating                                                     | Symbol             | Min | Тур  | Max  | Unit           |

| 1      | Р    | Self Clock Mode frequency                                  | f <sub>SCM</sub>   | 1   |      | 5.5  | MHz            |

| 2      | D    | VCO locking range                                          | f <sub>VCO</sub>   | 8   |      | 50   | MHz            |

| 3      | D    | Lock Detector transition from Acquisition to Tracking mode | $ \Delta_{trk} $   | 3   |      | 4    | % <sup>1</sup> |

| 4      | D    | Lock Detection                                             | $ \Delta_{Lock} $  | 0   |      | 1.5  | %(1)           |

| 5      | D    | Un-Lock Detection                                          | $ \Delta_{unl} $   | 0.5 |      | 2.5  | %(1)           |

| 6      | D    | Lock Detector transition from Tracking to Acquisition mode | Δ <sub>unt</sub>   | 6   |      | 8    | %(1)           |

| 7      | С    | PLLON Total Stabilization delay (Auto Mode) <sup>2</sup>   | t <sub>stab</sub>  |     | 0.5  |      | ms             |

| 8      | D    | PLLON Acquisition mode stabilization delay <sup>(2)</sup>  | t <sub>acq</sub>   |     | 0.3  |      | ms             |

| 9      | D    | PLLON Tracking mode stabilization delay <sup>(2)</sup>     | t <sub>al</sub>    |     | 0.2  |      | ms             |

| 10     | D    | Fitting parameter VCO loop gain                            | K <sub>1</sub>     |     | -120 |      | MHz/V          |

| 11     | D    | Fitting parameter VCO loop frequency                       | f <sub>1</sub>     |     | 75   |      | MHz            |

| 12     | D    | Charge pump current acquisition mode                       | ∣i <sub>ch</sub> ∣ |     | 38.5 |      | μA             |

| 13     | D    | Charge pump current tracking mode                          | ∣i <sub>ch</sub> ∣ |     | 3.5  |      | μA             |

| 14     | С    | Jitter fit parameter 1 <sup>(2)</sup>                      | j <sub>1</sub>     |     |      | 1.1  | %              |

| 15     | С    | Jitter fit parameter 2 <sup>(2)</sup>                      | j <sub>2</sub>     |     |      | 0.13 | %              |

NOTES:

1. % deviation from target frequency

2. f<sub>OSC</sub> = 4MHz, f<sub>BUS</sub> = 25MHz equivalent f<sub>VCO</sub> = 50MHz: REFDV = #\$03, SYNR = #\$018, Cs = 4.7nF, Cp = 470pF, Rs = 10KΩ.