# E·XFL

#### Motorola - MC9S12DT128CPV Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Active                                                      |

| Core Processor             | HCS12                                                       |

| Core Size                  | 16-Bit                                                      |

| Speed                      | 25MHz                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                          |

| Peripherals                | PWM, WDT                                                    |

| Number of I/O              | 91                                                          |

| Program Memory Size        | 128KB (128K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 8K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 5.25V                                               |

| Data Converters            | A/D 16x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

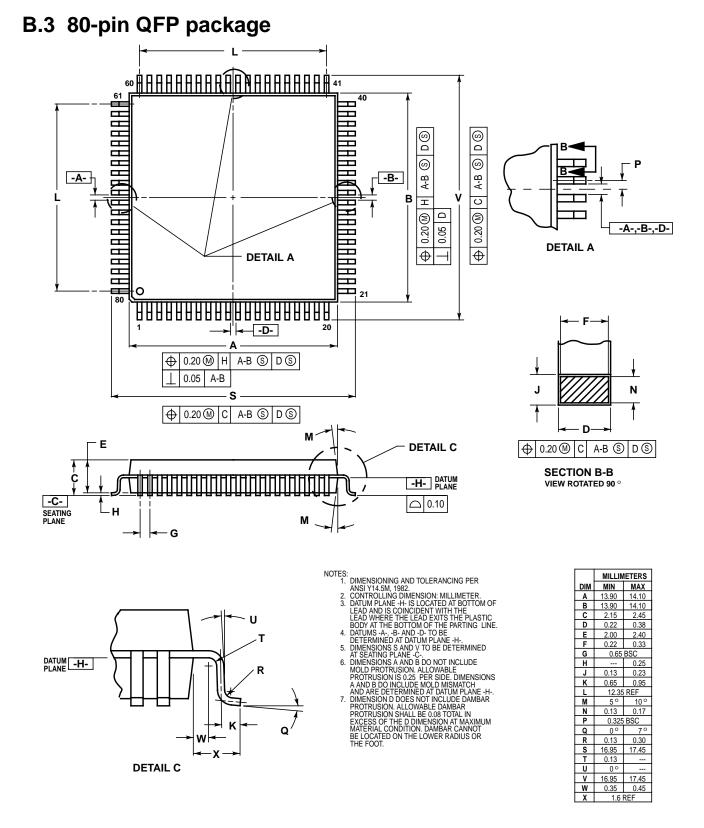

| Package / Case             | 112-LQFP                                                    |

| Supplier Device Package    | 112-LQFP (20x20)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc9s12dt128cpv |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Section 1 Introduction**

## 1.1 Overview

The MC9S12DT128B microcontroller unit (MCU) is a 16-bit device composed of standard on-chip peripherals including a 16-bit central processing unit (HCS12 CPU), 128K bytes of Flash EEPROM, 8K bytes of RAM, 2K bytes of EEPROM, two asynchronous serial communications interfaces (SCI), two serial peripheral interfaces (SPI), an 8-channel IC/OC enhanced capture timer, two 8-channel, 10-bit analog-to-digital converters (ADC), an 8-channel pulse-width modulator (PWM), a digital Byte Data Link Controller (BDLC), 29 discrete digital I/O channels (Port A, Port B, Port K and Port E), 20 discrete digital I/O lines with interrupt and wakeup capability, three CAN 2.0 A, B software compatible modules (MSCAN12), a Byteflight module and an Inter-IC Bus. The MC9S12DT128B has full 16-bit data paths throughout. However, the external bus can operate in an 8-bit narrow mode so single 8-bit wide memory can be interfaced for lower cost systems. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements.

## **1.2 Features**

- HCS12 Core

- 16-bit HCS12 CPU

- i. Upward compatible with M68HC11 instruction set

- ii. Interrupt stacking and programmer's model identical to M68HC11

- iii.20-bit ALU

- iv. Instruction queue

- v. Enhanced indexed addressing

- MEBI (Multiplexed External Bus Interface)

- MMC (Module Mapping Control)

- INT (Interrupt control)

- BKP (Breakpoints)

- BDM (Background Debug Mode)

- CRG (Clock and Reset Generator)

- Choice of low current Colpitts oscillator or standard Pierce Oscillator

- PLL

- COP watchdog

- real time interrupt

- clock monitor

- 8-bit and 4-bit ports with interrupt functionality

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide - V01.09

#### \$00E8 - \$00EF

#### **BDLC (Byte Level Data Link Controller J1850)**

| Address      | Name     |        | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  |

|--------------|----------|--------|-------|---------|-------|-------|-------|-------|--------|--------|

| \$00E8       | DLCBCR1  | Read:  | IMSG  | CLKS    | 0     | 0     | 0     | 0     | IE     | WCM    |

| <b>WOOLO</b> | DEODOINI | Write: |       | OLINO   |       |       |       |       |        | WOW    |

| \$00E9       | DLCBSVR  | Read:  | 0     | 0       | 13    | 12    | l1    | 10    | 0      | 0      |

| \$00E9       | DECROVIC | Write: |       |         |       |       |       |       |        |        |

| \$00EA       | DLCBCR2  | Read:  | SMRST | DLOOP   | RX4XE | NBFS  | TEOD  | TSIFR | TMIFR1 | TMIFR0 |

| <b>WOLA</b>  | DLCDCRZ  | Write: |       | DLOOI   | NA4AL | NDI 5 | ILOD  |       |        |        |

| \$00EB       | DLCBDR   | Read:  | D7    | D6      | D5    | D4    | D3    | D2    | D1     | D0     |

| <b>WOLD</b>  | DECODIN  | Write: | וט    | DO      | 5     | D4    | 5     | DZ    |        | 00     |

| \$00EC       | DLCBARD  | Read:  | 0     | RXPOL   | 0     | 0     | BO3   | BO2   | BO1    | BO0    |

| <b>WOLC</b>  | DECOARD  | Write: |       | INAL OF |       |       | 005   | 002   | DOT    | DOU    |

| \$00ED       | DLCBRSR  | Read:  | 0     | 0       | R5    | R4    | R3    | R2    | R1     | R0     |

| <b>JUDED</b> | DLCBRSR  | Write: |       |         | КJ    | Ν4    | N3    | NΖ    |        | ΝU     |

| \$00EE       | DLCSCR   | Read:  | 0     | 0       | 0     | BDLCE | 0     | 0     | 0      | 0      |

| φυυεε        | DLUGUK   | Write: |       |         |       | BULCE |       |       |        |        |

| \$00EF       | DLCBSTAT | Read:  | 0     | 0       | 0     | 0     | 0     | 0     | 0      | IDLE   |

| φυυεγ        | DLCBSTAT | Write: |       |         |       |       |       |       |        |        |

\$00F0 - \$00F7

#### **SPI1 (Serial Peripheral Interface)**

| Address | Name     | [               | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1   | Bit 0 |

|---------|----------|-----------------|-------|-------|-------|--------|---------|-------|---------|-------|

| \$00F0  | SPI1CR1  | Read:<br>Write: | SPIE  | SPE   | SPTIE | MSTR   | CPOL    | CPHA  | SSOE    | LSBFE |

| \$00F1  | SPI1CR2  | Read:<br>Write: | 0     | 0     | 0     | MODFEN | BIDIROE | 0     | SPISWAI | SPC0  |

| \$00F2  | SPI1BR   | Read:<br>Write: | 0     | SPPR2 | SPPR1 | SPPR0  | 0       | SPR2  | SPR1    | SPR0  |

| \$00F3  | SPI1SR   | Read:<br>Write: | SPIF  | 0     | SPTEF | MODF   | 0       | 0     | 0       | 0     |

| \$00F4  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

| \$00F5  | SPI1DR   | Read:<br>Write: | Bit7  | 6     | 5     | 4      | 3       | 2     | 1       | Bit0  |

| \$00F6  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

| \$00F7  | Reserved | Read:<br>Write: | 0     | 0     | 0     | 0      | 0       | 0     | 0       | 0     |

#### \$00F8 - \$00FF

#### Reserved

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$00F8 - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$00FF   | Reserved | Write: |       |       |       |       |       |       |       |       |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide - V01.09

#### \$0110 - \$011B

## EEPROM Control Register (eets2k)

| Address | Name    |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| \$0119  | EADDRLO | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| \$011A  | EDATAHI | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| \$011B  | EDATALO | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

#### \$011C - \$011F

#### **Reserved for RAM Control Register**

| Address  | Name     | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$011C - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$011F   | Reserveu | Write: |       |       |       |       |       |       |       |       |

\$0120 - \$013F

#### ATD1 (Analog to Digital Converter 10 Bit 8 Channel)

| S0120         ATD1CTL0         Read:<br>Write:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address       | Name             | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|--------|-------|-------|-------|---------|--------|-------|-------|-------|

| S0121         ATD1CTL1         Read<br>Write<br>Write         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ¢0120         |                  | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| SU121         AIDICILI         Write:         ABDPU         AFFC         AWAI         ETRIGLE         ETRIGP         ETRIG         ASCIF           \$0122         ATD1CTL2         Read:<br>Write         0         S8C         S4C         S2C         S1C         FIFO         FRZ1         FRZ0           \$0123         ATD1CTL3         Read:<br>Write         0         S8C         S4C         S2C         S1C         FIFO         FRZ1         FRZ0           \$0124         ATD1CTL4         Read:<br>Write         SRES8         SMP1         SMP0         PRS4         PRS3         PRS2         PRS1         PRS0           \$0125         ATD1CTL5         Read:<br>Write         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0126         ATD1STAT0         Read:<br>Write         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0127         Reserved         Read:<br>Write         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | φ0120         | AIDICILU         | Write: |       |       |       |         |        |       |       |       |

| \$0122         ATD1CTL2         Read:<br>Write:         ADPU         AFFC         AWAI         ETRIGLE         ETRIGP         ETRIG         ASCIE         ASCIF           \$0123         ATD1CTL3         Read:<br>Write:         0         S8C         S4C         S2C         S1C         FIFO         FRZ1         FRZ0           \$0124         ATD1CTL4         Read:<br>Write:         SRES8         SMP1         SMP0         PRS4         PRS3         PRS2         PRS1         PRS0           \$0125         ATD1CTL4         Read:<br>Write:         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0126         ATD1STAT0         Read:<br>Write:         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0126         ATD1STAT0         Read:         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0127         Reserved         Read:         O         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         SC         SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ¢0404         |                  | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| S0122         AIDTCTL2         Write         ADPU         AFFC         AWAI         ETRIGLE         ETRIG         ASCIE           \$0123         ATD1CTL3         Write         0         S8C         S4C         S2C         S1C         FIFO         FRZ1         FRZ0           \$0124         ATD1CTL4         Read:         0         S8C         S4C         S2C         S1C         FIFO         FRZ1         FRZ0           \$0124         ATD1CTL4         Read:         SRES8         SMP1         SMP0         PRS4         PRS3         PRS2         PRS1         PRS0           \$0125         ATD1CTL5         Read:         SRES8         SMP1         SMP0         PRS4         PRS3         PRS2         PRS1         PRS0           \$0126         ATD1STATO         Read:         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0126         ATD1STATO         Read:         D         0         0         0         CO         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         CC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | \$0121        | AIDICILI         | Write: |       |       |       |         |        |       |       |       |

| S0123       AIDICIL3       Write:<br>Read:<br>Write:       S8C       S4C       S2C       S1C       FIFO       FR21       FR20         \$0124       ATD1CTL4       Read:<br>Write:       SRES8       SMP1       SMP0       PRS4       PRS3       PRS2       PRS1       PRS0         \$0125       ATD1CTL5       Read:<br>Write:       DJM       DSGN       SCAN       MULT       0       CC       CB       CA         \$0126       ATD1STAT0       Read:<br>Write:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td>\$0122</td> <td>ATD1CTL2</td> <td></td> <td>ADPU</td> <td>AFFC</td> <td>AWAI</td> <td>ETRIGLE</td> <td>ETRIGP</td> <td>ETRIG</td> <td>ASCIE</td> <td>ASCIF</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$0122        | ATD1CTL2         |        | ADPU  | AFFC  | AWAI  | ETRIGLE | ETRIGP | ETRIG | ASCIE | ASCIF |

| S0124         AIDICIL4         Write:         SRES8         SMP1         SMP0         PRS4         PRS3         PRS2         PRS1         PRS0           \$0125         ATD1CTL5         Read:<br>Write:         DJM         DSGN         SCAN         MULT         0         CC         CB         CA           \$0126         ATD1STAT0         Read:<br>Write:         SCF         0         ETORF         FIFOR         0         CC2         CC1         CC0           \$0127         Reserved         Read:<br>Write:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>\$0123</td> <td>ATD1CTL3</td> <td></td> <td>0</td> <td>S8C</td> <td>S4C</td> <td>S2C</td> <td>S1C</td> <td>FIFO</td> <td>FRZ1</td> <td>FRZ0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | \$0123        | ATD1CTL3         |        | 0     | S8C   | S4C   | S2C     | S1C    | FIFO  | FRZ1  | FRZ0  |

| \$0125       AIDICILS       Write:       DJM       DSGN       SCAN       MULI       CC       CB       CA         \$0126       ATD1STAT0       Read:       SCF       0       ETORF       FIFOR       0       CC2       CC1       CC0         \$0127       Reserved       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$0124        | ATD1CTL4         |        | SRES8 | SMP1  | SMP0  | PRS4    | PRS3   | PRS2  | PRS1  | PRS0  |

| \$0126       AIDISIAIO       Write:       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td>\$0125</td> <td>ATD1CTL5</td> <td></td> <td>DJM</td> <td>DSGN</td> <td>SCAN</td> <td>MULT</td> <td>0</td> <td>СС</td> <td>СВ</td> <td>CA</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | \$0125        | ATD1CTL5         |        | DJM   | DSGN  | SCAN  | MULT    | 0      | СС    | СВ    | CA    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | \$0126        | ΔΤΟ19ΤΔΤΟ        | Read:  | SCF   | 0     | ETORF | FIFOR   | 0      | CC2   | CC1   | CC0   |

| \$0127       Reserved       Write:       Image: constraint of the served       Write:       Image: constraint of the served       Write:       Image: constraint of the served       Image: constraint of the                                                                                                                                                                                                                                                                                                                                                                                                   | φ0120         | AIDISIAIU        | Write: |       |       |       |         |        |       |       |       |

| Write:       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ¢0107         | <b>Descrived</b> | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0128       ATD1TEST0       Write:       Image: Constraint of the second seco         | φ012 <i>1</i> | Reserveu         | Write: |       |       |       |         |        |       |       |       |

| Write:       Read:       0       0       0       0       0       SC         \$0129       ATD1TEST1       Read:       0       0       0       0       0       0       SC         \$012A       Reserved       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ¢0128         |                  | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$0129       AIDTLESTI       Write:       Image: Constraint of the second seco         | ψ0120         | AIDIILSIU        | Write: |       |       |       |         |        |       |       |       |

| Write:         Read:         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \$012Q        |                  | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 50    |

| \$012A       Reserved       Write:       Image: Constraint of the second secon         | ψ0129         | AIDHESH          | Write: |       |       |       |         |        | 0     |       | 30    |

| Write:       Read:       CCF7       CCF6       CCF3       CCF3       CCF2       CCF1       CCF0         \$012B       ATD1STAT1       Read:       CCF7       CCF6       CCF5       CCF4       CCF3       CCF2       CCF1       CCF0         \$012C       Reserved       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0 <td>\$012A</td> <td>Reserved</td> <td>Read:</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$012A        | Reserved         | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$012B       ATD1STAT1       Write:       Write:       Image: Constraint of the second sec                  | ψυτζΑ         | iteseiveu        | Write: |       |       |       |         |        |       |       |       |

| Write:       Read:       0       0       0       0       0       0       0       0       0         \$012C       Reserved       Read:       0       0       0       0       0       0       0       0       0       0       0       0         \$012D       ATD1DIEN       Read:       Bit 7       6       5       4       3       2       1       Bit 0         \$012E       Reserved       Read:       0       0       0       0       0       0       0       0         \$012E       Reserved       Read:       0       0       0       0       0       0       0       0       0       0         \$012E       Reserved       Read:       Bit 7       6       5       4       3       2       1       Bit 0         \$012E       PORTAD1       Read:       Bit 7       6       5       4       3       2       1       BIT 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | \$012B        |                  |        | CCF7  | CCF6  | CCF5  | CCF4    | CCF3   | CCF2  | CCF1  | CCF0  |

| \$012C       Reserved       Write:       Write:       Image: Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ψ012D         | AIDIGIAII        | Write: |       |       |       |         |        |       |       |       |

| Write:       Read:       Bit 7       6       5       4       3       2       1       Bit 0         \$012D       ATD1DIEN       Read:       Write:       Bit 7       6       5       4       3       2       1       Bit 0         \$012E       Reserved       Read:       0       0       0       0       0       0       0       0         \$012E       Reserved       Read:       Bit 7       6       5       4       3       2       1       Bit 0         \$012E       Reserved       Read:       0       0       0       0       0       0       0         \$012E       PORTAD1       Read:       Bit7       6       5       4       3       2       1       BIT 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | \$012C        | Received         | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

| \$012D       AIDIDIEN       Write:       Bit 7       6       5       4       3       2       1       Bit 0         \$012E       Reserved       Read:       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | φυιζυ         | IVESEI VEU       | Write: |       |       |       |         |        |       |       |       |

| \$012E         Reserved         Write:         Image: Constant of the second se | \$012D        | ATD1DIEN         |        | Bit 7 | 6     | 5     | 4       | 3      | 2     | 1     | Bit 0 |

| Write:         Read:         Bit7         6         5         4         3         2         1         BIT 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ¢012E         | Basanuad         | Read:  | 0     | 0     | 0     | 0       | 0      | 0     | 0     | 0     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Φ012E         | Reserved         | Write: |       |       |       |         |        |       |       |       |

| Write:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ¢012E         |                  | Read:  | Bit7  | 6     | 5     | 4       | 3      | 2     | 1     | BIT 0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ΦU12F         | PURIADI          | Write: |       |       |       |         |        |       |       |       |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide - V01.09

#### \$0180 - \$01BF

### CAN1 (Motorola Scalable CAN - MSCAN)

| Address            | Name                     | [               | Bit 7  | Bit 6  | Bit 5   | Bit 4    | Bit 3     | Bit 2               | Bit 1  | Bit 0  |

|--------------------|--------------------------|-----------------|--------|--------|---------|----------|-----------|---------------------|--------|--------|

| \$0185             | CAN1RIER                 | Read:<br>Write: | WUPIE  | CSCIE  | RSTATE1 | RSTATE0  | TSTATE1   | TSTATE0             | OVRIE  | RXFIE  |

| \$0186             | CAN1TFLG                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | TXE2                | TXE1   | TXE0   |

| \$0187             | CAN1TIER                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | TXEIE2              | TXEIE1 | TXEIE0 |

| \$0188             | CAN1TARQ                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | ABTRQ2              | ABTRQ1 | ABTRQ0 |

| \$0189             | CAN1TAAK                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | ABTAK2              | ABTAK1 | ABTAK0 |

| \$018A             | CAN1TBSEL                | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | TX2                 | TX1    | TX0    |

| \$018B             | CAN1IDAC                 | Read:<br>Write: | 0      | 0      | IDAM1   | IDAM0    | 0         | IDHIT2              | IDHIT1 | IDHIT0 |

| \$018C             | Reserved                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | 0                   | 0      | 0      |

| \$018D             | Reserved                 | Read:<br>Write: | 0      | 0      | 0       | 0        | 0         | 0                   | 0      | 0      |

| \$018E             | CAN1RXERR                | Read:<br>Write: | RXERR7 | RXERR6 | RXERR5  | RXERR4   | RXERR3    | RXERR2              | RXERR1 | RXERR0 |

| \$018F             | CAN1TXERR                | Read:<br>Write: | TXERR7 | TXERR6 | TXERR5  | TXERR4   | TXERR3    | TXERR2              | TXERR1 | TXERR0 |

| \$0190 -<br>\$0193 | CAN1IDAR0 -<br>CAN1IDAR3 | Read:<br>Write: | AC7    | AC6    | AC5     | AC4      | AC3       | AC2                 | AC1    | AC0    |

| \$0194 -<br>\$0197 | CAN1IDMR0 -<br>CAN1IDMR3 | Read:<br>Write: | AM7    | AM6    | AM5     | AM4      | AM3       | AM2                 | AM1    | AM0    |

| \$0198 -<br>\$019B | CAN1IDAR4 -<br>CAN1IDAR7 | Read:<br>Write: | AC7    | AC6    | AC5     | AC4      | AC3       | AC2                 | AC1    | AC0    |

| \$019C -<br>\$019F | CAN1IDMR4 -<br>CAN1IDMR7 | Read:<br>Write: | AM7    | AM6    | AM5     | AM4      | AM3       | AM2                 | AM1    | AM0    |

| \$01A0 -<br>\$01AF | CANORXFG                 | Read:<br>Write: |        | FOI    | REGROUN | D RECEIV | E BUFFER  | see Table           | 1-2    |        |

| \$01B0 -<br>\$01BF | CAN0TXFG                 | Read:<br>Write: |        | FOR    | EGROUNI | D TRANSM | IT BUFFEI | R see <b>Tabl</b> e | e 1-2  |        |

#### \$01C0 - \$01FF

#### Reserved

| Address  | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$01C0 - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$01FF   | Reserveu | Write: |       |       |       |       |       |       |       |       |

#### \$0200 - \$023F

#### Reserved

| Address  | Name     | [      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$020C - | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$023F   | Reserveu | Write: |       |       |       |       |       |       |       |       |

#### Freescale Semiconductor, Inc. MC9S12D1128B Device User Guide — V01.09

#### \$0240 - \$027F

#### **PIM (Port Integration Module)**

| Address  | Name     |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|----------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0259   | PTIP     | Read:           | PTIP7 | PTIP6 | PTIP5 | PTIP4 | PTIP3 | PTIP2 | PTIP1 | PTIP0 |

| ψ0200    | 1 111    | Write:          |       |       |       |       |       |       |       |       |

| \$025A   | DDRP     | Read:<br>Write: | DDRP7 | DDRP7 | DDRP5 | DDRP4 | DDRP3 | DDRP2 | DDRP1 | DDRP0 |

| \$025B   | RDRP     | Read:<br>Write: | RDRP7 | RDRP6 | RDRP5 | RDRP4 | RDRP3 | RDRP2 | RDRP1 | RDRP0 |

| \$025C   | PERP     | Read:<br>Write: | PERP7 | PERP6 | PERP5 | PERP4 | PERP3 | PERP2 | PERP1 | PERP0 |

| \$025D   | PPSP     | Read:<br>Write: | PPSP7 | PPSP6 | PPSP5 | PPSP4 | PPSP3 | PPSP2 | PPSP1 | PPSS0 |

| \$025E   | PIEP     | Read:<br>Write: | PIEP7 | PIEP6 | PIEP5 | PIEP4 | PIEP3 | PIEP2 | PIEP1 | PIEP0 |

| \$025F   | PIFP     | Read:<br>Write: | PIFP7 | PIFP6 | PIFP5 | PIFP4 | PIFP3 | PIFP2 | PIFP1 | PIFP0 |

| \$0260   | PTH      | Read:<br>Write: | PTH7  | PTH6  | PTH5  | PTH4  | PTH3  | PTH2  | PTH1  | PTH0  |

| \$0261   | PTIH     | Read:<br>Write: | PTIH7 | PTIH6 | PTIH5 | PTIH4 | PTIH3 | PTIH2 | PTIH1 | PTIH0 |

| \$0262   | DDRH     | Read:<br>Write: | DDRH7 | DDRH7 | DDRH5 | DDRH4 | DDRH3 | DDRH2 | DDRH1 | DDRH0 |

| \$0263   | RDRH     | Read:<br>Write: | RDRH7 | RDRH6 | RDRH5 | RDRH4 | RDRH3 | RDRH2 | RDRH1 | RDRH0 |

| \$0264   | PERH     | Read:<br>Write: | PERH7 | PERH6 | PERH5 | PERH4 | PERH3 | PERH2 | PERH1 | PERH0 |

| \$0265   | PPSH     | Read:<br>Write: | PPSH7 | PPSH6 | PPSH5 | PPSH4 | PPSH3 | PPSH2 | PPSH1 | PPSH0 |

| \$0266   | PIEH     | Read:<br>Write: | PIEH7 | PIEH6 | PIEH5 | PIEH4 | PIEH3 | PIEH2 | PIEH1 | PIEH0 |

| \$0267   | PIFH     | Read:<br>Write: | PIFH7 | PIFH6 | PIFH5 | PIFH4 | PIFH3 | PIFH2 | PIFH1 | PIFH0 |

| \$0268   | PTJ      | Read:<br>Write: | PTJ7  | PTJ6  | 0     | 0     | 0     | 0     | PTJ1  | PTJ0  |

| \$0269   | PTIJ     | Read:<br>Write: | PTIJ7 | PTIJ6 | 0     | 0     | 0     | 0     | PTIJ1 | PTIJ0 |

| \$026A   | DDRJ     | Read:<br>Write: | DDRJ7 | DDRJ7 | 0     | 0     | 0     | 0     | DDRJ1 | DDRJ0 |

| \$026B   | RDRJ     | Read:<br>Write: | RDRJ7 | RDRJ6 | 0     | 0     | 0     | 0     | RDRJ1 | RDRJ0 |

| \$026C   | PERJ     | Read:<br>Write: | PERJ7 | PERJ6 | 0     | 0     | 0     | 0     | PERJ1 | PERJ0 |

| \$026D   | PPSJ     | Read:<br>Write: | PPSJ7 | PPSJ6 | 0     | 0     | 0     | 0     | PPSJ1 | PPSJ0 |

| \$026E   | PIEJ     | Read:<br>Write: | PIEJ7 | PIEJ6 | 0     | 0     | 0     | 0     | PIEJ1 | PIEJ0 |

| \$026F   | PIFJ     | Read:<br>Write: | PIFJ7 | PIFJ6 | 0     | 0     | 0     | 0     | PIFJ1 | PIFJ0 |

| \$0270 - | Reserved | Read:           | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| \$027F   |          | Write:          |       |       |       |       |       |       |       |       |

# MC9S12DT128B Device User Guide \_\_\_\_\_ VOT.09

\$0280 - \$02BF

### CAN4 (Motorola Scalable CAN - MSCAN)

| Address            | Name                     |                           | Bit 7  | Bit 6  | Bit 5   | Bit 4    | Bit 3    | Bit 2       | Bit 1  | Bit 0  |

|--------------------|--------------------------|---------------------------|--------|--------|---------|----------|----------|-------------|--------|--------|

| \$0280             | CAN4CTL0                 | Read:                     | RXFRM  | RXACT  | CSWAI   | SYNCH    | TIME     | WUPE        | SLPRQ  | INITRQ |

| φ0200              | CAN4CTE0                 | Write:                    |        |        | COWAI   |          |          | WOFE        |        |        |

| \$0281             | CAN4CTL1                 | Read:<br>Write:           | CANE   | CLKSRC | LOOPB   | LISTEN   | 0        | WUPM        | SLPAK  | INITAK |

| \$0282             | CAN4BTR0                 | Read:<br>Write:           | SJW1   | SJW0   | BRP5    | BRP4     | BRP3     | BRP2        | BRP1   | BRP0   |

| \$0283             | CAN4BTR1                 | Read:<br>Write:           | SAMP   | TSEG22 | TSEG21  | TSEG20   | TSEG13   | TSEG12      | TSEG11 | TSEG10 |

| \$0284             | CAN4RFLG                 | Read:<br>Write:           | WUPIF  | CSCIF  | RSTAT1  | RSTAT0   | TSTAT1   | TSTAT0      | OVRIF  | RXF    |

| \$0285             | CAN4RIER                 | Read:<br>Write:           | WUPIE  | CSCIE  | RSTATE1 | RSTATE0  | TSTATE1  | TSTATE0     | OVRIE  | RXFIE  |

| \$0286             | CAN4TFLG                 | Read:<br>Write:           | 0      | 0      | 0       | 0        | 0        | TXE2        | TXE1   | TXE0   |

| \$0287             | CAN4TIER                 | Read:<br>Write:           | 0      | 0      | 0       | 0        | 0        | TXEIE2      | TXEIE1 | TXEIE0 |

| \$0288             | CAN4TARQ                 | Read:<br>Write:           | 0      | 0      | 0       | 0        | 0        | ABTRQ2      | ABTRQ1 | ABTRQ0 |

| <b>\$</b> 0000     |                          | Read:                     | 0      | 0      | 0       | 0        | 0        | ABTAK2      | ABTAK1 | ABTAK0 |

| \$0289             | CAN4TAAK                 | Write:                    |        |        |         |          |          |             |        |        |

| \$028A             | CAN4TBSEL                | Read:<br>Write:           | 0      | 0      | 0       | 0        | 0        | TX2         | TX1    | TX0    |

| \$028B             | CAN4IDAC                 | Read:<br>Write:           | 0      | 0      | IDAM1   | IDAM0    | 0        | IDHIT2      | IDHIT1 | IDHIT0 |

| \$028C             | Reserved                 | Read:<br>Write:           | 0      | 0      | 0       | 0        | 0        | 0           | 0      | 0      |

| \$028D             | Reserved                 | Read:<br>Write:           | 0      | 0      | 0       | 0        | 0        | 0           | 0      | 0      |

| \$028E             | CAN4RXERR                | Read:<br>Write:           | RXERR7 | RXERR6 | RXERR5  | RXERR4   | RXERR3   | RXERR2      | RXERR1 | RXERR0 |

| \$028F             | CAN4TXERR                | Read:                     | TXERR7 | TXERR6 | TXERR5  | TXERR4   | TXERR3   | TXERR2      | TXERR1 | TXERR0 |

| \$0290 -<br>\$0293 | CAN0IDAR0 -<br>CAN0IDAR3 | Write:<br>Read:<br>Write: | AC7    | AC6    | AC5     | AC4      | AC3      | AC2         | AC1    | AC0    |

| \$0294 -<br>\$0297 | CANOIDMR0 -<br>CANOIDMR3 | Read:<br>Write:           | AM7    | AM6    | AM5     | AM4      | AM3      | AM2         | AM1    | AM0    |

| \$0298 -<br>\$029B | CANOIDAR4 -<br>CANOIDAR7 | Read:<br>Write:           | AC7    | AC6    | AC5     | AC4      | AC3      | AC2         | AC1    | AC0    |

| \$029C -<br>\$029F | CANOIDMR4 -<br>CANOIDMR7 | Read:                     | AM7    | AM6    | AM5     | AM4      | AM3      | AM2         | AM1    | AM0    |

| \$02A0 -           | CAN4RXFG                 | Read:                     |        | FOI    | REGROUN | D RECEIV | E BUFFER | see Table   | 1-2    |        |

| \$02AF             |                          | Write:                    |        |        |         |          |          |             |        |        |

| \$02B0 -<br>\$02BF | CAN4TXFG                 | Read:<br>Write:           |        | FOR    | EGROUN  | D TRANSM | IT BUFFE | R see Table | e 1-2  |        |

# MC9S12DT128B Device User Guide \_\_\_\_\_ VOT.09 Semiconductor, Inc.

## 2.3.6 PAD[15] / AN1[7] / ETRIG1 — Port AD Input Pin [15]

PAD15 is a general purpose input pin and analog input of the analog to digital converter ATD1. It can act as an external trigger input for the ATD1.

## 2.3.7 PAD[14:8] / AN1[6:0] — Port AD Input Pins [14:8]

PAD14 - PAD8 are general purpose input pins and analog inputs of the analog to digital converter ATD1.

## 2.3.8 PAD[7] / AN0[7] / ETRIG0 — Port AD Input Pin [7]

PAD7 is a general purpose input pin and analog input of the analog to digital converter ATD0. It can act as an external trigger input for the ATD0.

## 2.3.9 PAD[6:0] / AN0[6:0] — Port AD Input Pins [6:0]

PAD6 - PAD8 are general purpose input pins and analog inputs of the analog to digital converter ATD0.

## 2.3.10 PA[7:0] / ADDR[15:8] / DATA[15:8] - Port A I/O Pins

PA7-PA0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus.

## 2.3.11 PB[7:0] / ADDR[7:0] / DATA[7:0] - Port B I/O Pins

PB7-PB0 are general purpose input or output pins. In MCU expanded modes of operation, these pins are used for the multiplexed external address and data bus.

## 2.3.12 PE7 / NOACC / XCLKS — Port E I/O Pin 7

PE7 is a general purpose input or output pin. During MCU expanded modes of operation, the NOACC signal, when enabled, is used to indicate that the current bus cycle is an unused or "free" cycle. This signal will assert when the CPU is not using the bus.

The  $\overline{\text{XCLKS}}$  is an input signal which controls whether a crystal in combination with the internal Colpitts (low power) oscillator is used or whether Pierce oscillator/external clock circuitry is used. The state of this pin is latched at the rising edge of  $\overline{\text{RESET}}$ . If the input is a logic low the EXTAL pin is configured for an external clock drive. If input is a logic high an oscillator circuit is configured on EXTAL and XTAL. Since this pin is an input with a pull-up device during reset, if the pin is left floating, the default configuration is an oscillator circuit on EXTAL and XTAL.

# MC9S12DT128B Device User Guide - V01.09 Semiconductor, Inc.

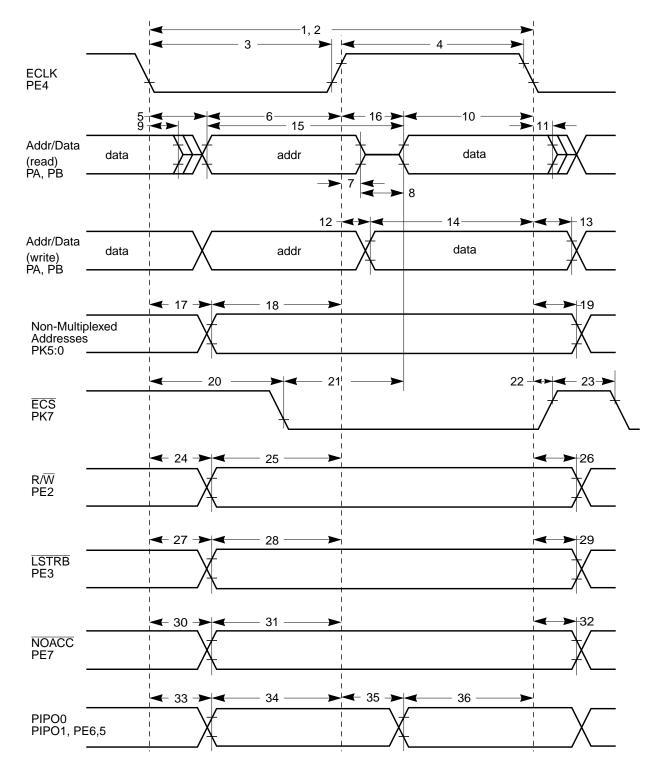

## 2.3.13 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low.

## 2.3.14 PE5 / MODA / IPIPE0 — Port E I/O Pin 5

PE5 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODA bit at the rising edge of  $\overline{\text{RESET}}$ . This pin is shared with the instruction queue tracking signal IPIPE0. This pin is an input with a pull-down device which is only active when  $\overline{\text{RESET}}$  is low.

## 2.3.15 PE4 / ECLK — Port E I/O Pin 4

PE4 is a general purpose input or output pin. It can be configured to drive the internal bus clock ECLK. ECLK can be used as a timing reference.

## 2.3.16 PE3 / LSTRB / TAGLO — Port E I/O Pin 3

PE3 is a general purpose input or output pin. In MCU expanded modes of operation,  $\overline{\text{LSTRB}}$  can be used for the low-byte strobe function to indicate the type of bus access and when instruction tagging is on,  $\overline{\text{TAGLO}}$  is used to tag the low half of the instruction word being read into the instruction queue.

## 2.3.17 PE2 / R/W - Port E I/O Pin 2

PE2 is a general purpose input or output pin. In MCU expanded modes of operations, this pin drives the read/write output signal for the external bus. It indicates the direction of data on the external bus.

## 2.3.18 PE1 / IRQ — Port E Input Pin 1

PE1 is a general purpose input pin and the maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from STOP or WAIT mode.

## 2.3.19 PE0 / XIRQ — Port E Input Pin 0

PE0 is a general purpose input pin and the non-maskable interrupt request input that provides a means of applying asynchronous interrupt requests. This will wake up the MCU from STOP or WAIT mode.

## 2.3.20 PH7 / KWH7 - Port H I/O Pin 7

PH7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode.

## 2.3.36 PM4 / BF\_PSYN / RXCAN0 / RXCAN4/ MOSI0 - Port M I/O Pin 4

PM4 is a general purpose input or output pin. It can be configured as the correct synchronisation pulse reception/transmission output pulse pin of Byteflight. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controllers 0 or 4 (CAN0 or CAN4). It can be configured as the master output (during master mode) or slave input pin (during slave mode) MOSI for the Serial Peripheral Interface 0 (SPI0).

## 2.3.37 PM3 / TX\_BF / TXCAN1 / TXCAN0 / SS0 - Port M I/O Pin 3

PM3 is a general purpose input or output pin. It can be configured as the transmit pinTX\_BF of Byteflight. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controllers 1 or 0 (CAN1 or CAN0). It can be configured as the slave select pin  $\overline{SS}$  of the Serial Peripheral Interface 0 (SPI0).

## 2.3.38 PM2 / RX\_BF / RXCAN1 / RXCAN0 / MISO0 - Port M I/O Pin 2

PM2 is a general purpose input or output pin. It can be configured as the receive pin RX\_BF of Byteflight. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controllers 1 or 0 (CAN1 or CAN0). It can be configured as the master input (during master mode) or slave output pin (during slave mode) MISO for the Serial Peripheral Interface 0 (SPI0).

## 2.3.39 PM1 / TXCAN0 / TXB - Port M I/O Pin 1

PM1 is a general purpose input or output pin. It can be configured as the transmit pin TXCAN of the Motorola Scalable Controller Area Network controller 0 (CAN0). It can be configured as the transmit pin TXB of the BDLC.

## 2.3.40 PM0 / RXCAN0 / RXB - Port M I/O Pin 0

PM0 is a general purpose input or output pin. It can be configured as the receive pin RXCAN of the Motorola Scalable Controller Area Network controller 0 (CAN0). It can be configured as the receive pin RXB of the BDLC.

## 2.3.41 PP7 / KWP7 / PWM7 — Port P I/O Pin 7

PP7 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 7 output.

## 2.3.42 PP6 / KWP6 / PWM6 - Port P I/O Pin 6

PP6 is a general purpose input or output pin. It can be configured to generate an interrupt causing the MCU to exit STOP or WAIT mode. It can be configured as Pulse Width Modulator (PWM) channel 6 output.

## Section 5 Resets and Interrupts

# 5.1 Overview

Consult the Exception Processing section of the HCS12 Core User Guide for information on resets and interrupts.

## 5.2 Vectors

## 5.2.1 Vector Table

**Table 5-1** lists interrupt sources and vectors in default order of priority.

| Vector Address | Interrupt Source                    | CCR<br>Mask | Local Enable                         | HPRIO Value<br>to Elevate |

|----------------|-------------------------------------|-------------|--------------------------------------|---------------------------|

| \$FFFE, \$FFFF | Reset                               | None        | None                                 | _                         |

| \$FFFC, \$FFFD | Clock Monitor fail reset            | None        | COPCTL (CME, FCME)                   | _                         |

| \$FFFA, \$FFFB | COP failure reset                   | None        | COP rate select                      | _                         |

| \$FFF8, \$FFF9 | Unimplemented instruction trap      | None        | None                                 | _                         |

| \$FFF6, \$FFF7 | SWI                                 | None        | None                                 | _                         |