Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                        |

| Core Processor            | dsPIC                                                                           |

| Core Size                 | 16-Bit                                                                          |

| Speed                     | 40 MIPs                                                                         |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals               | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O             | 35                                                                              |

| Program Memory Size       | 16KB (16K x 8)                                                                  |

| Program Memory Type       | FLASH                                                                           |

| EEPROM Size               | -                                                                               |

| RAM Size                  | 2K x 8                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters           | A/D 13x12b                                                                      |

| Oscillator Type           | Internal                                                                        |

| Operating Temperature     | -40°C ~ 125°C (TA)                                                              |

| Mounting Type             | Surface Mount                                                                   |

| Package / Case            | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package   | 44-QFN (8x8)                                                                    |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp304-e-ml |

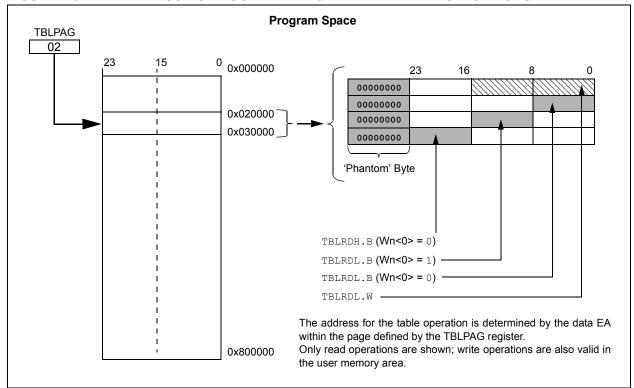

## 4.8.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, this

instruction maps the lower word of the program

space location (P<15:0>) to a data address

(D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

TBLRDH (Table Read High): In Word mode, this

instruction maps the entire upper word of a program

address (P<23:16>) to a data address. Note that

D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

FIGURE 4-8: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| <u>usi 10331 (</u> | JJZGFZU | 12/204 an | u usrics | 373 100 | 7304 |

|--------------------|---------|-----------|----------|---------|------|

| NOTES:             |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

|                    |         |           |          |         |      |

#### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-0         | W-0 | W-0 | W-0 | W-0 | W-0 | W-0 | W-0   |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|

| NVMKEY<7:0> |     |     |     |     |     |     |       |  |

| bit 7       |     |     |     |     |     |     | bit 0 |  |

**Legend:** SO = Settable Only bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (Write Only) bits

#### REGISTER 7-11: IPC0: INTERRUPT PRIORITY CONTROL REGISTER 0

| U-0    | R/W-1     | R/W-0 | R/W-0 | U-0 | R/W-1      | R/W-0 | R/W-0 |

|--------|-----------|-------|-------|-----|------------|-------|-------|

| _      | T1IP<2:0> |       |       | _   | OC1IP<2:0> |       |       |

| bit 15 |           |       |       |     |            |       | bit 8 |

| U-0   | R/W-1      | R/W-0 | R/W-0 | U-0 | R/W-1       | R/W-0 | R/W-0 |

|-------|------------|-------|-------|-----|-------------|-------|-------|

| _     | IC1IP<2:0> |       |       | _   | INT0IP<2:0> |       |       |

| bit 7 |            |       |       |     |             |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 T1IP<2:0>: Timer1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

\_

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11 **Unimplemented:** Read as '0'

bit 10-8 OC1IP<2:0>: Output Compare Channel 1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 Unimplemented: Read as '0'

bit 6-4 IC1IP<2:0>: Input Capture Channel 1 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3 **Unimplemented:** Read as '0'

bit 2-0 INT0IP<2:0>: External Interrupt 0 Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

| <u> </u> | )F332GF | 202/20 | 74 allu ( | <u> </u> | 7304 |

|----------|---------|--------|-----------|----------|------|

| NOTES:   |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

|          |         |        |           |          |      |

TABLE 19-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| TABLE 19-2:  | CONFIGUR | KATION BI      | TS DESCRIPTION (CONTINUED)                                                                                                                                                                                                                                                                         |

|--------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field    | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                                                                                        |

| FCKSM<1:0>   | FOSC     | Immediate      | Clock Switching Mode bits $1x = \text{Clock}$ switching is disabled, Fail-Safe Clock Monitor is disabled $01 = \text{Clock}$ switching is enabled, Fail-Safe Clock Monitor is disabled $00 = \text{Clock}$ switching is enabled, Fail-Safe Clock Monitor is enabled                                |

| IOL1WAY      | FOSC     | Immediate      | Peripheral Pin Select Configuration bit  1 = Allow only one reconfiguration  0 = Allow multiple reconfigurations                                                                                                                                                                                   |

| OSCIOFNC     | FOSC     | Immediate      | OSC2 Pin Function bit (except in XT and HS modes)  1 = OSC2 is clock output  0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                           |

| POSCMD<1:0>  | FOSC     | Immediate      | Primary Oscillator Mode Select bits  11 = Primary oscillator disabled  10 = HS Crystal Oscillator mode  01 = XT Crystal Oscillator mode  00 = EC (External Clock) mode                                                                                                                             |

| FWDTEN       | FWDT     | Immediate      | Watchdog Timer Enable bit  1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled.  Clearing the SWDTEN bit in the RCON register will have no effect.)  0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register) |

| WINDIS       | FWDT     | Immediate      | Watchdog Timer Window Enable bit  1 = Watchdog Timer in Non-Window mode  0 = Watchdog Timer in Window mode                                                                                                                                                                                         |

| WDTPRE       | FWDT     | Immediate      | Watchdog Timer Prescaler bit 1 = 1:128 0 = 1:32                                                                                                                                                                                                                                                    |

| WDTPOST<3:0> | FWDT     | Immediate      | Watchdog Timer Postscaler bits  1111 = 1:32,768  1110 = 1:16,384                                                                                                                                                                                                                                   |

| ALTI2C       | FPOR     | Immediate      | Alternate $I^2C^{TM}$ pins<br>1 = $I^2C$ mapped to SDA1/SCL1 pins<br>0 = $I^2C$ mapped to ASDA1/ASCL1 pins                                                                                                                                                                                         |

| FPWRT<2:0>   | FPOR     | Immediate      | Power-on Reset Timer Value Select bits  111 = PWRT = 128 ms  110 = PWRT = 64 ms  101 = PWRT = 32 ms  100 = PWRT = 16 ms  011 = PWRT = 8 ms  010 = PWRT = 4 ms  001 = PWRT = 2 ms  000 = PWRT = Disabled                                                                                            |

| JTAGEN       | FICD     | Immediate      | JTAG Enable bit  1 = JTAG enabled  0 = JTAG disabled                                                                                                                                                                                                                                               |

Note:

#### 19.5 JTAG Interface

dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices implement a JTAG interface, which supports boundary scan device testing, as well as in-circuit programming. Detailed information on this interface will be provided in future revisions of the document.

## 19.6 Code Protection and CodeGuard™ Security

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 product families offer the intermediate implementation of CodeGuard ™ Security. CodeGuard Security enables multiple parties to securely share resources (memory, interrupts and

TABLE 19-3: CODE FLASH SECURITY SEGMENT SIZES FOR 32 KBYTE DEVICES

| CONFIG BITS         |                                        |                                                                                                         |

|---------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------|

| BSS<2:0>=x11<br>0K  | VS = 256 IW<br>GS = 11008 IW           | 0x000000<br>0x0001FE<br>0x000220<br>0x0007FE<br>0x00800<br>0x001FFE<br>0x002000<br>0x003FFE<br>0x004000 |

|                     |                                        | 0x0057FE                                                                                                |

|                     | VS = 256 IW<br>BS = 768 IW             | 0x000000<br>0x0001FE<br>0x000200                                                                        |

| BSS<2:0>=x10<br>256 | GS = 10240 IW                          | 0x0007FE<br>0x000800<br>0x001FFE<br>0x002000<br>0x003FFE<br>0x004000                                    |

|                     | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | 0x0057FE<br>0x000000                                                                                    |

| BSS<2:0>=x01        | VS = 256 IW<br>BS = 3840 IW            | 0x0001FE<br>0x000200<br>0x0007FE<br>0x000800<br>0x001FFE                                                |

| 768                 | GS = 7168 IW                           | 0x002000<br>0x003FFE<br>0x004000<br>0x0057FE                                                            |

|                     | VS = 256 IW                            | 0x000000<br>0x0001FE                                                                                    |

| BSS<2:0>=x00        | BS = 7936 IW                           | 0x000200<br>0x0007FE<br>0x000800<br>0x001FFE<br>0x002000<br>0x003FFE                                    |

|                     | GS = 3072 IW                           | 0x004000<br>0x0057FE                                                                                    |

peripherals) on a single chip. This feature helps protect individual Intellectual Property in collaborative system designs.

When coupled with software encryption libraries, Code-Guard™ Security can be used to securely update Flash even when multiple IPs reside on the single chip.

The code protection features are controlled by the Configuration registers: FBS and FGS. The Secure segment and RAM is not implemented.

Refer to Section 23. "CodeGuard™ Security" (DS70199) in the "dsPIC33F/PIC24H Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

TABLE 19-4: CODE FLASH SECURITY SEGMENT SIZES FOR 16 KBYTE DEVICES

| CONFIG BITS  |              |                                                                                  |

|--------------|--------------|----------------------------------------------------------------------------------|

| BSS<2:0>=x11 | VS = 256 IW  | 0x000000<br>0x0001FE<br>0x000200<br>0x0007FE<br>0x000800<br>0x001FFE<br>0x002000 |

| U.V.         | GS = 5376 IW | 0x002BFE                                                                         |

|              | VS = 256 IW  | 0x000000<br>0x0001FE                                                             |

| BSS<2:0>=x10 | BS = 768 IW  | 0x000200<br>0x0007FE                                                             |

| 256          |              | 0x000800<br>0x001FFE<br>0x002000                                                 |

|              | GS = 4608 IW | 0x002BFE                                                                         |

|              | VS = 256 IW  | 0x000000<br>0x0001FE                                                             |

| BSS<2:0>=x01 | BS = 3840 IW | 0x000200<br>0x0007FE<br>0x000800<br>0x001FFE                                     |

| 768          |              | 0x002000                                                                         |

|              | GS = 1536 IW | 0x002BFE                                                                         |

|              | VS = 256 IW  | 0x000000<br>0x0001FE                                                             |

| BSS<2:0>=x00 | BS = 5376 IW | 0x000200<br>0x0007FE<br>0x000800<br>0x001FFE                                     |

| 1792         |              | 0x002000                                                                         |

|              |              | 0x002BFE                                                                         |

#### TABLE 20-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                     |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                   |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                   |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                           |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                               |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                    |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                        |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                    |

| Wso   | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                           |

| Wx    | X data space prefetch address register for DSP instructions ∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2, [W9]+ = 6, [W9]+ = 4, [W9]+ = 2, [W9], [W9]- = 6, [W9]- = 4, [W9]- = 2, [W9 + W12], none}                |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                        |

| Wy    | Y data space prefetch address register for DSP instructions ∈ {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]- = 2, [W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- = 2, [W11 + W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                        |

TABLE 22-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTERISTICS |                        |     | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+85°C for Industrial -40°C ≤TA ≤+125°C for Extended |       |            |      |         |

|--------------------|------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|---------|

| Parameter No.      | Typical <sup>(2)</sup> | Max | Doze<br>Ratio                                                                                                                                               | Units | Conditions |      |         |

| Doze Current (IDC  | )ZE) <sup>(1)</sup>    |     |                                                                                                                                                             |       |            |      |         |

| DC73a              | 41                     | 51  | 1:2                                                                                                                                                         | mA    |            |      |         |

| DC73f              | 20                     | 28  | 1:64                                                                                                                                                        | mA    | -40°C      | 3.3V | 40 MIPS |

| DC73g              | 19                     | 24  | 1:128                                                                                                                                                       | mA    |            |      |         |

| DC70a              | 40                     | 46  | 1:2                                                                                                                                                         | mA    |            |      |         |

| DC70f              | 18                     | 20  | 1:64                                                                                                                                                        | mA    | +25°C      | 3.3V | 40 MIPS |

| DC70g              | 18                     | 20  | 1:128                                                                                                                                                       | mA    |            |      |         |

| DC71a              | 40                     | 46  | 1:2                                                                                                                                                         | mA    |            |      |         |

| DC71f              | 18                     | 25  | 1:64                                                                                                                                                        | mA    | +85°C      | 3.3V | 40 MIPS |

| DC71g              | 18                     | 20  | 1:128                                                                                                                                                       | mA    |            |      |         |

| DC72a              | 39                     | 55  | 1:2                                                                                                                                                         | mA    |            |      |         |

| DC72f              | 18                     | 30  | 1:64                                                                                                                                                        | mA    | +125°C     | 3.3V | 40 MIPS |

| DC72g              | 18                     | 25  | 1:128                                                                                                                                                       | mA    |            |      |         |

- **Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail with overshoot/undershoot < 250 mV</li>

- $\bullet\,$  CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while (1) statement

- · JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

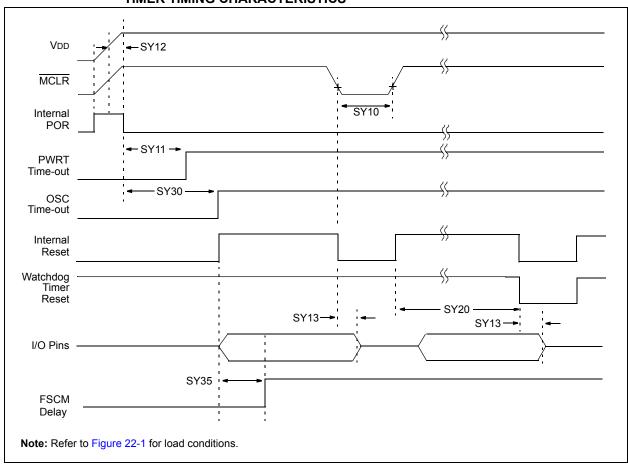

FIGURE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

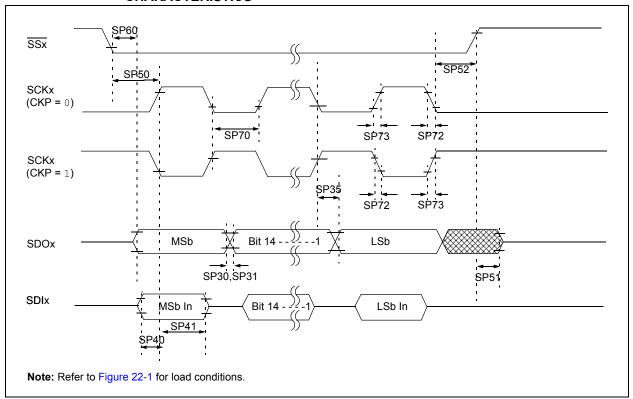

FIGURE 22-13: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

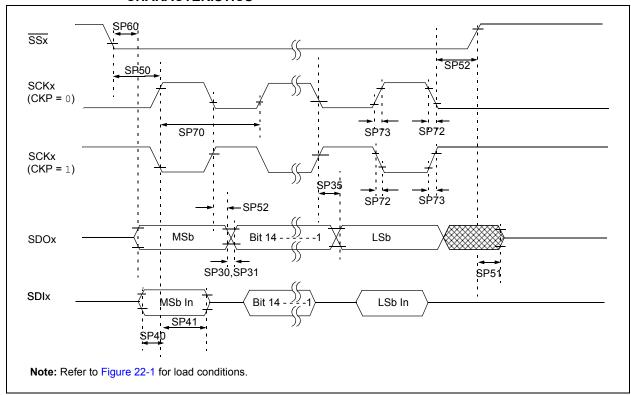

FIGURE 22-14: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

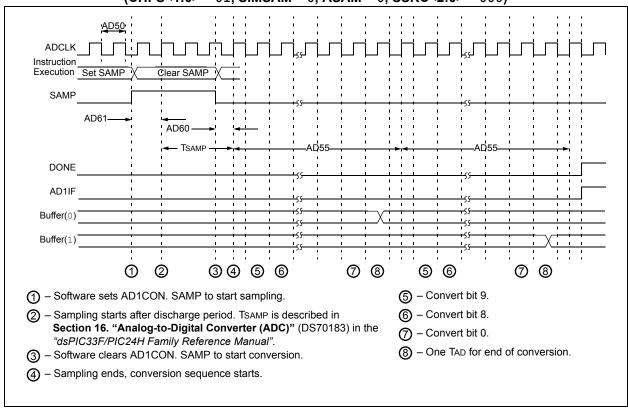

FIGURE 22-22: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000)

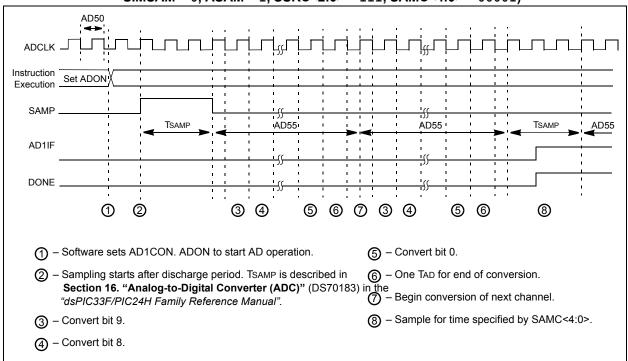

FIGURE 22-23: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SAMC<4:0> = 00001)

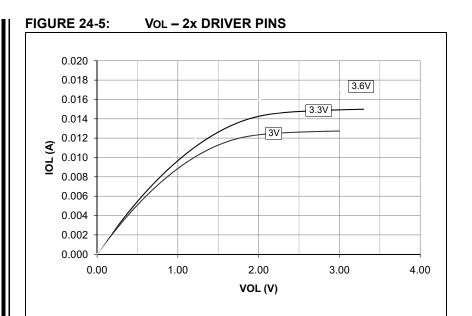

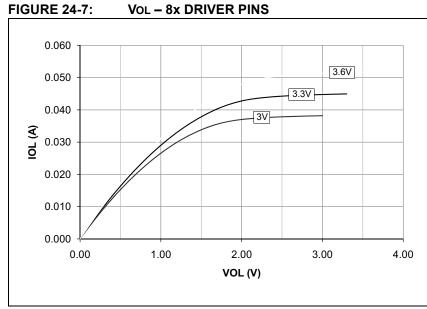

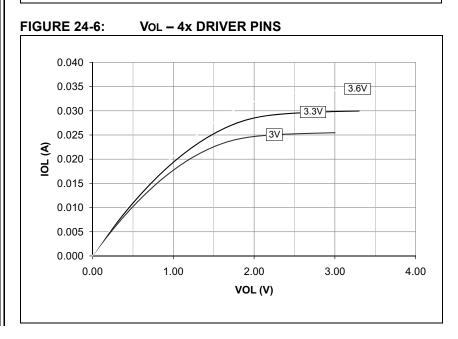

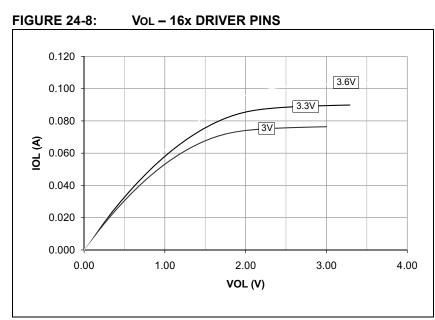

TABLE 23-7: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHA | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature -40°C ≤TA ≤+85°C for High Temperature |                                                                                                    |      |      |      |       |                                                            |

|--------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|------|------|-------|------------------------------------------------------------|

| Param. | Symbol                                                                                                                            | Characteristic                                                                                     | Min. | Тур. | Max. | Units | Conditions                                                 |

| DO10   | VoL                                                                                                                               | Output Low Voltage I/O Pins: 2x Sink Driver Pins - All pins not defined by 4x or 8x driver pins    | _    | _    | 0.4  | V     | IoL ≤1.8 mA, VDD = 3.3V<br>See <b>Note 1</b>               |

|        |                                                                                                                                   | Output Low Voltage I/O Pins: 4x Sink Driver Pins - RA0, RA1, RB5, RB6, RB8, RB9, RB14              | _    | _    | 0.4  | V     | IOL ≤3.6 mA, VDD = 3.3V<br>See <b>Note 1</b>               |

|        |                                                                                                                                   | Output Low Voltage I/O Pins: 8x Sink Driver Pins - OSCO, CLKO, RA3                                 | _    |      | 0.4  | V     | IoL ⊴6 mA, VDD = 3.3V<br>See <b>Note 1</b>                 |

| DO20   | Vон                                                                                                                               | Output High Voltage I/O Pins: 2x Source Driver Pins - All pins not defined by 4x or 8x driver pins | 2.4  | _    | _    | >     | IOL ≥ -1.8 mA, V <sub>DD</sub> = 3.3V<br>See <b>Note 1</b> |

|        |                                                                                                                                   | Output High Voltage I/O Pins: 4x Source Driver Pins - RA0, RA1, RB5, RB6, RB8, RB9, RB14           | 2.4  | _    | _    | ٧     | IoL ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>               |

|        |                                                                                                                                   | Output High Voltage I/O Pins: 8x Source Driver Pins - OSCO, CLKO, RA3                              | 2.4  | _    | _    | V     | IOL ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>               |

|        | Mand                                                                                                                              | Output High Voltage I/O Pins: 2x Source Driver Pins - All pins not defined by 4x or 8x driver pins | 1.5  | _    | _    | V     | IOH ≥ -1.9 mA, VDD = 3.3V<br>See <b>Note 1</b>             |

|        |                                                                                                                                   |                                                                                                    | 2.0  | _    | _    |       | IOH ≥ -1.85 mA, VDD = 3.3V<br>See <b>Note 1</b>            |

|        |                                                                                                                                   |                                                                                                    | 3.0  |      | _    |       | IOH ≥ -1.4 mA, VDD = 3.3V<br>See <b>Note 1</b>             |

| DO20A  |                                                                                                                                   | Output High Voltage<br>4x Source Driver Pins - RA0,<br>RA1, RB5, RB6, RB8, RB9,<br>RB14            | 1.5  | _    | _    | V     | IOH ≥ -3.9 mA, VDD = 3.3V<br>See <b>Note 1</b>             |

|        |                                                                                                                                   |                                                                                                    | 2.0  | _    | _    |       | IOH ≥ -3.7 mA, VDD = 3.3V<br>See <b>Note 1</b>             |

|        |                                                                                                                                   |                                                                                                    | 3.0  | _    | _    |       | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>               |

|        |                                                                                                                                   | Output High Voltage<br>8x Source Driver Pins -OSCO,<br>CLKO, RA3                                   | 1.5  | _    | _    | V     | IOH ≥ -7.5 mA, VDD = 3.3V<br>See <b>Note 1</b>             |

|        |                                                                                                                                   |                                                                                                    | 2.0  | _    | _    |       | IOH ≥ -6.8 mA, VDD = 3.3V<br>See <b>Note 1</b>             |

|        |                                                                                                                                   |                                                                                                    | 3.0  | _    | _    |       | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>               |

Note 1: Parameters are characterized, but not tested.

#### **TABLE 23-15: ADC MODULE SPECIFICATIONS**

| AC<br>CHARACTERISTICS |  | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤TA ≤+150°C for High Temperature |     |          |           |                          |                                                  |  |  |

|-----------------------|--|-------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----------|--------------------------|--------------------------------------------------|--|--|

| Param<br>No. Symbol   |  | Characteristic                                                                                                                      | Min | Тур      | Max       | Units                    | Conditions                                       |  |  |

| Reference Inputs      |  |                                                                                                                                     |     |          |           |                          |                                                  |  |  |

| HAD08   IREF   C      |  | Current Drain                                                                                                                       | _   | 250<br>— | 600<br>50 | μ <b>Α</b><br>μ <b>Α</b> | ADC operating, See Note 1<br>ADC off, See Note 1 |  |  |

Note 1: These parameters are not characterized or tested in manufacturing.

#### TABLE 23-16: ADC MODULE SPECIFICATIONS (12-BIT MODE)(3)

| TABLE 20-10. ABO MODULE OF CONTINUES (12-DT MODE)                                  |        |                                                                       |              |     |     |       |                                                  |  |  |  |

|------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------|--------------|-----|-----|-------|--------------------------------------------------|--|--|--|

| AC                                                                                 |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |              |     |     |       |                                                  |  |  |  |

| CHARACTERISTICS                                                                    |        | Operating temperature -40°C ≤TA ≤+150°C for High Temperature          |              |     |     |       |                                                  |  |  |  |

| Param<br>No.                                                                       | Symbol | Characteristic                                                        | Min          | Тур | Max | Units | Conditions                                       |  |  |  |

| ADC Accuracy (12-bit Mode) – Measurements with External VREF+/VREF- <sup>(1)</sup> |        |                                                                       |              |     |     |       |                                                  |  |  |  |

| HAD20a                                                                             | Nr     | Resolution <sup>(3)</sup>                                             | 12 data bits |     |     | bits  |                                                  |  |  |  |

| HAD21a                                                                             | INL    | Integral Nonlinearity                                                 | -2           | _   | +2  | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD22a                                                                             | DNL    | Differential Nonlinearity                                             | > -1         | _   | < 1 | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD23a                                                                             | GERR   | Gain Error                                                            | -2           | _   | 10  | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| HAD24a                                                                             | EOFF   | Offset Error                                                          | -3           | _   | 5   | LSb   | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |  |  |  |

| ADC Accuracy (12-bit Mode) – Measurements with Internal VREF+/VREF-(1)             |        |                                                                       |              |     |     |       |                                                  |  |  |  |

| HAD20a                                                                             | Nr     | Resolution <sup>(3)</sup>                                             | 12 data bits |     |     | bits  | _                                                |  |  |  |

| HAD21a                                                                             | INL    | Integral Nonlinearity                                                 | -2           | _   | +2  | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |  |

| HAD22a                                                                             | DNL    | Differential Nonlinearity                                             | > -1         | _   | < 1 | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |  |

| HAD23a                                                                             | GERR   | Gain Error                                                            | 2            | _   | 20  | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |  |

| HAD24a                                                                             | EOFF   | Offset Error                                                          | 2            | _   | 10  | LSb   | VINL = AVSS = 0V, AVDD = 3.6V                    |  |  |  |

| Dynamic Performance (12-bit Mode) <sup>(2)</sup>                                   |        |                                                                       |              |     |     |       |                                                  |  |  |  |

| HAD33a                                                                             | FNYQ   | Input Signal Bandwidth                                                | _            | _   | 200 | kHz   | _                                                |  |  |  |

Note 1: These parameters are characterized, but are tested at 20 ksps only.

<sup>2:</sup> These parameters are characterized, but are not tested in manufacturing.

<sup>2:</sup> These parameters are characterized by similarity, but are not tested in manufacturing.

<sup>3:</sup> Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

#### 25.2 Package Details

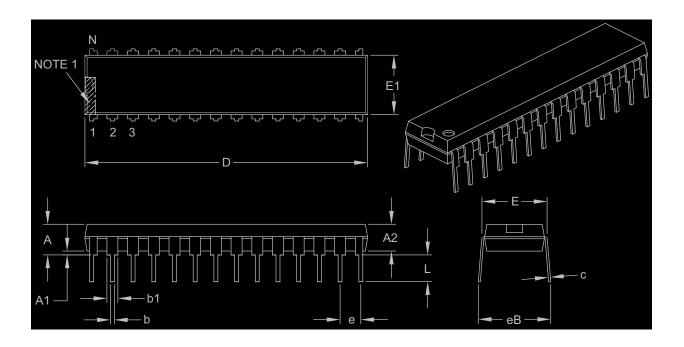

28-Lead Skinny Plastic Dual In-Line (SP) – 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |          |       | INCHES |  |  |  |

|----------------------------|------------------|----------|-------|--------|--|--|--|

| Dimension                  | Dimension Limits |          |       | MAX    |  |  |  |

| Number of Pins             | N                |          | 28    |        |  |  |  |

| Pitch                      | е                | .100 BSC |       |        |  |  |  |

| Top to Seating Plane       | Α                | _        | _     | .200   |  |  |  |

| Molded Package Thickness   | A2               | .120     | .135  | .150   |  |  |  |

| Base to Seating Plane      | A1               | .015     | _     | _      |  |  |  |

| Shoulder to Shoulder Width | Е                | .290     | .310  | .335   |  |  |  |

| Molded Package Width       | E1               | .240     | .285  | .295   |  |  |  |

| Overall Length             | D                | 1.345    | 1.365 | 1.400  |  |  |  |

| Tip to Seating Plane       | L                | .110     | .130  | .150   |  |  |  |

| Lead Thickness             | С                | .008     | .010  | .015   |  |  |  |

| Upper Lead Width           | b1               | .040     | .050  | .070   |  |  |  |

| Lower Lead Width           | b                | .014     | .018  | .022   |  |  |  |

| Overall Row Spacing §      | eВ               | _        | -     | .430   |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

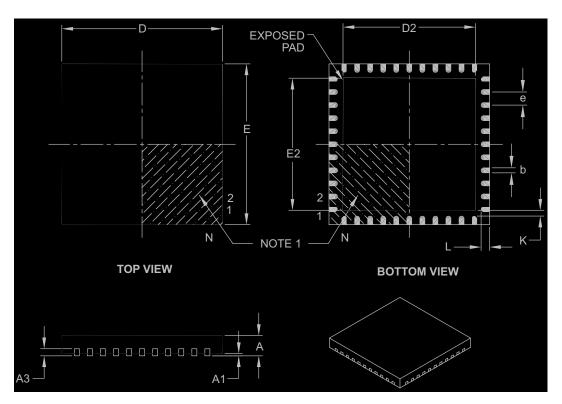

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |          |      | MILLIMETERS |  |  |  |

|------------------------|-------|----------|------|-------------|--|--|--|

| Dimens                 | MIN   | NOM      | MAX  |             |  |  |  |

| Number of Pins         | N     | 44       |      |             |  |  |  |

| Pitch                  | е     | 0.65 BSC |      |             |  |  |  |

| Overall Height         | А     | 0.80     | 0.90 | 1.00        |  |  |  |

| Standoff               | A1    | 0.00     | 0.02 | 0.05        |  |  |  |

| Contact Thickness      | A3    | 0.20 REF |      |             |  |  |  |

| Overall Width          | E     | 8.00 BSC |      |             |  |  |  |

| Exposed Pad Width      | E2    | 6.30     | 6.45 | 6.80        |  |  |  |

| Overall Length         | D     | 8.00 BSC |      |             |  |  |  |

| Exposed Pad Length     | D2    | 6.30     | 6.45 | 6.80        |  |  |  |

| Contact Width          | b     | 0.25     | 0.30 | 0.38        |  |  |  |

| Contact Length         | L     | 0.30     | 0.40 | 0.50        |  |  |  |

| Contact-to-Exposed Pad | K     | 0.20     | _    | _           |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, Keeloq, Keeloq logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007-2011, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-62076-334-6

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.