Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

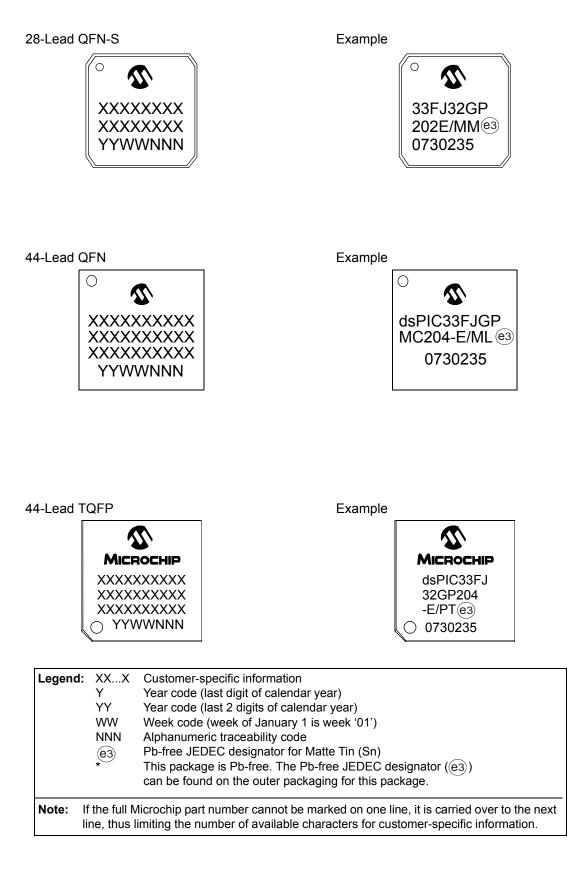

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj16gp304-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33FJ32GP204 product page of the Microchip web site (www.microchip.com).

> In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70202)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 25. "Device Configuration" (DS70194)

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins

(see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (even if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

Note: The AVDD and AVSS pins must be connected independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSs is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| U-0              | U-0                            | U-0                                 | R/W-0           | R/W-0               | R-0              | R-0              | R-0   |

|------------------|--------------------------------|-------------------------------------|-----------------|---------------------|------------------|------------------|-------|

|                  |                                | _                                   | US              | EDT <sup>(1)</sup>  |                  | DL<2:0>          |       |

| bit 15           | •                              |                                     |                 |                     |                  |                  | bit   |

| R/W-0            | R/W-0                          | R/W-1                               | R/W-0           | R/C-0               | R/W-0            | R/W-0            | R/W-0 |

| SATA             | SATB                           | SATDW                               | ACCSAT          | IPL3 <sup>(2)</sup> | PSV              | RND              | IF    |

| bit 7            |                                |                                     |                 |                     |                  |                  | bit   |

| Legend:          |                                | C = Clear on                        | v bit           |                     |                  |                  |       |

| R = Readable     | e bit                          | W = Writable                        | -               | -n = Value at       | POR              | '1' = Bit is set |       |

| 0' = Bit is clea |                                | 'x = Bit is unk                     |                 |                     | nented bit, read |                  |       |

| bit 15-13        | Unimplemen                     | ted: Read as                        | 0'              |                     |                  |                  |       |

| bit 12           | -                              | tiply Unsigned                      |                 | ol bit              |                  |                  |       |

|                  |                                | ne multiplies a                     | 0               |                     |                  |                  |       |

|                  | 0 = DSP engi                   | ne multiplies a                     | ire signed      |                     |                  |                  |       |

| bit 11           | EDT: Early DO                  | D Loop Termina                      | ation Control b | oit(1)              |                  |                  |       |

|                  | 1 = Terminate<br>0 = No effect | e executing DO                      | loop at end of  | f current loop it   | eration          |                  |       |

| bit 10-8         | DL<2:0>: DO                    | Loop Nesting                        | Level Status b  | its                 |                  |                  |       |

|                  | 111 <b>= 7</b> DO <b>Io</b>    | ops active                          |                 |                     |                  |                  |       |

|                  | •                              |                                     |                 |                     |                  |                  |       |

|                  | •<br>001 = 1 DO lo             | on active                           |                 |                     |                  |                  |       |

|                  | 000 = 0 DO IO                  |                                     |                 |                     |                  |                  |       |

| bit 7            |                                | Saturation Ena                      | ble bit         |                     |                  |                  |       |

|                  |                                | ator A saturatio                    |                 |                     |                  |                  |       |

| bit 6            |                                | ator A saturation<br>Saturation Ena |                 |                     |                  |                  |       |

|                  |                                | ator B saturatio                    |                 |                     |                  |                  |       |

|                  |                                | ator B saturation                   |                 |                     |                  |                  |       |

| bit 5            | SATDW: Data                    | a Space Write                       | from DSP Eng    | ine Saturation      | Enable bit       |                  |       |

|                  |                                | ce write satura                     |                 |                     |                  |                  |       |

|                  | •                              | ce write satura                     |                 |                     |                  |                  |       |

| bit 4            |                                | cumulator Satu                      |                 | Select bit          |                  |                  |       |

|                  |                                | ration (super s<br>ration (normal   | ,               |                     |                  |                  |       |

| bit 3            |                                | terrupt Priority                    |                 | nit 3(2)            |                  |                  |       |

|                  |                                | rrupt Priority L                    |                 |                     |                  |                  |       |

|                  |                                | rrupt Priority L                    | 0               |                     |                  |                  |       |

| bit 2            | PSV: Program                   | n Space Visibi                      | ity in Data Spa | ace Enable bit      |                  |                  |       |

|                  | •                              | space visible i                     | •               |                     |                  |                  |       |

| 1.11.4           | -                              | space not visit                     | -               | ce                  |                  |                  |       |

| bit 1            |                                | ng Mode Sele                        |                 | 1                   |                  |                  |       |

|                  |                                | onventional) ro<br>(convergent)     |                 |                     |                  |                  |       |

| bit 0            |                                | Fractional Mu                       | -               |                     |                  |                  |       |

|                  | 1 = Integer m                  | ode enabled fo                      | or DSP multipl  | y ops               |                  |                  |       |

|                  | - Erectione                    | l mada anabla                       | d for DSP mul   | tinly one           |                  |                  |       |

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| File Name |      | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4 | Bit 3 | 16GP30<br>Bit 2 | Bit 1 | Bit 0 | All    |

|-----------|------|--------|--------|--------|--------|------------|-----------|-------|-------|-------|------------|-------|-------|-------|-----------------|-------|-------|--------|

|           |      | 2.0.10 |        | 2.0.10 |        | 2          | 2         | 2     |       |       |            |       |       | 2     |                 | 2     | 2     | Resets |

| RPOR0     | 06C0 | _      | _      | _      |        |            | RP1R<4:0> |       |       | —     | _          | _     |       |       | RP0R<4:0>       | •     |       | 0000   |

| RPOR1     | 06C2 | _      | _      | _      |        |            | RP3R<4:0> |       |       | _     | _          | _     |       |       | RP2R<4:0>       | •     |       | 0000   |

| RPOR2     | 06C4 | _      | _      | _      |        |            | RP5R<4:0> |       |       | _     | _          | _     |       |       | RP4R<4:0>       |       |       | 0000   |

| RPOR3     | 06C6 |        | _      |        |        |            | RP7R<4:0> |       |       |       | _          | _     |       |       | RP6R<4:0>       | •     |       | 0000   |

| RPOR4     | 06C8 | _      | _      | _      |        |            | RP9R<4:0> |       |       | _     | _          | _     |       |       | RP8R<4:0>       | •     |       | 0000   |

| RPOR5     | 06CA |        | _      |        |        | RP11R<4:0> |           |       | _     | _     | RP10R<4:0> |       |       | 0000  |                 |       |       |        |

| RPOR6     | 06CC |        | _      |        |        | F          | RP13R<4:0 | >     |       |       | _          | _     |       |       | RP12R<4:0       | >     |       | 0000   |

| RPOR7     | 06CE | _      | _      | _      |        | F          | RP15R<4:0 | >     |       | _     | _          | _     |       |       | RP14R<4:0       | >     |       | 0000   |

| RPOR8     | 06D0 | _      | _      | _      |        | F          | RP17R<4:0 | >     |       | _     | _          | _     |       |       | RP16R<4:0       | >     |       | 0000   |

| RPOR9     | 06D2 | _      | _      | _      |        | F          | RP19R<4:0 | >     |       | _     | _          | _     |       |       | RP18R<4:0       | >     |       | 0000   |

| RPOR10    | 06D4 |        | _      |        |        | RP21R<4:0> |           |       | _     | _     | RP20R<4:0> |       |       | 0000  |                 |       |       |        |

| RPOR11    | 06D6 | _      | _      |        |        | F          | RP23R<4:0 | >     |       | _     | _          | _     |       |       | RP22R<4:0       | >     |       | 0000   |

| RPOR12    | 06D8 | _      | _      | _      |        | F          | RP25R<4:0 | >     |       | _     | _          | _     |       |       | RP24R<4:0       | >     |       | 0000   |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register.

Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries also check for addresses less than or greater than these addresses. Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (such as [W7+W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

# 4.7 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing).

- The BREN bit is set in the XBREV register.

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

**Note:** All bit-reversed EA calculations assume word sized data (LSB of every EA is always clear). The XB value is scaled accordingly to generate compatible (byte) addresses.

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word sized data writes. It will not function for any other addressing mode or for byte sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word sized data is a requirement, the LSb of the EA is ignored (and always clear).

**Note:** Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active for the X WAGU and X WAGU Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN bit (XBREV<15>), a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

| Symbol | Parameter                        | Value            |

|--------|----------------------------------|------------------|

| VPOR   | POR threshold                    | 1.8V nominal     |

| TPOR   | POR extension time               | 30 μs maximum    |

| VBOR   | BOR threshold                    | 2.5V nominal     |

| TBOR   | BOR extension time               | 100 μs maximum   |

| TPWRT  | Programmable power-up time delay | 0-128 ms nominal |

| TFSCM  | Fail-Safe Clock Monitor Delay    | 900 μs maximum   |

### TABLE 6-2: OSCILLATOR PARAMETERS

Note: When the device exits the Reset condition (begins normal operation), the device operating parameters (voltage, frequency, temperature, etc.) must be within their operating ranges, otherwise the device may not function correctly. The user application must ensure that the delay between the time power is first applied, and the time SYSRST becomes inactive, is long enough to get operating parameters within all specification.

### 6.4 Power-on Reset (POR)

A Power-on Reset (POR) circuit ensures the device is reset from power-on. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 22.0 "Electrical Characteristics" for details.

The POR status (POR) bit in the Reset Control (RCON<0>) register is set to indicate the Power-on Reset.

# 6.4.1 Brown-out Reset (BOR) and Power-up timer (PWRT)

The on-chip regulator has a Brown-out Reset (BOR) circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

The BOR status bit in the Reset Control register (RCON<1>) is set to indicate the Brown-out Reset.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provide eight settings (from 0 ms to 128 ms). Refer to **Section 19.0 "Special Features"** for further details.

Figure 6-3 shows the typical brown-out scenarios. The reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point

| REGISTER      | 7-8: IEC0:                         | INTERRUPT                        | ENABLE CO        | ONTROL REC        | GISTER 0        |                 |        |

|---------------|------------------------------------|----------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| U-0           | U-0                                | R/W-0                            | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| _             | _                                  | AD1IE                            | U1TXIE           | U1RXIE            | SPI1IE          | SPI1EIE         | T3IE   |

| bit 15        |                                    |                                  |                  |                   |                 |                 | bit 8  |

| R/W-0         | R/W-0                              | R/W-0                            | U-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

| T2IE          | OC2IE                              | IC2IE                            | 0-0              | T1IE              | OC1IE           | IC1IE           | INTOIE |

| bit 7         | UUZIE                              | ICZIE                            |                  | 111               | OCTIE           | ICTIE           | bit (  |

|               |                                    |                                  |                  |                   |                 |                 |        |

| Legend:       |                                    |                                  |                  |                   |                 |                 |        |

| R = Readable  | e bit                              | W = Writable                     | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |

| -n = Value at | POR                                | '1' = Bit is set                 |                  | '0' = Bit is clea | ared            | x = Bit is unkn | own    |

| bit 15-14     | Unimplemen                         | ted: Read as '                   | 0'               |                   |                 |                 |        |

| bit 13        | AD1IE: ADC1                        | Conversion C                     | complete Inter   | rupt Enable bit   |                 |                 |        |

|               | 1 = Interrupt r                    | equest enable                    | d                |                   |                 |                 |        |

|               | 0 = Interrupt r                    | equest not en                    | abled            |                   |                 |                 |        |

| bit 12        |                                    | RT1 Transmitte                   | •                | able bit          |                 |                 |        |

|               | •                                  | equest enable<br>equest not ena  |                  |                   |                 |                 |        |

| bit 11        |                                    | RT1 Receiver I                   |                  | e hit             |                 |                 |        |

| bit II        |                                    | equest enable                    |                  |                   |                 |                 |        |

|               |                                    | equest not en                    |                  |                   |                 |                 |        |

| bit 10        | SPI1IE: SPI1                       | Event Interrup                   | t Enable bit     |                   |                 |                 |        |

|               |                                    | equest enable                    |                  |                   |                 |                 |        |

| <b>h</b> # 0  |                                    | equest not en                    |                  |                   |                 |                 |        |

| bit 9         |                                    | 1 Error Interru<br>equest enable |                  |                   |                 |                 |        |

|               |                                    | request not enable               |                  |                   |                 |                 |        |

| bit 8         | T3IE: Timer3                       | Interrupt Enab                   | le bit           |                   |                 |                 |        |

|               |                                    | equest enable<br>equest not ena  |                  |                   |                 |                 |        |

| bit 7         | T2IE: Timer2                       | Interrupt Enab                   | le bit           |                   |                 |                 |        |

|               |                                    | equest enable<br>equest not en   |                  |                   |                 |                 |        |

| bit 6         | •                                  | ut Compare Ch                    |                  | upt Enable bit    |                 |                 |        |

|               |                                    | equest enable<br>equest not en   |                  |                   |                 |                 |        |

| bit 5         | IC2IE: Input C                     | Capture Chann                    | el 2 Interrupt I | Enable bit        |                 |                 |        |

|               |                                    | equest enable<br>equest not ena  |                  |                   |                 |                 |        |

| bit 4         | Unimplemen                         | ted: Read as '                   | 0'               |                   |                 |                 |        |

| bit 3         | T1IE: Timer1                       | Interrupt Enab                   | le bit           |                   |                 |                 |        |

|               | •                                  | equest enable<br>equest not en   |                  |                   |                 |                 |        |

| bit 2         | OC1IE: Output                      | ut Compare Ch                    | annel 1 Interr   | upt Enable bit    |                 |                 |        |

|               | 1 = Interrupt r<br>0 = Interrupt r | equest enable                    | d                |                   |                 |                 |        |

####

| U-0               | U-0                                                                                                       | U-0                                                                                                        | U-0                                           | R-0                | R-0             | R-0             | R-0   |

|-------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|-----------------|-----------------|-------|

| —                 | —                                                                                                         | —                                                                                                          |                                               |                    | ILF             | R<3:0>          |       |

| bit 15            |                                                                                                           |                                                                                                            |                                               |                    |                 |                 | bit 8 |

|                   |                                                                                                           |                                                                                                            |                                               |                    |                 |                 |       |

| U-0               | R-0                                                                                                       | R-0                                                                                                        | R-0                                           | R-0                | R-0             | R-0             | R-0   |

|                   |                                                                                                           |                                                                                                            |                                               | VECNUM<6:0         | >               |                 |       |

| bit 7             |                                                                                                           |                                                                                                            |                                               |                    |                 |                 | bit ( |

| Legend:           |                                                                                                           |                                                                                                            |                                               |                    |                 |                 |       |

| R = Readabl       | le bit                                                                                                    | W = Writable                                                                                               | bit                                           | U = Unimplen       | nented bit, rea | ad as '0'       |       |

| -n = Value at     | t POR                                                                                                     | '1' = Bit is set                                                                                           |                                               | '0' = Bit is clea  | ared            | x = Bit is unkr | nown  |

| bit 11-8<br>bit 7 | 1111 = CPU<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Iew CPU Interrup<br>J Interrupt Priorit<br>J Interrupt Priorit<br>J Interrupt Priorit<br>ented: Read as '( | y Level is 15<br>y Level is 1<br>y Level is 0 | el bits            |                 |                 |       |

|                   | •                                                                                                         |                                                                                                            |                                               |                    |                 |                 |       |

| bit 6-0           | 0111111 =<br>•<br>•<br>0000001 =                                                                          | :0>: Vector Num<br>Interrupt Vector<br>Interrupt Vector<br>Interrupt Vector                                | pending is nu<br>pending is nu                | mber 135<br>mber 9 |                 |                 |       |

## REGISTER 7-19: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

# 8.1 CPU Clocking System

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 device provides seven system clock options:

- · Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- · FRC Oscillator with postscaler

#### 8.1.1 SYSTEM CLOCK SOURCES

#### 8.1.1.1 Fast RC

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

#### 8.1.1.2 Primary

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

#### 8.1.1.3 Secondary

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

### 8.1.1.4 Low-Power RC

The Low-Power RC (LPRC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

#### 8.1.1.5 FRC

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in Section 8.1.3 "PLL Configuration".

The FRC frequency depends on the FRC accuracy (see Table 22-18) and the value of the FRC Oscillator Tuning register (see Register 8-4).

### 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The Oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to Section 19.1 "Configuration Bits" for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits. POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) Fosc is divided by 2 to generate the device instruction clock (FcY) and the peripheral clock time base (FP). FcY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 architecture.

Instruction execution speed or device operating frequency, FCY, is given by:

### EQUATION 8-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

### 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 8-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2.' This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

# REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0          | U-0                | U-0              | U-0          | U-0                                | U-0              | U-0      | U-0   |  |

|--------------|--------------------|------------------|--------------|------------------------------------|------------------|----------|-------|--|

| _            | —                  | —                | _            | —                                  | —                | —        | _     |  |

| bit 15       |                    |                  |              |                                    |                  |          | bit 8 |  |

|              |                    |                  |              |                                    |                  |          |       |  |

| U-0          | U-0                | U-0              | R/W-1        | R/W-1                              | R/W-1            | R/W-1    | R/W-1 |  |

| —            | —                  | —                | — INT2R<4:0> |                                    |                  |          |       |  |

| bit 7        |                    |                  |              |                                    |                  |          | bit 0 |  |

|              |                    |                  |              |                                    |                  |          |       |  |

| Legend:      |                    |                  |              |                                    |                  |          |       |  |

| R = Readab   | le bit             | W = Writable     | bit          | U = Unimple                        | mented bit, read | d as '0' |       |  |

| -n = Value a | It POR             | '1' = Bit is set |              | '0' = Bit is cleared x = Bit is un |                  |          | nown  |  |

| bit 15-5     | Unimpleme          | nted: Read as '  | 0'           |                                    |                  |          |       |  |

|              | -                  |                  |              |                                    | oorrooponding    | DDn nin  |       |  |

| bit 4-0      |                    | : Assign Extern  | ai menupi 2  | (INTR2) to the                     | corresponding    | RPITPIT  |       |  |

|              | •                  | ut tied to Vss   |              |                                    |                  |          |       |  |

|              | 11001 <b>= Inp</b> | ut tied to RP25  |              |                                    |                  |          |       |  |

|              | •                  |                  |              |                                    |                  |          |       |  |

|              | •                  |                  |              |                                    |                  |          |       |  |

|              | •                  |                  |              |                                    |                  |          |       |  |

|              | 00001 - 100        |                  |              |                                    |                  |          |       |  |

00001 = Input tied to RP1 00000 = Input tied to RP0

| U-0           | U-0                                                                      | U-0                                               | R/W-1            | R/W-1           | R/W-1           | R/W-1     | R/W-1 |  |  |

|---------------|--------------------------------------------------------------------------|---------------------------------------------------|------------------|-----------------|-----------------|-----------|-------|--|--|

| _             | _                                                                        |                                                   |                  |                 | IC2R<4:0>       |           |       |  |  |

| bit 15        |                                                                          |                                                   |                  |                 |                 |           | bit 8 |  |  |

|               |                                                                          |                                                   |                  |                 |                 |           |       |  |  |

| U-0           | U-0                                                                      | U-0                                               | R/W-1            | R/W-1           | R/W-1           | R/W-1     | R/W-1 |  |  |

|               | —                                                                        | —                                                 |                  |                 | IC1R<4:0>       |           |       |  |  |

| bit 7         |                                                                          |                                                   |                  |                 |                 |           | bit 0 |  |  |

| Legend:       |                                                                          |                                                   |                  |                 |                 |           |       |  |  |

| R = Readabl   | le bit                                                                   | W = Writable                                      | bit              | U = Unimpler    | mented bit, rea | ad as '0' |       |  |  |

| -n = Value at | n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknow |                                                   |                  |                 |                 |           |       |  |  |

|               | 11001 = Inpu<br>•                                                        | t tied to RP25                                    |                  |                 |                 |           |       |  |  |

|               | •<br>00001 = Inpu<br>00000 = Inpu                                        | t tied to RP0                                     |                  |                 |                 |           |       |  |  |

| bit 7-5       | •                                                                        | ted: Read as '                                    |                  |                 |                 |           |       |  |  |

| bit 4-0       | 11111 <b>= Inpu</b>                                                      | ssign Input Ca<br>t tied to Vss<br>t tied to RP25 | ipture 1 (IC1) i | to the correspo | onding RPn pir  | n         |       |  |  |

|               | 00001 = Inpu<br>00000 = Inpu                                             |                                                   |                  |                 |                 |           |       |  |  |

## REGISTER 10-4: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7

### REGISTER 10-14: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0    | U-0 | U-0 | R/W-0     | R/W-0 | R/W-0     | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-----|-----------|-------|-----------|-------|-------|--|--|--|

| —      | —   | —   | RP9R<4:0> |       |           |       |       |  |  |  |

| bit 15 |     |     |           |       |           |       | bit 8 |  |  |  |

|        |     |     |           |       |           |       |       |  |  |  |

| U-0    | U-0 | U-0 | R/W-0     | R/W-0 | R/W-0     | R/W-0 | R/W-0 |  |  |  |

| _      | _   | —   |           |       | RP8R<4:0> |       |       |  |  |  |

| bit 7  | ·   |     | •         |       |           |       | bit 0 |  |  |  |

|        |     |     |           |       |           |       |       |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-15: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0           | U-0                         | U-0                       | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0           |

|---------------|-----------------------------|---------------------------|---------------|------------------|-----------------|------------------|-----------------|

| _             | —                           | —                         |               |                  | RP11R<4:0>      | >                |                 |

| bit 15        | •                           |                           |               |                  |                 |                  | bit 8           |

|               |                             |                           |               |                  |                 |                  |                 |

| U-0           | U-0                         | U-0                       | R/W-0         | R/W-0            | R/W-0           | R/W-0            | R/W-0           |

| —             | —                           |                           |               |                  | RP10R<4:0>      | >                |                 |

| bit 7         |                             |                           |               |                  |                 |                  | bit 0           |

|               |                             |                           |               |                  |                 |                  |                 |

| Legend:       |                             |                           |               |                  |                 |                  |                 |

| R = Readable  | e bit                       | W = Writable I            | oit           | U = Unimpler     | nented bit, rea | d as '0'         |                 |

| -n = Value at | POR                         | '1' = Bit is set          |               | '0' = Bit is cle | x = Bit is unkr | nown             |                 |

|               |                             |                           |               |                  |                 |                  |                 |

| bit 15-13     | Unimpleme                   | nted: Read as '           | )'            |                  |                 |                  |                 |

| bit 12-8      | RP11R<4:0><br>eral function | : Peripheral Out numbers) | tput Functior | n is Assigned to | RP11 Output F   | Pin (see Table 1 | 0-2 for periph- |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin (see Table 10-2 for peripheral function numbers)

# 13.2 Input Capture Registers

## REGISTER 13-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | -   | —   | —   | _   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

|        |     |        |     |     |     |     |       |

| R/W-0 | R/W-0    | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0 R/W-0 R/V |       |

|-------|----------|-------|---------|---------|-------|-----------------|-------|

| ICTMR | ICI<1:0> |       | ICOV    | ICBNE   |       |                 |       |

| bit 7 |          |       |         |         |       |                 | bit 0 |

| Legend:           |                  | HC = C                | leared in hardware |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                                                                                                                              |  |  |  |  |  |

|           | <ul> <li>1 = Input capture module will halt in CPU Idle mode</li> <li>0 = Input capture module will continue to operate in CPU Idle mode</li> </ul>                                                                                                                                |  |  |  |  |  |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                         |  |  |  |  |  |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                                                                                                                                             |  |  |  |  |  |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                                                                       |  |  |  |  |  |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                                                                             |  |  |  |  |  |

|           | <ul> <li>11 = Interrupt on every fourth capture event</li> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                                                                                        |  |  |  |  |  |

|           | 00 = Interrupt on every capture event                                                                                                                                                                                                                                              |  |  |  |  |  |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                                                                                                           |  |  |  |  |  |

|           | <ul> <li>1 = Input capture overflow occurred</li> <li>0 = No input capture overflow occurred</li> </ul>                                                                                                                                                                            |  |  |  |  |  |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                                                                                                                           |  |  |  |  |  |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                                                                                  |  |  |  |  |  |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                                                                                                                           |  |  |  |  |  |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br/>(Rising edge detect only, all other control bits are not applicable.)</li> <li>110 = Unused (module disabled)</li> <li>101 = Capture mode, every 16th rising edge</li> </ul> |  |  |  |  |  |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                                                                          |  |  |  |  |  |

|           | <ul> <li>011 = Capture mode, every rising edge</li> <li>010 = Capture mode, every falling edge</li> </ul>                                                                                                                                                                          |  |  |  |  |  |

|           | 001 = Capture mode, every edge (rising and falling)                                                                                                                                                                                                                                |  |  |  |  |  |

|           | (ICI<1:0> bits do not control interrupt generation for this mode.)                                                                                                                                                                                                                 |  |  |  |  |  |

|           | 000 = Input capture module turned off                                                                                                                                                                                                                                              |  |  |  |  |  |

|                                                                                                              |                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                           | EGISTER 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U-0                                                                                                          | U-0                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                        |