Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp202-e-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>NameSFR<br>AddrBit 15Bit 14Bit 13Bit 12Bit 11Bit 10Bit 9Bit 8Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0All ResetsINTCON10080NSTDISOVAERROVBERCOVAERRCOVAERROVBEROVATEOVBTECOVTESTACERRDIVOERR-MATHERRADDRERRSTACERRSSCFAIL-0000INTCON20082ALTIVTDISI0000IFS00086AD11FU1TXIFU1RXIFSPI1EFT31FT21FOC21FIC21F-T11FOC11FIC11FINTOFP0000IFS40086AD11FU1TXIFU1RXIFSPI1EFT31FT21FOC21FIC21F-MI2C11FSI21F0000IFS40086AD11FU1TXIFSPI1EFSPI1EFT31ET21FOC21FIC21F-MI2C11FSI2C1F0000IFS40086AD11FU1TXIFSPI1EFSPI1EFT31ET21EOC21FIC21F-MI2C11FSI2C1F0000IEC40096INT21E-AD11EU1TXIFSPI1EFSPI1EFT31ET21EOC21EIC71E-INT1ECNIE-MI2C11FSI2C1F0000IEC40096 <td< th=""><th></th><th></th><th></th><th></th><th>-</th><th>-</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></td<> |         |      |        |        | -          | -        |         |        |            |       |          |         |             |         |           |        |            |         |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------|--------|------------|----------|---------|--------|------------|-------|----------|---------|-------------|---------|-----------|--------|------------|---------|---------------|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -       |      | Bit 15 | Bit 14 | Bit 13     | Bit 12   | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3     | Bit 2  | Bit 1      | Bit 0   | All<br>Resets |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INTCON1 | 0080 | NSTDIS | OVAERR | OVBERR     | COVAERR  | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | _           | MATHERR | ADDRERR   | STKERR | OSCFAIL    | —       | 0000          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INTCON2 | 0082 | ALTIVT | DISI   | —          | —        | —       | —      | —          | —     | —        | —       | —           | —       | —         | INT2EP | INT1EP     | INT0EP  | 0000          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IFS0    | 0084 | —      | —      | AD1IF      | U1TXIF   | U1RXIF  | SPI1IF | SPI1EIF    | T3IF  | T2IF     | OC2IF   | IC2IF       | —       | T1IF      | OC1IF  | IC1IF      | INT0IF  | 0000          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IFS1    | 0086 | —      | —      | INT2IF     | —        | —       | —      | —          | _     | IC8IF    | IC7IF   | _           | INT1IF  | CNIF      | —      | MI2C1IF    | SI2C1IF | 0000          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IFS4    | 008C | —      | —      | —          | _        | —       | —      | —          | —     | -        | —       | —           | —       | —         | —      | U1EIF      | _       | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEC0    | 0094 | —      | —      | AD1IE      | U1TXIE   | U1RXIE  | SPI1IE | SPI1EIE    | T3IE  | T2IE     | OC2IE   | IC2IE       | —       | T1IE      | OC1IE  | IC1IE      | INT0IE  | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEC1    | 0096 | —      | —      | INT2IE     | _        | —       | —      | —          | —     | IC8IE    | IC7IE   | —           | INT1IE  | CNIE      | —      | MI2C1IE    | SI2C1IE | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEC4    | 009C | —      | —      | —          | _        | —       | —      | —          | —     | -        | —       | —           | —       | —         | —      | U1EIE      | _       | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC0    | 00A4 | —      |        | T1IP<2:0>  |          | —       | (      | OC1IP<2:0  | )>    | —        |         | IC1IP<2:0>  |         | —         | 11     | VT0IP<2:0> | •       | 4444          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC1    | 00A6 | —      |        | T2IP<2:0>  |          | —       | (      | OC2IP<2:0  | )>    | _        |         | IC2IP<2:0>  |         | —         | —      | —          | _       | 4440          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC2    | 00A8 | _      | ι      | J1RXIP<2:0 | )>       | _       | 0,     | SPI1IP<2:0 | )>    | _        |         | SPI1EIP<2:0 | >       | _         |        | T3IP<2:0>  |         | 4444          |

| IPC5       00AE       -       IC8IP<2:0>       -       IC7IP<2:0>       -       -       -       -       -       -       4404         IPC7       00B2       -       -       -       -       -       -       -       -       -       4004         IPC7       00B2       -       -       -       -       -       -       -       -       0040         IPC16       00C4       -       -       -       -       -       -       -       0040                                                                                                                                                                                                                                                                                                                                                                                                     | IPC3    | 00AA | —      | —      | —          | _        | —       | —      | —          | —     | —        |         | AD1IP<2:0>  | >       | —         | U      | 1TXIP<2:0  | >       | 0044          |

| IPC7       00B2       -       -       -       -       -       -       INT2IP<2:0>       -       -       -       0040         IPC16       00C4       -       -       -       -       -       -       -       0040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IPC4    | 00AC | —      |        | CNIP<2:0>  | •        | —       | —      | —          | —     | -        | I       | MI2C1IP<2:0 | )>      | —         | SI     | 2C1IP<2:0  | >       | 4044          |

| IPC16       00C4       -       -       -       -       -       U1EIP<2:0>       -       -       -       0040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IPC5    | 00AE | —      |        | IC8IP<2:0> | <b>`</b> | —       |        | IC7IP<2:0  | >     | _        | —       | —           | —       | —         | 11     | VT1IP<2:0> | •       | 4404          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IPC7    | 00B2 | _      | _      | _          | _        | _       | _      | _          | _     | _        |         | INT2IP<2:02 | >       | _         | _      | _          | _       | 0040          |

| INTTREG 00E0 ILR<3:0> - VECNUM<6:0> 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IPC16   | 00C4 | —      | —      | —          | —        | —       | —      | —          | _     | —        |         | U1EIP<2:0>  | >       | —         | —      | —          |         | 0040          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INTTREG | 00E0 | —      | —      | —          | —        |         | ILR<   | 3:0>       |       | —        |         |             | VE      | CNUM<6:0> |        |            |         | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

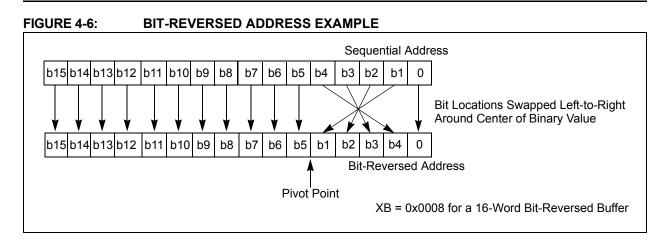

#### TABLE 4-24: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | s       |    |    | Bit-Rev | ersed Ac | Idress  |

|----|----|-------|-----------|---------|----|----|---------|----------|---------|

| A3 | A2 | A1    | A0        | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0  | 0  | 0     | 0         | 0       | 0  | 0  | 0       | 0        | 0       |

| 0  | 0  | 0     | 1         | 1       | 1  | 0  | 0       | 0        | 8       |

| 0  | 0  | 1     | 0         | 2       | 0  | 1  | 0       | 0        | 4       |

| 0  | 0  | 1     | 1         | 3       | 1  | 1  | 0       | 0        | 12      |

| 0  | 1  | 0     | 0         | 4       | 0  | 0  | 1       | 0        | 2       |

| 0  | 1  | 0     | 1         | 5       | 1  | 0  | 1       | 0        | 10      |

| 0  | 1  | 1     | 0         | 6       | 0  | 1  | 1       | 0        | 6       |

| 0  | 1  | 1     | 1         | 7       | 1  | 1  | 1       | 0        | 14      |

| 1  | 0  | 0     | 0         | 8       | 0  | 0  | 0       | 1        | 1       |

| 1  | 0  | 0     | 1         | 9       | 1  | 0  | 0       | 1        | 9       |

| 1  | 0  | 1     | 0         | 10      | 0  | 1  | 0       | 1        | 5       |

| 1  | 0  | 1     | 1         | 11      | 1  | 1  | 0       | 1        | 13      |

| 1  | 1  | 0     | 0         | 12      | 0  | 0  | 1       | 1        | 3       |

| 1  | 1  | 0     | 1         | 13      | 1  | 0  | 1       | 1        | 11      |

| 1  | 1  | 1     | 0         | 14      | 0  | 1  | 1       | 1        | 7       |

| 1  | 1  | 1     | 1         | 15      | 1  | 1  | 1       | 1        | 15      |

#### 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows a dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD),

ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user application can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time or a single program memory word, and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

#### 5.1 Table Instructions and Flash Programming

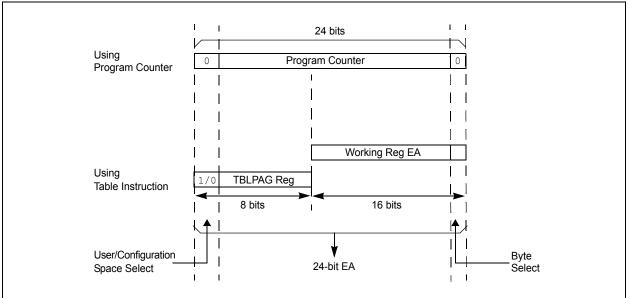

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits <7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| U-0          | U-0           | R/W-0                                                 | U-0            | U-0              | U-0             | U-0             | U-0     |  |  |

|--------------|---------------|-------------------------------------------------------|----------------|------------------|-----------------|-----------------|---------|--|--|

| _            |               | INT2IF                                                | —              |                  | —               |                 |         |  |  |

| bit 15       |               |                                                       |                |                  |                 |                 | bit 8   |  |  |

|              |               |                                                       |                |                  |                 |                 |         |  |  |

| R/W-0        | R/W-0         | U-0                                                   | R/W-0          | R/W-0            | U-0             | R/W-0           | R/W-0   |  |  |

| IC8IF        | IC7IF         |                                                       | INT1IF         | CNIF             |                 | MI2C1IF         | SI2C1IF |  |  |

| bit 7        |               |                                                       |                |                  |                 |                 | bit (   |  |  |

| d.           |               |                                                       |                |                  |                 |                 |         |  |  |

| Legend:      |               |                                                       | L:4            |                  | nonted bit ve   |                 |         |  |  |

| R = Readab   |               | W = Writable                                          | DIT            | •                | nented bit, rea |                 |         |  |  |

| -n = Value a | t POR         | '1' = Bit is set                                      |                | '0' = Bit is cle | ared            | x = Bit is unkr | IOWN    |  |  |

| bit 15-14    | Unimplemer    | nted: Read as '                                       | ז'             |                  |                 |                 |         |  |  |

| bit 13       | -             | rnal Interrupt 2                                      |                | it               |                 |                 |         |  |  |

|              |               | request has occ                                       | •              |                  |                 |                 |         |  |  |

|              |               | request has not                                       |                |                  |                 |                 |         |  |  |

| bit 12-8     | Unimplemer    | nted: Read as '                                       | )'             |                  |                 |                 |         |  |  |

| bit 7        | IC8IF: Input  | Capture Channe                                        | el 8 Interrupt | Flag Status bit  |                 |                 |         |  |  |

|              |               | request has occ                                       |                |                  |                 |                 |         |  |  |

|              | -             | request has not                                       |                |                  |                 |                 |         |  |  |

| bit 6        | •             | Capture Channe                                        | •              | Flag Status bit  |                 |                 |         |  |  |

|              |               | request has occ                                       |                |                  |                 |                 |         |  |  |

| bit 5        |               | request has not<br>nted: Read as '(                   |                |                  |                 |                 |         |  |  |

| bit 4        | •             | rnal Interrupt 1                                      |                | :+               |                 |                 |         |  |  |

| DIL 4        |               | request has occ                                       | •              | п                |                 |                 |         |  |  |

|              |               | request has not                                       |                |                  |                 |                 |         |  |  |

| bit 3        | •             | Change Notifica                                       |                | Flag Status bit  |                 |                 |         |  |  |

|              | •             | request has occ                                       | •              | - 3              |                 |                 |         |  |  |

|              | 0 = Interrupt | request has not                                       | occurred       |                  |                 |                 |         |  |  |

| bit 2        | Unimplemer    | nted: Read as '                                       | )'             |                  |                 |                 |         |  |  |

| bit 1        | MI2C1IF: 120  | MI2C1IF: I2C1 Master Events Interrupt Flag Status bit |                |                  |                 |                 |         |  |  |

|              |               | request has occ                                       |                |                  |                 |                 |         |  |  |

|              | •             | request has not                                       |                |                  |                 |                 |         |  |  |

| bit 0        |               | 1 Slave Events                                        |                | g Status bit     |                 |                 |         |  |  |

|              |               | request has occur                                     |                |                  |                 |                 |         |  |  |

|              | 0 = interrupt | request has not                                       | occurred       |                  |                 |                 |         |  |  |

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

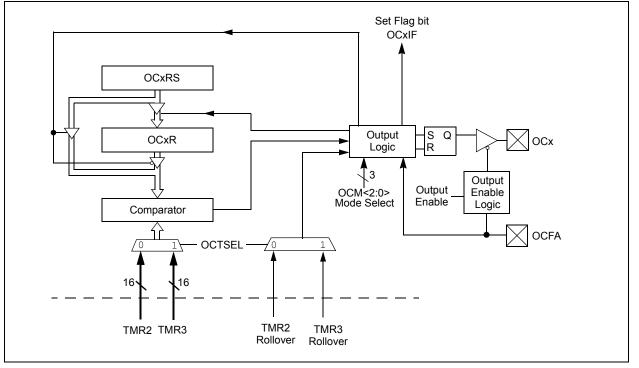

### 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

#### FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

#### 14.3 Output Compare Register

#### REGISTER 14-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER

| U-0      | U-0 | R/W-0          | U-0        | U-0           | U-0      | U-0      | U-0   |

|----------|-----|----------------|------------|---------------|----------|----------|-------|

| _        | _   | OCSIDL         | —          | —             | _        | —        | _     |

| bit 15   |     | ·              |            |               |          |          | bit 8 |

|          |     |                |            |               |          |          |       |

| U-0      | U-0 | U-0            | R-0 HC     | R/W-0         | R/W-0    | R/W-0    | R/W-0 |

| —        | —   | —              | OCFLT      | OCTSEL        |          | OCM<2:0> |       |

| bit 7    |     |                |            |               |          |          | bit 0 |

|          |     |                |            |               |          |          |       |

| l egend: |     | HC = Cleared i | n Hardware | HS = Set in H | Hardware |          |       |

| Legend:           | HC = Cleared in Hardware | HS = Set in Hardware       |                    |

|-------------------|--------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>1 = Output Compare x will halt in CPU Idle mode</li> <li>0 = Output Compare x will continue to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred<br/>(This bit is only used when OCM&lt;2:0&gt; = 111.)</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | <ul> <li>1 = Timer3 is the clock source for Compare x</li> <li>0 = Timer2 is the clock source for Compare x</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = PWM mode on OCx, Fault pin enabled</li> <li>110 = PWM mode on OCx, Fault pin disabled</li> <li>101 = Initialize OCx pin low, generate continuous output pulses on OCx pin</li> <li>100 = Initialize OCx pin low, generate single output pulse on OCx pin</li> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initialize OCx pin high, compare event forces OCx pin low</li> <li>001 = Initialize OCx pin low, compare event forces OCx pin high</li> <li>000 = Output compare channel is disabled</li> </ul> |

#### REGISTER 18-2: AD1CON2: ADC1 CONTROL REGISTER 2

| R/W-0  | R/W-0     | R/W-0 | U-0   | U-0   | R/W-0 | R/W-0 | R/W-0  |

|--------|-----------|-------|-------|-------|-------|-------|--------|

|        | VCFG<2:0> |       | —     | _     | CSCNA | CHPS  | S<1:0> |

| bit 15 |           |       |       |       |       |       | bit 8  |

|        |           |       |       |       |       |       |        |

| R-0    | U-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

| BUFS   | _         |       | SMP   | <3:0> |       | BUFM  | ALTS   |

| bit 7  |           |       |       |       |       |       | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-13 VCFG<2:0>: Converter Voltage Reference Configuration bits

| bit 15-13 | VCFG<2:0>: Converter Voltage Reference Configuration bits                                                                                                                    |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|           | ADREF+                                                                                                                                                                       | ADREF-                                                                                                                                                                                      |                                                                                                                    |  |  |  |  |  |  |

|           | 000 Avdd                                                                                                                                                                     | Avss                                                                                                                                                                                        |                                                                                                                    |  |  |  |  |  |  |

|           | 001 External VREF                                                                                                                                                            | Avss                                                                                                                                                                                        |                                                                                                                    |  |  |  |  |  |  |

|           | 010 AVDD                                                                                                                                                                     |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           | 011 External VREF                                                                                                                                                            | External VREF-                                                                                                                                                                              |                                                                                                                    |  |  |  |  |  |  |

|           | 1xx AVDD                                                                                                                                                                     | Avss                                                                                                                                                                                        |                                                                                                                    |  |  |  |  |  |  |

| bit 12-11 | Unimplemented: Read                                                                                                                                                          | <b>as</b> '0'                                                                                                                                                                               |                                                                                                                    |  |  |  |  |  |  |

| bit 10    | CSCNA: Scan Input Se                                                                                                                                                         | ections for CH0+ dur                                                                                                                                                                        | ing Sample A bit                                                                                                   |  |  |  |  |  |  |

|           | 1 = Scan inputs                                                                                                                                                              |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           | 0 = Do not scan inputs                                                                                                                                                       |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

| bit 9-8   | CHPS<1:0>: Select Ch                                                                                                                                                         |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           |                                                                                                                                                                              |                                                                                                                                                                                             | nplemented, Read as '0'                                                                                            |  |  |  |  |  |  |

|           | 1x = Converts CH0, CH<br>01 = Converts CH0 and                                                                                                                               | ,                                                                                                                                                                                           |                                                                                                                    |  |  |  |  |  |  |

|           | 00 = Converts CH0                                                                                                                                                            |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

| bit 7     | BUFS: Buffer Fill Status                                                                                                                                                     | bit (valid only when                                                                                                                                                                        | 3UFM = 1)                                                                                                          |  |  |  |  |  |  |

|           |                                                                                                                                                                              |                                                                                                                                                                                             | ffer, user application should access data in the first half user application should access data in the second half |  |  |  |  |  |  |

| bit 6     | Unimplemented: Read                                                                                                                                                          | <b>as</b> '0'                                                                                                                                                                               |                                                                                                                    |  |  |  |  |  |  |

| bit 5-2   | SMPI<3:0>: Sample/Co                                                                                                                                                         | nvert Sequences Pe                                                                                                                                                                          | Interrupt Selection bits                                                                                           |  |  |  |  |  |  |

|           |                                                                                                                                                                              |                                                                                                                                                                                             | rsion for each 16th sample/convert sequence                                                                        |  |  |  |  |  |  |

|           | 1110 = Interrupts at the completion of conversion for each 15th sample/convert sequence                                                                                      |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           | •                                                                                                                                                                            |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           | •                                                                                                                                                                            |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           | 0001 = Interrupts at the completion of conversion for each 2nd sample/convert sequence<br>0000 = Interrupts at the completion of conversion for each sample/convert sequence |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

| bit 1     | BUFM: Buffer Fill Mode Select bit                                                                                                                                            |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

|           |                                                                                                                                                                              | <ul> <li>1 = Starts filling first half of buffer on first interrupt and the second half of buffer on next interrupt</li> <li>0 = Always starts filling buffer from the beginning</li> </ul> |                                                                                                                    |  |  |  |  |  |  |

| bit 0     | ALTS: Alternate Input S                                                                                                                                                      | ample Mode Select b                                                                                                                                                                         | vit                                                                                                                |  |  |  |  |  |  |

|           | <ol> <li>1 = Uses channel input</li> <li>0 = Always uses channel</li> </ol>                                                                                                  | •                                                                                                                                                                                           | on first sample and Sample B on next sample ample A                                                                |  |  |  |  |  |  |

|           |                                                                                                                                                                              |                                                                                                                                                                                             |                                                                                                                    |  |  |  |  |  |  |

#### REGISTER 18-5: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample A bits<br>dsPIC33FJ32GP204 and dsPIC33FJ16GP304 devices only:<br>01100 = Channel 0 positive input is AN12 |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 00010 = Channel 0 positive input is AN2<br>00001 = Channel 0 positive input is AN1<br>00000 = Channel 0 positive input is AN0                                    |

|         | dsPIC33FJ32GP202 devices only:<br>01100 = Channel 0 positive input is AN12<br>•<br>•<br>01000 = Reserved<br>00111 = Reserved<br>00110 = Reserved                 |

|         | <ul> <li>00010 = Channel 0 positive input is AN2</li> <li>00001 = Channel 0 positive input is AN1</li> <li>00000 = Channel 0 positive input is AN0</li> </ul>    |

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                             |

|-----------|----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ICS<1:0>  | FICD     | Immediate      | ICD Communication Channel Select bits<br>11 = Communicate on PGEC1 and PGED1<br>10 = Communicate on PGEC2 and PGED2<br>01 = Communicate on PGEC3 and PGED3<br>00 = Reserved, do not use |

#### TABLE 19-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

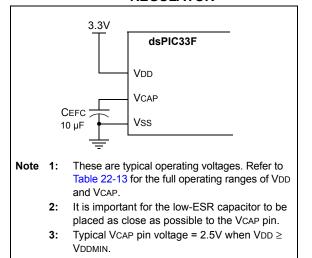

#### 19.2 On-Chip Voltage Regulator

All of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 19-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 22-13 located in Section 22.1 "DC Characteristics".

| Note: | It is important for the low-ESR capacitor to |

|-------|----------------------------------------------|

|       | be placed as close as possible to the VCAP   |

|       | pin.                                         |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 19-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 19.3 BOR: Brown-out Reset

The Brown-out Reset (BOR) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| DC CHARACTERISTICS |                        |     | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |       |                  |      |         |

|--------------------|------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|------|---------|

| Parameter No.      | Typical <sup>(2)</sup> | Max | Doze<br>Ratio                                                                                                                                                                            | Units | Inits Conditions |      |         |

| Doze Current (IDO  | ze) <sup>(1)</sup>     |     |                                                                                                                                                                                          |       |                  |      |         |

| DC73a              | 41                     | 51  | 1:2                                                                                                                                                                                      | mA    |                  |      |         |

| DC73f              | 20                     | 28  | 1:64                                                                                                                                                                                     | mA    | -40°C            | 3.3V | 40 MIPS |

| DC73g              | 19                     | 24  | 1:128                                                                                                                                                                                    | mA    |                  |      |         |

| DC70a              | 40                     | 46  | 1:2                                                                                                                                                                                      | mA    |                  |      |         |

| DC70f              | 18                     | 20  | 1:64                                                                                                                                                                                     | mA    | +25°C            | 3.3V | 40 MIPS |

| DC70g              | 18                     | 20  | 1:128                                                                                                                                                                                    | mA    |                  |      |         |

| DC71a              | 40                     | 46  | 1:2                                                                                                                                                                                      | mA    |                  |      |         |

| DC71f              | 18                     | 25  | 1:64                                                                                                                                                                                     | mA    | +85°C            | 3.3V | 40 MIPS |

| DC71g              | 18                     | 20  | 1:128                                                                                                                                                                                    | mA    |                  |      |         |

| DC72a              | 39                     | 55  | 1:2                                                                                                                                                                                      | mA    |                  | Ì    |         |

| DC72f              | 18                     | 30  | 1:64                                                                                                                                                                                     | mA    | +125°C           | 3.3V | 40 MIPS |

| DC72g              | 18                     | 25  | 1:128                                                                                                                                                                                    | mA    |                  |      |         |

#### TABLE 22-8: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail with overshoot/undershoot < 250 mV</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (defined PMDx bits are set to zero and unimplemented PMDx bits are set to one)

- CPU executing while (1) statement

- JTAG is disabled

- **2:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

#### TABLE 22-17:PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stateOperating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |     |     |                    |     |       |                                |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|-----|-------|--------------------------------|

| Param<br>No.       | Symbol | Characteris                                                                                                                                                                                             | tic | Min | Тур <sup>(1)</sup> | Max | Units | Conditions                     |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range <sup>(2)</sup>                                                                                                                      |     | 0.8 |                    | 8   | MHz   | ECPLL, XTPLL modes             |

| OS51               | Fsys   | On-Chip VCO System<br>Frequency <sup>(3)</sup>                                                                                                                                                          |     | 100 | _                  | 200 | MHz   | _                              |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time) <sup>(3)</sup>                                                                                                                                                            |     | 0.9 | 1.5                | 3.1 | ms    | —                              |

| OS53               | DCLK   | CLKO Stability (Jitter)                                                                                                                                                                                 | (3) | -3  | 0.5                | 3   | %     | Measured over 100 ms<br>period |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: These parameters are characterized by similarity, but are tested in manufacturing at 7.7 MHz input only.

**3:** These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: Fosc = 32 MHz, DCLK = 3%, SPI bit rate clock, (i.e., SCK) is 2 MHz.

$$SPI SCK Jitter = \left[\frac{D_{CLK}}{\sqrt{\left(\frac{32 MHz}{2 MHz}\right)}}\right] = \left[\frac{3\%}{\sqrt{16}}\right] = \left[\frac{3\%}{4}\right] = 0.75\%$$

#### TABLE 22-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICS       Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for industrial         -40°C ≤TA ≤+125°C for Extended |                                                                 |     |                              |    |   |                   | rial           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|------------------------------|----|---|-------------------|----------------|

| Param<br>No.                                                                                                                                                                                              | Characteristic                                                  | Min | Min Typ Max Units Conditions |    |   |                   | lions          |

|                                                                                                                                                                                                           | Internal FRC Accuracy @ FRC Frequency = 7.37 MHz <sup>(1)</sup> |     |                              |    |   |                   |                |

| F20a                                                                                                                                                                                                      | FRC                                                             | -2  | _                            | +2 | % | -40°C ≤TA ≤+85°C  | VDD = 3.0-3.6V |

| F20b                                                                                                                                                                                                      | FRC                                                             | -5  | _                            | +5 | % | -40°C ≤TA ≤+125°C | VDD = 3.0-3.6V |

**Note 1:** Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

#### TABLE 22-19: INTERNAL RC ACCURACY

| AC CHARACTERISTICS       Standard Operating Conditions: 3.0V to 3.6V (unless otherwise state         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                    |                              |    |     |   |                   | erwise stated) |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------|----|-----|---|-------------------|----------------|--|

| Param<br>No.                                                                                                                                                                                            | Characteristic                     | Min Typ Max Units Conditions |    |     |   |                   |                |  |

|                                                                                                                                                                                                         | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                              |    |     |   |                   |                |  |

| F21a                                                                                                                                                                                                    | LPRC                               | -15                          | ±6 | +15 | % | -40°C ≤TA ≤+85°C  | VDD = 3.0-3.6V |  |

| F21b                                                                                                                                                                                                    | LPRC                               | -40                          | _  | +40 | % | -40°C ≤Ta ≤+125°C | VDD = 3.0-3.6V |  |

**Note 1:** Change of LPRC frequency as VDD changes.

2: LPRC impacts the Watchdog Timer Time-out Period (TWDT1). See Section 19.4 "Watchdog Timer (WDT)" for more information.

#### TABLE 22-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

|              |        |                                                                               | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                 |     |       |                                                                                      |  |