#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp202-e-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

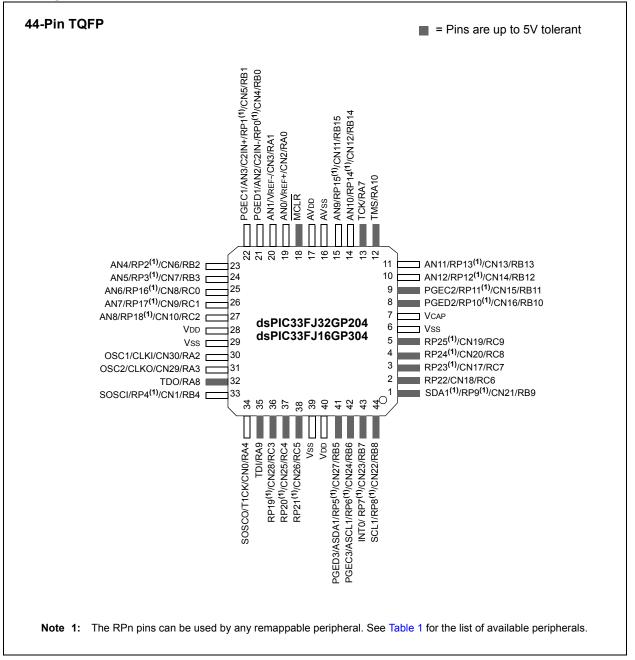

## Pin Diagrams (Continued)

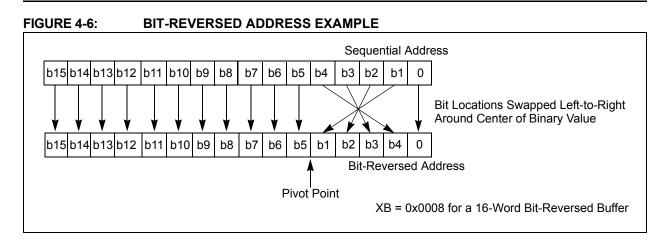

## TABLE 4-24: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

| Normal Address Bit-Reversed Address |    |    |    |         | Idress |    |    |    |         |

|-------------------------------------|----|----|----|---------|--------|----|----|----|---------|

| A3                                  | A2 | A1 | A0 | Decimal | A3     | A2 | A1 | A0 | Decimal |

| 0                                   | 0  | 0  | 0  | 0       | 0      | 0  | 0  | 0  | 0       |

| 0                                   | 0  | 0  | 1  | 1       | 1      | 0  | 0  | 0  | 8       |

| 0                                   | 0  | 1  | 0  | 2       | 0      | 1  | 0  | 0  | 4       |

| 0                                   | 0  | 1  | 1  | 3       | 1      | 1  | 0  | 0  | 12      |

| 0                                   | 1  | 0  | 0  | 4       | 0      | 0  | 1  | 0  | 2       |

| 0                                   | 1  | 0  | 1  | 5       | 1      | 0  | 1  | 0  | 10      |

| 0                                   | 1  | 1  | 0  | 6       | 0      | 1  | 1  | 0  | 6       |

| 0                                   | 1  | 1  | 1  | 7       | 1      | 1  | 1  | 0  | 14      |

| 1                                   | 0  | 0  | 0  | 8       | 0      | 0  | 0  | 1  | 1       |

| 1                                   | 0  | 0  | 1  | 9       | 1      | 0  | 0  | 1  | 9       |

| 1                                   | 0  | 1  | 0  | 10      | 0      | 1  | 0  | 1  | 5       |

| 1                                   | 0  | 1  | 1  | 11      | 1      | 1  | 0  | 1  | 13      |

| 1                                   | 1  | 0  | 0  | 12      | 0      | 0  | 1  | 1  | 3       |

| 1                                   | 1  | 0  | 1  | 13      | 1      | 0  | 1  | 1  | 11      |

| 1                                   | 1  | 1  | 0  | 14      | 0      | 1  | 1  | 1  | 7       |

| 1                                   | 1  | 1  | 1  | 15      | 1      | 1  | 1  | 1  | 15      |

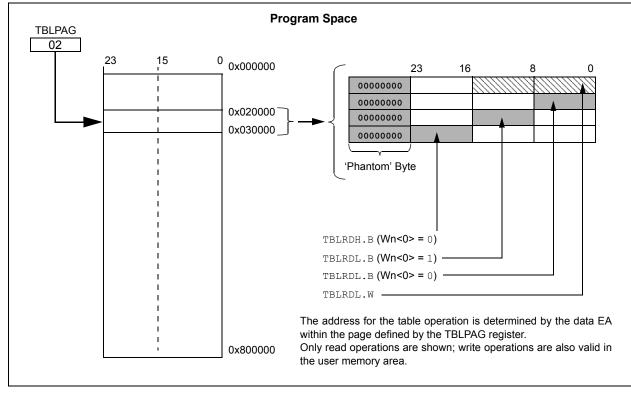

#### 4.8.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

• TBLRDL (Table Read Low): In Word mode, this instruction maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

• TBLRDH (Table Read High): In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address, as in the TBLRDL instruction. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in Section 5.0 "Flash Program Memory".

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-8: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

| U-0              | U-0 | U-0            | U-0      | U-0                                | U-0 | U-0 | U-0   |

|------------------|-----|----------------|----------|------------------------------------|-----|-----|-------|

| —                | _   | —              | _        | —                                  | —   | —   | —     |

| bit 15           |     |                |          |                                    |     |     | bit 8 |

|                  |     |                |          |                                    |     |     |       |

| W-0              | W-0 | W-0            | W-0      | W-0                                | W-0 | W-0 | W-0   |

|                  |     |                | NVMK     | EY<7:0>                            |     |     |       |

| bit 7            |     |                |          |                                    |     |     | bit 0 |

|                  |     |                |          |                                    |     |     |       |

| Legend:          |     | SO = Settable  | Only bit |                                    |     |     |       |

| R = Readable bit |     | W = Writable I | bit      | U = Unimplemented bit, read as '0' |     |     |       |

#### NVMKEY: NONVOLATILE MEMORY KEY REGISTER **REGISTER 5-2:**

| Legend:           | SO = Settable Only bit |                                    |                    |  |

|-------------------|------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared               | x = Bit is unknown |  |

Unimplemented: Read as '0' bit 15-8

bit 7-0 NVMKEY<7:0>: Key Register (Write Only) bits

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 2

IDLE: Wake-up from Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1

BOR: Brown-out Reset Flag bit

1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

bit 0

POR: Power-on Reset Flag bit

1 = A Power-on Reset has occurred

- 0 = A Power-on Reset has occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

# 7.3 Interrupt Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | the product page using the link above,  |  |  |  |  |  |  |

|       | enter this URL in your browser:         |  |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/   |  |  |  |  |  |  |

|       | Devices.aspx?dDocName=en530331          |  |  |  |  |  |  |

#### 7.3.1 KEY RESOURCES

- Section 6. "Interrupts" (DS70184)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 7.4 Interrupt Control and Status Registers

dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices implement a total of 17 registers for the interrupt controller:

- Interrupt Control Register 1 (INTCON1)

- Interrupt Control Register 2 (INTCON2)

- Interrupt Flag Status Registers (IFSx)

- Interrupt Enable Control Registers (IECx)

- Interrupt Priority Control Registers (IPCx)

- Interrupt Control and Status Register (INTTREG)

### 7.4.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

## 7.4.2 IFSx

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

## 7.4.3 IECx

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

### 7.4.4 IPCx

The IPC registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

### 7.4.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt priority Level, which are latched into the vector number (VECNUM<6:0>) and Interrupt level bits (ILR<3:0>) in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first position of IPC0 (IPC0<2:0>).

### 7.4.6 STATUS REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality:

- The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit, so that trap events cannot be masked by the user software.

All Interrupt bits and registers are described in Register 7-1 through Register 7-19.

| R-0                  | R-0                  | R/C-0                | R/C-0 | R-0          | R/C-0            | R -0     | R/W-0 |

|----------------------|----------------------|----------------------|-------|--------------|------------------|----------|-------|

| OA                   | OB                   | SA                   | SB    | OAB          | SAB              | DA       | DC    |

| bit 15               |                      |                      |       |              |                  |          | bit 8 |

|                      |                      |                      |       |              |                  |          |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0   | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA    | N            | OV               | Z        | С     |

| bit 7                |                      | ·                    |       |              | •                |          | bit 0 |

|                      |                      |                      |       |              |                  |          |       |

| Legend:              |                      |                      |       |              |                  |          |       |

| C = Clear only       | bit                  | R = Readable         | bit   | U = Unimplei | mented bit, read | l as '0' |       |

#### SR: CPU STATUS REGISTER<sup>(1)</sup> **REGISTER 7-1:**

| Legend:            |                      |                                    |

|--------------------|----------------------|------------------------------------|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |

bit 7-5

bit 3

IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

- 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

Note 1: For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS bit (INTCON1<15>) = 1.

#### CORCON: CORE CONTROL REGISTER<sup>(1)</sup> **REGISTER 7-2:**

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R-0 | R-0     | R-0   |

|--------|-----|-----|-------|-------|-----|---------|-------|

| —      | —   | —   | US    | EDT   |     | DL<2:0> |       |

| bit 15 |     |     |       |       |     |         | bit 8 |

|        |     |     |       |       |     |         |       |

| R/W-0 | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------------------|-------|-------|-------|

| SATA  | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND   | IF    |

| bit 7 |       |       |        |                     |       |       | bit 0 |

| Legend:             | C = Clear only bit  |                             |                  |

|---------------------|---------------------|-----------------------------|------------------|

| R = Readable bit    | W = Writable bit    | -n = Value at POR           | '1' = Bit is set |

| 0' = Bit is cleared | 'x = Bit is unknown | U = Unimplemented bit, read | l as '0'         |

IPL3: CPU Interrupt Priority Level Status bit 3<sup>(2)</sup>

- 1 = CPU Interrupt Priority Level is greater than 7

- 0 = CPU Interrupt Priority Level is 7 or less

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## 10.9 Peripheral Pin Select Registers

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices implement 17 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (9)

- Output Remappable Peripheral Registers (8)

| Note: | Input and Output Register values can only |

|-------|-------------------------------------------|

|       | be changed if OSCCON[IOLOCK] = 0.         |

|       | See Section 10.6.3.1 "Control Register    |

|       | Lock" for a specific command sequence.    |

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0                                | U-0 | U-0          | R/W-1 | R/W-1                                   | R/W-1      | R/W-1 | R/W-1 |  |

|------------------------------------|-----|--------------|-------|-----------------------------------------|------------|-------|-------|--|

| —                                  | —   | —            |       |                                         | INT1R<4:0> |       |       |  |

| bit 15                             |     |              |       |                                         |            |       | bit 8 |  |

| U-0                                | U-0 | U-0          | U-0   | U-0                                     | U-0        | U-0   | U-0   |  |

| _                                  | —   | _            | _     | —                                       | _          | —     | —     |  |

| bit 7                              |     |              |       |                                         |            |       | bit 0 |  |

| Legend:                            |     |              |       |                                         |            |       |       |  |

| R = Readable                       | bit | W = Writable | bit   | U = Unimplemented bit, read as '0'      |            |       |       |  |

| -n = Value at POR '1' = Bit is set |     |              |       | '0' = Bit is cleared x = Bit is unknown |            |       | nown  |  |

bit 12-8

INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

11111 = Input tied to Vss

11001 = Input tied to RP25

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

| U-0                                | U-0                                                                                         | U-0                               | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1    |

|------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------|-------|------------------|-----------------|-----------------|----------|

| _                                  | _                                                                                           | _                                 |       |                  | SCK1R<4:0       | >               |          |

| bit 15                             |                                                                                             | •                                 |       |                  |                 |                 | bit 8    |

| U-0                                | U-0                                                                                         | U-0                               | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1    |

|                                    | 0-0                                                                                         | 0-0                               | N/W-1 | FV/ VV- I        | SDI1R<4:0>      |                 | D/ VV- I |

| bit 7                              |                                                                                             |                                   |       |                  | 00111(4.0)      |                 | bit 0    |

|                                    |                                                                                             |                                   |       |                  |                 |                 |          |

| Legend:                            |                                                                                             |                                   |       |                  |                 |                 |          |

| R = Readab                         | le bit                                                                                      | W = Writable                      | bit   | U = Unimplei     | mented bit, rea | ıd as '0'       |          |

| -n = Value at POR '1' = Bit is set |                                                                                             |                                   |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown     |

| bit 7-5                            | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | it tied to RP25                   | 0'    |                  |                 |                 |          |

| bit 7-5<br>bit 4-0                 | -                                                                                           |                                   |       |                  |                 | :-              |          |

| Dit <del>4</del> -0                | 11111 <b>= Inpu</b>                                                                         | it tied to RP25<br>it tied to RP1 |       |                  |                 |                 |          |

## REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

#### REGISTER 10-20: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP21R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP20R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0' |

|-----------|----------------------------|

|-----------|----------------------------|

- bit 12-8 **RP21R<4:0>:** Peripheral Output Function is Assigned to RP21 Output Pin (see Table 10-2 for peripheral function numbers)

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-21: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11

| U-0             | U-0 | U-0              | R/W-0                                       | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|-----------------|-----|------------------|---------------------------------------------|--------------|------------------|----------|-------|

| _               | —   | —                |                                             |              | RP23R<4:0>       |          |       |

| bit 15          |     | ·                |                                             |              |                  |          | bit 8 |

|                 |     |                  |                                             |              |                  |          |       |

| U-0             | U-0 | U-0              | R/W-0                                       | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| —               | _   | —                |                                             |              | RP22R<4:0>       |          |       |

| bit 7           |     |                  |                                             |              |                  |          | bit 0 |

|                 |     |                  |                                             |              |                  |          |       |

| Legend:         |     |                  |                                             |              |                  |          |       |

| R = Readable    | bit | W = Writable     | bit                                         | U = Unimpler | nented bit, read | d as '0' |       |

| -n = Value at P | OR  | '1' = Bit is set | set '0' = Bit is cleared x = Bit is unknown |              |                  |          | nown  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP23R<4:0>:** Peripheral Output Function is Assigned to RP23 Output Pin (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP22R<4:0>:** Peripheral Output Function is Assigned to RP22 Output Pin (see Table 10-2 for peripheral function numbers)

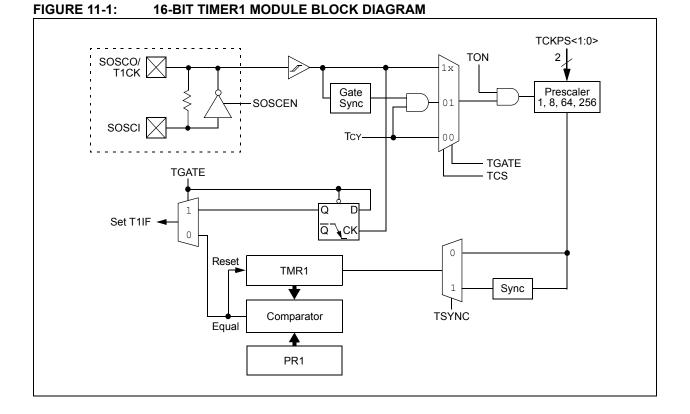

# 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site: (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 11-1 illustrates a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in the T1CON register to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

# 14.3 Output Compare Register

## REGISTER 14-1: OCxCON: OUTPUT COMPARE x CONTROL REGISTER

| U-0      | U-0 | R/W-0          | U-0        | U-0           | U-0      | U-0      | U-0   |

|----------|-----|----------------|------------|---------------|----------|----------|-------|

| _        | _   | OCSIDL         | —          | —             | _        | —        |       |

| bit 15   |     | ·              |            |               |          |          | bit 8 |

|          |     |                |            |               |          |          |       |

| U-0      | U-0 | U-0            | R-0 HC     | R/W-0         | R/W-0    | R/W-0    | R/W-0 |

| —        | —   | —              | OCFLT      | OCTSEL        |          | OCM<2:0> |       |

| bit 7    |     |                |            |               |          |          | bit 0 |

|          |     |                |            |               |          |          |       |

| l egend: |     | HC = Cleared i | n Hardware | HS = Set in H | Hardware |          |       |

| Legend:           | HC = Cleared in Hardware | HS = Set in Hardware       |                    |

|-------------------|--------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | <ul> <li>1 = Output Compare x will halt in CPU Idle mode</li> <li>0 = Output Compare x will continue to operate in CPU Idle mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred<br/>(This bit is only used when OCM&lt;2:0&gt; = 111.)</li> </ul>                                                                                                                                                                                                                                                                                                                                         |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           | <ul> <li>1 = Timer3 is the clock source for Compare x</li> <li>0 = Timer2 is the clock source for Compare x</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | <ul> <li>111 = PWM mode on OCx, Fault pin enabled</li> <li>110 = PWM mode on OCx, Fault pin disabled</li> <li>101 = Initialize OCx pin low, generate continuous output pulses on OCx pin</li> <li>100 = Initialize OCx pin low, generate single output pulse on OCx pin</li> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initialize OCx pin high, compare event forces OCx pin low</li> <li>001 = Initialize OCx pin low, compare event forces OCx pin high</li> <li>000 = Output compare channel is disabled</li> </ul> |

| R/W-0                            | U-0                                                                                                                                                                                                                                            | R/W-0                                                                                                                                                                                                      | R/W-1 HC                                                                                                               | R/W-0                                          | R/W-0                          | R/W-0                    | R/W-0         |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------|--------------------------|---------------|

| I2CEN                            | —                                                                                                                                                                                                                                              | I2CSIDL                                                                                                                                                                                                    | SCLREL                                                                                                                 | IPMIEN                                         | A10M                           | DISSLW                   | SMEN          |

| bit 15                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |                                                                                                                        |                                                |                                |                          | bit 8         |

| R/W-0                            | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                      | R/W-0 HC                                                                                                               | R/W-0 HC                                       | R/W-0 HC                       | R/W-0 HC                 | R/W-0 HC      |

| GCEN                             | STREN                                                                                                                                                                                                                                          | ACKDT                                                                                                                                                                                                      | ACKEN                                                                                                                  | RCEN                                           | PEN                            | RSEN                     | SEN           |

| bit 7                            | Onten                                                                                                                                                                                                                                          | , tone i                                                                                                                                                                                                   | AGREN                                                                                                                  | ROEN                                           | 1 214                          | ROER                     | bit (         |

| Legend:                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                            | nented bit, read                                                                                                       | d ac 'O'                                       |                                |                          |               |

| R = Readable                     | a hit                                                                                                                                                                                                                                          | W = Writable                                                                                                                                                                                               |                                                                                                                        | HS = Set in h                                  | ardware                        | HC = Cleared             | in hardware   |

| -n = Value at                    |                                                                                                                                                                                                                                                | '1' = Bit is set                                                                                                                                                                                           |                                                                                                                        | '0' = Bit is cle                               |                                | x = Bit is unkr          |               |

|                                  | FUR                                                                                                                                                                                                                                            |                                                                                                                                                                                                            |                                                                                                                        |                                                | areu                           | X - DILISUIIKI           | IOWIT         |

| bit 15                           | 12CEN: 12Cx                                                                                                                                                                                                                                    | Enable bit                                                                                                                                                                                                 |                                                                                                                        |                                                |                                |                          |               |

|                                  |                                                                                                                                                                                                                                                |                                                                                                                                                                                                            |                                                                                                                        |                                                | nd SCLx pins a by port functio | as serial port pir<br>ns | าร            |

| bit 14                           | Unimplemen                                                                                                                                                                                                                                     | ted: Read as '                                                                                                                                                                                             | 0'                                                                                                                     |                                                |                                |                          |               |

| bit 13                           | I2CSIDL: Sto                                                                                                                                                                                                                                   | p in Idle Mode                                                                                                                                                                                             | bit                                                                                                                    |                                                |                                |                          |               |

|                                  |                                                                                                                                                                                                                                                |                                                                                                                                                                                                            | ration when de<br>ion in Idle mod                                                                                      |                                                | ı Idle mode                    |                          |               |

| bit 12                           | SCLREL: SC                                                                                                                                                                                                                                     | Lx Release Co                                                                                                                                                                                              | ontrol bit (when                                                                                                       | operating as                                   | l <sup>2</sup> C™ slave)       |                          |               |

|                                  | 1 = Release \$<br>0 = Hold SCL                                                                                                                                                                                                                 | SCLx clock<br>x clock low (cl                                                                                                                                                                              | ock stretch)                                                                                                           |                                                |                                |                          |               |

|                                  | <u>If STREN = 1</u><br>Bit is R/W (i.e                                                                                                                                                                                                         |                                                                                                                                                                                                            | n write '0' to init                                                                                                    | tiate stretch ar                               | nd write '1' to re             | elease clock). H         | lardware clea |

|                                  | at beginning o                                                                                                                                                                                                                                 | of slave transm                                                                                                                                                                                            | ission. Hardwa                                                                                                         | are clear at en                                | d of slave rece                | ption.                   |               |

|                                  | If STREN = 0<br>Bit is R/S (i.e.<br>transmission.                                                                                                                                                                                              | ., software can                                                                                                                                                                                            | only write '1' to                                                                                                      | o release cloc                                 | k). Hardware cl                | ear at beginnin          | g of slave    |

| bit 11                           |                                                                                                                                                                                                                                                |                                                                                                                                                                                                            | al Managemen                                                                                                           | t Interface (IP                                | MI) Enable bit                 |                          |               |

|                                  |                                                                                                                                                                                                                                                | le is enabled; a                                                                                                                                                                                           | all addresses A                                                                                                        |                                                |                                |                          |               |

| bit 10                           |                                                                                                                                                                                                                                                | Slave Address                                                                                                                                                                                              | <b>L</b> :                                                                                                             |                                                |                                |                          |               |

|                                  |                                                                                                                                                                                                                                                |                                                                                                                                                                                                            | 5 DIL                                                                                                                  |                                                |                                |                          |               |

|                                  |                                                                                                                                                                                                                                                | is a 10-bit slav<br>is a 7-bit slave                                                                                                                                                                       | e address                                                                                                              |                                                |                                |                          |               |

| bit 9                            | 0 = I2CxADD                                                                                                                                                                                                                                    | is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate                                                                                                                                                     | ve address<br>e address                                                                                                |                                                |                                |                          |               |

| bit 9                            | 0 = I2CxADD<br><b>DISSLW:</b> Dis<br>1 = Slew rate                                                                                                                                                                                             | is a 7-bit slave                                                                                                                                                                                           | ve address<br>e address<br>e Control bit<br>ed                                                                         |                                                |                                |                          |               |

|                                  | 0 = I2CxADD<br><b>DISSLW:</b> Dis<br>1 = Slew rate<br>0 = Slew rate                                                                                                                                                                            | is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable                                                                                                                                    | ve address<br>e address<br>e Control bit<br>ed                                                                         |                                                |                                |                          |               |

|                                  | 0 = I2CxADD<br>DISSLW: Dis<br>1 = Slew rate<br>0 = Slew rate<br>SMEN: SMB0<br>1 = Enable I/0                                                                                                                                                   | is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>us Input Levels<br>O pin threshold                                                                                              | ve address<br>e address<br>e Control bit<br>ed<br>bit<br>bit<br>s compliant wit                                        | th SMBus spe                                   | cification                     |                          |               |

| bit 8                            | 0 = I2CxADD<br>DISSLW: Dis<br>1 = Slew rate<br>0 = Slew rate<br>SMEN: SMBu<br>1 = Enable I/0<br>0 = Disable S                                                                                                                                  | is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>us Input Levels<br>O pin threshold<br>MBus input thr                                                                            | ve address<br>e address<br>e Control bit<br>ed<br>bit<br>ls compliant wit<br>resholds                                  |                                                |                                |                          |               |

| bit 8                            | 0 = I2CxADD<br>DISSLW: Dis<br>1 = Slew rate<br>0 = Slew rate<br>SMEN: SMBu<br>1 = Enable I/0<br>0 = Disable S<br>GCEN: Gene<br>1 = Enable ir<br>(module                                                                                        | is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>us Input Levels<br>O pin threshold<br>MBus input the<br>ral Call Enable<br>is enabled for                                       | ve address<br>a ddress<br>a Control bit<br>ed<br>bit<br>ls compliant wit<br>resholds<br>a general call a<br>reception) | rating as I <sup>2</sup> C s                   |                                | xRSR                     |               |

| bit 9<br>bit 8<br>bit 7<br>bit 6 | <ul> <li>0 = I2CxADD</li> <li>DISSLW: Dis</li> <li>1 = Slew rate</li> <li>0 = Slew rate</li> <li>SMEN: SMBut</li> <li>1 = Enable I/0</li> <li>0 = Disable S</li> <li>GCEN: Gene</li> <li>1 = Enable in (module</li> <li>0 = General</li> </ul> | is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>us Input Levels<br>D pin threshold<br>MBus input the<br>ral Call Enable<br>nterrupt when a<br>is enabled for<br>call address di | ve address<br>a ddress<br>a Control bit<br>ed<br>bit<br>ls compliant wit<br>resholds<br>a general call a<br>reception) | rating as I <sup>2</sup> C s<br>ddress is rece | lave)<br>ived in the I2C:      | xRSR                     |               |

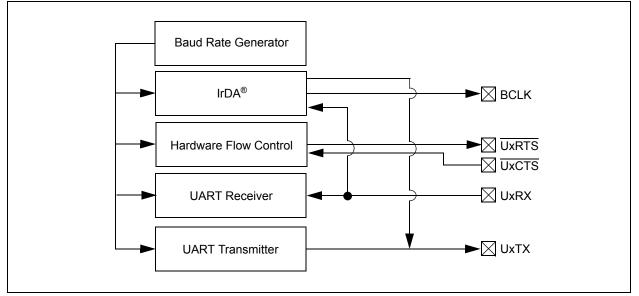

# 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-bit or 9-bit Data Transmission through the UxTX and UxRX pins

- Even, odd or no parity options (for 8-bit data)

- One or two stop bits

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-bit prescaler

- Baud rates ranging from 10 Mbps to 38 bps at 40 MIPS

- 4-deep first-in-first-out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, framing and buffer overrun error detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive interrupts

- A separate interrupt for all UART error conditions

- · Loopback mode for diagnostic support

- · Support for Sync and Break characters

- · Support for automatic baud rate detection

- IrDA<sup>®</sup> encoder and decoder logic

- 16x baud clock output for IrDA<sup>®</sup> support

A simplified block diagram of the UART module is shown in Figure 17-1. The UART module consists of these key hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

### FIGURE 17-1: UART SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 18-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0        | R/W-0 | R/W-0   |

|--------|-----|-----|-----|-----|--------------|-------|---------|

| —      | —   | —   | —   | —   | CH123NB<1:0> |       | CH123SB |

| bit 15 |     |     |     |     |              |       | bit 8   |

|        |     |     |     |     |              |       |         |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0   | R/W-0   |

|-------|-----|-----|-----|-----|--------|---------|---------|

| _     | —   | —   | —   | —   | CH123N | IA<1:0> | CH123SA |

| bit 7 |     |     |     |     |        |         | bit 0   |

### Legend:

| Legenu.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 15-11 Unimplemented: Read as '0'

bit 10-9 CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample B bits dsPIC33FJ32GP202 devices only:

- <u>If AD12B = 1:</u> 11 = Reserved 10 = Reserved

- 01 = Reserved

- 00 = Reserved

#### If AD12B = 0:

- 11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11

- 10 = Reserved

- 01 = CH1, CH2, CH3 negative input is VREF-

- 00 = CH1, CH2, CH3 negative input is VREF-

#### dsPIC33FJ32GP204 and dsPIC33FJ16GP304 devices only:

- <u>If AD12B = 1:</u> 11 = Reserved

- 10 = Reserved

- 01 = Reserved 00 = Reserved

#### If AD12B = 0:

11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8 01 = CH1, CH2, CH3 negative input is VREF-00 = CH1, CH2, CH3 negative input is VREF-

bit 8

CH123SB: Channel 1, 2, 3 Positive Input Select for Sample B bit

| If AD12B = 1: |  |  |  |

|---------------|--|--|--|

| 1 = Reserved  |  |  |  |

| 0 = Reserved  |  |  |  |

If AD12B = 0:

1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5 0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2

bit 7-3 Unimplemented: Read as '0'

| IADL               | E 20-2:              | INSIRU  | JCTION SET OVERVIE         |                                                             |               | 1              |                          |

|--------------------|----------------------|---------|----------------------------|-------------------------------------------------------------|---------------|----------------|--------------------------|

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax            | Description                                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

| 10                 | BTSC                 | BTSC    | f,#bit4                    | Bit Test f, Skip if Clear                                   | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSC    | Ws,#bit4                   | Bit Test Ws, Skip if Clear                                  | 1             | 1<br>(2 or 3)  | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4                    | Bit Test f, Skip if Set                                     | 1             | 1<br>(2 or 3)  | None                     |

|                    |                      | BTSS    | Ws,#bit4                   | Bit Test Ws, Skip if Set                                    | 1             | 1<br>(2 or 3)  | None                     |

| 12                 | BTST                 | BTST    | f,#bit4                    | Bit Test f                                                  | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4                   | Bit Test Ws to C                                            | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4                   | Bit Test Ws to Z                                            | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb                      | Bit Test Ws <wb> to C</wb>                                  | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb                      | Bit Test Ws <wb> to Z</wb>                                  | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4                    | Bit Test then Set f                                         | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4                   | Bit Test Ws to C, then Set                                  | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4                   | Bit Test Ws to Z, then Set                                  | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23                      | Call subroutine                                             | 2             | 2              | None                     |

|                    |                      | CALL    | Wn                         | Call indirect subroutine                                    | 1             | 2              | None                     |

| 15                 | CLR                  | CLR     | f                          | f = 0x0000                                                  | 1             | 1              | None                     |

|                    |                      | CLR     | WREG                       | WREG = 0x0000                                               | 1             | 1              | None                     |

|                    |                      | CLR     | Ws                         | Ws = 0x0000                                                 | 1             | 1              | None                     |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB | Clear Accumulator                                           | 1             | 1              | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT  | Acc, wa, wad, wy, wyd, Awb | Clear Watchdog Timer                                        | 1             | 1              | WDTO,Sleep               |

| 17                 |                      |         | c                          | $f = \overline{f}$                                          | 1             | 1              |                          |

| 17                 | COM                  | COM     | f                          | <u> </u>                                                    |               |                | N,Z                      |

|                    |                      | COM     | f,WREG                     | WREG = f                                                    | 1             | 1              | N,Z                      |

|                    |                      | COM     | Ws,Wd                      | $Wd = \overline{Ws}$                                        | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f                          | Compare f with WREG                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,#lit5                   | Compare Wb with lit5                                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                      | Compare Wb with Ws (Wb – Ws)                                | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CPO                  | CPO     | f                          | Compare f with 0x0000                                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPO     | Ws                         | Compare Ws with 0x0000                                      | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                          | Compare f with WREG, with Borrow                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit5                   | Compare Wb with lit5, with Borrow                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                      | Compare Wb with Ws, with Borrow (Wb - Ws - $\overline{C}$ ) | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb, Wn                     | Compare Wb with Wn, skip if =                               | 1             | 1<br>(2 or 3)  | None                     |

| 22                 | CPSGT                | CPSGT   | Wb, Wn                     | Compare Wb with Wn, skip if >                               | 1             | 1<br>(2 or 3)  | None                     |

| 23                 | CPSLT                | CPSLT   | Wb, Wn                     | Compare Wb with Wn, skip if <                               | 1             | 1<br>(2 or 3)  | None                     |

| 24                 | CPSNE                | CPSNE   | Wb, Wn                     | Compare Wb with Wn, skip if ≠                               | 1             | 1<br>(2 or 3)  | None                     |

| 25                 | DAW                  | DAW     | Wn                         | Wn = decimal adjust Wn                                      | 1             | 1              | С                        |

| 26                 | DEC                  | DEC     | f                          | f = f - 1                                                   | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | f,WREG                     | WREG = f - 1                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | Ws,Wd                      | Wd = Ws - 1                                                 | 1             | 1              | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2    | f                          | f = f - 2                                                   | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | f,WREG                     | WREG = f - 2                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | Ws,Wd                      | Wd = Ws - 2                                                 | 1             | 1              | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI    | #lit14                     | Disable Interrupts for k instruction cycles                 | 1             | 1              | None                     |

## TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

### TABLE 22-17:PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |  |     |                    |     |       |                                |

|--------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|--------------------|-----|-------|--------------------------------|

| Param<br>No.       | Symbol | I Characteristic                                                                                                                                                                |  | Min | Тур <sup>(1)</sup> | Max | Units | Conditions                     |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range <sup>(2)</sup>                                                                                              |  | 0.8 |                    | 8   | MHz   | ECPLL, XTPLL modes             |

| OS51               | Fsys   | On-Chip VCO System<br>Frequency <sup>(3)</sup>                                                                                                                                  |  | 100 | _                  | 200 | MHz   | _                              |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time) <sup>(3)</sup>                                                                                                                                    |  | 0.9 | 1.5                | 3.1 | ms    | —                              |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(3)</sup>                                                                                                                                          |  | -3  | 0.5                | 3   | %     | Measured over 100 ms<br>period |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: These parameters are characterized by similarity, but are tested in manufacturing at 7.7 MHz input only.

**3:** These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

$$Peripheral Clock Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$