#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp202-e-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3 Special MCU Features

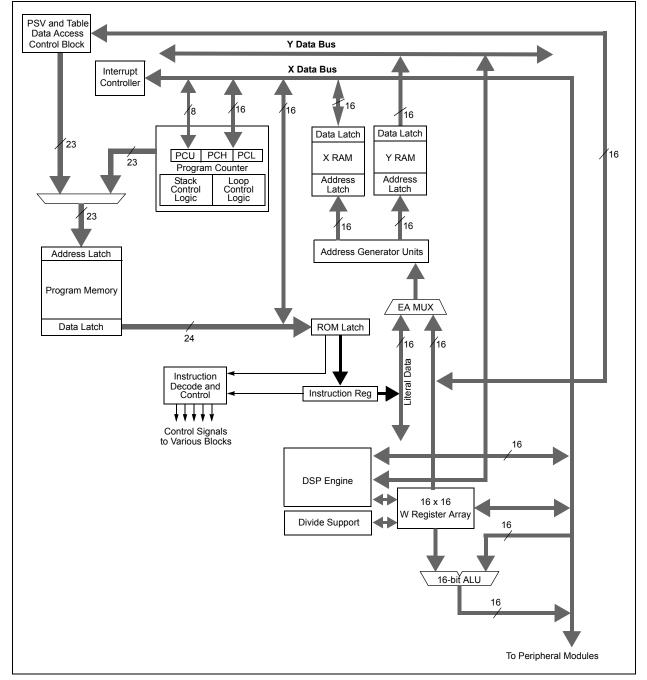

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit barrel shifter is used to perform up to a 16-bit left or right shift in a single cycle. The barrel shifter can be used by both MCU and DSP instructions.

#### FIGURE 3-1: dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 CPU CORE BLOCK DIAGRAM

| U-0              | U-0 | U-0            | U-0      | U-0          | U-0              | U-0    | U-0   |

|------------------|-----|----------------|----------|--------------|------------------|--------|-------|

| —                | _   | —              | _        | —            | —                | —      | —     |

| bit 15           |     |                |          |              |                  |        | bit 8 |

|                  |     |                |          |              |                  |        |       |

| W-0              | W-0 | W-0            | W-0      | W-0          | W-0              | W-0    | W-0   |

|                  |     |                | NVMK     | EY<7:0>      |                  |        |       |

| bit 7            |     |                |          |              |                  |        | bit 0 |

|                  |     |                |          |              |                  |        |       |

| Legend:          |     | SO = Settable  | Only bit |              |                  |        |       |

| R = Readable bit |     | W = Writable I | bit      | U = Unimpler | mented bit, read | as '0' |       |

#### NVMKEY: NONVOLATILE MEMORY KEY REGISTER **REGISTER 5-2:**

| Legend:           | SO = Settable Only bit |                             |                    |

|-------------------|------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, read | d as 'O'           |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared        | x = Bit is unknown |

Unimplemented: Read as '0' bit 15-8

bit 7-0 NVMKEY<7:0>: Key Register (Write Only) bits

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit |

|-------|----------------------------------------------------------|

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### INTOIF: External Interrupt 0 Flag Status bit

bit 0

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

# 8.3 Oscillator Control Registers

### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0                 | R-0                                                                                          | R-0                                                                                                                                                       | R-0                                                                                      | U-0              | R/W-y                       | R/W-y                              | R/W-y          |  |  |

|---------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|-----------------------------|------------------------------------|----------------|--|--|

| —                   |                                                                                              | COSC<2:0>                                                                                                                                                 |                                                                                          | —                |                             | NOSC<2:0>(2)                       |                |  |  |

| bit 15              |                                                                                              |                                                                                                                                                           |                                                                                          |                  |                             |                                    | bit 8          |  |  |

| R/W-0               | R/W-0                                                                                        | R-0                                                                                                                                                       | U-0                                                                                      | R/C-0            | U-0                         | R/W-0                              | R/W-0          |  |  |

| CLKLOCK             | IOLOCK                                                                                       | LOCK                                                                                                                                                      | _                                                                                        | CF               | —                           | LPOSCEN                            | OSWEN          |  |  |

| bit 7               |                                                                                              |                                                                                                                                                           |                                                                                          |                  |                             |                                    | bit (          |  |  |

| Legend:             |                                                                                              | v = Value set                                                                                                                                             | from Configu                                                                             | ration bits on F | POR                         | C = Clea                           | r only bit     |  |  |

| R = Readable        | e bit                                                                                        | W = Writable                                                                                                                                              | -                                                                                        |                  | mented bit, rea             |                                    | · <b>)</b> · · |  |  |

| -n = Value at I     | POR                                                                                          | '1' = Bit is se                                                                                                                                           | t                                                                                        | '0' = Bit is cle |                             | x = Bit is unkn                    | own            |  |  |

| bit 15<br>bit 14-12 | <b>COSC&lt;2:0&gt;:</b><br>111 = Fast R                                                      | ted: Read as<br>Current Oscill<br>C oscillator (Fl<br>C oscillator (Fl                                                                                    | ator Selection<br>RC) with Divid                                                         | e-by-n           | /)                          |                                    |                |  |  |

|                     | 101 = Low-Pe<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R                 | ower RC oscillator (Fl<br>ower RC oscill<br>dary oscillator<br>y oscillator (XT<br>y oscillator (Fl<br>C oscillator (Fl<br>C oscillator (Fl               | ator (LPRC)<br>(Sosc)<br>, HS, EC) with<br>, HS, EC)<br>RC) with PLL                     | -                |                             |                                    |                |  |  |

| bit 11              | Unimplemen                                                                                   | ted: Read as                                                                                                                                              | 0'                                                                                       |                  |                             |                                    |                |  |  |

| bit 10-8            | NOSC<2:0>:                                                                                   | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                                                   |                                                                                          |                  |                             |                                    |                |  |  |

|                     | 110 = Fast R<br>101 = Low-Pe<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R | C oscillator (FI<br>C oscillator (FI<br>ower RC oscill<br>dary oscillator<br>y oscillator (XT<br>y oscillator (XT<br>C oscillator (FI<br>C oscillator (FI | RC) with Divid<br>ator (LPRC)<br>(Sosc)<br>7, HS, EC) with<br>7, HS, EC)<br>RC) with PLL | e-by-16          |                             |                                    |                |  |  |

| bit 7               | CLKLOCK: (                                                                                   | Clock Lock Ena                                                                                                                                            | able bit                                                                                 |                  |                             |                                    |                |  |  |

|                     | 1 = Clock sw                                                                                 | itching is disat                                                                                                                                          | oled, system c                                                                           | lock source is   |                             | <u>0b01)</u><br>by clock switching | a              |  |  |

| bit 6               | IOLOCK: Per<br>1 = Peripheri                                                                 | ripheral Pin Se<br>ial Pin Select is                                                                                                                      | lect Lock bit<br>s locked, write                                                         | to Peripheral    | Pin Select regi             | ster is not allowe                 | d              |  |  |

| bit 5               | LOCK: PLL L                                                                                  | ock Status bit                                                                                                                                            | (read-only)                                                                              |                  |                             |                                    |                |  |  |

|                     |                                                                                              | that PLL is in that PLL is ou                                                                                                                             |                                                                                          |                  | satisfied<br>progress or PL | L is disabled                      |                |  |  |

| bit 4               | Unimplemen                                                                                   | ted: Read as                                                                                                                                              | 0'                                                                                       |                  |                             |                                    |                |  |  |

|                     | ites to this regis<br>PIC33F/PIC24F                                                          |                                                                                                                                                           |                                                                                          |                  | ection 7. "Os               | cillator" (DS701                   | 86) in the     |  |  |

|                     |                                                                                              | •                                                                                                                                                         |                                                                                          |                  | th PLL and FR               | CPLL mode are r                    | not permitted  |  |  |

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

# 9.6 Power-Saving Control Registers

| REGISTER     | 9-1: PMC                      | D1: PERIPHER                          | AL MODUL               | E DISABLE CO      | ONTROL F      | REGISTER 1     |                      |  |

|--------------|-------------------------------|---------------------------------------|------------------------|-------------------|---------------|----------------|----------------------|--|

| U-0          | U-0                           | R/W-0                                 | R/W-0                  | R/W-0             | U-0           | U-0            | U-0                  |  |

| _            | _                             | T3MD                                  | T2MD                   | T1MD              | _             | —              | _                    |  |

| bit 15       |                               |                                       |                        | · · · · · ·       |               |                | bit 8                |  |

| R/W-0        | U-0                           | R/W-0                                 | U-0                    | R/W-0             | U-0           | U-0            | R/W-0                |  |

| I2C1MD       | —                             | U1MD                                  | _                      | SPI1MD            |               | _              | AD1MD <sup>(1)</sup> |  |

| bit 7        |                               |                                       |                        |                   |               |                | bit (                |  |

| Legend:      |                               |                                       |                        |                   |               |                |                      |  |

| R = Readab   | le bit                        | W = Writable                          | bit                    | U = Unimplem      | ented bit, re | ad as '0'      |                      |  |

| -n = Value a | t POR                         | '1' = Bit is set                      |                        | ʻ0' = Bit is clea | ired          | x = Bit is unl | known                |  |

| bit 15-14    | Unimpleme                     | ented: Read as '                      | )'                     |                   |               |                |                      |  |

| bit 13       | T3MD: Time                    | er3 Module Disat                      | ole bit                |                   |               |                |                      |  |

|              |                               | module is disable<br>module is enable |                        |                   |               |                |                      |  |

| bit 12       |                               | er2 Module Disat                      |                        |                   |               |                |                      |  |

|              | 1 = Timer2 module is disabled |                                       |                        |                   |               |                |                      |  |

|              | 0 = Timer2 module is enabled  |                                       |                        |                   |               |                |                      |  |

| bit 11       | T1MD: Time                    | er1 Module Disat                      | ole bit                |                   |               |                |                      |  |

|              | -                             | module is disable<br>module is enable |                        |                   |               |                |                      |  |

| bit 10-8     | Unimpleme                     | ented: Read as '                      | )'                     |                   |               |                |                      |  |

| bit 7        | 12C1MD: 12                    | C1 Module Disat                       | ole bit                |                   |               |                |                      |  |

|              | 1 = I2C1 module is disabled   |                                       |                        |                   |               |                |                      |  |

|              |                               | odule is enabled                      |                        |                   |               |                |                      |  |

| bit 6        | -                             | ented: Read as '                      |                        |                   |               |                |                      |  |

| bit 5        |                               | RT1 Module Disa                       |                        |                   |               |                |                      |  |

|              | -                             | module is disable<br>module is enable |                        |                   |               |                |                      |  |

| bit 4        |                               | ented: Read as '                      |                        |                   |               |                |                      |  |

| bit 3        | -                             | PI1 Module Disal                      |                        |                   |               |                |                      |  |

| bit 0        |                               | odule is disabled                     |                        |                   |               |                |                      |  |

|              |                               | odule is enabled                      |                        |                   |               |                |                      |  |

| bit 2-1      | Unimpleme                     | ented: Read as '                      | )'                     |                   |               |                |                      |  |

| bit 0        | AD1MD: AD                     | DC1 Module Disa                       | ble bit <sup>(1)</sup> |                   |               |                |                      |  |

|              |                               | nodule is disable                     |                        |                   |               |                |                      |  |

|              | 0 = ADC1 m                    |                                       |                        |                   |               |                |                      |  |

# REGISTER 9-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

# 10.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) of Family "dsPIC33F/PIC24H the Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

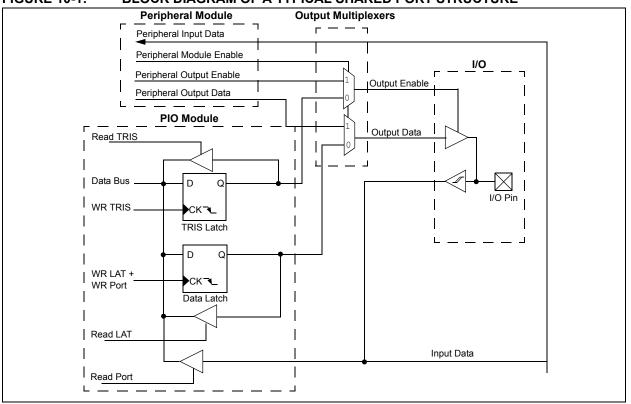

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 10.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is generally subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 10-1 shows how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch, write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

© 2007-2011 Microchip Technology Inc.

| U-0                 | U-0                                                                                         | U-0              | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1    |

|---------------------|---------------------------------------------------------------------------------------------|------------------|-------|------------------|-----------------|-----------------|----------|

| _                   | _                                                                                           | _                |       |                  | SCK1R<4:0       | >               |          |

| bit 15              |                                                                                             | •                |       |                  |                 |                 | bit 8    |

| U-0                 | U-0                                                                                         | U-0              | R/W-1 | R/W-1            | R/W-1           | R/W-1           | R/W-1    |

|                     | 0-0                                                                                         | 0-0              | N/W-1 | FV/ VV- I        | SDI1R<4:0>      |                 | D/ VV- I |

| bit 7               |                                                                                             |                  |       |                  | 00111(4.0)      |                 | bit 0    |

|                     |                                                                                             |                  |       |                  |                 |                 |          |

| Legend:             |                                                                                             |                  |       |                  |                 |                 |          |

| R = Readab          | le bit                                                                                      | W = Writable     | bit   | U = Unimplei     | mented bit, rea | ıd as '0'       |          |

| -n = Value a        | t POR                                                                                       | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown     |

| bit 7-5             | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | it tied to RP25  | 0'    |                  |                 |                 |          |

| bit 7-5<br>bit 4-0  | -                                                                                           |                  |       |                  |                 | :-              |          |

| Dit <del>4</del> -0 | 11111 <b>= Inpu</b>                                                                         | it tied to RP25  |       |                  |                 |                 |          |

### REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

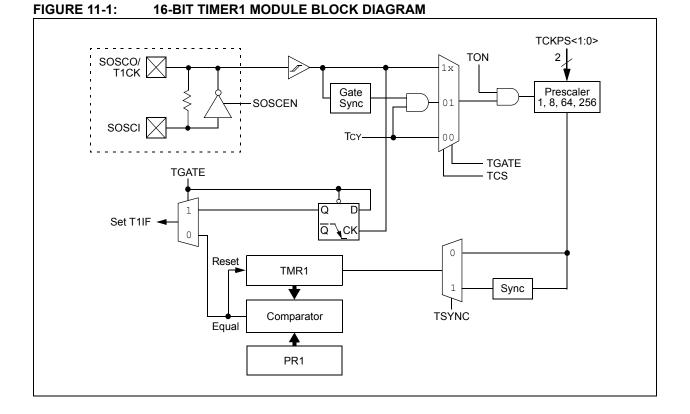

## 11.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site: (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 11-1 illustrates a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- Set or clear the TSYNC bit in the T1CON register to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

NOTES:

| R/W-0         | R/W-0        | R/W-0                               | U-0             | U-0                | U-0             | U-0              | U-0   |

|---------------|--------------|-------------------------------------|-----------------|--------------------|-----------------|------------------|-------|

| FRMEN         | SPIFSD       | FRMPOL                              | —               | —                  | _               | —                | —     |

| bit 15        |              |                                     |                 |                    |                 |                  | bit 8 |

|               |              |                                     |                 |                    |                 |                  |       |

| U-0           | U-0          | U-0                                 | U-0             | U-0                | U-0             | R/W-0            | U-0   |

|               | —            | _                                   | —               | —                  | —               | FRMDLY           | —     |

| bit 7         |              |                                     |                 |                    |                 |                  | bit 0 |

|               |              |                                     |                 |                    |                 |                  |       |

| Legend:       |              |                                     |                 |                    |                 |                  |       |

| R = Readable  | e bit        | W = Writable                        | bit             | U = Unimplen       | nented bit, rea | ad as '0'        |       |

| -n = Value at | POR          | '1' = Bit is set                    |                 | '0' = Bit is cle   | ared            | x = Bit is unkno | own   |

|               |              |                                     |                 |                    |                 |                  |       |

| bit 15        | FRMEN: Fran  | med SPIx Supp                       | ort bit         |                    |                 |                  |       |

|               |              |                                     |                 | oin used as fram   | ne sync pulse i | input/output)    |       |

|               |              | SPIx support dis                    |                 |                    |                 |                  |       |

| bit 14        |              | me Sync Pulse                       |                 | ntrol bit          |                 |                  |       |

|               |              | nc pulse input (<br>nc pulse output | · /             |                    |                 |                  |       |

| bit 13        | -            | ame Sync Pulse                      | . ,             |                    |                 |                  |       |

| bit 15        |              | nc pulse is acti                    | -               |                    |                 |                  |       |

|               |              | nc pulse is acti                    |                 |                    |                 |                  |       |

| bit 12-2      |              | Unimplemented: Read as '0'          |                 |                    |                 |                  |       |

| bit 1         | FRMDLY: Fra  | ame Sync Pulse                      | e Edge Selec    | t bit              |                 |                  |       |

|               |              | nc pulse coinci                     | •               |                    |                 |                  |       |

|               | 0 = Frame sy | nc pulse prece                      | des first bit c | lock               |                 |                  |       |

| bit 0         | Unimplemen   | ted: This bit m                     | ust not be se   | t to '1' by the us | ser application | I                |       |

|               |              |                                     |                 |                    |                 |                  |       |

# REGISTER 15-3: SPIxCON2: SPIx CONTROL REGISTER 2

# 17.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, UART receive inputs react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 17.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530331

#### 17.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

# 18.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Analog-to-Digital Section 16. Converter (ADC)" (DS70183) of the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices have up to 13 Analog-to-Digital Conversion (ADC) module input channels.

The AD12B bit (AD1CON1<10>) allows each of the ADC modules to be configured as either a 10-bit, 4-sample-and-hold ADC (default configuration) or a 12-bit, 1-sample-and-hold ADC.

Note: The ADC module must be disabled before the AD12B bit can be modified.

# 18.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 13 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- · Operation during CPU Sleep and Idle modes

- 16-word conversion result buffer

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported.

- There is only one sample and hold (S/H) amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs can be shared with other analog input pins.

The actual number of analog input pins and external voltage reference input configuration will depend on the specific device. Refer to the specific device data sheet for further details.

A block diagram of the ADC for the dsPIC33FJ16GP304 and dsPIC33FJ32GP204 devices is shown in Figure 18-1. A block diagram of the ADC for the dsPIC33FJ32GP202 device is shown in Figure 18-2.

### 18.2 ADC Initialization

To configure the ADC module:

- 1. Select port pins as analog inputs (AD1PCFGH<15:0> or AD1PCFGL<15:0>).

- 2. Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- Select the analog conversion clock to match desired data rate with processor clock (AD1CON3<7:0>).

- 4. Determine how many sample-and-hold channels will be used (AD1CON2<9:8> and AD1PCFGH<15:0> or AD1PCFGL<15:0>).

- 5. Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- 6. Select the way conversion results are presented in the buffer (AD1CON1<9:8>).

- c) Turn on the ADC module (AD1CON1<15>).

- 7. Configure ADC interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select ADC interrupt priority.

| TABL               | E 20-2:              | INSTRUCTION SET OVERVIEW (CONTINUED) |                                     |                                        |               |                |                          |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-------------------------------------|----------------------------------------|---------------|----------------|--------------------------|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax                     | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |

| 29                 | DIV                  | DIV.S                                | Wm,Wn                               | Signed 16/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |  |  |  |  |

|                    |                      | DIV.SD                               | Wm,Wn                               | Signed 32/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |  |  |  |  |

|                    |                      | DIV.U                                | Wm,Wn                               | Unsigned 16/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |  |  |  |  |

|                    |                      | DIV.UD                               | Wm,Wn                               | Unsigned 32/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |  |  |  |  |

| 30                 | DIVF                 | DIVF                                 | Wm,Wn                               | Signed 16/16-bit Fractional Divide     | 1             | 18             | N,Z,C,OV                 |  |  |  |  |

| 31                 | DO                   | DO                                   | #lit14,Expr                         | Do code to PC + Expr, lit14 + 1 times  | 2             | 2              | None                     |  |  |  |  |

|                    |                      | DO                                   | Wn,Expr                             | Do code to PC + Expr, (Wn) + 1 times   | 2             | 2              | None                     |  |  |  |  |

| 32                 | ED                   | ED                                   | Wm*Wm, Acc, Wx, Wy, Wxd             | Euclidean Distance (no accumulate)     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 33                 | EDAC                 | EDAC                                 | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance                     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 34                 | EXCH                 | EXCH                                 | Wns,Wnd                             | Swap Wns with Wnd                      | 1             | 1              | None                     |  |  |  |  |

| 35                 | FBCL                 | FBCL                                 | Ws,Wnd                              | Find Bit Change from Left (MSb) Side   | 1             | 1              | С                        |  |  |  |  |

| 36                 | FF1L                 | FF1L                                 | Ws,Wnd                              | Find First One from Left (MSb) Side    | 1             | 1              | С                        |  |  |  |  |

| 37                 | FF1R                 | FF1R                                 | Ws,Wnd                              | Find First One from Right (LSb) Side   | 1             | 1              | С                        |  |  |  |  |

| 38                 | GOTO                 | GOTO                                 | Expr                                | Go to address                          | 2             | 2              | None                     |  |  |  |  |

|                    |                      | GOTO                                 | Wn                                  | Go to indirect                         | 1             | 2              | None                     |  |  |  |  |

| 39                 | INC                  | INC                                  | f                                   | f = f + 1                              | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC                                  | f,WREG                              | WREG = f + 1                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC                                  | Ws,Wd                               | Wd = Ws + 1                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 40                 | INC2                 | INC2                                 | f                                   | f = f + 2                              | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC2                                 | f,WREG                              | WREG = f + 2                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

|                    |                      | INC2                                 | Ws,Wd                               | Wd = Ws + 2                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |

| 41                 | IOR                  | IOR                                  | f                                   | f = f.IOR. WREG                        | 1             | 1              | N,Z                      |  |  |  |  |

|                    | 1010                 | IOR                                  | f,WREG                              | WREG = f .IOR. WREG                    | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | #lit10,Wn                           | Wd = lit10 .IOR. Wd                    | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | Wb,Ws,Wd                            | Wd = Wb .IOR. Ws                       | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | IOR                                  | Wb,#lit5,Wd                         | Wd = Wb .IOR. lit5                     | 1             | 1              | N,Z                      |  |  |  |  |

| 42                 | LAC                  | LAC                                  | Wso,#Slit4,Acc                      | Load Accumulator                       | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 43                 | LNK                  | LNK                                  | #lit14                              | Link Frame Pointer                     | 1             | 1              | None                     |  |  |  |  |

| 44                 | LSR                  | LSR                                  | f                                   | f = Logical Right Shift f              | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | f,WREG                              | WREG = Logical Right Shift f           | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | Ws,Wd                               | Wd = Logical Right Shift Ws            | 1             | 1              | C,N,OV,Z                 |  |  |  |  |

|                    |                      | LSR                                  | Wb,Wns,Wnd                          | Wnd = Logical Right Shift Wb by Wns    | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | LSR                                  | Wb,#lit5,Wnd                        | Wnd = Logical Right Shift Wb by lit5   | 1             | 1              | N,Z                      |  |  |  |  |

| 45                 | MAC                  | MAC                                  | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Accumulate                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

|                    |                      | MAC                                  | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd        | Square and Accumulate                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |

| 46                 | MOV                  | MOV                                  | f,Wn                                | Move f to Wn                           | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | f                                   | Move f to f                            | 1             | 1              | N,Z                      |  |  |  |  |

|                    |                      | MOV                                  | f,WREG                              | Move f to WREG                         | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | #lit16,Wn                           | Move 16-bit literal to Wn              | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV.b                                | #lit8,Wn                            | Move 8-bit literal to Wn               | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | Wn,f                                | Move Wn to f                           | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | Wso,Wdo                             | Move Ws to Wd                          | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV                                  | WREG, f                             | Move WREG to f                         | 1             | 1              | None                     |  |  |  |  |

|                    |                      | MOV.D                                | Wns,Wd                              | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |  |  |  |  |

|                    |                      | MOV.D                                | Ws,Wnd                              | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |  |  |  |  |

| 47                 | MOVSAC               | MOVSAC                               | Acc, Wx, Wxd, Wy, Wyd, AWB          | Prefetch and store accumulator         | 1             | 1              | None                     |  |  |  |  |

|                    | -                    |                                      |                                     |                                        | 1             | 1              |                          |  |  |  |  |

# TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

# 22.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                    | 40°C to +125°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$      | 0.3V to +5.6V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> | 0.3V to 3.6V         |

| Maximum current out of Vss pin                                                    |                      |

| Maximum current into Vod pin <sup>(2)</sup>                                       | 250 mA               |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 8 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 15 mA                |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 25 mA                |

| Maximum current sunk by all ports                                                 | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA               |

| Note 1: | Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the                |

|---------|---------------------------------------------------------------------------------------------------------------|

|         | device. This is a stress rating only, and functional operation of the device at those or any other conditions |

|         | above those indicated in the operation listings of this specification is not implied. Exposure to maximum     |

|         | rating conditions for extended periods can affect device reliability.                                         |

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 22-2).

- **3:** Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: Refer to the "Pin Diagrams" section for 5V tolerant pins.

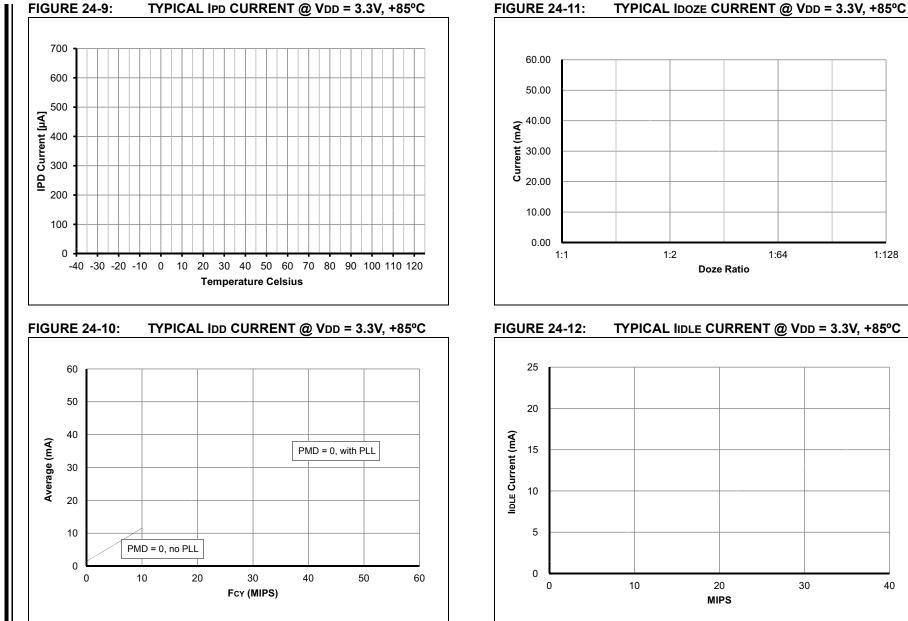

| DC CHARACTERISTICS              |                        |     | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |            |      |                                                |  |

|---------------------------------|------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------------------------------------------|--|

| Parameter<br>No. <sup>(5)</sup> | Typical <sup>(2)</sup> | Мах | Units                                                                                                                                                                                      | Conditions |      |                                                |  |

| Power-Down                      | Current (IPD)          | (1) |                                                                                                                                                                                            |            |      |                                                |  |

| DC60d                           | 55                     | 500 | μA                                                                                                                                                                                         | -40°C      |      |                                                |  |

| DC60a                           | 63                     | 300 | μA                                                                                                                                                                                         | +25°C      | 3.3V | Base Power-Down Current <sup>(3,4)</sup>       |  |

| DC60b                           | 85                     | 350 | μA                                                                                                                                                                                         | +85°C      |      |                                                |  |

| DC60c                           | 146                    | 600 | μA                                                                                                                                                                                         | +125°C     |      |                                                |  |

| DC61d                           | 8                      | 15  | μA                                                                                                                                                                                         | -40°C      |      |                                                |  |

| DC61a                           | 2                      | 3   | μA                                                                                                                                                                                         | +25°C      | 3.3V | Match dog Timor Currents (1997-(3.5)           |  |

| DC61b                           | 2                      | 2   | μA                                                                                                                                                                                         | +85°C      |      | Watchdog Timer Current: △IwDT <sup>(3,5)</sup> |  |

| DC61c                           | 3                      | 5   | μA                                                                                                                                                                                         | +125°C     | 1    |                                                |  |

Note 1: IPD (Sleep) current is measured as follows:

• CPU core is off, oscillator is configured in EC mode and external clock active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled, all peripheral modules are disabled (PMDx bits are all ones)

- VREGS bit (RCON<8>) = 0 (i.e., core regulator is set to stand-by while the device is in Sleep mode)

- RTCC is disabled.

- JTAG is disabled

- 2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The Watchdog Timer Current is the additional current consumed when the WDT module is enabled. This current should be added to the base IPD current.

- 4: These currents are measured on the device containing the most memory in this family.

- 5: These parameters are characterized, but are not tested in manufacturing.

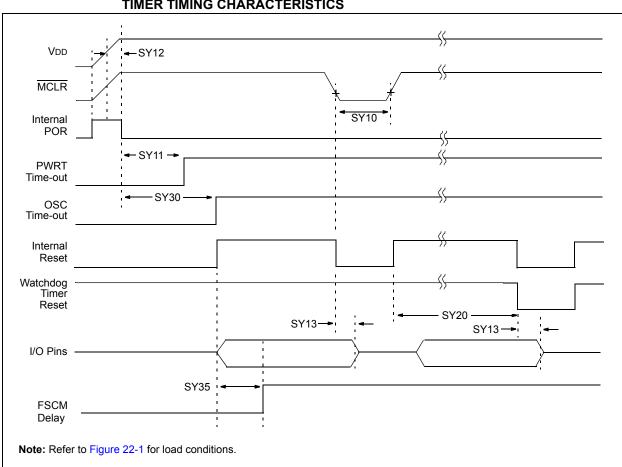

# FIGURE 22-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

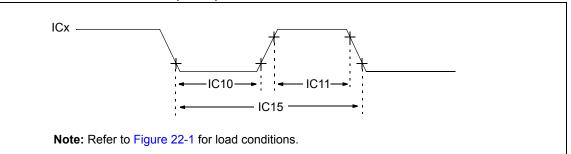

#### FIGURE 22-6: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 22-25: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS       |        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                |              |     |       |                                  |

|--------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|-----|-------|----------------------------------|

| Param<br>No.             | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                            |                | Min          | Мах | Units | Conditions                       |

| IC10                     | TccL   | ICx Input Low Time                                                                                                                                                                                       | No Prescaler   | 0.5 Tcy + 20 | _   | ns    | —                                |

|                          |        |                                                                                                                                                                                                          | With Prescaler | 10           | _   | ns    |                                  |

| IC11 TccH ICx Input High |        | ICx Input High Time                                                                                                                                                                                      | No Prescaler   | 0.5 TCY + 20 | _   | ns    | —                                |

|                          |        |                                                                                                                                                                                                          | With Prescaler | 10           |     | ns    |                                  |

| IC15                     | TccP   | ICx Input Period                                                                                                                                                                                         | •              | (Tcy + 40)/N | —   | ns    | N = prescale<br>value (1, 4, 16) |

Note 1: These parameters are characterized but not tested in manufacturing.

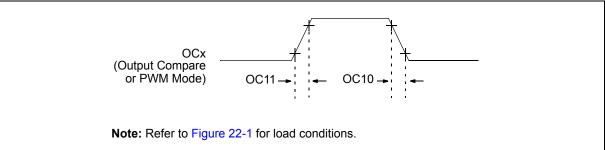

#### FIGURE 22-7: OUTPUT COMPARE MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 22-26: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |                         |     |                    |       |                    |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----|--------------------|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                            | Min                     | Тур | Мах                | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time                                                                                                                                                                                     | —                       | _   | —                  | ns    | See parameter D032 |

| OC11               | TccR   | OCx Output Rise Time                                                                                                                                                                                     | — — ns See parameter D0 |     | See parameter D031 |       |                    |

Note 1: These parameters are characterized but not tested in manufacturing.

1:128

40

| Section Name                                                       | Update Description                                                                                                                                                                               |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 14.0 "Serial Peripheral<br>Interface (SPI)"                | Removed the following sections, which are now available in the related section of the dsPIC33F/PIC24H Family Reference Manual:                                                                   |

|                                                                    | • 14.1 "Interrupts"                                                                                                                                                                              |

|                                                                    | 14.2 "Receive Operations"                                                                                                                                                                        |

|                                                                    | 14.3 "Transmit Operations"                                                                                                                                                                       |

|                                                                    | • 14.4 "SPI Setup" (retained Figure 14-1: SPI Module Block Diagram)                                                                                                                              |

| Section 15.0 "Inter-Integrated<br>Circuit (I <sup>2</sup> C™)"     | Removed the following sections, which are now available in the related section of the dsPIC33F/PIC24H Family Reference Manual:                                                                   |

|                                                                    | • 15.3 "I <sup>2</sup> C Interrupts"                                                                                                                                                             |

|                                                                    | • 15.4 "Baud Rate Generator" (retained Figure 15-1: I <sup>2</sup> C Block Diagram)                                                                                                              |

|                                                                    | <ul> <li>15.5 "I<sup>2</sup>C Module Addresses"</li> </ul>                                                                                                                                       |

|                                                                    | <ul> <li>15.6 "Slave Address Masking"</li> </ul>                                                                                                                                                 |

|                                                                    | 15.7 "IPMI Support"                                                                                                                                                                              |

|                                                                    | <ul> <li>15.8 "General Call Address Support"</li> </ul>                                                                                                                                          |

|                                                                    | <ul> <li>15.9 "Automatic Clock Stretch"</li> </ul>                                                                                                                                               |

|                                                                    | <ul> <li>15.10 "Software Controlled Clock Stretching (STREN = 1)"</li> </ul>                                                                                                                     |

|                                                                    | 15.11 "Slope Control"                                                                                                                                                                            |

|                                                                    | 15.12 "Clock Arbitration"                                                                                                                                                                        |

|                                                                    | • 15.13 "Multi-Master Communication, Bus Collision, and Bus Arbitration"                                                                                                                         |

|                                                                    | <ul> <li>15.14 "Peripheral Pin Select Limitations"</li> </ul>                                                                                                                                    |

| Section 16.0 "Universal<br>Asynchronous Receiver Transmitter       | Removed the following sections, which are now available in the related section of the dsPIC33F/PIC24H Family Reference Manual:                                                                   |

| (UART)"                                                            | <ul> <li>16.1 "UART Baud Rate Generator"</li> </ul>                                                                                                                                              |

|                                                                    | <ul> <li>16.2 "Transmitting in 8-bit Data Mode"</li> </ul>                                                                                                                                       |

|                                                                    | <ul> <li>16.3 "Transmitting in 9-bit Data Mode"</li> </ul>                                                                                                                                       |

|                                                                    | <ul> <li>16.4 "Break and Sync Transmit Sequence"</li> </ul>                                                                                                                                      |

|                                                                    | <ul> <li>16.5 "Receiving in 8-bit or 9-bit Data Mode"</li> </ul>                                                                                                                                 |

|                                                                    | <ul> <li>16.6 "Flow Control Using UxCTS and UxRTS Pins"</li> </ul>                                                                                                                               |

|                                                                    | 16.7 "Infrared Support"                                                                                                                                                                          |

|                                                                    | Removed IrDA references and Note 1, and updated the bit and bit value descriptions for UTXINV (UxSTA<14>) in the UARTx Status and Control Register (see Register 16-2).                          |

| Section 17.0 "10-bit/12-bit Analog-<br>to-Digital Converter (ADC)" | Removed Equation 17-1: ADC Conversion Clock Period and Figure 17-2: ADC Transfer Function (10-Bit Example).                                                                                      |

|                                                                    | Added ADC1 Module Block Diagram for dsPIC33FJ16GP304 and dsPIC33FJ32GP204 Devices (Figure 18-1) and ADC1 Module Block Diagram FOR dsPIC33FJ32GP202 Devices (Figure 17-2).                        |

|                                                                    | Added Note 2 to Figure 17-3: ADC Conversion Clock Period Block Diagram.                                                                                                                          |

|                                                                    | Added device-specific information to Note 1 in the ADC1 Input Scan Select Register Low (see Register 17-6), and updated the default bit value for bits 12-10 (CSS12-CSS10) from U-0 to R/W-0.    |

|                                                                    | Added device-specific information to Note 1 in the ADC1 Port Configuration Register Low (see Register 17-7), and updated the default bit value for bits 12-10 (PCFG12-PCFG10) from U-0 to R/W-0. |

#### TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Registers                                          | 163     |

|----------------------------------------------------|---------|

| I <sup>2</sup> C Module                            |         |

| I2C1 Register Map                                  |         |

| In-Circuit Debugger                                |         |

| In-Circuit Emulation                               |         |

| In-Circuit Serial Programming (ICSP)               | 39, 196 |

| Input Capture                                      |         |

| Registers                                          |         |

| Input Change Notification                          |         |

| Instruction Addressing Modes                       |         |

| File Register Instructions                         |         |

| Fundamental Modes Supported                        |         |

| MAC Instructions                                   |         |

| MCU Instructions                                   |         |

| Move and Accumulator Instructions                  |         |

| Other Instructions                                 | 46      |

| Instruction Set                                    |         |

| Overview                                           |         |

| Summary                                            |         |

| Instruction-Based Power-Saving Modes               |         |

| Idle                                               |         |

| Sleep                                              | 109     |

| Internal RC Oscillator                             |         |

| Use with WDT                                       |         |

| Internet Address                                   |         |

| Interrupt Control and Status Registers             | 74      |

| IECx                                               |         |

| IFSx                                               | 74      |

| INTCON1                                            | 74      |

| INTCON2                                            | 74      |

| IPCx                                               |         |

| Interrupt Setup Procedures                         | 96      |

| Initialization                                     | 96      |