Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp204-h-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

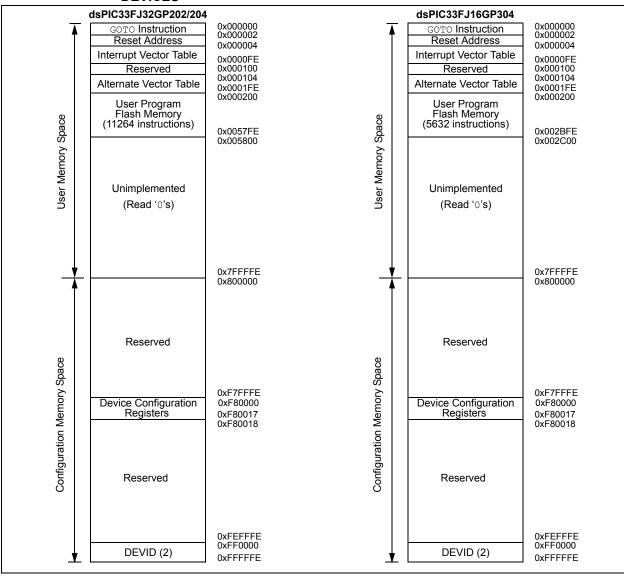

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features the dsPIC33FJ32GP202/204 of and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Memory" Section 4. "Program (DS70202) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory maps for the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices are shown in Figure 4-1.

# FIGURE 4-1: PROGRAM MEMORY FOR dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 DEVICES

## TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP

| SFR<br>NameSFR<br>AddrBit 15Bit 14Bit 13Bit 12Bit 11Bit 10Bit 9Bit 8Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0All ResetsINTCON10080NSTDISOVAERROVBERCOVAERRCOVAERROVBEROVATEOVBTECOVTESTACERRDIVOERR-MATHERRADDRERRSTACERRSSCFAIL-0000INTCON20082ALTIVTDISI0000IFS00086AD11FU1TXIFU1RXIFSPI1EFT31FT21FOC21FIC21F-T11FOC11FIC11FINTOFP0000IFS40086AD11FU1TXIFU1RXIFSPI1EFT31FT21FOC21FIC21F-MI2C11FSI21F0000IFS40086AD11FU1TXIFSPI1EFSPI1EFT31ET21FOC21FIC21F-MI2C11FSI2C1F0000IFS40086AD11FU1TXIFSPI1EFSPI1EFT31ET21EOC21FIC21F-MI2C11FSI2C1F0000IEC40096INT21E-AD11EU1TXIFSPI1EFSPI1EFT31ET21EOC21EIC71E-INT1ECNIE-MI2C11FSI2C1F0000IEC40096 <td< th=""><th></th><th></th><th></th><th></th><th>-</th><th>-</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></td<> |         |      |        |        | -          | -        |         |        |            |       |          |         |             |         |           |        |            |         |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------|--------|------------|----------|---------|--------|------------|-------|----------|---------|-------------|---------|-----------|--------|------------|---------|---------------|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -       |      | Bit 15 | Bit 14 | Bit 13     | Bit 12   | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3     | Bit 2  | Bit 1      | Bit 0   | All<br>Resets |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INTCON1 | 0080 | NSTDIS | OVAERR | OVBERR     | COVAERR  | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | _           | MATHERR | ADDRERR   | STKERR | OSCFAIL    | —       | 0000          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | INTCON2 | 0082 | ALTIVT | DISI   | —          | —        | —       | —      | —          | —     | —        | —       | —           | —       | —         | INT2EP | INT1EP     | INT0EP  | 0000          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IFS0    | 0084 | —      | —      | AD1IF      | U1TXIF   | U1RXIF  | SPI1IF | SPI1EIF    | T3IF  | T2IF     | OC2IF   | IC2IF       | —       | T1IF      | OC1IF  | IC1IF      | INTOIF  | 0000          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IFS1    | 0086 | —      | —      | INT2IF     | —        | —       | —      | —          | —     | IC8IF    | IC7IF   | _           | INT1IF  | CNIF      | —      | MI2C1IF    | SI2C1IF | 0000          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IFS4    | 008C | —      | —      | —          | _        | —       | —      | —          | —     | -        | —       | —           | —       | —         | —      | U1EIF      | _       | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEC0    | 0094 | —      | —      | AD1IE      | U1TXIE   | U1RXIE  | SPI1IE | SPI1EIE    | T3IE  | T2IE     | OC2IE   | IC2IE       | —       | T1IE      | OC1IE  | IC1IE      | INT0IE  | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEC1    | 0096 | —      | —      | INT2IE     | _        | —       | —      | —          | —     | IC8IE    | IC7IE   | —           | INT1IE  | CNIE      | —      | MI2C1IE    | SI2C1IE | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IEC4    | 009C | —      | —      | —          | _        | —       | —      | —          | —     | -        | —       | —           | —       | —         | —      | U1EIE      | _       | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC0    | 00A4 | —      |        | T1IP<2:0>  |          | —       | (      | OC1IP<2:0  | )>    | —        |         | IC1IP<2:0>  |         | —         | 11     | VT0IP<2:0> | •       | 4444          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IPC1    | 00A6 | —      |        | T2IP<2:0>  |          | —       | (      | OC2IP<2:0  | )>    | _        |         | IC2IP<2:0>  |         | —         | —      | —          | _       | 4440          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IPC2    | 00A8 | _      | ι      | J1RXIP<2:0 | )>       | _       | 0,     | SPI1IP<2:0 | )>    | _        |         | SPI1EIP<2:0 | >       | _         |        | T3IP<2:0>  |         | 4444          |

| IPC5       00AE       -       IC8IP<2:0>       -       IC7IP<2:0>       -       -       -       -       -       -       4404         IPC7       00B2       -       -       -       -       -       -       -       -       -       4004         IPC7       00B2       -       -       -       -       -       -       -       -       0040         IPC16       00C4       -       -       -       -       -       -       -       0040                                                                                                                                                                                                                                                                                                                                                                                                     | IPC3    | 00AA | —      | —      | —          | _        | —       | —      | —          | —     | —        |         | AD1IP<2:0>  | >       | —         | U      | 1TXIP<2:0  | >       | 0044          |

| IPC7       00B2       -       -       -       -       -       -       INT2IP<2:0>       -       -       -       0040         IPC16       00C4       -       -       -       -       -       -       -       0040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IPC4    | 00AC | —      |        | CNIP<2:0>  | •        | —       | —      | —          | —     | -        | I       | MI2C1IP<2:0 | )>      | —         | SI     | 2C1IP<2:0  | >       | 4044          |

| IPC16       00C4       -       -       -       -       -       U1EIP<2:0>       -       -       -       0040                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IPC5    | 00AE | —      |        | IC8IP<2:0> | <b>`</b> | —       |        | IC7IP<2:0  | >     | _        | —       | —           | —       | —         | 11     | VT1IP<2:0> | •       | 4404          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IPC7    | 00B2 | _      | _      | _          | _        | _       | _      | _          | _     | _        |         | INT2IP<2:02 | >       | _         | _      | _          | _       | 0040          |

| INTTREG 00E0 ILR<3:0> - VECNUM<6:0> 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IPC16   | 00C4 | —      | —      | —          | —        | —       | —      | —          | _     | —        |         | U1EIP<2:0>  | >       | —         | —      | —          |         | 0040          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INTTREG | 00E0 | —      | —      | —          | —        |         | ILR<   | 3:0>       |       | —        |         |             | VE      | CNUM<6:0> |        |            |         | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 8-2:** CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup> (CONTINUED)

00000 = Input/2 (default)

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register is reset only on a Power-on Reset (POR).

## 9.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | the product page using the link above,  |  |  |  |  |  |  |  |  |  |

|       | enter this URL in your browser:         |  |  |  |  |  |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/   |  |  |  |  |  |  |  |  |  |

|       | Devices.aspx?dDocName=en530331          |  |  |  |  |  |  |  |  |  |

### 9.5.1 KEY RESOURCES

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0              | U-0                             | R/W-0                | U-0                                                     | U-0                           | U-0             | U-0                | U-0   |

|--------------------|---------------------------------|----------------------|---------------------------------------------------------|-------------------------------|-----------------|--------------------|-------|

| TON <sup>(2)</sup> |                                 | TSIDL <sup>(1)</sup> | —                                                       |                               |                 | _                  | —     |

| bit 15             |                                 |                      |                                                         |                               |                 |                    | bit 8 |

|                    |                                 |                      |                                                         |                               |                 |                    |       |

| U-0                | R/W-0                           | R/W-0                | R/W-0                                                   | U-0                           | U-0             | R/W-0              | U-0   |

|                    | TGATE <sup>(2)</sup>            | TCKPS<               | <1:0> <sup>(2)</sup>                                    |                               | —               | TCS <sup>(2)</sup> | _     |

| bit 7              |                                 |                      |                                                         |                               |                 |                    | bit C |

| Legend:            |                                 |                      |                                                         |                               |                 |                    |       |

| R = Readabl        | e bit                           | W = Writable I       | oit                                                     | U = Unimpler                  | mented bit, rea | d as '0'           |       |

| -n = Value at      | POR                             | '1' = Bit is set     |                                                         | '0' = Bit is cle              | ared            | x = Bit is unkne   | own   |

|                    |                                 |                      |                                                         |                               |                 |                    |       |

| bit 15             | TON: Timer3                     |                      |                                                         |                               |                 |                    |       |

|                    | 1 = Starts 16-<br>0 = Stops 16- |                      |                                                         |                               |                 |                    |       |

| bit 14             | •                               | ted: Read as '0      | ,                                                       |                               |                 |                    |       |

| bit 13             | -                               | n Idle Mode bit      |                                                         |                               |                 |                    |       |

| bit 10             |                                 | ue timer operati     |                                                         | rice enters Idle              | mode            |                    |       |

|                    |                                 | timer operation      |                                                         |                               |                 |                    |       |

| bit 12-7           | Unimplemen                      | ted: Read as '0      | )'                                                      |                               |                 |                    |       |

| bit 6              | TGATE: Time                     | er3 Gated Time       | Accumulation                                            | n Enable bit <sup>(2)</sup>   |                 |                    |       |

|                    | When TCS =                      |                      |                                                         |                               |                 |                    |       |

|                    | This bit is igno<br>When TCS =  |                      |                                                         |                               |                 |                    |       |

|                    |                                 | e accumulation       | enabled                                                 |                               |                 |                    |       |

|                    |                                 | e accumulation       |                                                         |                               |                 |                    |       |

| bit 5-4            | TCKPS<1:0>                      | : Timer3 Input (     | Clock Presca                                            | le Select bits <sup>(2)</sup> |                 |                    |       |

|                    | 11 = 1:256 pr                   |                      |                                                         |                               |                 |                    |       |

|                    | 10 = 1:64 pre<br>01 = 1:8 pres  |                      |                                                         |                               |                 |                    |       |

|                    | 00 = 1:1 pres                   |                      |                                                         |                               |                 |                    |       |

| bit 3-2            | •                               | ted: Read as '0      | )'                                                      |                               |                 |                    |       |

| bit 1              | TCS: Timer3                     | Clock Source S       | elect bit <sup>(2)</sup>                                |                               |                 |                    |       |

|                    | 1 = External c                  | clock from T3Cl      | <pin< td=""><td></td><td></td><td></td><td></td></pin<> |                               |                 |                    |       |

|                    | 0 = Internal cl                 | lock (Fosc/2)        |                                                         |                               |                 |                    |       |

|                    | Unimplemen                      |                      |                                                         |                               |                 |                    |       |

## REGISTER 12-2: T3CON CONTROL REGISTER

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), these bits have no effect.

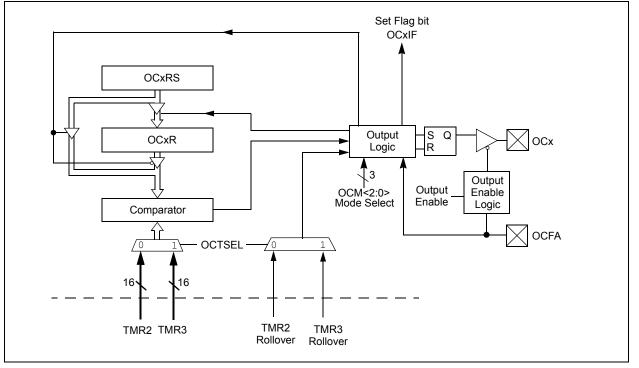

# 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without fault protection

- · PWM mode with fault protection

## FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

## 15.1 SPI Helpful Tips

- 1. In Frame mode, if there is a possibility that the master may not be initialized before the slave:

- a) If FRMPOL (SPIxCON2<13>) = 1, use a pull-down resistor on SSx.

- b) If FRMPOL = 0, use a pull-up resistor on  $\frac{1}{SSx}$ .

| Note: | This   | insures   | that  | the        | first | fr | ame |

|-------|--------|-----------|-------|------------|-------|----|-----|

|       | transr | nission a | after | initializa | ation | is | not |

|       | shifte |           |       |            |       |    |     |

- 2. In non-framed 3-wire mode, (i.e., not using SSx from a master):

- a) If CKP (SPIxCON1<6>) = 1, always place a pull-up resistor on SSx.

- b) If CKP = 0, always place a pull-down resistor on SSx.

- Note: This will insure that during power-up and initialization the master/slave will not lose sync due to an errant SCK transition that would cause the slave to accumulate data shift errors for both transmit and receive appearing as corrupted data.

- FRMEN (SPIxCON2<15>) = 1 and SSEN (SPIxCON1<7>) = 1 are exclusive and invalid. In Frame mode, SCKx is continuous and the Frame sync pulse is active on the SSx pin, which indicates the start of a data frame.

- Note: Not all third-party devices support Frame mode timing. Refer to the SPI electrical characteristics for details.

- In Master mode only, set the SMP bit (SPIxCON1<9>) to a '1' for the fastest SPI data rate possible. The SMP bit can only be set at the same time or after the MSTEN bit (SPIxCON1<5>) is set.

- 5. To avoid invalid slave read data to the master, the user's master software must guarantee enough time for slave software to fill its write buffer before the user application initiates a master write/read cycle. It is always advisable to preload the SPIxBUF transmit register in advance of the next master transaction cycle. SPIxBUF is transferred to the SPI shift register and is empty once the data transmission begins.

## 15.2 SPI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http:// www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en530331

### 15.2.1 KEY RESOURCES

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

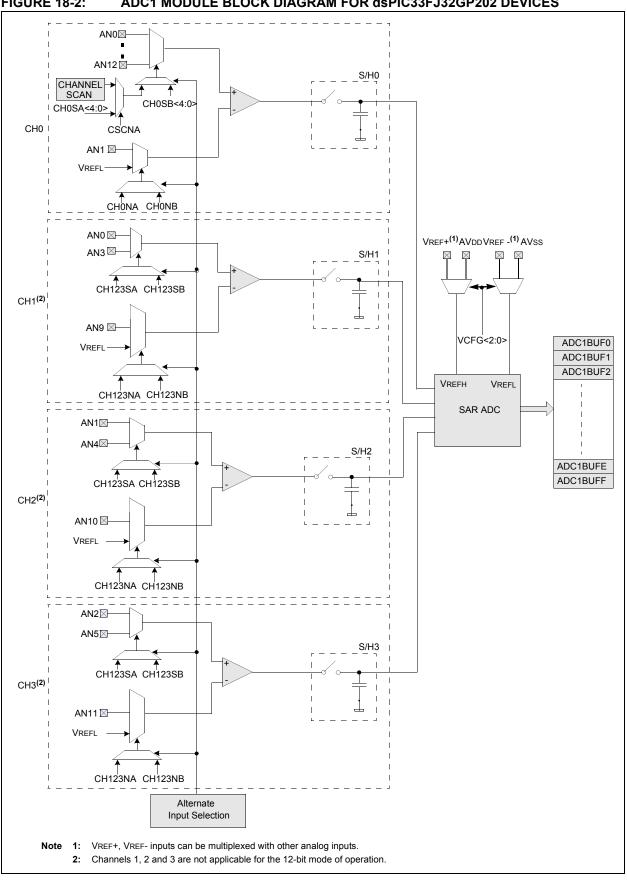

**FIGURE 18-2:** ADC1 MODULE BLOCK DIAGRAM FOR dsPIC33FJ32GP202 DEVICES

| ABLE 20-2:         |                      | INSTR  | NSTRUCTION SET OVERVIEW (CONTINUED) |                                        |               |                |                          |  |  |  |  |  |  |

|--------------------|----------------------|--------|-------------------------------------|----------------------------------------|---------------|----------------|--------------------------|--|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax                     | Description                            | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |  |  |  |  |  |  |

| 29                 | DIV                  | DIV.S  | Wm,Wn                               | Signed 16/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |  |

|                    |                      | DIV.SD | Wm,Wn                               | Signed 32/16-bit Integer Divide        | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |  |

|                    |                      | DIV.U  | Wm,Wn                               | Unsigned 16/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |  |

|                    |                      | DIV.UD | Wm,Wn                               | Unsigned 32/16-bit Integer Divide      | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |  |

| 30                 | DIVF                 | DIVF   | Wm,Wn                               | Signed 16/16-bit Fractional Divide     | 1             | 18             | N,Z,C,OV                 |  |  |  |  |  |  |

| 31                 | DO                   | DO     | #lit14,Expr                         | Do code to PC + Expr, lit14 + 1 times  | 2             | 2              | None                     |  |  |  |  |  |  |

|                    |                      | DO     | Wn,Expr                             | Do code to PC + Expr, (Wn) + 1 times   | 2             | 2              | None                     |  |  |  |  |  |  |

| 32                 | ED                   | ED     | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance (no accumulate)     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |  |

| 33                 | EDAC                 | EDAC   | Wm*Wm,Acc,Wx,Wy,Wxd                 | Euclidean Distance                     | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |  |

| 34                 | EXCH                 | EXCH   | Wns,Wnd                             | Swap Wns with Wnd                      | 1             | 1              | None                     |  |  |  |  |  |  |

| 35                 | FBCL                 | FBCL   | Ws,Wnd                              | Find Bit Change from Left (MSb) Side   | 1             | 1              | С                        |  |  |  |  |  |  |

| 36                 | FF1L                 | FF1L   | Ws,Wnd                              | Find First One from Left (MSb) Side    | 1             | 1              | С                        |  |  |  |  |  |  |

| 37                 | FF1R                 | FF1R   | Ws,Wnd                              | Find First One from Right (LSb) Side   | 1             | 1              | С                        |  |  |  |  |  |  |

| 38                 | GOTO                 | GOTO   | Expr                                | Go to address                          | 2             | 2              | None                     |  |  |  |  |  |  |

|                    |                      | GOTO   | Wn                                  | Go to indirect                         | 1             | 2              | None                     |  |  |  |  |  |  |

| 39                 | INC                  | INC    | f                                   | f = f + 1                              | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |  |

|                    |                      | INC    | f,WREG                              | WREG = f + 1                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |  |

|                    |                      | INC    | Ws,Wd                               | Wd = Ws + 1                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |  |

| 40                 | INC2                 | INC2   | f                                   | f = f + 2                              | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |  |

|                    |                      | INC2   | f,WREG                              | WREG = f + 2                           | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |  |

|                    |                      | INC2   | Ws,Wd                               | Wd = Ws + 2                            | 1             | 1              | C,DC,N,OV,Z              |  |  |  |  |  |  |

| 41                 | IOR                  | IOR    | f                                   | f = f.IOR. WREG                        | 1             | 1              | N,Z                      |  |  |  |  |  |  |

|                    | 1010                 | IOR    | f,WREG                              | WREG = f .IOR. WREG                    | 1             | 1              | N,Z                      |  |  |  |  |  |  |

|                    |                      | IOR    | #lit10,Wn                           | Wd = lit10 .IOR. Wd                    | 1             | 1              | N,Z                      |  |  |  |  |  |  |

|                    |                      | IOR    | Wb,Ws,Wd                            | Wd = Wb .IOR. Ws                       | 1             | 1              | N,Z                      |  |  |  |  |  |  |

|                    |                      | IOR    | Wb,#lit5,Wd                         | Wd = Wb .IOR. lit5                     | 1             | 1              | N,Z                      |  |  |  |  |  |  |

| 42                 | LAC                  | LAC    | Wso,#Slit4,Acc                      | Load Accumulator                       | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |  |

| 43                 | LNK                  | LNK    | #lit14                              | Link Frame Pointer                     | 1             | 1              | None                     |  |  |  |  |  |  |

| 44                 | LSR                  | LSR    | f                                   | f = Logical Right Shift f              | 1             | 1              | C,N,OV,Z                 |  |  |  |  |  |  |

|                    |                      | LSR    | f,WREG                              | WREG = Logical Right Shift f           | 1             | 1              | C,N,OV,Z                 |  |  |  |  |  |  |

|                    |                      | LSR    | Ws,Wd                               | Wd = Logical Right Shift Ws            | 1             | 1              | C,N,OV,Z                 |  |  |  |  |  |  |

|                    |                      | LSR    | Wb,Wns,Wnd                          | Wnd = Logical Right Shift Wb by Wns    | 1             | 1              | N,Z                      |  |  |  |  |  |  |

|                    |                      | LSR    | Wb,#lit5,Wnd                        | Wnd = Logical Right Shift Wb by lit5   | 1             | 1              | N,Z                      |  |  |  |  |  |  |

| 45                 | MAC                  | MAC    | Wm*Wn,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Accumulate                | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |  |

|                    |                      | MAC    | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd        | Square and Accumulate                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |  |  |  |  |  |  |

| 46                 | MOV                  | MOV    | f,Wn                                | Move f to Wn                           | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV    | f                                   | Move f to f                            | 1             | 1              | N,Z                      |  |  |  |  |  |  |

|                    |                      | MOV    | f,WREG                              | Move f to WREG                         | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV    | #lit16,Wn                           | Move 16-bit literal to Wn              | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV.b  | #lit8,Wn                            | Move 8-bit literal to Wn               | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV    | Wn,f                                | Move Wn to f                           | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV    | Wso,Wdo                             | Move Ws to Wd                          | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV    | WREG, f                             | Move WREG to f                         | 1             | 1              | None                     |  |  |  |  |  |  |

|                    |                      | MOV.D  | Wns,Wd                              | Move Double from W(ns):W(ns + 1) to Wd | 1             | 2              | None                     |  |  |  |  |  |  |

|                    |                      | MOV.D  | Ws,Wnd                              | Move Double from Ws to W(nd + 1):W(nd) | 1             | 2              | None                     |  |  |  |  |  |  |

| 47                 | MOVSAC               | MOVSAC | Acc, Wx, Wxd, Wy, Wyd, AWB          | Prefetch and store accumulator         | 1             | 1              | None                     |  |  |  |  |  |  |

|                    | -                    |        |                                     |                                        | 1             | 1              |                          |  |  |  |  |  |  |

## TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |                   | Assembly Syntax              | Description                                                                                   | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------------------|------------------------------|-----------------------------------------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Ac   | cc,Wx,Wxd,Wy,Wyd             | Multiply Wm by Wn to Accumulator                                                              | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,Ad   | cc,Wx,Wxd,Wy,Wyd             | Square Wm to Accumulator                                                                      | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,Ad | cc,Wx,Wxd,Wy,Wyd             | -(Multiply Wm by Wn) to Accumulator                                                           | 1             | 1              | None                     |

| 50                 | MSC                  | MSC               | Wm*Wm, Acc, Wx, Wxd, Wy, Wyd | Multiply and Subtract from Accumulator                                                        | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 51                 |                      | NUT 00            | AWB                          | (A/ad + 1)(A/ad) = aignod(A/b) * aignod(A/a)                                                  | 4             | 1              | Nono                     |

| 51                 | MUL                  | MUL.SS            | Wb,Ws,Wnd                    | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)                                                      | 1             | 1              | None                     |

|                    |                      | MUL.SU            | Wb,Ws,Wnd                    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)                                                    | 1             | 1              | None<br>None             |

|                    |                      | MUL.US<br>MUL.UU  | Wb,Ws,Wnd<br>Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)<br>{Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws) | 1             | 1              | None                     |

|                    |                      | MUL.SU            | Wb,#lit5,Wnd                 | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)                                                  | 1             | 1              | None                     |

|                    |                      | MUL.UU            | Wb,#lit5,Wnd                 | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5)                                             | 1             | 1              | None                     |

|                    |                      | MUL               | f                            | W3:W2 = f * WREG                                                                              | 1             | 1              | None                     |

| 52                 | NEG                  | NEG               | Acc                          | Negate Accumulator                                                                            | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | NEG               | f                            | $f = \overline{f} + 1$                                                                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG               | f,WREG                       | WREG = $\overline{f}$ + 1                                                                     | 1             | 1              | C,DC,N,OV,2              |

|                    |                      | NEG               | Ws,Wd                        | $Wd = \overline{Ws} + 1$                                                                      | 1             | 1              | C,DC,N,OV,2              |

| 53                 | NOP                  | NOP               |                              | No Operation                                                                                  | 1             | 1              | None                     |

|                    |                      | NOPR              |                              | No Operation                                                                                  | 1             | 1              | None                     |

| 54                 | POP                  | POP               | f                            | Pop f from Top-of-Stack (TOS)                                                                 | 1             | 1              | None                     |

|                    |                      | POP               | Wdo                          | Pop from Top-of-Stack (TOS) to Wdo                                                            | 1             | 1              | None                     |

|                    |                      | POP.D             | Wnd                          | Pop from Top-of-Stack (TOS) to<br>W(nd):W(nd + 1)                                             | 1             | 2              | None                     |

|                    |                      | POP.S             |                              | Pop Shadow Registers                                                                          | 1             | 1              | All                      |

| 55                 | PUSH                 | PUSH              | f                            | Push f to Top-of-Stack (TOS)                                                                  | 1             | 1              | None                     |

|                    |                      | PUSH              | Wso                          | Push Wso to Top-of-Stack (TOS)                                                                | 1             | 1              | None                     |

|                    |                      | PUSH.D            | Wns                          | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)                                                    | 1             | 2              | None                     |

|                    |                      | PUSH.S            |                              | Push Shadow Registers                                                                         | 1             | 1              | None                     |

| 56                 | PWRSAV               | PWRSAV            | #lit1                        | Go into Sleep or Idle mode                                                                    | 1             | 1              | WDTO,Sleep               |

| 57                 | RCALL                | RCALL             | Expr                         | Relative Call                                                                                 | 1             | 2              | None                     |

|                    |                      | RCALL             | Wn                           | Computed Call                                                                                 | 1             | 2              | None                     |

| 58                 | REPEAT               | REPEAT            | #lit14                       | Repeat Next Instruction lit14 + 1 times                                                       | 1             | 1              | None                     |

|                    |                      | REPEAT            | Wn                           | Repeat Next Instruction (Wn) + 1 times                                                        | 1             | 1              | None                     |

| 59                 | RESET                | RESET             |                              | Software device Reset                                                                         | 1             | 1              | None                     |

| 60                 | RETFIE               | RETFIE            |                              | Return from interrupt                                                                         | 1             | 3 (2)          | None                     |

| 61                 | RETLW                | RETLW             | #lit10,Wn                    | Return with literal in Wn                                                                     | 1             | 3 (2)          | None                     |

| 62                 | RETURN               | RETURN            |                              | Return from Subroutine                                                                        | 1             | 3 (2)          | None                     |

| 63                 | RLC                  | RLC               | f                            | f = Rotate Left through Carry f                                                               | 1             | 1              | C,N,Z                    |

|                    |                      | RLC               | f,WREG                       | WREG = Rotate Left through Carry f                                                            | 1             | 1              | C,N,Z                    |

| 64                 | DING                 | RLC               | Ws,Wd                        | Wd = Rotate Left through Carry Ws                                                             | 1             | 1              | C,N,Z                    |

| 64                 | RLNC                 | RLNC              | f<br>f WDDC                  | f = Rotate Left (No Carry) f                                                                  | 1             | 1              | N,Z                      |

|                    |                      | RLNC              | f,WREG                       | WREG = Rotate Left (No Carry) f                                                               | 1             | 1              | N,Z                      |

| 65                 | DDC                  | RLNC              | Ws,Wd                        | Wd = Rotate Left (No Carry) Ws                                                                | 1             | 1              | N,Z                      |

| 65                 | RRC                  | RRC               | f<br>f WDEC                  | f = Rotate Right through Carry f                                                              | 1             | 1              | C,N,Z                    |

|                    |                      | RRC               | f,WREG<br>Ws,Wd              | WREG = Rotate Right through Carry f<br>Wd = Rotate Right through Carry Ws                     | 1             | 1              | C,N,Z<br>C,N,Z           |

### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

# 21.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit™ 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 21.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- · Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

| IADLE             | 22-4. 1  | JC TEIVIPERATURE AND VOL                                            | TAGE SP                                                                                                                                                                                    |                    |     |       |                         |  |  |  |  |

|-------------------|----------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------------------|--|--|--|--|

| DC СН4            | ARACTER  | ISTICS                                                              | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                         |  |  |  |  |

| Param<br>No.      | Symbol   | Characteristic                                                      | Min                                                                                                                                                                                        | Typ <sup>(1)</sup> | Max | Units | Conditions              |  |  |  |  |

| Operating Voltage |          |                                                                     |                                                                                                                                                                                            |                    |     |       |                         |  |  |  |  |

| DC10              | Supply V | /oltage                                                             |                                                                                                                                                                                            |                    |     |       |                         |  |  |  |  |

|                   | Vdd      |                                                                     | 3.0                                                                                                                                                                                        |                    | 3.6 | V     | Industrial and Extended |  |  |  |  |

| DC12              | Vdr      | RAM Data Retention Voltage <sup>(2)</sup>                           | 1.8                                                                                                                                                                                        |                    | —   | V     | _                       |  |  |  |  |

| DC16              | VPOR     | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _                                                                                                                                                                                          | _                  | Vss | V     | _                       |  |  |  |  |

| DC17              | SVDD     | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.03                                                                                                                                                                                       | _                  | —   | V/ms  | 0-3.0V in 0.1s          |  |  |  |  |

## TABLE 22-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

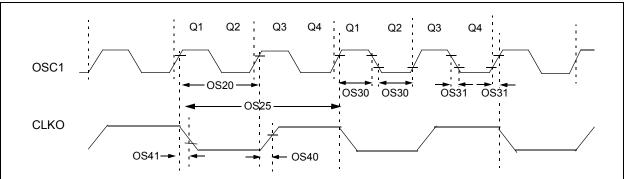

## TABLE 22-16: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHA       | RACTERI       | STICS                                                                                             | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |                |                   |                          |  |  |  |

|--------------|---------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|--|--|

| Param<br>No. | Symbol        | Characteristic                                                                                    | Min                                                                                                                                                                                      | Тур <sup>(1)</sup> | Мах            | Units             | Conditions               |  |  |  |

| OS10         | FIN           | External CLKI Frequency <sup>(4)</sup><br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                                                                                                                                                       | _                  | 40             | MHz               | EC                       |  |  |  |

|              |               | Oscillator Crystal Frequency <sup>(5)</sup>                                                       | 3.5<br>10                                                                                                                                                                                |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC         |  |  |  |

| OS20         | Tosc          | Tosc = 1/Fosc <sup>(4)</sup>                                                                      | 12.5                                                                                                                                                                                     | _                  | DC             | ns                | —                        |  |  |  |

| OS25         | TCY           | Instruction Cycle Time <sup>(2,4)</sup>                                                           | 25                                                                                                                                                                                       |                    | DC             | ns                | _                        |  |  |  |

| OS30         | TosL,<br>TosH | External Clock in (OSC1) <sup>(5)</sup><br>High or Low Time                                       | 0.375 x Tosc                                                                                                                                                                             | —                  | 0.625 x Tosc   | ns                | EC                       |  |  |  |

| OS31         | TosR,<br>TosF | External Clock in (OSC1) <sup>(5)</sup><br>Rise or Fall Time                                      | —                                                                                                                                                                                        | _                  | 20             | ns                | EC                       |  |  |  |

| OS40         | TckR          | CLKO Rise Time <sup>(3,5)</sup>                                                                   | _                                                                                                                                                                                        | 5.2                |                | ns                | _                        |  |  |  |

| OS41         | TckF          | CLKO Fall Time <sup>(3,5)</sup>                                                                   | _                                                                                                                                                                                        | 5.2                | —              | ns                | —                        |  |  |  |

| OS42         | Gм            | External Oscillator<br>Transconductance <sup>(6)</sup>                                            | 14                                                                                                                                                                                       | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |  |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

- 2: Instruction cycle period (TCY) equals two times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits can result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

- 3: Measurements are taken in EC mode. The CLKO signal is measured on the OSC2 pin.

- 4: These parameters are characterized by similarity, but are tested in manufacturing at FIN = 40 MHz only.

- 5: These parameters are characterized by similarity, but are not tested in manufacturing.

- 6: Data for this parameter is preliminary. This parameter is characterized, but is not tested in manufacturing.

## 23.1 High Temperature DC Characteristics

## TABLE 23-1: OPERATING MIPS VS. VOLTAGE

|                | VDD Range                   | Temperature Range | Max MIPS                                     |

|----------------|-----------------------------|-------------------|----------------------------------------------|

| Characteristic | (in Volts)                  | (in °C)           | dsPIC33FJ32GP202/204 and<br>dsPIC33FJ16GP304 |

| HDC5           | VBOR to 3.6V <sup>(1)</sup> | -40°C to +150°C   | 20                                           |

**Note 1:** Device is functional at VBORMIN < VDD < VDDMIN. Analog modules such as the ADC will have degraded performance. Device functionality is tested but not characterized. Refer to parameter BO10 in Table 22-11 for the minimum and maximum BOR values.

## TABLE 23-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                 | Symbol | Min           | Тур         | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-------------|------|------|

| High Temperature Devices                                                                                                                                                               |        |               |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                   | TJ     | -40           | _           | +155 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                    | TA     | -40           | _           | +150 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | I             | Pint + Pi/c | )    | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                      | Pdmax  | (Tj - Ta)/θja |             |      | W    |

## TABLE 23-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARA                                                                            | CTERISTIC | S              | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+150°C for High Temperature |     |     |       |                 |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------|----------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-----------------|--|--|--|--|

| Parameter<br>No. Symbol Characteristic                                              |           |                | Min                                                                                                                             | Тур | Max | Units | Conditions      |  |  |  |  |

| Operating V                                                                         | Voltage   |                |                                                                                                                                 |     |     |       |                 |  |  |  |  |

| HDC10                                                                               | Supply Vo | Supply Voltage |                                                                                                                                 |     |     |       |                 |  |  |  |  |

| VDD         —         3.0         3.3         3.6         V         -40°C to +150°C |           |                |                                                                                                                                 |     |     |       | -40°C to +150°C |  |  |  |  |

### TABLE 23-4: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACTERISTICS                      |     |       | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+150°C for High Temperature |                                                            |      |                                          |

|-----------------------------------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------------------------------------------|

| Parameter<br>No. Typical Max            |     | Units | Conditions                                                                                                                                               |                                                            |      |                                          |