Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Becano                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DCI, DMA, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 32KB (32K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 2K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 13x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj32gp204t-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ABLE 4-5: | TIMER REGISTER MAP |

|-----------|--------------------|

|-----------|--------------------|

| ABLE 4-5: | TIMER REGISTER MAP |

|-----------|--------------------|

|           |                    |

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12 | Bit 11  | Bit 10 | Bit 9         | Bit 8         | Bit 7       | Bit 6      | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|-------------------|--------|--------|---------|--------|---------------|---------------|-------------|------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1     | 0100        |        |                   |        |        |         |        |               | Timer1        | Register    |            |       |        |       |       |       |       | 0000          |

| PR1      | 0102        |        | Period Register 1 |        |        |         |        |               |               |             |            |       |        | FFFF  |       |       |       |               |

| T1CON    | 0104        | TON    | —                 | TSIDL  | —      | —       | _      | _             | _             | —           | TGATE      | TCKP  | S<1:0> | _     | TSYNC | TCS   | —     | 0000          |

| TMR2     | 0106        |        | Timer2 Register   |        |        |         |        |               |               |             |            |       | 0000   |       |       |       |       |               |

| TMR3HLD  | 0108        |        |                   |        |        |         | Time   | er3 Holding I | Register (for | 32-bit time | operations | only) |        |       |       |       |       | XXXX          |

| TMR3     | 010A        |        |                   |        |        |         |        |               | Timer3        | Register    |            |       |        |       |       |       |       | 0000          |

| PR2      | 010C        |        |                   |        |        |         |        |               | Period R      | Register 2  |            |       |        |       |       |       |       | FFFF          |

| PR3      | 010E        |        |                   |        |        |         |        |               | Period R      | Register 3  |            |       |        |       |       |       |       | FFFF          |

| T2CON    | 0110        | TON    | —                 | TSIDL  | —      | —       | _      | _             | _             | —           | TGATE      | TCKP  | S<1:0> | T32   |       | TCS   | —     | 0000          |

| T3CON    | 0112        | TON    | _                 | TSIDL  | —      | _       | _      | _             | —             | _           | TGATE      | TCKP  | S<1:0> | _     | —     | TCS   | _     | 0000          |

| Lanandi  |             |        |                   |        |        | L (al D |        | ore chours    | 2 . I         | et al a d   |            |       |        |       |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-6**: **INPUT CAPTURE REGISTER MAP**

|          | ••••••••••••••••••••••••••••••••••••••• |        |                          |        |        |           |        |       |             |              |       |       |       |       |       |          |       |               |

|----------|-----------------------------------------|--------|--------------------------|--------|--------|-----------|--------|-------|-------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| SFR Name | SFR<br>Addr                             | Bit 15 | Bit 14                   | Bit 13 | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

| IC1BUF   | 0140                                    |        |                          |        |        |           |        |       | Input 1 Cap | ture Registe | r     |       |       |       |       |          |       | XXXX          |

| IC1CON   | 0142                                    | —      | _                        | ICSIDL | _      | —         |        |       | —           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144                                    |        | Input 2 Capture Register |        |        |           |        |       |             | XXXX         |       |       |       |       |       |          |       |               |

| IC2CON   | 0146                                    | —      | _                        | ICSIDL | _      | _         | _      | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158                                    |        |                          |        |        |           |        |       | Input 7 Cap | ture Registe | r     |       |       |       |       |          |       | XXXX          |

| IC7CON   | 015A                                    | _      | _                        | ICSIDL | _      | _         | _      | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C                                    |        |                          |        |        |           |        |       | Input 8 Cap | ture Registe | r     |       |       |       |       |          |       | XXXX          |

| IC8CON   | 015E                                    | _      | _                        | ICSIDL | _      | _         | _      | _     | _           | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| 1        |                                         |        | <b>_</b>                 |        |        | d a fal D |        |       |             |              |       |       |       |       |       |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **OUTPUT COMPARE REGISTER MAP TABLE 4-7:**

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                    | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|---------------------------|------------|--------|--------|--------|--------|--------------|--------------|----------|-------|-------|--------|-------|----------|-------|---------------|

| OC1RS    | 0180        |        |                           |            |        |        |        | Output | Compare 1    | Secondary I  | Register |       |       |        |       |          |       | XXXX          |

| OC1R     | 0182        |        | Output Compare 1 Register |            |        |        |        |        |              | XXXX         |          |       |       |        |       |          |       |               |

| OC1CON   | 0184        | _      | _                         | OCSIDL     | _      | _      | _      | _      | _            | _            | _        | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        |                           |            |        |        |        | Output | Compare 2    | Secondary I  | Register |       |       |        |       |          |       | XXXX          |

| OC2R     | 0188        |        |                           |            |        |        |        | 0      | utput Comp   | are 2 Regist | er       |       |       |        |       |          |       | XXXX          |

| OC2CON   | 018A        | —      | _                         | OCSIDL     | _      | _      | _      | —      | —            | _            |          | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| Lawandi  |             |        | Deed                      | - unimalar |        |        |        |        | in hereinder | line al      |          |       |       |        |       |          |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.4.1 SOFTWARE STACK

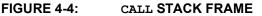

In addition to its use as a working register, the W15 register in the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-4. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | concatenates the SRL register to the MSB |

|       | of the PC prior to the push.             |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned.

When an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. For example, to cause a stack error trap when the stack grows beyond address 0x1000 in RAM, initialize the SPLIM with the value 0x0FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### 4.4.2 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features that enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for Boot Segment) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

## 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-23 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where:

Operand 1 is always a working register (that is, the addressing mode can only be register direct), which is referred to as Wb.

Operand 2 can be a W register, fetched from data memory, or a 5-bit literal.

The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site: (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

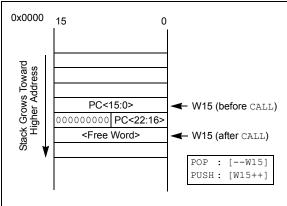

The Reset module combines all reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

### FIGURE 6-1: RESET MODULE BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset sets a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR bit (RCON<0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

**Note:** The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

| U-0             | U-0             | U-0                                                  | U-0 | U-0                                     | U-0 | U-0   | U-0   |  |  |  |

|-----------------|-----------------|------------------------------------------------------|-----|-----------------------------------------|-----|-------|-------|--|--|--|

|                 | —               | —                                                    | —   | —                                       | —   | —     | —     |  |  |  |

| bit 15          |                 |                                                      |     |                                         |     | •     | bit 8 |  |  |  |

|                 |                 |                                                      |     |                                         |     |       |       |  |  |  |

| U-0             | U-0             | U-0                                                  | U-0 | U-0                                     | U-0 | R/W-0 | U-0   |  |  |  |

| —               | —               | —                                                    | _   | —                                       | —   | U1EIE | —     |  |  |  |

| bit 7           |                 |                                                      |     |                                         |     |       | bit 0 |  |  |  |

|                 |                 |                                                      |     |                                         |     |       |       |  |  |  |

| Legend:         |                 |                                                      |     |                                         |     |       |       |  |  |  |

| R = Readable    | bit             | W = Writable                                         | bit | U = Unimplemented bit, read as '0'      |     |       |       |  |  |  |

| -n = Value at P | POR             | '1' = Bit is set                                     |     | '0' = Bit is cleared x = Bit is unknown |     |       |       |  |  |  |

|                 |                 |                                                      |     |                                         |     |       |       |  |  |  |

| bit 15-2        | Unimplemen      | ted: Read as '                                       | )'  |                                         |     |       |       |  |  |  |

| bit 1           | 1 = Interrupt r | 1 Error Interrup<br>equest enabled<br>equest not ena | t   |                                         |     |       |       |  |  |  |

### REGISTER 7-10: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

bit 0 Unimplemented: Read as '0'

# dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304

| U-0                 | U-0     | U-0              | U-0   | U-0              | U-0              | U-0            | R/W-0     |

|---------------------|---------|------------------|-------|------------------|------------------|----------------|-----------|

| —                   | —       | —                | —     | —                | _                | _              | PLLDIV<8> |

| bit 15              |         |                  |       |                  |                  |                | bit 8     |

| R/W-0               | R/W-0   | R/W-1            | R/W-1 | R/W-0            | R/W-0            | R/W-0          | R/W-0     |

| 11/00-0             | 10/00-0 | 10/00-1          |       | V<7:0>           | 10/00-0          | 10,00-0        | 10/00-0   |

| bit 7               |         |                  |       | V ~1.0P          |                  |                | bit 0     |

|                     |         |                  |       |                  |                  |                |           |

| Legend:             |         |                  |       |                  |                  |                |           |

| R = Readable        | e bit   | W = Writable I   | oit   | U = Unimplen     | nented bit, read | as '0'         |           |

| -n = Value at       | POR     | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unl | known     |

| bit 15-9<br>bit 8-0 | -       | 513              |       | (also denoted    | as 'M', PLL mul  | tiplier)       |           |

# REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

NOTES:

### 10.9 Peripheral Pin Select Registers

The dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304 devices implement 17 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (9)

- Output Remappable Peripheral Registers (8)

| Note: | Input and Output Register values can only |

|-------|-------------------------------------------|

|       | be changed if OSCCON[IOLOCK] = 0.         |

|       | See Section 10.6.3.1 "Control Register    |

|       | Lock" for a specific command sequence.    |

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0             | U-0 | U-0              | R/W-1 | R/W-1            | R/W-1            | R/W-1              | R/W-1 |  |

|-----------------|-----|------------------|-------|------------------|------------------|--------------------|-------|--|

| —               | —   | —                |       |                  | INT1R<4:0>       |                    |       |  |

| bit 15          |     |                  |       |                  |                  |                    | bit 8 |  |

| U-0             | U-0 | U-0              | U-0   | U-0              | U-0              | U-0                | U-0   |  |

| _               | —   | _                | _     | —                | _                | —                  | —     |  |

| bit 7           |     |                  |       |                  |                  |                    | bit 0 |  |

| Legend:         |     |                  |       |                  |                  |                    |       |  |

| R = Readable    | bit | W = Writable     | bit   | U = Unimpler     | nented bit, read | d as '0'           |       |  |

| -n = Value at F | POR | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

bit 12-8

INT1R<4:0>: Assign External Interrupt 1 (INTR1) to the corresponding RPn pin

11111 = Input tied to Vss

11001 = Input tied to RP25

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

# 12.3 Timer2/3 Control Registers

| R/W-0                      | U-0                                     | R/W-0                                                          | U-0              | U-0                               | U-0           | U-0             | U-0   |  |  |  |  |  |

|----------------------------|-----------------------------------------|----------------------------------------------------------------|------------------|-----------------------------------|---------------|-----------------|-------|--|--|--|--|--|

| TON                        | —                                       | TSIDL                                                          | —                | —                                 | —             | —               |       |  |  |  |  |  |

| bit 15                     |                                         |                                                                |                  |                                   |               |                 | bit 8 |  |  |  |  |  |

|                            |                                         |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

| U-0                        | R/W-0                                   | R/W-0                                                          | R/W-0            | R/W-0                             | U-0           | R/W-0           | U-0   |  |  |  |  |  |

| —                          | TGATE                                   | TCKP                                                           | S<1:0>           | T32                               | —             | TCS             |       |  |  |  |  |  |

| bit 7                      |                                         |                                                                |                  |                                   |               |                 | bit ( |  |  |  |  |  |

|                            |                                         |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

| Legend:                    | la hit                                  |                                                                | L.1              |                                   | anted bit rea | d aa (0)        |       |  |  |  |  |  |

| R = Readab<br>-n = Value a |                                         | W = Writable<br>'1' = Bit is set                               |                  | U = Unimplem<br>'0' = Bit is clea |               |                 | 0.4/0 |  |  |  |  |  |

|                            | IPUR                                    |                                                                |                  |                                   | areu          | x = Bit is unkn | OWIT  |  |  |  |  |  |

| bit 15                     | TON: Timer2                             | On hit                                                         |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | When T32 =                              |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | 1 = Starts 32                           | -bit Timer2/3                                                  |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | •                                       | 0 = Stops 32-bit Timer2/3                                      |                  |                                   |               |                 |       |  |  |  |  |  |

|                            |                                         | $\frac{\text{When T32 = 0:}}{1 = \text{Starts 16-bit Timer2}}$ |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | 1 = Starts 16<br>0 = Stops 16           |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

| bit 14                     | -                                       |                                                                | 0'               |                                   |               |                 |       |  |  |  |  |  |

| bit 13                     | -                                       | Unimplemented: Read as '0'<br>TSIDL: Stop in Idle Mode bit     |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | =                                       | 1 = Discontinue module operation when device enters Idle mode  |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | 0 = Continue                            | module operat                                                  | tion in Idle mo  | de                                |               |                 |       |  |  |  |  |  |

| bit 12-7                   | Unimplemer                              | nted: Read as '                                                | 0'               |                                   |               |                 |       |  |  |  |  |  |

| bit 6                      |                                         | er2 Gated Time                                                 | e Accumulation   | n Enable bit                      |               |                 |       |  |  |  |  |  |

|                            | When TCS =                              |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | This bit is ign                         |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

|                            |                                         | When TCS = 0:<br>1 = Gated time accumulation enabled           |                  |                                   |               |                 |       |  |  |  |  |  |

|                            |                                         | 0 = Gated time accumulation disabled                           |                  |                                   |               |                 |       |  |  |  |  |  |

| bit 5-4                    | TCKPS<1:0>                              | : Timer2 Input                                                 | Clock Presca     | le Select bits                    |               |                 |       |  |  |  |  |  |

|                            | 11 <b>= 1:256</b>                       |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | 10 = 1:64                               |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | 01 = 1.8<br>00 = 1:1                    | 01 = 1:8<br>00 = 1:1                                           |                  |                                   |               |                 |       |  |  |  |  |  |

| bit 3                      | T32: 32-bit T                           | imer Mode Sele                                                 | ect bit          |                                   |               |                 |       |  |  |  |  |  |

|                            | 1 = Timer2 a                            | 1 = Timer2 and Timer3 form a single 32-bit timer               |                  |                                   |               |                 |       |  |  |  |  |  |

|                            | 0 = Timer2 a                            | nd Timer3 act a                                                | as two 16-bit ti | imers                             |               |                 |       |  |  |  |  |  |

| bit 2                      | -                                       | nted: Read as '                                                |                  |                                   |               |                 |       |  |  |  |  |  |

| bit 1                      |                                         | Clock Source                                                   |                  |                                   |               |                 |       |  |  |  |  |  |

|                            |                                         | clock from pin                                                 | T2CK (on the     | rising edge)                      |               |                 |       |  |  |  |  |  |

| 1.1.0                      | 0 = Internal o                          | llock (FCY)<br>nted: Read as '                                 | o.1              |                                   |               |                 |       |  |  |  |  |  |

| bit 0                      | IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |                                                                |                  |                                   |               |                 |       |  |  |  |  |  |

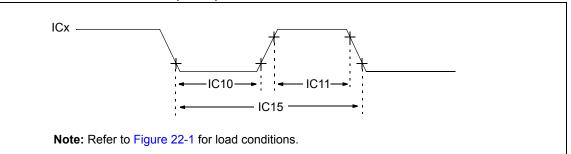

# 13.2 Input Capture Registers

### REGISTER 13-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | -   | —   | —   |     | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

|        |     |        |     |     |     |     |       |

| R/W-0 | R/W-0 | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0    | R/W-0 |

|-------|-------|-------|---------|---------|-------|----------|-------|

| ICTMR | ICI<  | 1:0>  | ICOV    | ICBNE   |       | ICM<2:0> |       |

| bit 7 |       |       |         |         |       |          | bit 0 |

| Legend:           |                  | HC = C                | leared in hardware |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Module Stop in Idle Control bit                                                                                                                                                                          |

|           | 1 = Input capture module will halt in CPU Idle mode                                                                                                                                                                            |

|           | 0 = Input capture module will continue to operate in CPU Idle mode                                                                                                                                                             |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                     |

| bit 7     | ICTMR: Input Capture Timer Select bits                                                                                                                                                                                         |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                   |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                         |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                   |

|           | 10 = Interrupt on every third capture event                                                                                                                                                                                    |

|           | <ul> <li>01 = Interrupt on every second capture event</li> <li>00 = Interrupt on every capture event</li> </ul>                                                                                                                |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                                                                                       |

|           | 1 = Input capture overflow occurred                                                                                                                                                                                            |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                         |

| bit 3     | ICBNE: Input Capture Buffer Empty Status bit (read-only)                                                                                                                                                                       |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                              |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                                                                                       |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode<br/>(Rising edge detect only, all other control bits are not applicable.)</li> <li>110 = Unused (module disabled)</li> </ul> |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                                                                                     |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                      |

|           | 011 = Capture mode, every rising edge<br>010 = Capture mode, every falling edge                                                                                                                                                |

|           | 001 = Capture mode, every edge (rising and falling)                                                                                                                                                                            |

|           | (ICI<1:0> bits do not control interrupt generation for this mode.)                                                                                                                                                             |

|           | 000 = Input capture module turned off                                                                                                                                                                                          |

|           |                                                                                                                                                                                                                                |

# 15.3 SPI Control Registers

### REGISTER 15-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER

| _      |        |         |     |     |     |        |        |

|--------|--------|---------|-----|-----|-----|--------|--------|

| R/W-0  | U-0    | R/W-0   | U-0 | U-0 | U-0 | U-0    | U-0    |

| SPIEN  | —      | SPISIDL | —   | -   | —   | —      | —      |

| bit 15 |        |         |     |     |     |        | bit 8  |

|        |        |         |     |     |     |        |        |

| U-0    | R/C-0  | U-0     | U-0 | U-0 | U-0 | R-0    | R-0    |

| —      | SPIROV | —       | _   | _   | —   | SPITBF | SPIRBF |

| bit 7  |        |         |     |     |     |        | bit 0  |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15   | SPIEN: SPIx Enable bit                                                                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = Enables module and configures SCKx, SDOx, SDIx and $\overline{SSx}$ as serial port pins 0 = Disables module                                                                                                                                                                                                |

| bit 14   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 13   | SPISIDL: Stop in Idle Mode bit                                                                                                                                                                                                                                                                                 |

|          | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul>                                                                                                                                                                             |

| bit 12-7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 6    | <ul> <li>SPIROV: Receive Overflow Flag bit</li> <li>1 = A new byte/word is completely received and discarded. The user software has not read the previous data in the SPIxBUF register</li> <li>0 = No overflow has occurred.</li> </ul>                                                                       |

| bit 5-2  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                     |

| bit 1    | SPITBF: SPIx Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                   |

|          | <ul> <li>1 = Transmit not yet started, SPIxTXB is full</li> <li>0 = Transmit started, SPIxTXB is empty</li> <li>Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.</li> <li>Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.</li> </ul> |

| bit 0    | SPIRBF: SPIx Receive Buffer Full Status bit                                                                                                                                                                                                                                                                    |

|          | <ul> <li>1 = Receive complete, SPIxRXB is full</li> <li>0 = Receive is not complete, SPIxRXB is empty</li> <li>Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB.</li> <li>Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.</li> </ul>         |

## REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 5 | <b>ACKDT:</b> Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | <ul> <li>ACKEN: Acknowledge Sequence Enable bit</li> <li>(when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3 | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)<br>1 = Enables Receive mode for I <sup>2</sup> C. Hardware clear at end of eighth bit of master receive data byte<br>0 = Receive sequence not in progress                                                                                                                    |

| bit 2 | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence</li> <li>0 = Stop condition not in progress</li> </ul>                                                                                                       |

| bit 1 | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence</li> <li>0 = Repeated Start condition not in progress</li> </ul>                                                              |

| bit 0 | <ul> <li>SEN: Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence</li> <li>0 = Start condition not in progress</li> </ul>                                                                                                   |

### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | Start bit                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul> |

|       | Hardware set or clear when Start, Repeated Start or Stop detected.                                                                         |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                                                          |

|       | 1 = Read – indicates data transfer is output from slave                                                                                    |

|       | 0 = Write – indicates data transfer is input to slave                                                                                      |

|       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.                                                             |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                        |

|       | 1 = Receive complete, I2CxRCV is full                                                                                                      |

|       | 0 = Receive not complete, I2CxRCV is empty                                                                                                 |

|       | Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV.                                    |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                       |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                                                  |

|       | 0 = Transmit complete, I2CxTRN is empty                                                                                                    |

|       | Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.                                              |

# dsPIC33FJ32GP202/204 and dsPIC33FJ16GP304

| R/W-0         | U-0                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                         | R/W-0                                               | R/W-0            | R/W-0           | R/W-0          |  |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-----------------|----------------|--|--|--|--|--|--|--|

| CH0NB         |                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                      |                                                                                                                                                                                               |                                                     | CH0SB<4:0>       |                 |                |  |  |  |  |  |  |  |

| bit 15        |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |                                                     |                  |                 | bit            |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        | DAMA                                                                                                                                                                                          | DAALO                                               | DANO             | <b>D</b> /// 0  | <b>D</b> 444.0 |  |  |  |  |  |  |  |

| R/W-0         | U-0                                                                                                                                                                                                                             | U-0                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                         | R/W-0                                               | R/W-0            | R/W-0           | R/W-0          |  |  |  |  |  |  |  |

| CHONA         | —                                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                      |                                                                                                                                                                                               |                                                     | CH0SA<4:0>       |                 |                |  |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |                                                     |                  |                 | bit            |  |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |                                                     |                  |                 |                |  |  |  |  |  |  |  |

| R = Readabl   | e bit                                                                                                                                                                                                                           | W = Writable                                                                                                                                                                                                                                           | bit                                                                                                                                                                                           | U = Unimple                                         | mented bit, read | l as '0'        |                |  |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                                                                       | :                                                                                                                                                                                             | '0' = Bit is cle                                    | eared            | x = Bit is unkr | nown           |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |                                                     |                  |                 |                |  |  |  |  |  |  |  |

| bit 15        | CH0NB: Ch                                                                                                                                                                                                                       | annel 0 Negativ                                                                                                                                                                                                                                        | e Input Select                                                                                                                                                                                | for Sample B b                                      | bit              |                 |                |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                 | l 0 negative inpu                                                                                                                                                                                                                                      |                                                                                                                                                                                               |                                                     |                  |                 |                |  |  |  |  |  |  |  |

|               | 0 = Channel                                                                                                                                                                                                                     | l 0 negative inpu                                                                                                                                                                                                                                      | it is VREF-                                                                                                                                                                                   |                                                     |                  |                 |                |  |  |  |  |  |  |  |

| bit 14-13     | Unimpleme                                                                                                                                                                                                                       | nted: Read as '                                                                                                                                                                                                                                        | 0'                                                                                                                                                                                            |                                                     |                  |                 |                |  |  |  |  |  |  |  |

| bit 12-8      | CH0SB<4:0>: Channel 0 Positive Input Select for Sample B bits                                                                                                                                                                   |                                                                                                                                                                                                                                                        |                                                                                                                                                                                               |                                                     |                  |                 |                |  |  |  |  |  |  |  |

|               |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                        | •                                                                                                                                                                                             | dsPIC33FJ32GP204 and dsPIC33FJ16GP304 devices only: |                  |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3                                                                                                                                                                                                                      | 32GP204 and d                                                                                                                                                                                                                                          | sPIC33FJ16G                                                                                                                                                                                   |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                        | sPIC33FJ16G                                                                                                                                                                                   |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3                                                                                                                                                                                                                      | 32GP204 and d                                                                                                                                                                                                                                          | sPIC33FJ16G                                                                                                                                                                                   |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3                                                                                                                                                                                                                      | 32GP204 and d                                                                                                                                                                                                                                          | sPIC33FJ16G                                                                                                                                                                                   |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•                                                                                                                                                                                              | 32GP204 and data and a data annel 0 positive                                                                                                                                                                                                           | sPIC33FJ16G<br>input is AN12                                                                                                                                                                  |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch                                                                                                                                                                                | 32GP204 and d                                                                                                                                                                                                                                          | sPIC33FJ16G<br>input is AN12<br>input is AN2                                                                                                                                                  |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch                                                                                                                                                                  | <b>32GP204 and d</b> annel 0 positive<br>annel 0 positive                                                                                                                                                                                              | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1                                                                                                                                  |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch<br>00000 = Ch                                                                                                                                                    | <b>32GP204 and d</b><br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive                                                                                                                                                   | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0                                                                                                                  |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>dsPIC33FJ3                                                                                                                                      | 32GP204 and de<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>32GP202 device                                                                                                                                       | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:                                                                                                      |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>dsPIC33FJ3                                                                                                                                      | <b>32GP204 and d</b><br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive                                                                                                                                                   | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:                                                                                                      |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>dsPIC33FJ3                                                                                                                                      | 32GP204 and de<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br>32GP202 device                                                                                                                                       | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:                                                                                                      |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>dsPIC33FJ3<br>01100 = Ch<br>•                                                                                                                   | <b>32GP204 and d</b><br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br><b>32GP202 device</b><br>annel 0 positive                                                                                                                          | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:                                                                                                      |                                                     | only:            |                 |                |  |  |  |  |  |  |  |

|               | dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>00010 = Ch<br>00001 = Ch<br>00000 = Ch<br>dsPIC33FJ3<br>01100 = Ch<br>•<br>•<br>•                                                                                                         | <b>32GP204 and d</b><br>annel 0 positive<br>annel 0 positive<br>annel 0 positive<br><b>32GP202 device</b><br>annel 0 positive                                                                                                                          | sPIC33FJ16G<br>input is AN12<br>input is AN2<br>input is AN1<br>input is AN0<br>es only:                                                                                                      |                                                     | only:            |                 |                |  |  |  |  |  |  |  |