#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

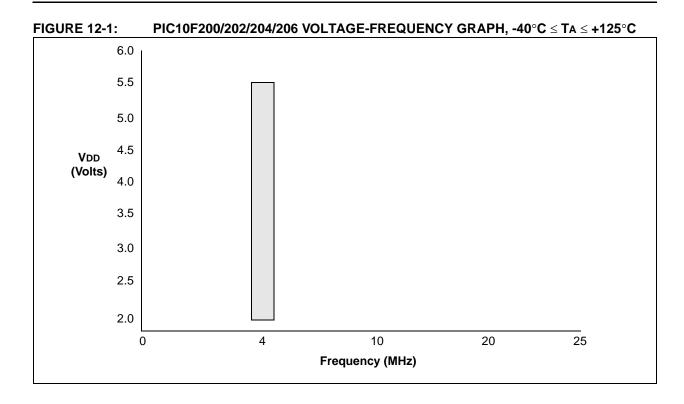

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 3                                                                        |

| Program Memory Size        | 384B (256 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f200-i-mc |

|                            |                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 PIC10F200/202/204/206 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC10F200/202/204/206 Product Identification System at the back of this data sheet to specify the correct part number.

### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry code, password or ID number.

## 4.0 MEMORY ORGANIZATION

The PIC10F200/202/204/206 memories are organized into program memory and data memory. Data memory banks are accessed using the File Select Register (FSR).

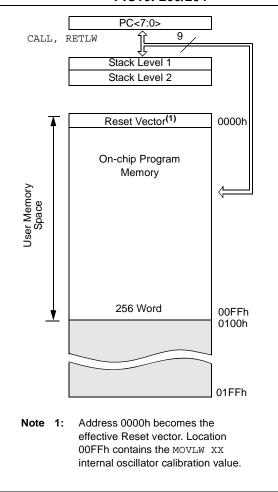

## 4.1 Program Memory Organization for the PIC10F200/204

The PIC10F200/204 devices have a 9-bit Program Counter (PC) capable of addressing a  $512 \times 12$  program memory space.

Only the first  $256 \times 12$  (0000h-00FFh) for the PIC10F200/204 are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wraparound within the first  $256 \times 12$  space (PIC10F200/204). The effective Reset vector is at 0000h (see Figure 4-1). Location 00FFh (PIC10F200/204) contains the internal clock oscillator calibration value. This value should never be overwritten.

### FIGURE 4-1:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC10F200/204

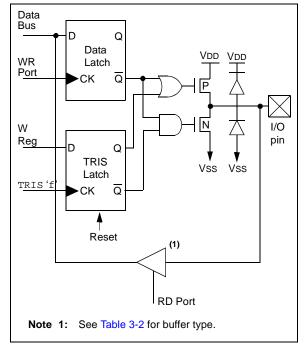

## 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

### 5.1 GPIO

GPIO is an 8-bit I/O register. Only the low-order 4 bits are used (GP<3:0>). Bits 7 through 4 are unimplemented and read as '0's. Please note that GP3 is an input-only pin. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are <u>not pin</u> selectable. If GP3/MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

## 5.2 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input-only and the GP2/TOCKI/COUT/FOSC4 pin, which may be controlled by various registers. See Table 5-1.

**Note:** A read of the ports reads the pins, not the output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is low.

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

#### TABLE 5-1: ORDER OF PRECEDENCE FOR PIN FUNCTIONS

| Priority | GP0       | GP1                 | GP2       | GP3    |

|----------|-----------|---------------------|-----------|--------|

| 1        | CIN+      | CIN-                | FOSC4     | I/MCLR |

| 2        | TRIS GPIO | TRIS GPIO TRIS GPIO |           | _      |

| 3        | _         | _                   | T0CKI     | _      |

| 4        | _         | —                   | TRIS GPIO | _      |

## 5.3 I/O Interfacing

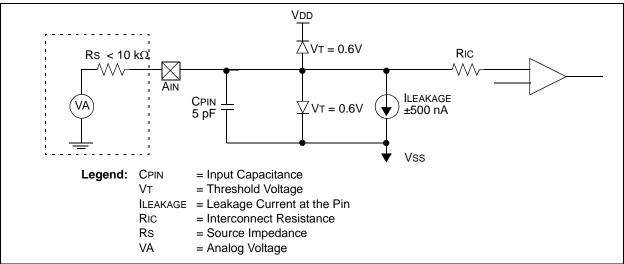

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is inputonly, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

#### PIC10F200/202/204/206 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

### FIGURE 5-2: SUCCESSIVE I/O OPERATION (PIC10F200/202/204/206)

`Q1| Q2| Q3| Q4` Q1| Q2| Q3| Q4` Q1| Q2| Q3| Q4` Q1| Q2| Q3| Q4`

| Instruction             | PC         | V PC + 1                                                  | PC + 2                                                 | X PC + 3 | This example shows a write to GPIO followed by a read from GPIO.                       |

|-------------------------|------------|-----------------------------------------------------------|--------------------------------------------------------|----------|----------------------------------------------------------------------------------------|

| Fetched                 | MOVWF GPIO | MOVF GPIO, W                                              | NOP                                                    | NOP      | Data setup time = (0.25 TCY - TPD)                                                     |

|                         |            | i i                                                       |                                                        |          | where: TCY = instruction cycle                                                         |

| GP<2:0>                 |            |                                                           | χ                                                      |          | TPD = propagation delay                                                                |

| Instruction<br>Executed |            | Port pin<br>written here<br>MOVWF GPIO<br>(Write to GPIO) | Port pin<br>sampled here<br>MOVF GPIO,W<br>(Read GPIO) | NOP      | Therefore, at higher clock frequencies, a write followed by a read may be problematic. |

## 8.0 COMPARATOR MODULE

The comparator module contains one Analog comparator. The inputs to the comparator are multiplexed with GP0 and GP1 pins. The output of the comparator can be placed on GP2.

The CMCON0 register, shown in Register 8-1, controls the comparator operation. A block diagram of the comparator is shown in Figure 8-1.

#### REGISTER 8-1: CMCON0 REGISTER

| R-1    | R/W-1 R/W-1 |  | R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|-------------|--|---------|-------|-------|-------|-------|

| CMPOUT |             |  | CMPT0CS | CMPON | CNREF | CPREF | CWU   |

| bit 7  |             |  |         |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7  |    | CMPOUT: Comparator Output bit                                                                                                     |

|--------|----|-----------------------------------------------------------------------------------------------------------------------------------|

|        |    | 1 = VIN + > VIN-                                                                                                                  |

|        |    | $0 = VIN + \langle VIN - UIN \rangle$                                                                                             |

| bit 6  |    | <b>COUTEN:</b> Comparator Output Enable bit <sup>(1, 2)</sup>                                                                     |

|        |    | 1 = Output of comparator is NOT placed on the COUT pin                                                                            |

| h:+ 7  |    | <ul> <li>0 = Output of comparator is placed in the COUT pin</li> <li>POL: Comparator Output Polarity bit<sup>(2)</sup></li> </ul> |

| bit 5  |    |                                                                                                                                   |

|        |    | <ul> <li>1 = Output of comparator not inverted</li> <li>0 = Output of comparator inverted</li> </ul>                              |

| bit 4  |    | <b>CMPT0CS</b> : Comparator TMR0 Clock Source bit <sup>(2)</sup>                                                                  |

|        |    | 1 = TMR0 clock source selected by T0CS control bit                                                                                |

|        |    | 0 = Comparator output used as TMR0 clock source                                                                                   |

| bit 3  |    | CMPON: Comparator Enable bit                                                                                                      |

|        |    | 1 = Comparator is on                                                                                                              |

|        |    | 0 = Comparator is off                                                                                                             |

| bit 2  |    | <b>CNREF:</b> Comparator Negative Reference Select bit <sup>(2)</sup>                                                             |

|        |    | $1 = \text{CIN-pin}^{(3)}$                                                                                                        |

| L 14 A |    | 0 = Internal voltage reference                                                                                                    |

| bit 1  |    | <b>CPREF:</b> Comparator Positive Reference Select bit <sup>(2)</sup><br>1 = CIN+ pin <sup>(3)</sup>                              |

|        |    | 0 = CIN+ pint(3)                                                                                                                  |

| bit 0  |    | <b>CWU</b> : Comparator Wake-up on Change Enable bit <sup>(2)</sup>                                                               |

|        |    | 1 = Wake-up on comparator change is disabled                                                                                      |

|        |    | 0 = Wake-up on comparator change is enabled.                                                                                      |

| Note   | 1: | Overrides T0CS bit for TRIS control of GP2.                                                                                       |

|        | 2: | When the comparator is turned on, these control bits assert themselves. When the comparator is off, these                         |

|        |    | bits have no effect on the device operation and the other control registers have precedence.                                      |

|        | 3: | PIC10F204/206 only.                                                                                                               |

**3:** PIC10F204/206 only.

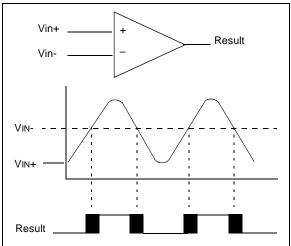

## 8.2 Comparator Operation

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time. See Table 12-1 for Common Mode Voltage.

FIGURE 8-2: SINGLE COMPARATOR

## 8.3 Comparator Reference

An internal reference signal may be used depending on the Comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 8-2). Please see Table 12-1 for internal reference specifications.

## 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is to have a valid level. If the comparator inputs are changed, a delay must be used to allow the comparator to settle to its new state. Please see Table 12-1 for comparator response time specifications.

### 8.5 Comparator Output

The comparator output is read through CMCON0 register. This bit is read-only. The comparator output may also be used internally, see Figure 8-1.

| Note: |           | alog levels o<br>ligital input i |      |         |      |    |

|-------|-----------|----------------------------------|------|---------|------|----|

|       | to<br>spe | consume<br>ecified.              | more | current | than | is |

### 8.6 Comparator Wake-up Flag

The comparator wake-up flag is set whenever all of the following conditions are met:

- $\overline{\text{CWU}} = 0$  (CMCON0<0>)

- CMCON0 has been read to latch the last known state of the CMPOUT bit (MOVF CMCON0, W)

- Device is in Sleep

- The output of the comparator has changed state

The wake-up flag may be cleared in software or by another device Reset.

# 8.7 Comparator Operation During Sleep

When the comparator is active and the device is placed in Sleep mode, the comparator remains active. While the comparator is powered-up, higher Sleep currents than shown in the power-down current specification will occur. To minimize power consumption while in Sleep mode, turn off the comparator before entering Sleep.

## 8.8 Effects of a Reset

A Power-on Reset (POR) forces the CMCON0 register to its Reset state. This forces the comparator module to be in the comparator Reset mode. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparator will be powered-down during the Reset interval.

## 8.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 8-3. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### FIGURE 8-3: ANALOG INPUT MODE

| Address | Name     | Bit 7  | Bit 6  | Bit 5 | Bit 4   | Bit 3     | Bit 2      | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>All Other<br>Resets |

|---------|----------|--------|--------|-------|---------|-----------|------------|-------|-------|-----------------|---------------------------------|

| 03h     | STATUS   | GPWUF  | CWUF   | _     | TO      | PD        | Z          | DC    | С     | 00-1 1xxx       | qq0q quuu                       |

| 07h     | CMCON0   | CMPOUT | COUTEN | POL   | CMPT0CS | CMPON     | CNREF      | CPREF | CWU   | 1111 1111       | uuuu uuuu                       |

| N/A     | TRISGPIO | —      | _      | _     | —       | I/O Contr | ol Registe | er    | 1111  | 1111            |                                 |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0', q = Depends on condition.

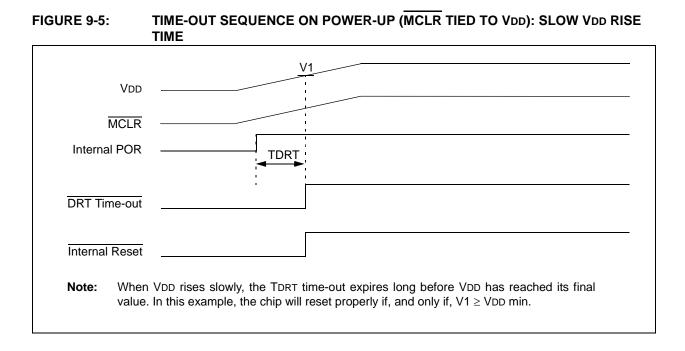

# 9.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC10F200/202/204/206 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT)

- Wake-up from Sleep on pin change

- Wake-up from Sleep on comparator change

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

- · Clock Out

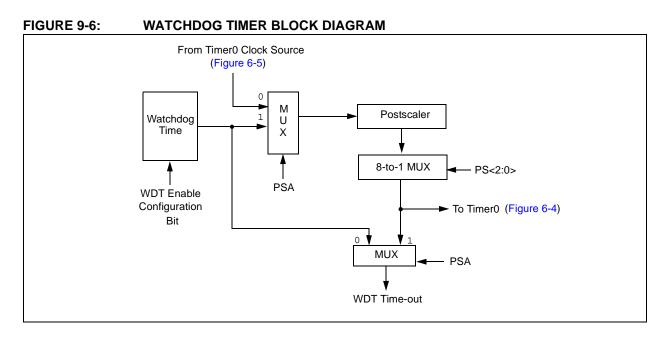

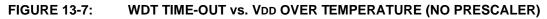

The PIC10F200/202/204/206 devices have a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. When using INTRC, there is an 18 ms delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through a change on input pins, wake-up from comparator change, or through a Watchdog Timer time-out.

### 9.1 Configuration Bits

The PIC10F200/202/204/206 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. One bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (see Register 9-1).

#### **REGISTER 9-1:** CONFIGURATION WORD FOR PIC10F200/202/204/206<sup>(1,2)</sup>

| R/P-1  | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 | R/P-1 |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | —     | MCLRE | CP    | WDTE  | _     | —     |

| bit 11 |       |       |       |       |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

- bit 11-5 Unimplemented: Read as '0'

- bit 4 MCLRE: GP3/MCLR Pin Function Select bit

- $1 = GP3/\overline{MCLR}$  pin function is  $\overline{MCLR}$

- 0 = GP3/MCLR pin function is digital I/O, MCLR internally tied to VDD

- bit 3 CP: Code Protection bit

- 1 = Code protection off

- 0 = Code protection on

- bit 2 WDTE: Watchdog Timer Enable bit

- 1 = WDT enabled

- 0 = WDT disabled

- bit 1-0 Reserved: Read as '0'

- **Note 1:** Refer to the "*PIC10F200/202/204/206 Memory Programming Specifications*" (DS41228) to determine how to access the Configuration Word. The Configuration Word is not user addressable during device operation.

- 2: INTRC is the only oscillator mode offered on the PIC10F200/202/204/206.

#### TABLE 9-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer, - = unimplemented, read as '0', u = unchanged.

## 10.0 INSTRUCTION SET SUMMARY

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories.

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 12-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

#### TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                             |

| W             | Working register (accumulator)                                                                                                                                                   |

| b             | Bit address within an 8-bit file register                                                                                                                                        |

| k             | Literal field, constant data or label                                                                                                                                            |

| x             | Don't care location (= $0$ or 1)<br>The assembler will generate code with x = $0$ . It is<br>the recommended form of use for compatibility with<br>all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register '£')<br>Default is d = 1                                                                |

| label         | Label name                                                                                                                                                                       |

| TOS           | Top-of-Stack                                                                                                                                                                     |

| PC            | Program Counter                                                                                                                                                                  |

| WDT           | Watchdog Timer counter                                                                                                                                                           |

| TO            | Time-out bit                                                                                                                                                                     |

| PD            | Power-down bit                                                                                                                                                                   |

| dest          | Destination, either the W register or the specified register file location                                                                                                       |

| [ ]           | Options                                                                                                                                                                          |

| ( )           | Contents                                                                                                                                                                         |

| $\rightarrow$ | Assigned to                                                                                                                                                                      |

| < >           | Register bit field                                                                                                                                                               |

| ∈             | In the set of                                                                                                                                                                    |

| italics       | User defined term (font is courier)                                                                                                                                              |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 10-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

## FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations                                                                                               |                    |       |            |   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|------------|---|--|--|--|--|

| <u>11 6</u>                                                                                                                          | 5                  | 4     |            | 0 |  |  |  |  |

| OPCODE                                                                                                                               | d                  |       | f (FILE #) |   |  |  |  |  |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 5-bit file register address                                                |                    |       |            |   |  |  |  |  |

| Bit-oriented file regis                                                                                                              | ter op             | oerat | ions       |   |  |  |  |  |

| <u>11 8</u>                                                                                                                          | 7                  | 5     | 4          | 0 |  |  |  |  |

| OPCODE                                                                                                                               | b (B               | T #)  | f (FILE #) |   |  |  |  |  |

| <ul> <li>b = 3-bit address</li> <li>f = 5-bit file register address</li> <li>Literal and control operations (except GOTO)</li> </ul> |                    |       |            |   |  |  |  |  |

| <u>11</u>                                                                                                                            | 8                  | 7     |            | 0 |  |  |  |  |

| OPCODE                                                                                                                               | OPCODE k (literal) |       |            |   |  |  |  |  |

| k = 8-bit immedia                                                                                                                    | ate va             | lue   |            |   |  |  |  |  |

| Literal and control operations – GOTO instruction                                                                                    |                    |       |            |   |  |  |  |  |

| 11                                                                                                                                   | 9                  | 8     |            | 0 |  |  |  |  |

| OPCODE k (literal)                                                                                                                   |                    |       |            |   |  |  |  |  |

| k = 9-bit immediate value                                                                                                            |                    |       |            |   |  |  |  |  |

© 2004-2014 Microchip Technology Inc.

Increment f

INCF

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                    |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

Decrement f, Skip if 0 [label] DECFSZ f,d

(f)  $-1 \rightarrow d$ ; skip if result = 0

The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in

If the result is '0', the next instruction, which is already fetched, is

discarded and a NOP is executed

instead making it a 2-cycle instruc-

$0 \leq f \leq 31$

$d \in [0,1]$

register 'f'.

tion.

None

DECFSZ

Operands:

Operation:

Description:

Status Affected:

Syntax:

| Syntax:                 | [label] INCF f,d                                                                                                                                                           |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Operands:               | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |

| Operation:              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |  |  |  |  |

| Status Affected:        | Z                                                                                                                                                                          |  |  |  |  |

| Description:            | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |

| INCFSZ                  | Increment f, Skip if 0                                                                                                                                                     |  |  |  |  |

|                         | , 1                                                                                                                                                                        |  |  |  |  |

| Syntax:                 | [label] INCFSZ f,d                                                                                                                                                         |  |  |  |  |

| Syntax:<br>Operands:    | · •                                                                                                                                                                        |  |  |  |  |

| ,                       | [ <i>label</i> ] INCFSZ f,d<br>$0 \le f \le 31$                                                                                                                            |  |  |  |  |

| Operands:               | [ <i>label</i> ] INCFSZ f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$                                                                                                           |  |  |  |  |

| Operands:<br>Operation: | [ label ] INCFSZ f,d<br>$0 \le f \le 31$<br>$d \in [0,1]$<br>(f) + 1 $\rightarrow$ (dest), skip if result = 0                                                              |  |  |  |  |

fetched, is discarded and a NOP is executed instead making it a 2-cycle instruction.

| GOTO             | Unconditional Branch                                                                                                                                                                     |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                  |  |  |  |  |

| Operands:        | $0 \leq k \leq 511$                                                                                                                                                                      |  |  |  |  |

| Operation:       | k → PC<8:0>;<br>STATUS<6:5> → PC<10:9>                                                                                                                                                   |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                     |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a 2-cycle<br>instruction. |  |  |  |  |

| IORLW Inclusive OR literal with W |                                                                                                              |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                           | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |

| Operands:                         | $0 \le k \le 255$                                                                                            |  |  |  |  |

| Operation:                        | (W) .OR. (k) $\rightarrow$ (W)                                                                               |  |  |  |  |

| Status Affected:                  | Z                                                                                                            |  |  |  |  |

| Description:                      | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

### 11.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 11.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 12.4 Timing Parameter Symbology and Load Conditions – PIC10F200/202/204/206

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| 2. TppS     |                                          |     |                |  |  |  |

|-------------|------------------------------------------|-----|----------------|--|--|--|

| т           |                                          |     |                |  |  |  |

| F Frequency |                                          |     | T Time         |  |  |  |

| Lower       | case subscripts (pp) and their meanings: |     |                |  |  |  |

| рр          |                                          |     |                |  |  |  |

| 2           | to                                       | mc  | MCLR           |  |  |  |

| ck          | CLKOUT                                   | osc | Oscillator     |  |  |  |

| су          | Cycle time                               | tO  | ТОСКІ          |  |  |  |

| drt         | Device Reset Timer                       | wdt | Watchdog Timer |  |  |  |

| io          | I/O port                                 | wdt | Watchdog Timer |  |  |  |

| Upper       | case letters and their meanings:         |     |                |  |  |  |

| S           |                                          |     |                |  |  |  |

| F           | Fall                                     | Р   | Period         |  |  |  |

| Н           | High                                     | R   | Rise           |  |  |  |

| 1           | Invalid (high-impedance)                 | V   | Valid          |  |  |  |

| L           | Low                                      | Z   | High-impedance |  |  |  |

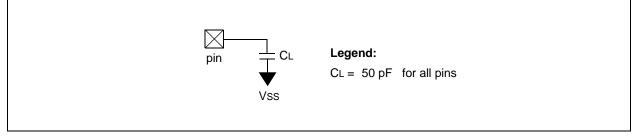

### FIGURE 12-2: LOAD CONDITIONS – PIC10F200/202/204/206

| AC CHARACTERISTICS |      | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial),} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in} \\ \mbox{Section 12.1 "DC Characteristics: PIC10F200/202/204/206} \\ \mbox{(Industrial)"} \end{array} $ |                    |              |              |              |            |                                                                                                                                                                                     |

|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--------------|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Sym. | Characteristic                                                                                                                                                                                                                                                                                                                                                                                                 | Freq.<br>Tolerance | Min.         | Тур.†        | Max.         | Units      | Conditions                                                                                                                                                                          |

| F10                | Fosc | Internal Calibrated<br>INTOSC Frequency <sup>(1,2)</sup>                                                                                                                                                                                                                                                                                                                                                       | ± 1%<br>± 2%       | 3.96<br>3.92 | 4.00<br>4.00 | 4.04<br>4.08 | MHz<br>MHz | VDD=3.5V @ 25°C<br>2.5V ≤ VDD ≤ 5.5V<br>0°C ≤ TA ≤ +85°C (industrial)                                                                                                               |

|                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                | ± 5%               | 3.80         | 4.00         | 4.20         | MHz        | $\begin{array}{l} 2.0V \leq VDD \leq 5.5V \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ (industrial)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ (extended)} \end{array}$ |

#### TABLE 12-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC10F200/202/204/206

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

2: Under stable VDD conditions.

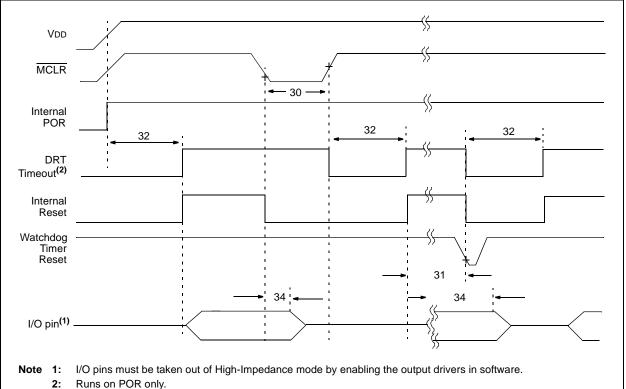

## FIGURE 12-3: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER TIMING – PIC10F200/202/204/206

© 2004-2014 Microchip Technology Inc.

## TABLE 14-1:8-LEAD 2x3 DFN (MC)PACKAGE TOP MARKING

| Part Number    | Marking |

|----------------|---------|

| PIC10F200-I/MC | BA0     |

| PIC10F200-E/MC | BB0     |

| PIC10F202-I/MC | BC0     |

| PIC10F202-E/MC | BD0     |

| PIC10F204-I/MC | BE0     |

| PIC10F204-E/MC | BF0     |

| PIC10F206-I/MC | BG0     |

| PIC10F206-E/MC | BH0     |

### TABLE 14-2: 6-LEAD SOT-23 (OT) PACKAGE TOP MARKING

| Marking |

|---------|

| 00NN    |

| 00NN    |

| 02NN    |

| 02NN    |

| 04NN    |

| 04NN    |

| 06NN    |

| 06NN    |

|         |

Note: NN represents the alphanumeric traceability code.

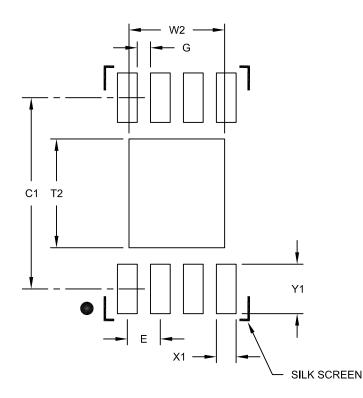

8-Lead Plastic Dual Flat, No Lead Package (MC) - 2x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                            | MILLIMETERS            |      |          |      |

|----------------------------|------------------------|------|----------|------|

| Dimensio                   | MIN                    | NOM  | MAX      |      |

| Contact Pitch              | E                      |      | 0.50 BSC |      |

| Optional Center Pad Width  | W2                     |      |          | 1.45 |

| Optional Center Pad Length | I Center Pad Length T2 |      |          | 1.75 |

| Contact Pad Spacing C1     |                        |      | 2.90     |      |

| Contact Pad Width (X8)     | X1                     |      |          | 0.30 |

| Contact Pad Length (X8)    | Y1                     |      |          | 0.75 |

| Distance Between Pads      |                        | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2123B