Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 384B (256 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f200t-e-ot |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

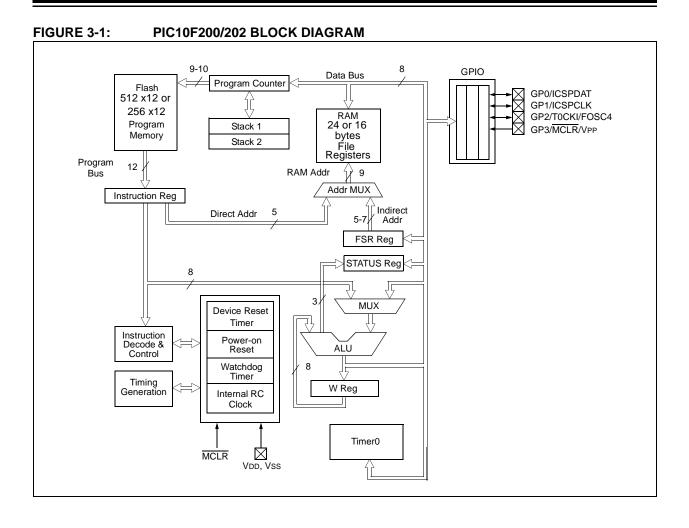

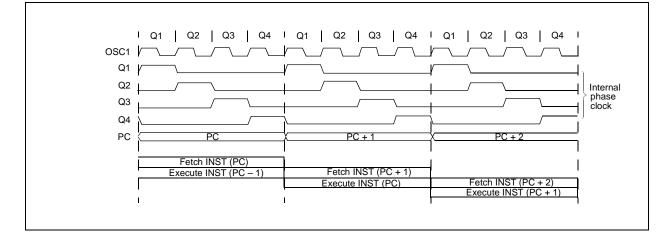

#### 3.1 Clocking Scheme/Instruction Cycle

FIGURE 3-3:

The clock is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3 and Example 3-1.

**CLOCK/INSTRUCTION CYCLE**

#### 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

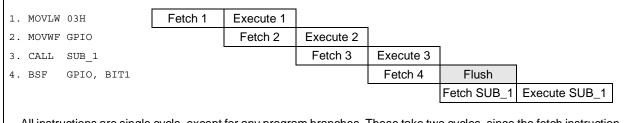

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

#### 4.3.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1).

The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

#### TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY (PIC10F200/202/204/206)

| Address            | Name     | Bit 7       | Bit 6               | Bit 5    | Bit 4        | Bit 3      | Bit 2      | Bit 1       | Bit 0 | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Register<br>on Page |

|--------------------|----------|-------------|---------------------|----------|--------------|------------|------------|-------------|-------|----------------------------------------------|---------------------|

| 00h                | INDF     | Uses Cont   | ents of FSF         | R to Add | ress Data Me | emory (not | a physica  | l register) |       | xxxx xxxx                                    | 19                  |

| 01h                | TMR0     | 8-bit Real- | Time Clock          | /Counter | r            |            |            |             |       | xxxx xxxx                                    | 23, 27              |

| 02h <sup>(1)</sup> | PCL      | Low-order   | 8 bits of PC        | )        |              |            |            |             |       | 1111 1111                                    | 18                  |

| 03h                | STATUS   | GPWUF       | CWUF <sup>(5)</sup> | _        | TO           | PD         | Z          | DC          | С     | 00-1 1xxx <b>(3)</b>                         | 15                  |

| 04h                | FSR      | Indirect Da | ata Memory          | Address  | s Pointer    |            |            |             |       | 111x xxxx                                    | 19                  |

| 05h                | OSCCAL   | CAL6        | CAL5                | CAL4     | CAL3         | CAL2       | CAL1       | CAL0        | FOSC4 | 1111 1110                                    | 17                  |

| 06h                | GPIO     | _           | _                   | _        | _            | GP3        | GP2        | GP1         | GP0   | xxxx                                         | 20                  |

| 07h <sup>(4)</sup> | CMCON0   | CMPOUT      | COUTEN              | POL      | CMPT0CS      | CMPON      | CNREF      | CPREF       | CWU   | 1111 1111                                    | 28                  |

| N/A                | TRISGPIO | —           |                     | —        | —            | I/O Contro | ol Registe | r           |       | 1111                                         | 31                  |

| N/A                | OPTION   | GPWU        | GPPU                | TOCS     | T0SE         | PSA        | PS2        | PS1         | PS0   | 1111 1111                                    | 16                  |

**Legend:** -= unimplemented, read as '0', x = unknown, u = unchanged, q = value depends on condition.

**Note 1:** The upper byte of the Program Counter is not directly accessible. See **Section 4.7** "**Program Counter**" for an explanation of how to access these bits.

2: Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

**3:** See Table 9-1 for other Reset specific values.

4: PIC10F204/206 only.

5: PIC10F204/206 only. On all other devices, this bit is reserved and should not be used.

### 4.6 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal precision 4 MHz oscillator. It contains seven bits for calibration.

| Note: | Erasing the device will also erase the       |

|-------|----------------------------------------------|

|       | pre-programmed internal calibration value    |

|       | for the internal oscillator. The calibration |

|       | value must be read prior to erasing the      |

|       | part so it can be reprogrammed correctly     |

|       | later.                                       |

After you move in the calibration constant, do not change the value. See Section 9.2.2 "Internal 4 MHz Oscillator".

#### **REGISTER 4-3: OSCCAL REGISTER**

| R/W-1 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | FOSC4 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-1 | CAL<6:0>: Oscillator Calibration bits            |

|---------|--------------------------------------------------|

|         | 0111111 = Maximum frequency                      |

|         | •                                                |

|         | •                                                |

|         | •                                                |

|         | 000001                                           |

|         | 0000000 = Center frequency                       |

|         | 1111111                                          |

|         | •                                                |

|         | •                                                |

|         | •                                                |

|         | 1000000 = Minimum frequency                      |

| bit 0   | FOSC4: INTOSC/4 Output Enable bit <sup>(1)</sup> |

|         | 1 = INTOSC/4 output onto GP2                     |

|         | 0 = GP2/T0CKI/COUT applied to GP2                |

|         |                                                  |

Note 1: Overrides GP2/T0CKI/COUT control registers when enabled.

## 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

#### 5.1 GPIO

GPIO is an 8-bit I/O register. Only the low-order 4 bits are used (GP<3:0>). Bits 7 through 4 are unimplemented and read as '0's. Please note that GP3 is an input-only pin. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are <u>not pin</u> selectable. If GP3/MCLR is configured as MCLR, weak pull-up is always on and wake-up on change for this pin is not enabled.

#### 5.2 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input-only and the GP2/TOCKI/COUT/FOSC4 pin, which may be controlled by various registers. See Table 5-1.

**Note:** A read of the ports reads the pins, not the output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is low.

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

## TABLE 5-1:ORDER OF PRECEDENCEFOR PIN FUNCTIONS

| Priority | GP0       | GP1       | GP2          | GP3    |

|----------|-----------|-----------|--------------|--------|

| 1        | CIN+      | CIN-      | FOSC4        | I/MCLR |

| 2        | TRIS GPIO | TRIS GPIO | COUT         | —      |

| 3        |           | —         | <b>T0CKI</b> | _      |

| 4        | _         | _         | TRIS GPIO    | _      |

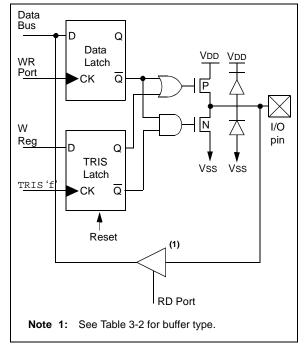

#### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3 which is inputonly, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

#### PIC10F200/202/204/206 EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

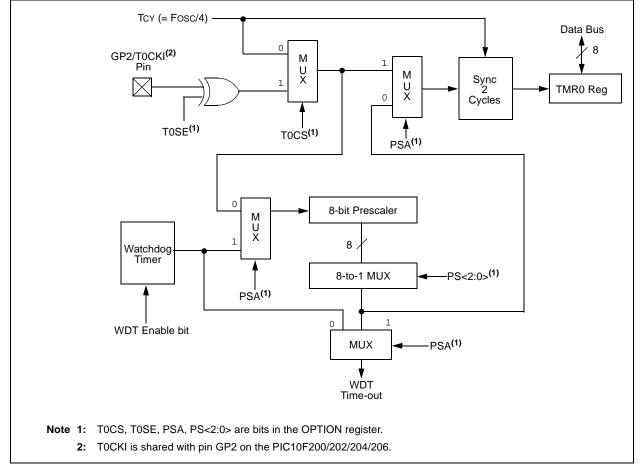

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        |            | · ·                 |

|--------|------------|---------------------|

| CLRWDT |            | ;Clear WDT and      |

|        |            | ;prescaler          |

| MOVLW  | 'xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

|        |            |                     |

### FIGURE 6-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

#### FIGURE 7-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| (Program<br>Counter)              | ( PC – 1 )   | PC         | ( PC + 1 )                        | Q1 Q2 Q3 Q4            | (PC + 3)    | ( PC + 4 )             | ( PC+5 )                               | PC + 6      |

|-----------------------------------|--------------|------------|-----------------------------------|------------------------|-------------|------------------------|----------------------------------------|-------------|

| Instruction<br>Fetch              | //<br>!<br>! | MOVWF TMR0 | MOVF TMR0,W                       | MOVF TMR0,W            | MOVF TMR0,W | MOVF TMR0,W            | MOVF TMR0,W                            | i<br>1<br>1 |

| Timer0<br>Instruction<br>Executed | ( <u>T0)</u> | Τ0 + 1 )   | T0 + 2)<br>Write TMR0<br>executed | Read TMR0<br>reads NT0 | NT0         | Read TMR0<br>reads NT0 | NT0 + 1)<br>Read TMR0<br>reads NT0 + 1 | NT0 + 2     |

#### FIGURE 7-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

| PC<br>(Program<br>Counter) | PC - 1 |             | $\frac{1}{\sqrt{\frac{PC+1}{PC+1}}}$ | Q1 Q2 Q3 Q4<br>(PC + 2) | Q1 Q2 Q3 Q4<br>(PC + 3) | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4<br>PC + 6 |

|----------------------------|--------|-------------|--------------------------------------|-------------------------|-------------------------|-------------|-------------|-----------------------|

| Instruction<br>Fetch       |        | MOVWF TMR0  | MOVF TMR0,W                          | MOVF TMR0,W             | MOVF TMR0,W             | MOVF TMR0,W | MOVF TMR0,W |                       |

| Timer0                     | (то )  | T0 + 1      |                                      |                         | NT0                     | 1<br>       |             | NT0 + 1               |

| Instruction<br>Executed    |        | 1<br>1<br>1 | Write TMR0                           | Read TMR0               | Read TMR0               | Read TMR0   | Read TMR0   | Read TMR0             |

#### **TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0**

| Address | Name        | Bit 7       | Bit 6                                | Bit 5 | Bit 4   | Bit 3      | Bit 2      | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------|-------------|--------------------------------------|-------|---------|------------|------------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0        | Timer0 – 8- | mer0 – 8-bit Real-Time Clock/Counter |       |         |            |            |       |       | XXXX XXXX                     | uuuu uuuu                       |

| 07h     | CMCON0      | CMPOUT      | COUTEN                               | POL   | CMPT0CS | CMPON      | CNREF      | CPREF | CWU   | 1111 1111                     | uuuu uuuu                       |

| N/A     | OPTION      | GPWU        | GPPU                                 | TOCS  | T0SE    | PSA        | PS2        | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRISGPIO(1) |             | _                                    |       | _       | I/O Contro | ol Registe | r     |       | 1111                          | 1111                            |

Legend: Shaded cells not used by Timer0. – = unimplemented, The TRIS of the T0CKI pin is overridden when T0CS = 1. Note 1:

#### 7.1 Using Timer0 with an External Clock (PIC10F204/206)

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.1.1 EXTERNAL CLOCK **SYNCHRONIZATION**

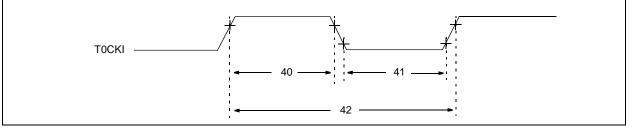

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of an external clock with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-4). Therefore, it is necessary for TOCKI or the comparator output to be high for at least 2 Tosc (and a

x = unknown.u = unchanged.

small RC delay of 2 Tt0H) and low for at least 2 Tosc (and a small RC delay of 2 Tt0H). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T0CKI or the comparator output to have a period of at least 4 Tosc (and a small RC delay of 4 Tt0H) divided by the prescaler value. The only requirement on TOCKI or the comparator output high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 8.0 COMPARATOR MODULE

The comparator module contains one Analog comparator. The inputs to the comparator are multiplexed with GP0 and GP1 pins. The output of the comparator can be placed on GP2.

The CMCON0 register, shown in Register 8-1, controls the comparator operation. A block diagram of the comparator is shown in Figure 8-1.

#### REGISTER 8-1: CMCON0 REGISTER

| R-1    | R/W-1  | R/W-1 | R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|---------|-------|-------|-------|-------|

| CMPOUT | COUTEN | POL   | CMPT0CS | CMPON | CNREF | CPREF | CWU   |

| bit 7  |        |       |         |       |       |       | bit 0 |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

| ł | oit 7         | CMPOUT: Comparator Output bit                                                                                          |

|---|---------------|------------------------------------------------------------------------------------------------------------------------|

|   |               | 1 = VIN + > VIN-                                                                                                       |

|   |               | 0 = VIN + < VIN - (4.2)                                                                                                |

| ł | oit 6         | <b>COUTEN:</b> Comparator Output Enable bit <sup>(1, 2)</sup>                                                          |

|   |               | 1 = Output of comparator is NOT placed on the COUT pin                                                                 |

|   |               | 0 = Output of comparator is placed in the COUT pin                                                                     |

| 1 | oit 5         | POL: Comparator Output Polarity bit <sup>(2)</sup>                                                                     |

|   |               | <ul> <li>1 = Output of comparator not inverted</li> <li>0 = Output of comparator inverted</li> </ul>                   |

|   | oit 4         | CMPT0CS: Comparator TMR0 Clock Source bit <sup>(2)</sup>                                                               |

|   | JIL 4         | 1 = TMR0 clock source selected by T0CS control bit                                                                     |

|   |               | 0 = Comparator output used as TMR0 clock source                                                                        |

| ł | oit 3         | CMPON: Comparator Enable bit                                                                                           |

|   |               | 1 = Comparator is on                                                                                                   |

|   |               | 0 = Comparator is off                                                                                                  |

| ł | oit 2         | CNREF: Comparator Negative Reference Select bit <sup>(2)</sup>                                                         |

|   |               | 1 = CIN- pin <sup>(3)</sup>                                                                                            |

|   |               | 0 = Internal voltage reference                                                                                         |

| ł | oit 1         | <b>CPREF:</b> Comparator Positive Reference Select bit <sup>(2)</sup>                                                  |

|   |               | $1 = \text{CIN} + \text{pin}^{(3)}$                                                                                    |

|   |               | $0 = \text{CIN-pin}^{(3)}$                                                                                             |

| 1 | oit 0         | <b>CWU:</b> Comparator Wake-up on Change Enable bit <sup>(2)</sup>                                                     |

|   |               | <ul> <li>1 = Wake-up on comparator change is disabled</li> <li>0 = Wake-up on comparator change is enabled.</li> </ul> |

|   | Note 1:       | Overrides T0CS bit for TRIS control of GP2.                                                                            |

|   | 101e 1.<br>2: | When the comparator is turned on, these control bits assert themselves. When the comparator is off, these              |

|   | ۷.            | bits have no effect on the device operation and the other control registers have precedence.                           |

|   | 3:            | PIC10F204/206 only.                                                                                                    |

**3:** PIC10F204/206 only.

#### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC10F200/202/204/206 devices are offered with Internal Oscillator mode only.

• INTOSC: Internal 4 MHz Oscillator

#### 9.2.2 INTERNAL 4 MHz OSCILLATOR

The internal oscillator provides a 4 MHz (nominal) system clock (see **Section 12.0 "Electrical Characteristics"** for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal oscillator. This location is always uncode protected, regardless of the codeprotect settings. This value is programmed as a MOVLW xx instruction where xx is the calibration value and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

| Note: | Erasing the device will also erase the pre- |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|

|       | programmed internal calibration value for   |  |  |  |  |  |  |

|       | the internal oscillator. The calibration    |  |  |  |  |  |  |

|       | value must be read prior to erasing the     |  |  |  |  |  |  |

|       | part so it can be reprogrammed correctly    |  |  |  |  |  |  |

|       | later.                                      |  |  |  |  |  |  |

#### 9.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- · WDT time-out Reset during normal operation

- WDT time-out Reset during Sleep

- · Wake-up from Sleep on pin change

- · Wake-up from Sleep on comparator change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD, GPWUF and CWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 9-1 for a full description of Reset states of all registers.

| Register              | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change, Wake on<br>Comparator Change |

|-----------------------|---------|--------------------------|----------------------------------------------------------------------------------|

| W                     | _       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                                                         |

| INDF                  | 00h     | XXXX XXXX                | uuuu uuuu                                                                        |

| TMR0                  | 01h     | XXXX XXXX                | uuuu uuuu                                                                        |

| PCL                   | 02h     | 1111 1111                | 1111 1111                                                                        |

| STATUS                | 03h     | 00-1 1xxx                | q00q quuu <b>(2)</b>                                                             |

| STATUS <sup>(3)</sup> | 03h     | 00-1 1xxx                | qq0q quuu <b>(2)</b>                                                             |

| FSR                   | 04h     | 111x xxxx                | 111u uuuu                                                                        |

| OSCCAL                | 05h     | 1111 1110                | uuuu uuuu                                                                        |

| GPIO                  | 06h     | xxxx                     | uuuu                                                                             |

| CMCON <sup>(3)</sup>  | 07h     | 1111 1111                | սսսս սսսս                                                                        |

| OPTION                | _       | 1111 1111                | 1111 1111                                                                        |

| TRISGPIO              | —       | 1111                     | 1111                                                                             |

#### TABLE 9-1: RESET CONDITIONS FOR REGISTERS – PIC10F200/202/204/206

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

**2:** See Table 9-2 for Reset value for specific conditions.

3: PIC10F204/206 only.

| Mnem   | onic, | Description                                       | Cycles           | 12-1   | Bit Opc | ode  | Status   | Notes   |

|--------|-------|---------------------------------------------------|------------------|--------|---------|------|----------|---------|

| Opera  | ands  | Description                                       | Cycles           | MSb    |         | LSb  | Affected | Notes   |

| ADDWF  | f, d  | Add W and f                                       | 1                | 0001   | 11df    | ffff | C, DC, Z | 1, 2, 4 |

| ANDWF  | f, d  | AND W with f                                      | 1                | 0001   | 01df    | ffff | Z        | 2, 4    |

| CLRF   | f     | Clear f                                           | 1                | 0000   | 011f    | ffff | Z        | 4       |

| CLRW   | —     | Clear W                                           | 1                | 0000   | 0100    | 0000 | Z        |         |

| COMF   | f, d  | Complement f                                      | 1                | 0010   | 01df    | ffff | Z        |         |

| DECF   | f, d  | Decrement f                                       | 1                | 0000   | 11df    | ffff | Z        | 2, 4    |

| DECFSZ | f, d  | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010   | 11df    | ffff | None     | 2, 4    |

| INCF   | f, d  | Increment f                                       | 1                | 0010   | 10df    | ffff | Z        | 2, 4    |

| INCFSZ | f, d  | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011   | 11df    | ffff | None     | 2, 4    |

| IORWF  | f, d  | Inclusive OR W with f                             | 1                | 0001   | 00df    | ffff | Z        | 2, 4    |

| MOVF   | f, d  | Move f                                            | 1                | 0010   | 00df    | ffff | Z        | 2, 4    |

| MOVWF  | f     | Move W to f                                       | 1                | 0000   | 001f    | ffff | None     | 1, 4    |

| NOP    | _     | No Operation                                      | 1                | 0000   | 0000    | 0000 | None     |         |

| RLF    | f, d  | Rotate left f through Carry                       | 1                | 0011   | 01df    | ffff | С        | 2, 4    |

| RRF    | f, d  | Rotate right f through Carry                      | 1                | 0011   | 00df    | ffff | С        | 2, 4    |

| SUBWF  | f, d  | Subtract W from f                                 | 1                | 0000   | 10df    | ffff | C, DC, Z | 1, 2, 4 |

| SWAPF  | f, d  | Swap f                                            | 1                | 0011   | 10df    | ffff | None     | 2, 4    |

| XORWF  | f, d  | Exclusive OR W with f                             | 1                | 0001   | 10df    | ffff | Z        | 2, 4    |

|        |       | BIT-ORIENTED FILE REGISTE                         |                  | ATIONS |         |      |          |         |

| BCF    | f, b  | Bit Clear f                                       | 1                | 0100   | bbbf    | ffff | None     | 2, 4    |

| BSF    | f, b  | Bit Set f                                         | 1                | 0101   | bbbf    | ffff | None     | 2, 4    |

| BTFSC  | f, b  | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110   | bbbf    | ffff | None     |         |

| BTFSS  | f, b  | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111   | bbbf    | ffff | None     |         |

|        |       | LITERAL AND CONTROL C                             | PERATIO          | ONS    |         |      |          |         |

| ANDLW  | k     | AND literal with W                                | 1                | 1110   | kkkk    | kkkk | Z        |         |

| CALL   | k     | Call Subroutine                                   | 2                | 1001   | kkkk    | kkkk | None     | 1       |

| CLRWDT |       | Clear Watchdog Timer                              | 1                | 0000   | 0000    | 0100 | TO, PD   |         |

| GOTO   | k     | Unconditional branch                              | 2                | 101k   | kkkk    | kkkk | None     |         |

| IORLW  | k     | Inclusive OR literal with W                       | 1                | 1101   | kkkk    | kkkk | Z        |         |

| MOVLW  | k     | Move literal to W                                 | 1                | 1100   | kkkk    | kkkk | None     |         |

| OPTION | _     | Load OPTION register                              | 1                | 0000   | 0000    | 0010 | None     |         |

| RETLW  | k     | Return, place Literal in W                        | 2                | 1000   | kkkk    | kkkk | None     |         |

| SLEEP  | _     | Go into Standby mode                              | 1                | 0000   | 0000    | 0011 | TO, PD   |         |

| TRIS   | f     | Load TRIS register                                | 1                | 0000   | 0000    | 0fff | None     | 3       |

| XORLW  | k     | Exclusive OR literal to W                         | 1                |        | kkkk    |      | Z        | -       |

| Note 1 |       | it of the program counter will be forced to a fai |                  |        |         |      |          |         |

#### TABLE 10-2: INSTRUCTION SET SUMMARY

**Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. See Section 4.7 "Program Counter".

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

**4:** If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

## 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 11.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- Simultaneous debugging sessions

File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

| AC CHARACTERISTICS |      |                                                          | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial),} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in} \\ \mbox{Section 12.1 "DC Characteristics: PIC10F200/202/204/206} \\ \mbox{(Industrial)"} \end{array} $ |              |              |              |            |                                                                                                                                                                                     |

|--------------------|------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Sym. | Characteristic                                           | Freq.<br>Tolerance                                                                                                                                                                                                                                                                                                                                                                                                 | Min.         | Тур.†        | Max.         | Units      | Conditions                                                                                                                                                                          |

| F10                | Fosc | Internal Calibrated<br>INTOSC Frequency <sup>(1,2)</sup> | ± 1%<br>± 2%                                                                                                                                                                                                                                                                                                                                                                                                       | 3.96<br>3.92 | 4.00<br>4.00 | 4.04<br>4.08 | MHz<br>MHz | VDD=3.5V @ 25°C<br>2.5V $\leq$ VDD $\leq$ 5.5V<br>0°C $\leq$ TA $\leq$ +85°C (industrial)                                                                                           |

|                    |      |                                                          | ± 5%                                                                                                                                                                                                                                                                                                                                                                                                               | 3.80         | 4.00         | 4.20         | MHz        | $\begin{array}{l} 2.0V \leq VDD \leq 5.5V \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ (industrial)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ (extended)} \end{array}$ |

#### TABLE 12-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC10F200/202/204/206

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

2: Under stable VDD conditions.

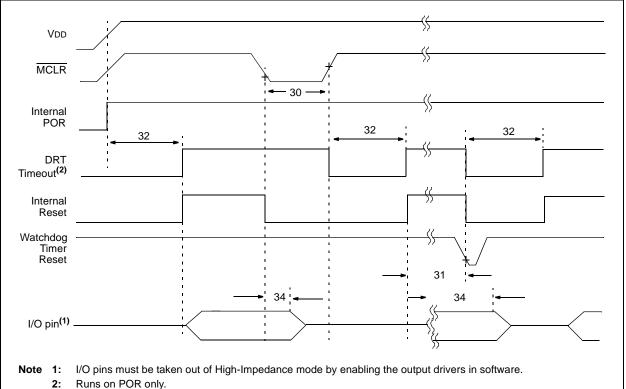

#### FIGURE 12-3: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER TIMING – PIC10F200/202/204/206

#### TABLE 12-4: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER – PIC10F200/202/204/206

| AC CHARACTERISTICS                |                  |                                                  | $eq:standard operating Conditions (unless otherwise specified Operating Temperature -40°C \leq TA \leq +85°C (industrial) -40°C \leq TA \leq +125°C (extended) Operating Voltage VDD range is described in Section 12.1 "DC Characteristics: PIC10F200/202/204/206 (Industrial)"$ |                     |          |          |                                                  |

|-----------------------------------|------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|----------|--------------------------------------------------|

| Param.<br>No. Sym. Characteristic |                  |                                                  | Min.                                                                                                                                                                                                                                                                              | Тур. <sup>(1)</sup> | Max.     | Units    | Conditions                                       |

| 30                                | Тмс <sub>L</sub> | MCLR Pulse Width (low)                           | 2*<br>5*                                                                                                                                                                                                                                                                          | _                   |          | μs<br>μs | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |

| 31                                | Twdt             | Watchdog Timer Time-out<br>Period (no prescaler) | 10<br>10                                                                                                                                                                                                                                                                          | 16<br>16            | 29<br>31 | ms<br>ms | VDD = 5.0V (industrial)<br>VDD = 5.0V (extended) |

| 32                                | Tdrt             | Device Reset Timer Period (standard)             | 10<br>10                                                                                                                                                                                                                                                                          | 16<br>16            | 29<br>31 | ms<br>ms | VDD = 5.0V (industrial)<br>VDD = 5.0V (extended) |

| 34                                | Tioz             | I/O High-impedance from MCLR low                 |                                                                                                                                                                                                                                                                                   | _                   | 2*       | μs       |                                                  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 12-4: TIMER0 CLOCK TIMINGS – PIC10F200/202/204/206

#### TABLE 12-5: TIMER0 CLOCK REQUIREMENTS - PIC10F200/202/204/206

| AC CHARACTERISTICS                |       |                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in} \\ \mbox{Section 12.1 "DC Characteristics: PIC10F200/202/204/206 (Industrial)"}. \end{array}$ |                                 |                     |      |       |                                                                |

|-----------------------------------|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------|------|-------|----------------------------------------------------------------|

| Param.<br>No. Sym. Characteristic |       |                  | eristic                                                                                                                                                                                                                                                                                                                                                                                            | Min.                            | Тур. <sup>(1)</sup> | Max. | Units | Conditions                                                     |

| 40                                | Tt0H  | T0CKI High Pulse | No Prescaler                                                                                                                                                                                                                                                                                                                                                                                       | 0.5 TCY + 20*                   | —                   | —    | ns    |                                                                |

|                                   |       | Width            | With Prescaler                                                                                                                                                                                                                                                                                                                                                                                     | 10*                             | —                   |      | ns    |                                                                |

| 41                                | Tt0L  | T0CKI Low Pulse  | No Prescaler                                                                                                                                                                                                                                                                                                                                                                                       | 0.5 TCY + 20*                   | —                   |      | ns    |                                                                |

|                                   | Width |                  | With Prescaler                                                                                                                                                                                                                                                                                                                                                                                     | 10*                             | —                   | _    | ns    |                                                                |

| 42                                | Tt0P  | T0CKI Period     |                                                                                                                                                                                                                                                                                                                                                                                                    | 20 or $\frac{T_{CY} + 40^*}{N}$ | —                   | —    | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

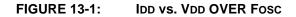

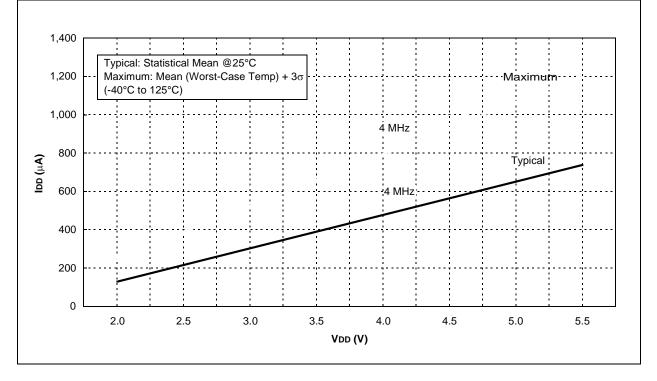

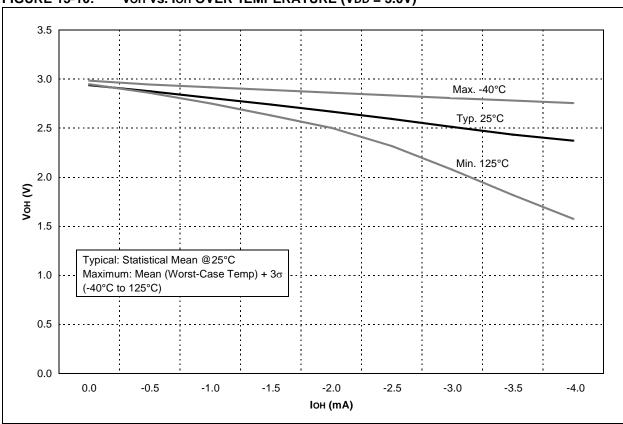

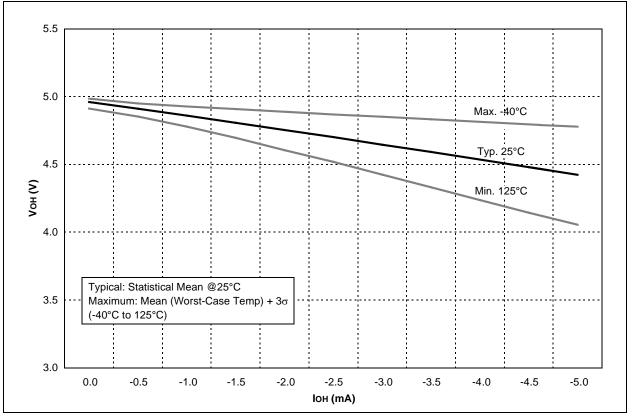

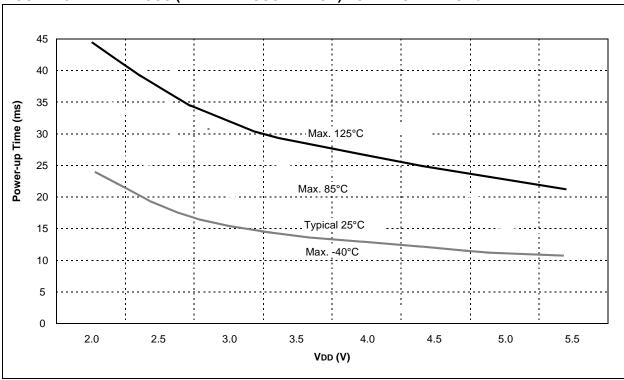

## 13.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

FIGURE 13-11: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V)

FIGURE 13-10: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

#### FIGURE 13-14: INTOSC (INTERNAL OSCILLATOR) POWER-UP TIMES vs. VDD

#### **Package Marking Information (Continued)**

8-Lead DFN (2x3x0.9 mm)

Example

| Legenc | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>(e3)<br>*                                                                                                                                                                | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Note:  | e: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

\* Standard PIC<sup>®</sup> device marking consists of Microchip part number, year code, week code, and traceability code. For PIC device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

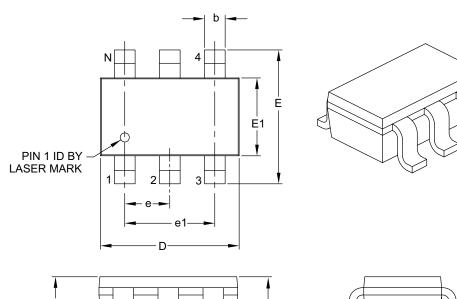

### 14.2 Package Details

The following sections give the technical details of the packages.

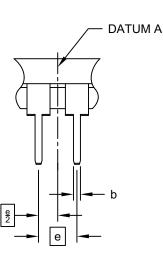

#### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |      |          | 6    |

|--------------------------|------------------|------|----------|------|

| ]                        | Dimension Limits | MIN  | NOM      | MAX  |

| Number of Pins           | N                |      | 6        |      |

| Pitch                    | е                |      | 0.95 BSC |      |

| Outside Lead Pitch       | e1               |      | 1.90 BSC |      |

| Overall Height           | А                | 0.90 | -        | 1.45 |

| Molded Package Thickness | A2               | 0.89 | -        | 1.30 |

| Standoff                 | A1               | 0.00 | -        | 0.15 |

| Overall Width            | E                | 2.20 | -        | 3.20 |

| Molded Package Width     | E1               | 1.30 | -        | 1.80 |

| Overall Length           | D                | 2.70 | -        | 3.10 |

| Foot Length              | L                | 0.10 | -        | 0.60 |

| Footprint                | L1               | 0.35 | -        | 0.80 |

| Foot Angle               | ¢                | 0°   | -        | 30°  |

| Lead Thickness           | С                | 0.08 | -        | 0.26 |

| Lead Width               | b                | 0.20 | -        | 0.51 |

#### Notes:

1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

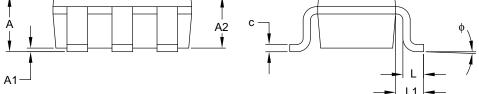

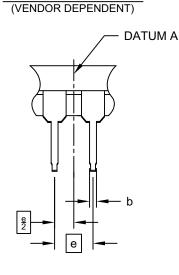

### 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

ALTERNATE LEAD DESIGN

|                            | INCHES |      |          |      |

|----------------------------|--------|------|----------|------|

| Dimension                  | MIN    | NOM  | MAX      |      |

| Number of Pins             | N      |      | 8        |      |

| Pitch                      | е      |      | .100 BSC |      |

| Top to Seating Plane       | Α      | -    | -        | .210 |

| Molded Package Thickness   | A2     | .115 | .130     | .195 |

| Base to Seating Plane      | A1     | .015 | -        | -    |

| Shoulder to Shoulder Width | E      | .290 | .310     | .325 |

| Molded Package Width       | E1     | .240 | .250     | .280 |

| Overall Length             | D      | .348 | .365     | .400 |

| Tip to Seating Plane       | L      | .115 | .130     | .150 |

| Lead Thickness             | С      | .008 | .010     | .015 |

| Upper Lead Width           | b1     | .040 | .060     | .070 |

| Lower Lead Width           | b      | .014 | .018     | .022 |

| Overall Row Spacing §      | eВ     | -    | -        | .430 |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-018D Sheet 2 of 2

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

03/25/14