#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 3                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 24 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f202-e-mc |

|                            |                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | General Description                               | 4  |

|-------|---------------------------------------------------|----|

| 2.0   | PIC10F200/202/204/206 Device Varieties            | 5  |

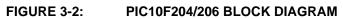

| 3.0   | Architectural Overview                            | 6  |

| 4.0   | Memory Organization                               | 11 |

| 5.0   | I/O Port                                          | 20 |

| 6.0   | Timer0 Module and TMR0 Register (PIC10F200/202)   | 23 |

| 7.0   | Timer() Module and TMR0 Register (PIC10F204/206). | 27 |

| 8.0   | Comparator Module                                 | 31 |

| 9.0   | Special Features of the CPU                       | 35 |

| 10.0  | Instruction Set Summary                           | 45 |

| 11.0  | Development Support Electrical Characteristics    | 53 |

| 12.0  | Electrical Characteristics                        | 57 |

| 13.0  | DC and AC Characteristics Graphs and Tables       | 67 |

| 14.0  | Packaging Information                             | 75 |

| The N | Iicrochip Web Site                                | 85 |

| Custo | mer Change Notification Service                   | 85 |

| Custo | mer Support<br>ict Identification System          | 85 |

| Produ | ct Identification System                          | 86 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

· Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# PIC10F200/202/204/206

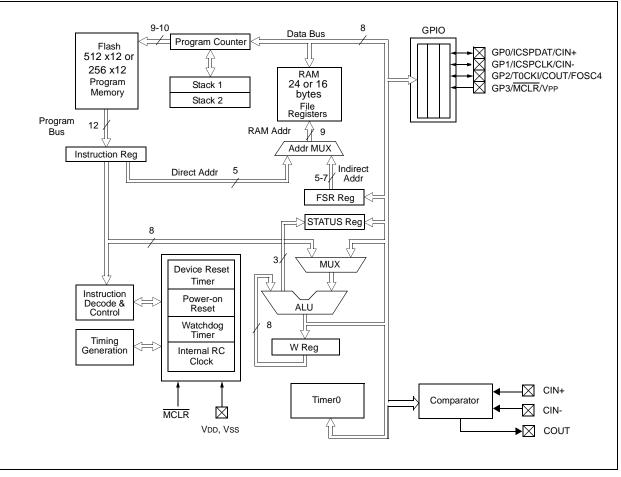

# 4.2 Program Memory Organization for the PIC10F202/206

The PIC10F202/206 devices have a 10-bit Program Counter (PC) capable of addressing a 1024 x 12 program memory space.

Only the first  $512 \times 12$  (0000h-01FFh) for the PIC10F202/206 are physically implemented (see Figure 4-2). Accessing a location above these boundaries will cause a wraparound within the first  $512 \times 12$  space (PIC10F202/206). The effective Reset vector is at 0000h (see Figure 4-2). Location 01FFh (PIC10F202/206) contains the internal clock oscillator calibration value. This value should never be overwritten.

## FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC10F202/206

# 4.3 Data Memory Organization

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers include the TMR0 register, the Program Counter (PCL), the STATUS register, the I/O register (GPIO) and the File Select Register (FSR). In addition, Special Function Registers are used to control the I/O port configuration and prescaler options.

The General Purpose registers are used for data and control information under command of the instructions.

For the PIC10F200/204, the register file is composed of seven Special Function registers and 16 General Purpose registers (see Figure 4-3 and Figure 4-4).

For the PIC10F202/206, the register file is composed of eight Special Function registers and 24 General Purpose registers (see Figure 4-4).

## 4.3.1 GENERAL PURPOSE REGISTER FILE

The General Purpose Register file is accessed, either directly or indirectly, through the File Select Register (FSR). See Section 4.9 "Indirect Data Addressing: INDF and FSR Registers".

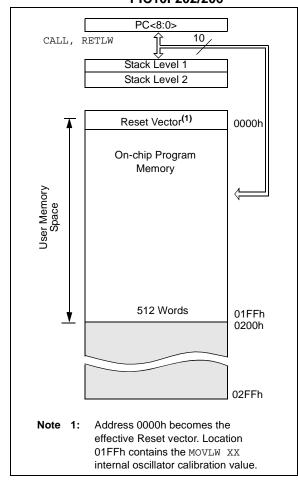

## 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

3: The arrows indicate the points in time where sampling occurs.

## 6.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see **Section 9.6** "**Watchdog Timer (WDT)**"). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |

|-------|-----------------------------------------|

|       | Timer0 module or the WDT, but not both. |

|       | Thus, a prescaler assignment for the    |

|       | Timer0 module means that there is no    |

|       | prescaler for the WDT and vice versa.   |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

## 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

| EXAMP  | PLE 6-1:             | CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT) |

|--------|----------------------|-----------------------------------------------|

| CLRWDT |                      | ;Clear WDT                                    |

| CLRF   | TMR0                 | ;Clear TMR0 & Prescaler                       |

| MOVLW  | `00xx1111 <i>'</i> b | ;These 3 lines (5, 6, 7)                      |

| OPTION |                      | ;are required only if                         |

|        |                      | ;desired                                      |

| CLRWDT |                      | ;PS<2:0> are 000 or 001                       |

| MOVLW  | `00xx1xxx'b          | ;Set Postscaler to                            |

| OPTION |                      | ;desired WDT rate                             |

# 8.0 COMPARATOR MODULE

The comparator module contains one Analog comparator. The inputs to the comparator are multiplexed with GP0 and GP1 pins. The output of the comparator can be placed on GP2.

The CMCON0 register, shown in Register 8-1, controls the comparator operation. A block diagram of the comparator is shown in Figure 8-1.

## REGISTER 8-1: CMCON0 REGISTER

| R-1         | R/W-1  | R/W-1 | R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------|--------|-------|---------|-------|-------|-------|-------|

| CMPOUT      | COUTEN | POL   | CMPT0CS | CMPON | CNREF | CPREF | CWU   |

| bit 7 bit 0 |        |       |         |       |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| I | oit 7         | CMPOUT: Comparator Output bit                                                                                          |

|---|---------------|------------------------------------------------------------------------------------------------------------------------|

|   |               | 1 = VIN + > VIN-                                                                                                       |

|   |               | 0 = VIN + < VIN - (4.2)                                                                                                |

| I | oit 6         | <b>COUTEN:</b> Comparator Output Enable bit <sup>(1, 2)</sup>                                                          |

|   |               | 1 = Output of comparator is NOT placed on the COUT pin                                                                 |

|   |               | 0 = Output of comparator is placed in the COUT pin                                                                     |

| 1 | oit 5         | POL: Comparator Output Polarity bit <sup>(2)</sup>                                                                     |

|   |               | <ul> <li>1 = Output of comparator not inverted</li> <li>0 = Output of comparator inverted</li> </ul>                   |

|   | oit 4         | CMPT0CS: Comparator TMR0 Clock Source bit <sup>(2)</sup>                                                               |

| 1 | JIL 4         | 1 = TMR0 clock source selected by T0CS control bit                                                                     |

|   |               | 0 = Comparator output used as TMR0 clock source                                                                        |

| I | oit 3         | CMPON: Comparator Enable bit                                                                                           |

|   |               | 1 = Comparator is on                                                                                                   |

|   |               | 0 = Comparator is off                                                                                                  |

| I | oit 2         | CNREF: Comparator Negative Reference Select bit <sup>(2)</sup>                                                         |

|   |               | 1 = CIN- pin <sup>(3)</sup>                                                                                            |

|   |               | 0 = Internal voltage reference                                                                                         |

| I | oit 1         | <b>CPREF:</b> Comparator Positive Reference Select bit <sup>(2)</sup>                                                  |

|   |               | $1 = \text{CIN} + \text{pin}^{(3)}$                                                                                    |

|   |               | $0 = \text{CIN-pin}^{(3)}$                                                                                             |

| 1 | oit 0         | <b>CWU:</b> Comparator Wake-up on Change Enable bit <sup>(2)</sup>                                                     |

|   |               | <ul> <li>1 = Wake-up on comparator change is disabled</li> <li>0 = Wake-up on comparator change is enabled.</li> </ul> |

| 1 | Note 1:       | Overrides T0CS bit for TRIS control of GP2.                                                                            |

|   | 101e 1.<br>2: | When the comparator is turned on, these control bits assert themselves. When the comparator is off, these              |

|   | ۷.            | bits have no effect on the device operation and the other control registers have precedence.                           |

|   | 3:            | PIC10F204/206 only.                                                                                                    |

**3:** PIC10F204/206 only.

# 8.2 Comparator Operation

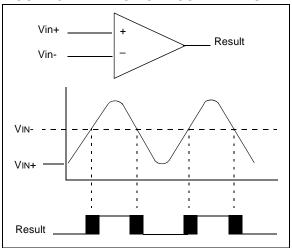

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time. See Table 12-1 for Common Mode Voltage.

FIGURE 8-2: SINGLE COMPARATOR

# 8.3 Comparator Reference

An internal reference signal may be used depending on the Comparator Operating mode. The analog signal that is present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 8-2). Please see Table 12-1 for internal reference specifications.

# 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is to have a valid level. If the comparator inputs are changed, a delay must be used to allow the comparator to settle to its new state. Please see Table 12-1 for comparator response time specifications.

## 8.5 Comparator Output

The comparator output is read through CMCON0 register. This bit is read-only. The comparator output may also be used internally, see Figure 8-1.

| Note: | Analog levels on any pin that is defined as a digital input may cause the input buffer |  |  |  |      |    |

|-------|----------------------------------------------------------------------------------------|--|--|--|------|----|

|       | to consume more current tha specified.                                                 |  |  |  | than | is |

## 8.6 Comparator Wake-up Flag

The comparator wake-up flag is set whenever all of the following conditions are met:

- $\overline{\text{CWU}} = 0$  (CMCON0<0>)

- CMCON0 has been read to latch the last known state of the CMPOUT bit (MOVF CMCON0, W)

- Device is in Sleep

- The output of the comparator has changed state

The wake-up flag may be cleared in software or by another device Reset.

# 8.7 Comparator Operation During Sleep

When the comparator is active and the device is placed in Sleep mode, the comparator remains active. While the comparator is powered-up, higher Sleep currents than shown in the power-down current specification will occur. To minimize power consumption while in Sleep mode, turn off the comparator before entering Sleep.

# 8.8 Effects of a Reset

A Power-on Reset (POR) forces the CMCON0 register to its Reset state. This forces the comparator module to be in the comparator Reset mode. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparator will be powered-down during the Reset interval.

# 8.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 8-3. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

# 9.2 Oscillator Configurations

## 9.2.1 OSCILLATOR TYPES

The PIC10F200/202/204/206 devices are offered with Internal Oscillator mode only.

• INTOSC: Internal 4 MHz Oscillator

## 9.2.2 INTERNAL 4 MHz OSCILLATOR

The internal oscillator provides a 4 MHz (nominal) system clock (see **Section 12.0 "Electrical Characteristics"** for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal oscillator. This location is always uncode protected, regardless of the codeprotect settings. This value is programmed as a MOVLW xx instruction where xx is the calibration value and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

| Note: | Erasing the device will also erase the pre- |  |  |

|-------|---------------------------------------------|--|--|

|       | programmed internal calibration value for   |  |  |

|       | the internal oscillator. The calibration    |  |  |

|       | value must be read prior to erasing the     |  |  |

|       | part so it can be reprogrammed correctly    |  |  |

|       | later.                                      |  |  |

## 9.3 Reset

The device differentiates between various kinds of Reset:

- Power-on Reset (POR)

- MCLR Reset during normal operation

- MCLR Reset during Sleep

- · WDT time-out Reset during normal operation

- WDT time-out Reset during Sleep

- · Wake-up from Sleep on pin change

- · Wake-up from Sleep on comparator change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are TO, PD, GPWUF and CWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 9-1 for a full description of Reset states of all registers.

| Register              | Address | Power-on Reset           | MCLR Reset, WDT Time-out,<br>Wake-up On Pin Change, Wake on<br>Comparator Change |

|-----------------------|---------|--------------------------|----------------------------------------------------------------------------------|

| W                     | _       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu(1)                                                                     |

| INDF                  | 00h     | XXXX XXXX                | uuuu uuuu                                                                        |

| TMR0                  | 01h     | XXXX XXXX                | uuuu uuuu                                                                        |

| PCL                   | 02h     | 1111 1111                | 1111 1111                                                                        |

| STATUS                | 03h     | 00-1 1xxx                | 9009 quuu <b>(2)</b>                                                             |

| STATUS <sup>(3)</sup> | 03h     | 00-1 1xxx                | qq0q quuu <b>(2)</b>                                                             |

| FSR                   | 04h     | 111x xxxx                | 111u uuuu                                                                        |

| OSCCAL                | 05h     | 1111 1110                | uuuu uuuu                                                                        |

| GPIO                  | 06h     | xxxx                     | uuuu                                                                             |

| CMCON <sup>(3)</sup>  | 07h     | 1111 1111                | uuuu uuuu                                                                        |

| OPTION                | _       | 1111 1111                | 1111 1111                                                                        |

| TRISGPIO              | —       | 1111                     | 1111                                                                             |

# TABLE 9-1: RESET CONDITIONS FOR REGISTERS – PIC10F200/202/204/206

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

**2:** See Table 9-2 for Reset value for specific conditions.

3: PIC10F204/206 only.

# 9.7 Time-out Sequence, Power-down and <u>Wake-up</u> from Sleep Status Bits (TO, PD, GPWUF, CWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , GPWUF and CWUF bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$ , Watchdog Timer (WDT) Reset, wake-up on comparator change or wake-up on pin change.

# TABLE 9-5: TO, PD, GPWUF, CWUF STATUS AFTER RESET

| CWUF | GPWUF | то | PD | Reset Caused By                         |

|------|-------|----|----|-----------------------------------------|

| 0    | 0     | 0  | 0  | WDT wake-up from Sleep                  |

| 0    | 0     | 0  | u  | WDT time-out (not from Sleep)           |

| 0    | 0     | 1  | 0  | MCLR wake-up from Sleep                 |

| 0    | 0     | 1  | 1  | Power-up                                |

| 0    | 0     | u  | u  | MCLR not during Sleep                   |

| 0    | 1     | 1  | 0  | Wake-up from Sleep on pin change        |

| 1    | 0     | 1  | 0  | Wake-up from Sleep on comparator change |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: The TO, PD, GPWUF and CWUF bits maintain their status (u) until a Reset occurs. A low-pulse on the MCLR input does not change the TO, PD, GPWUF or CWUF Status bits.

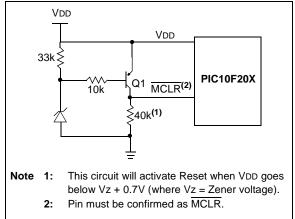

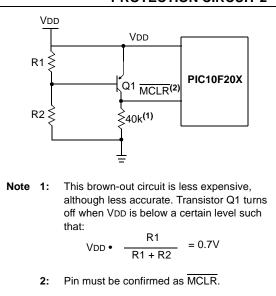

# 9.8 Reset on Brown-out

A Brown-out Reset is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC10F200/202/204/206 devices when a Brown-out Reset occurs, external brown-out protection circuits may be built, as shown in Figure 9-7 and Figure 9-8.

## FIGURE 9-7: BROWN-OUT PROTECTION CIRCUIT 1

## FIGURE 9-8: BROWN-OUT PROTECTION CIRCUIT 2

## 9.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (Reset vector) can be read, regardless of the code protection bit setting.

# 9.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify.

Use only the lower four bits of the ID locations and always program the upper eight bits as '0's.

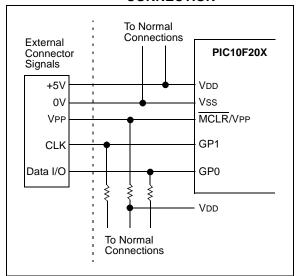

# 9.12 In-Circuit Serial Programming™

The PIC10F200/202/204/206 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1 becomes the programming clock and GP0 becomes the programming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 16 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC10F200/202/204/206 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-10.

## FIGURE 9-10:

## TYPICAL IN-CIRCUIT SERIAL PROGRAMMING™ CONNECTION

# PIC10F200/202/204/206

Increment f

INCF

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                    |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

Decrement f, Skip if 0 [label] DECFSZ f,d

(f)  $-1 \rightarrow d$ ; skip if result = 0

The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in

If the result is '0', the next instruction, which is already fetched, is

discarded and a NOP is executed

instead making it a 2-cycle instruc-

$0 \leq f \leq 31$

$d \in [0,1]$

register 'f'.

tion.

None

DECFSZ

Operands:

Operation:

Description:

Status Affected:

Syntax:

| Syntax:          | [label] INCF f,d                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.                                        |  |  |  |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', then the next |  |  |  |  |  |  |  |  |

If the result is '0', then the next instruction, which is already fetched, is discarded and a NOP is executed instead making it a 2-cycle instruction.

| GOTO             | Unconditional Branch                                                                                                                                                                     |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 511$                                                                                                                                                                        |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<8:0>;$<br>STATUS<6:5> $\rightarrow PC<10:9>$                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a 2-cycle<br>instruction. |  |  |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                            |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                               |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |  |

## 11.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 11.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 12.2 DC Characteristics: PIC10F200/202/204/206 (Extended)

| DC CHARACTERISTICS |      |                                               |       | Standard Operating Conditions (unless otherwise specified)Operating Temperature -40°C $\leq$ TA $\leq$ +125°C (extended) |            |          |                          |  |  |  |

|--------------------|------|-----------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------|------------|----------|--------------------------|--|--|--|

| Param.<br>No. Sym. |      | Characteristic                                | Min.  | Тур. <sup>(1)</sup>                                                                                                      | Max.       | Units    | Conditions               |  |  |  |

| D001               | Vdd  | Supply Voltage                                | 2.0   |                                                                                                                          | 5.5        | V        | See Figure 12-1          |  |  |  |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | 1.5*  |                                                                                                                          | —          | V        | Device in Sleep mode     |  |  |  |

| D003               | VPOR | VDD Start Voltage<br>to ensure Power-on Reset | —     | Vss                                                                                                                      | —          | V        |                          |  |  |  |

| D004               | SVDD | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05* | —                                                                                                                        | —          | V/ms     |                          |  |  |  |

|                    | IDD  | Supply Current <sup>(3)</sup>                 |       |                                                                                                                          |            |          |                          |  |  |  |

| D010               |      |                                               | _     | 175<br>0.63                                                                                                              | 275<br>1.1 | μA<br>mA | VDD = 2.0V<br>VDD = 5.0V |  |  |  |

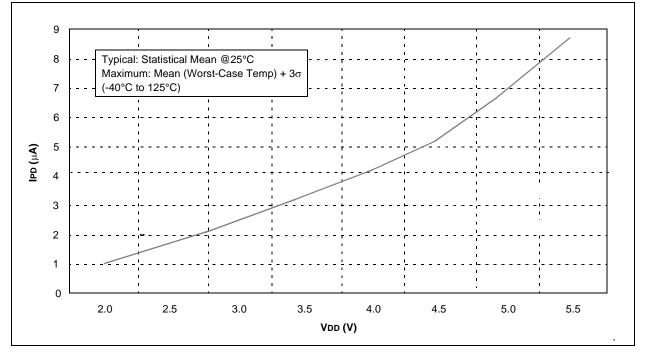

|                    | IPD  | Power-down Current <sup>(4)</sup>             |       |                                                                                                                          |            |          |                          |  |  |  |

| D020               |      |                                               | _     | 0.1<br>0.35                                                                                                              | 9<br>15    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |

|                    | IWDT | WDT Current <sup>(5)</sup>                    |       |                                                                                                                          |            |          |                          |  |  |  |

| D022               |      |                                               | _     | 1.0<br>7                                                                                                                 | 18<br>22   | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |

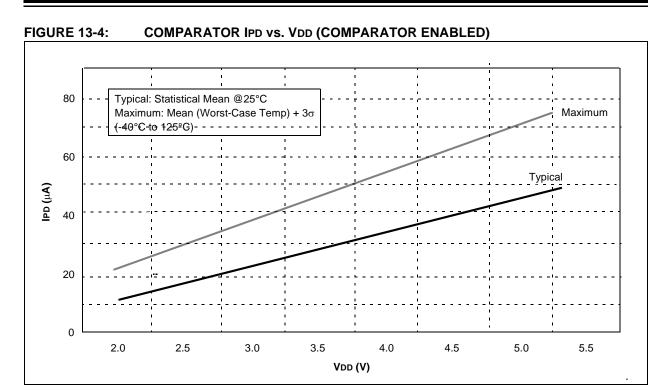

|                    | ICMP | Comparator Current <sup>(5)</sup>             |       | 1                                                                                                                        |            | 1        |                          |  |  |  |

| D023               |      |                                               | _     | 12<br>42                                                                                                                 | 27<br>85   | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |

|                    | VREF | Internal Reference Current <sup>(5,6</sup>    | 6)    |                                                                                                                          |            |          |                          |  |  |  |

| D024               |      |                                               | —     | 85<br>175                                                                                                                | 120<br>200 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are: All I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

- 4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS.

- **5:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled.

- 6: Measured with the Comparator enabled.

## 12.3 DC Characteristics: PIC10F200/202/204/206 (Industrial, Extended)

| DC CHA        | RACT | ERISTICS                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |             |       |                                                |  |  |  |  |

|---------------|------|---------------------------------------------|------------------------------------------------------|-------|-------------|-------|------------------------------------------------|--|--|--|--|

| Param.<br>No. | Sym. | Characteristic                              | Min.                                                 | Тур.† | Max.        | Units | Conditions                                     |  |  |  |  |

|               | VIL  | Input Low Voltage                           |                                                      |       |             |       |                                                |  |  |  |  |

|               |      | I/O ports:                                  |                                                      |       |             |       |                                                |  |  |  |  |

| D030          |      | with TTL buffer                             | Vss                                                  | —     | 0.8         | V     | For all $4.5V \le VDD \le 5.5V$                |  |  |  |  |

| D030A         |      |                                             | Vss                                                  | —     | 0.15<br>VDD | V     |                                                |  |  |  |  |

| D031          |      | with Schmitt Trigger<br>buffer              | Vss                                                  | _     | 0.2 Vdd     | V     |                                                |  |  |  |  |

| D032          |      | MCLR, T0CKI                                 | Vss                                                  | _     | 0.2 Vdd     | V     |                                                |  |  |  |  |

|               | Vih  | Input High Voltage                          |                                                      |       |             |       |                                                |  |  |  |  |

|               |      | I/O ports:                                  |                                                      |       |             |       |                                                |  |  |  |  |

| D040          |      | with TTL buffer                             | 2.0                                                  |       | Vdd         | V     | $4.5V \leq V\text{DD} \leq 5.5V$               |  |  |  |  |

| D040A         |      |                                             | 0.25 VDD + 0.8                                       | _     | Vdd         | V     | Otherwise                                      |  |  |  |  |

| D041          |      | with Schmitt Trigger<br>buffer              | 0.8Vdd                                               | —     | Vdd         | V     | For entire VDD range                           |  |  |  |  |

| D042          |      | MCLR, TOCKI                                 | 0.8Vdd                                               | —     | Vdd         | V     |                                                |  |  |  |  |

| D070          | IPUR | GPIO weak pull-up<br>current <sup>(3)</sup> | 50                                                   | 250   | 400         | μΑ    | VDD = 5V, VPIN = VSS                           |  |  |  |  |

|               | lı∟  | Input Leakage Current <sup>(1, 2</sup>      | 2)                                                   |       |             |       |                                                |  |  |  |  |

| D060          |      | I/O ports                                   | —                                                    | ±0.1  | ± 1         | μΑ    | $Vss \le VPIN \le VDD$ , Pin at high-impedance |  |  |  |  |

| D061          |      | GP3/MCLR <sup>(3)</sup>                     | —                                                    | ±0.7  | ± 5         | μΑ    | $Vss \leq V \text{PIN} \leq V \text{DD}$       |  |  |  |  |

|               |      | Output Low Voltage                          |                                                      |       |             |       |                                                |  |  |  |  |

| D080          |      | I/O ports                                   | —                                                    | —     | 0.6         | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C    |  |  |  |  |

| D080A         |      |                                             | —                                                    | —     | 0.6         | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C   |  |  |  |  |

|               |      | Output High Voltage                         |                                                      |       |             |       |                                                |  |  |  |  |

| D090          |      | I/O ports <sup>(2)</sup>                    | VDD - 0.7                                            |       | —           | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C   |  |  |  |  |

| D090A         |      |                                             | Vdd - 0.7                                            | —     | —           | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C  |  |  |  |  |

|               |      | Capacitive Loading Spece                    | s on Output Pins                                     | 5     |             |       |                                                |  |  |  |  |

| D101          |      | All I/O pins                                | _                                                    |       | 50*         | pF    |                                                |  |  |  |  |

† Data in "Typ." column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

\* These parameters are for design guidance only and are not tested.

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**2:** Negative current is defined as coming out of the pin.

**3:** This specification applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

## TABLE 12-1: COMPARATOR SPECIFICATIONS

## Standard Operating Conditions (unless otherwise stated)

|  |  | Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |

|--|--|-----------------------------------------------------|

|--|--|-----------------------------------------------------|

| Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |         |                                           |         |      |          |      |       |                                                                         |  |

|---------------------------------------------------------------|---------|-------------------------------------------|---------|------|----------|------|-------|-------------------------------------------------------------------------|--|

| Param.<br>No.                                                 | Sym.    | Characteristics                           |         | Min. | Тур.†    | Max. | Units | Comments                                                                |  |

| D300                                                          | Vos     | Input Offset Voltage                      |         | —    | ± 5.0    | ± 10 | mV    | (Vdd - 1.5)/2                                                           |  |

| D301                                                          | Vсм     | Input Common Mode V                       | 0       | —    | VDD-1.5* | V    |       |                                                                         |  |

| D302                                                          | CMRR    | Common Mode Rejection Ratio               |         | 55*  | _        |      | dB    |                                                                         |  |

| D303*                                                         | Trt     | Response Time                             | Falling | —    | 150      | 600  | ns    | (Note 1)                                                                |  |

|                                                               |         |                                           | Rising  | —    | 200      | 1000 | ns    |                                                                         |  |

| D304*                                                         | Тмc2coV | Comparator Mode Change to<br>Output Valid |         | _    | —        | 10*  | μS    |                                                                         |  |

| D305                                                          | Vivrf   | Internal Reference Voltage                |         | 0.55 | 0.6      | 0.65 | V     | $2.0V \le VDD \le 5.5V$<br>-40°C $\le$ TA $\le \pm 125°C$<br>(extended) |  |

\* These parameters are characterized but not tested.

Data in 'Typ.' column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV.

## TABLE 12-2: PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min. | Тур. | Max. | Units |

|-------------|------------------|------|------|------|-------|

| GP0/GP1     |                  |      |      |      |       |

| 2.0         | -40              | 73K  | 105K | 186K | Ω     |

|             | 25               | 73K  | 113K | 187K | Ω     |

|             | 85               | 82K  | 123K | 190K | Ω     |

|             | 125              | 86K  | 132k | 190K | Ω     |

| 5.5         | -40              | 15K  | 21K  | 33K  | Ω     |

|             | 25               | 15K  | 22K  | 34K  | Ω     |

|             | 85               | 19K  | 26k  | 35K  | Ω     |

|             | 125              | 23K  | 29K  | 35K  | Ω     |

| GP3         |                  |      |      |      | •     |

| 2.0         | -40              | 63K  | 81K  | 96K  | Ω     |

|             | 25               | 77K  | 93K  | 116K | Ω     |

|             | 85               | 82K  | 96k  | 116K | Ω     |

|             | 125              | 86K  | 100K | 119K | Ω     |

| 5.5         | -40              | 16K  | 20k  | 22K  | Ω     |

|             | 25               | 16K  | 21K  | 23K  | Ω     |

|             | 85               | 24K  | 25k  | 28K  | Ω     |

|             | 125              | 26K  | 27K  | 29K  | Ω     |

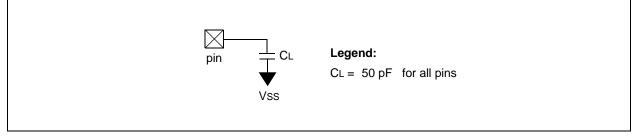

# 12.4 Timing Parameter Symbology and Load Conditions – PIC10F200/202/204/206

The timing parameter symbols have been created following one of the following formats:

1. TppS2ppS

2. TppS

| 2. TppS |                                          |        |                |  |  |  |  |

|---------|------------------------------------------|--------|----------------|--|--|--|--|

| т       |                                          |        |                |  |  |  |  |

| F F     | requency                                 | T Time |                |  |  |  |  |

| Lower   | case subscripts (pp) and their meanings: |        |                |  |  |  |  |

| рр      |                                          |        |                |  |  |  |  |

| 2       | to                                       | mc     | MCLR           |  |  |  |  |

| ck      | CLKOUT                                   | osc    | Oscillator     |  |  |  |  |

| су      | Cycle time                               | tO     | ТОСКІ          |  |  |  |  |

| drt     | Device Reset Timer                       | wdt    | Watchdog Timer |  |  |  |  |

| io      | I/O port                                 | wdt    | Watchdog Timer |  |  |  |  |

| Upper   | case letters and their meanings:         |        |                |  |  |  |  |

| S       |                                          |        |                |  |  |  |  |

| F       | Fall                                     | Р      | Period         |  |  |  |  |

| Н       | High                                     | R      | Rise           |  |  |  |  |

| 1       | Invalid (high-impedance)                 | V      | Valid          |  |  |  |  |

| L       | Low                                      | Z      | High-impedance |  |  |  |  |

## FIGURE 12-2: LOAD CONDITIONS – PIC10F200/202/204/206

| AC CHARACTERISTICS |      |                                                          | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ |              |              |              |            |                                                                                                                                                                                     |  |

|--------------------|------|----------------------------------------------------------|-------------------------------------------------------|--------------|--------------|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Sym. | Characteristic                                           | Freq.<br>Tolerance Min. Typ.† Max. Units Conditions   |              |              |              | Conditions |                                                                                                                                                                                     |  |

| F10                | Fosc | Internal Calibrated<br>INTOSC Frequency <sup>(1,2)</sup> | ± 1%<br>± 2%                                          | 3.96<br>3.92 | 4.00<br>4.00 | 4.04<br>4.08 | MHz<br>MHz | VDD=3.5V @ 25°C<br>2.5V $\leq$ VDD $\leq$ 5.5V<br>0°C $\leq$ TA $\leq$ +85°C (industrial)                                                                                           |  |

|                    |      |                                                          | ± 5%                                                  | 3.80         | 4.00         | 4.20         | MHz        | $\begin{array}{l} 2.0V \leq VDD \leq 5.5V \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ (industrial)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ (extended)} \end{array}$ |  |

## TABLE 12-3: CALIBRATED INTERNAL RC FREQUENCIES - PIC10F200/202/204/206

\* These parameters are characterized but not tested.

† Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

2: Under stable VDD conditions.

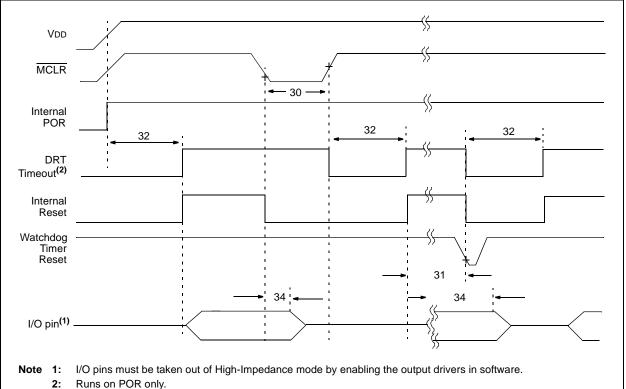

## FIGURE 12-3: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER TIMING – PIC10F200/202/204/206

# PIC10F200/202/204/206

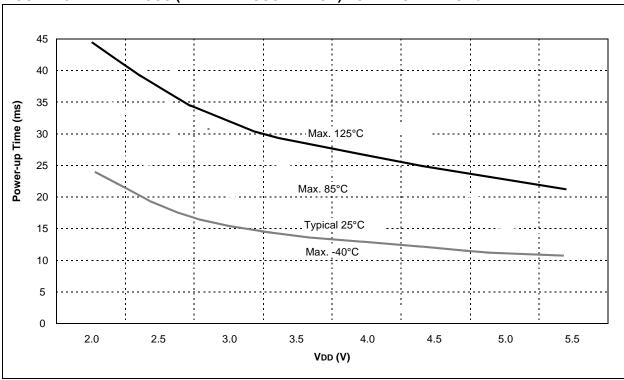

# FIGURE 13-14: INTOSC (INTERNAL OSCILLATOR) POWER-UP TIMES vs. VDD

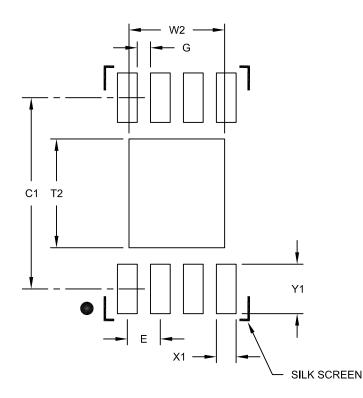

8-Lead Plastic Dual Flat, No Lead Package (MC) - 2x3x0.9mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                            | MILLIMETERS          |      |          |      |  |

|----------------------------|----------------------|------|----------|------|--|

| Dimensio                   | Dimension Limits     |      |          |      |  |

| Contact Pitch              | E                    |      | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2                   |      |          | 1.45 |  |

| Optional Center Pad Length | Center Pad Length T2 |      |          | 1.75 |  |

| Contact Pad Spacing        | C1                   |      | 2.90     |      |  |

| Contact Pad Width (X8)     | X1                   |      |          | 0.30 |  |

| Contact Pad Length (X8)    | Y1                   |      |          | 0.75 |  |

| Distance Between Pads      | G                    | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2123B

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

## ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

## ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79 Germany - Dusseldorf Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

03/25/14