Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

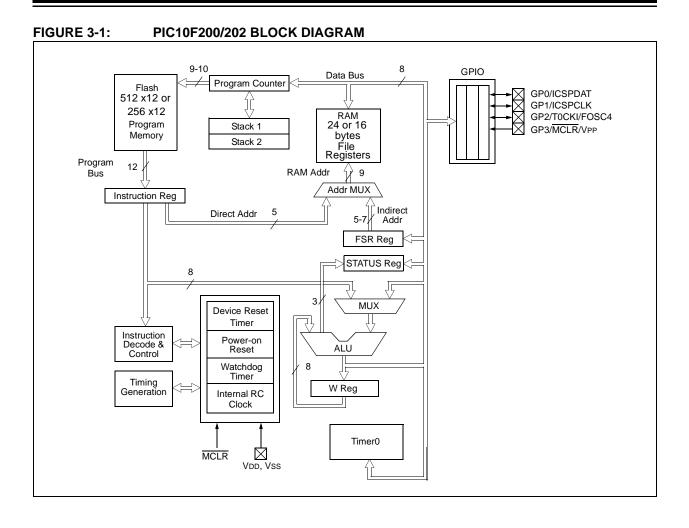

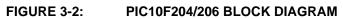

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 24 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f202t-e-ot |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

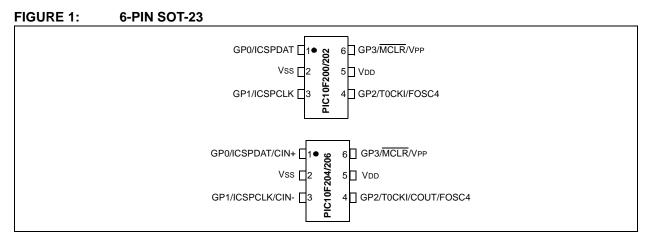

### **Pin Diagrams**

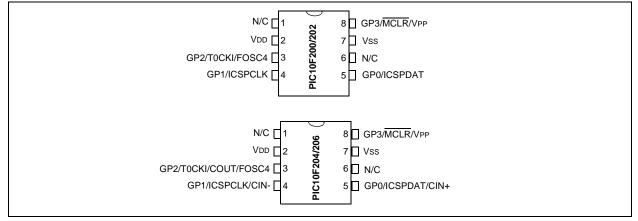

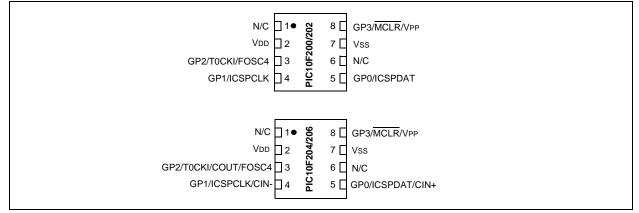

#### FIGURE 2: 8-PIN PDIP

### FIGURE 3: 8-PIN DFN

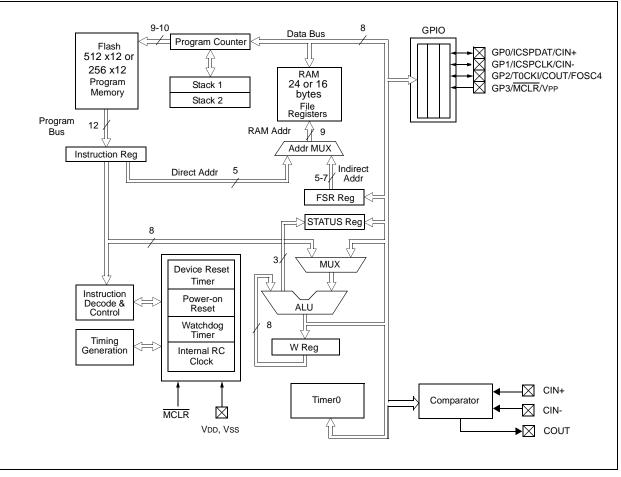

## 4.2 Program Memory Organization for the PIC10F202/206

The PIC10F202/206 devices have a 10-bit Program Counter (PC) capable of addressing a 1024 x 12 program memory space.

Only the first  $512 \times 12$  (0000h-01FFh) for the PIC10F202/206 are physically implemented (see Figure 4-2). Accessing a location above these boundaries will cause a wraparound within the first  $512 \times 12$  space (PIC10F202/206). The effective Reset vector is at 0000h (see Figure 4-2). Location 01FFh (PIC10F202/206) contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC10F202/206

### 4.3 Data Memory Organization

Data memory is composed of registers or bytes of RAM. Therefore, data memory for a device is specified by its register file. The register file is divided into two functional groups: Special Function Registers (SFR) and General Purpose Registers (GPR).

The Special Function Registers include the TMR0 register, the Program Counter (PCL), the STATUS register, the I/O register (GPIO) and the File Select Register (FSR). In addition, Special Function Registers are used to control the I/O port configuration and prescaler options.

The General Purpose registers are used for data and control information under command of the instructions.

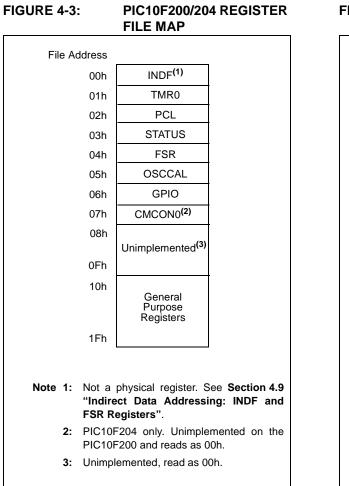

For the PIC10F200/204, the register file is composed of seven Special Function registers and 16 General Purpose registers (see Figure 4-3 and Figure 4-4).

For the PIC10F202/206, the register file is composed of eight Special Function registers and 24 General Purpose registers (see Figure 4-4).

#### 4.3.1 GENERAL PURPOSE REGISTER FILE

The General Purpose Register file is accessed, either directly or indirectly, through the File Select Register (FSR). See Section 4.9 "Indirect Data Addressing: INDF and FSR Registers".

FIGURE 4-4:

### PIC10F202/206 REGISTER FILE MAP

| ddress                     |                                                                                                    |                                                                                                                                                                                                                                                                 |

|----------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h                        | INDF <sup>(1)</sup>                                                                                |                                                                                                                                                                                                                                                                 |

| 01h                        | TMR0                                                                                               |                                                                                                                                                                                                                                                                 |

| 02h                        | PCL                                                                                                |                                                                                                                                                                                                                                                                 |

| 03h                        | STATUS                                                                                             |                                                                                                                                                                                                                                                                 |

| 04h                        | FSR                                                                                                |                                                                                                                                                                                                                                                                 |

| 05h                        | OSCCAL                                                                                             |                                                                                                                                                                                                                                                                 |

| 06h                        | GPIO                                                                                               |                                                                                                                                                                                                                                                                 |

| 07h                        | CMCON0 <sup>(2)</sup>                                                                              |                                                                                                                                                                                                                                                                 |

| 08h                        |                                                                                                    |                                                                                                                                                                                                                                                                 |

|                            | General<br>Purpose<br>Registers                                                                    |                                                                                                                                                                                                                                                                 |

| 1Fh                        |                                                                                                    |                                                                                                                                                                                                                                                                 |

| "Indire<br>FSR R<br>PIC10F | ct Data Addressi<br>egisters".<br>206 only. Unimple                                                | ing: INDF and<br>emented on the                                                                                                                                                                                                                                 |

|                            | 01h<br>02h<br>03h<br>04h<br>05h<br>06h<br>07h<br>08h<br>1Fh<br>Not a<br>"Indire<br>FSR R<br>PIC10F | 00h       INDF <sup>(1)</sup> 01h       TMR0         02h       PCL         03h       STATUS         04h       FSR         05h       OSCCAL         06h       GPIO         07h       CMCON0 <sup>(2)</sup> 08h       General<br>Purpose<br>Registers         1Fh |

### 4.4 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as  $000u \ u1uu$  (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions which do affect Status bits, see **Section 10.0** "Instruction Set Summary".

| R/W-0           | R/W-0                              | U-1                                                    | R-1                        | R-1              | R/W-x           | R/W-x             | R/W-x    |

|-----------------|------------------------------------|--------------------------------------------------------|----------------------------|------------------|-----------------|-------------------|----------|

| GPWUF           | CWUF <sup>(1)</sup>                | _                                                      | ТО                         | PD               | Z               | DC                | С        |

| bit 7           |                                    |                                                        |                            |                  |                 |                   | bit (    |

| Legend:         |                                    |                                                        |                            |                  |                 |                   |          |

| R = Readable    | bit                                | W = Writable I                                         | oit                        | U = Unimple      | mented bit, rea | ad as '0'         |          |

| -n = Value at F | POR                                | '1' = Bit is set                                       |                            | '0' = Bit is cle |                 | x = Bit is unkr   | nown     |

| L:1.7           |                                    |                                                        |                            |                  |                 |                   |          |

| bit 7           |                                    | e to wake-up fro<br>er-up or other F                   |                            | pin change       |                 |                   |          |

| bit 6           | <b>CWUF:</b> Comp<br>1 = Reset due | oarator Wake-u<br>e to wake-up fro<br>er-up or other F | o on Change<br>om Sleep on | comparator cha   | ange            |                   |          |

| bit 5           | Reserved: De                       | o not use. Use                                         | of this bit ma             | y affect upward  | d compatibility | with future produ | ucts.    |

| bit 4           | TO: Time-out                       | bit                                                    |                            |                  |                 |                   |          |

|                 |                                    | er-up, CLRWDT                                          |                            | SLEEP instruc    | ction           |                   |          |

| bit 3           | PD: Power-do                       | own bit                                                |                            |                  |                 |                   |          |

|                 |                                    | er-up or by the tion of the SLEE                       |                            |                  |                 |                   |          |

| bit 2           | Z: Zero bit                        |                                                        |                            |                  |                 |                   |          |

|                 |                                    | t of an arithmet                                       | • .                        |                  |                 |                   |          |

|                 |                                    | t of an arithmet                                       | • ·                        |                  |                 |                   |          |

| bit 1           | •                                  | ry/Borrow bit (fo                                      | or ADDWF and               | SUBWF instruc    | ctions)         |                   |          |

|                 | ADDWF:                             | ana tha 1th law.                                       | andan bit af th            |                  | a d             |                   |          |

|                 |                                    | om the 4th low-<br>om the 4th low-                     |                            |                  |                 |                   |          |

|                 | SUBWF:                             |                                                        |                            |                  |                 |                   |          |

|                 |                                    | from the 4th lov<br>from the 4th lov                   |                            |                  |                 |                   |          |

| bit 0           | C: Carry/Borr                      | ow bit (for ADD                                        | VF, SUBWF ar               | d RRF, RLF ins   | structions)     |                   |          |

|                 | ADDWF:                             |                                                        | UBWF:                      |                  | RRF or RLF:     |                   |          |

|                 | 1 = A carry or<br>0 = A carry di   |                                                        | = A borrow                 |                  | Load bit with L | Sb or MSb, resp   | ectively |

Note 1: This bit is used on the PIC10F204/206. For code compatibility do not use this bit on the PIC10F200/202.

#### 4.5 **OPTION Register**

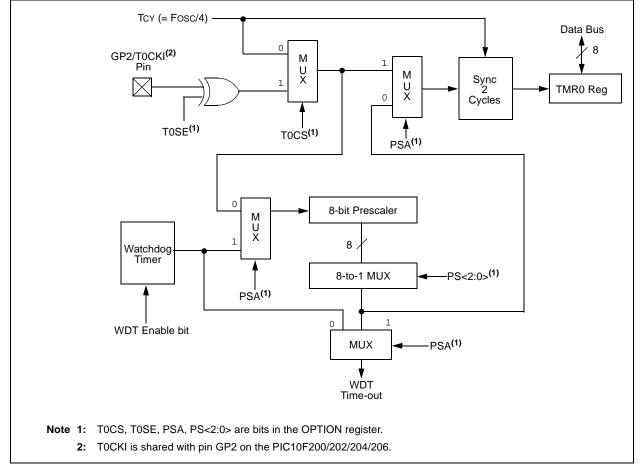

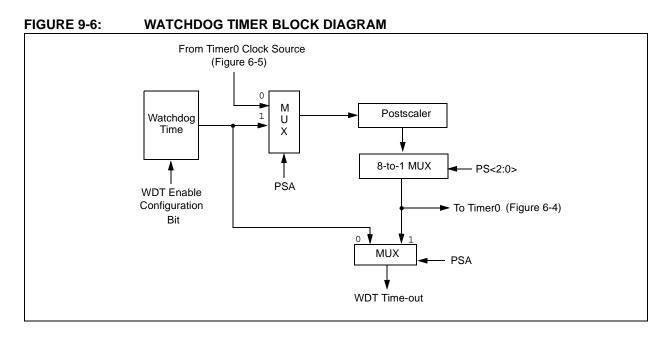

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

#### **REGISTER 4-2: OPTION REGISTER**

| Note: | If TRIS bit is set to '0', the wake-up on    |

|-------|----------------------------------------------|

|       | change and pull-up functions are disabled    |

|       | for that pin (i.e., note that TRIS overrides |

|       | Option control of GPPU and GPWU).            |

Note: If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

| W-1   | W-1 W-1   |  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|-----------|--|------|-----|-----|-----|-------|

| GPWU  | GPPU T0CS |  | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7 | •         |  |      |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

1:16

1:32

1:64

1:128

| 1 :     |                                                               |

|---------|---------------------------------------------------------------|

| bit 7   | <b>GPWU:</b> Enable Wake-up on Pin Change bit (GP0, GP1, GP3) |

|         | 1 = Disabled                                                  |

|         | 0 = Enabled                                                   |

| bit 6   | GPPU: Enable Weak Pull-ups bit (GP0, GP1, GP3)                |

|         | 1 = Disabled                                                  |

|         | 0 = Enabled                                                   |

| bit 5   | TOCS: Timer0 Clock Source Select bit                          |

|         | 1 = Transition on T0CKI pin (overrides TRIS on the T0CKI pin) |

|         | 0 = Transition on internal instruction cycle clock, Fosc/4    |

| bit 4   | TOSE: Timer0 Source Edge Select bit                           |

|         | 1 = Increment on high-to-low transition on the T0CKI pin      |

|         | 0 = Increment on low-to-high transition on the T0CKI pin      |

| bit 3   | PSA: Prescaler Assignment bit                                 |

|         | 1 = Prescaler assigned to the WDT                             |

|         | 0 = Prescaler assigned to Timer0                              |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                           |

|         | Bit Value Timer0 Rate WDT Rate                                |

|         | 000 1:2 1:1                                                   |

|         | 001 1:4 1:2                                                   |

|         | 010 1:8 1:4                                                   |

|         | 011 1:16 1:8                                                  |

1:32

1:64

1 : 128 1 : 256

100

101

110 111

#### FIGURE 5-2: SUCCESSIVE I/O OPERATION (PIC10F200/202/204/206)

`Q1| Q2| Q3| Q4` Q1| Q2| Q3| Q4` Q1| Q2| Q3| Q4` Q1| Q2| Q3| Q4`

| Instruction             | PC         | V PC + 1                                                  | PC + 2                                                 | X PC + 3 | This example shows a write to GPIO followed by a read from GPIO.                       |

|-------------------------|------------|-----------------------------------------------------------|--------------------------------------------------------|----------|----------------------------------------------------------------------------------------|

| Fetched                 | MOVWF GPIO | MOVF GPIO, W                                              | NOP                                                    | NOP      | Data setup time = (0.25 TCY - TPD)                                                     |

|                         |            | i i                                                       |                                                        |          | where: TCY = instruction cycle                                                         |

| GP<2:0>                 |            |                                                           | χ                                                      |          | TPD = propagation delay                                                                |

| Instruction<br>Executed |            | Port pin<br>written here<br>MOVWF GPIO<br>(Write to GPIO) | Port pin<br>sampled here<br>MOVF GPIO,W<br>(Read GPIO) | NOP      | Therefore, at higher clock frequencies, a write followed by a read may be problematic. |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        |            | · ·                 |

|--------|------------|---------------------|

| CLRWDT |            | ;Clear WDT and      |

|        |            | ;prescaler          |

| MOVLW  | 'xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

|        |            |                     |

### FIGURE 6-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

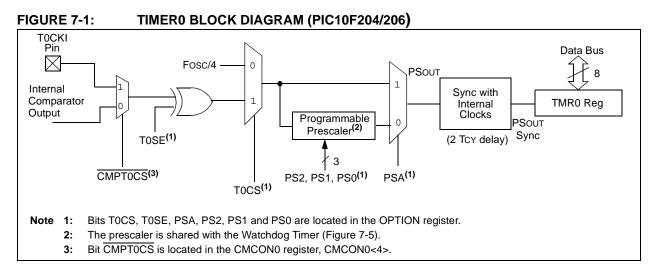

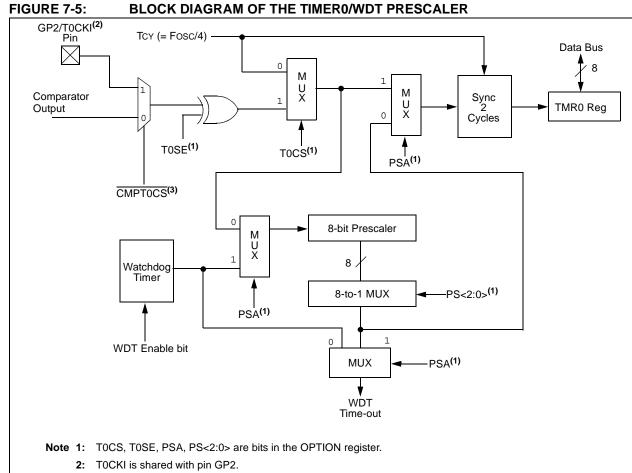

## 7.0 TIMER0 MODULE AND TMR0 REGISTER (PIC10F204/206)

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

- External clock from either the T0CKI pin or from the output of the comparator

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to the TMR0 register.

There are two types of Counter mode. The first Counter mode uses the T0CKI pin to increment Timer0. It is selected by setting the T0CS bit (OPTION<5>), setting the CMPT0CS bit (CMCON0<4>) and setting the COUTEN bit (CMCON0<6>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.1 "Using Timer0 with an External Clock (PIC10F204/206)".

The second Counter mode uses the output of the comparator to increment Timer0. It can be entered in two different ways. The first way is selected by setting the T0CS bit (OPTION<5>) and clearing the CMPT0CS bit (CMCON<4>); (COUTEN [CMCON<6>]) does not affect this mode of operation. This enables an internal connection between the comparator and the Timer0.

The second way is selected by setting the TOCS bit (OPTION<5>). the **CMPT0CS** setting bit and clearing the COUTEN (CMCON0<4>) bit (CMCON0<6>). This allows the output of the comparator onto the TOCKI pin, while keeping the T0CKI input active. Therefore, any comparator change on the COUT pin is fed back into the TOCKI input. The TOSE bit (OPTION<4>) determines the source edge. Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input as discussed in Section 7.1 "Using Timer0 with an External Clock (PIC10F204/206)"

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. **Section 7.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 7-1.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        |            | · /                 |

|--------|------------|---------------------|

| CLRWDT |            | ;Clear WDT and      |

|        |            | ;prescaler          |

| MOVLW  | `xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

|        |            |                     |

3: Bit CMPT0CS is located in the CMCON0 register.

#### TABLE 9-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE WATCHDOG TIMER

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| N/A     | OPTION | GPWU  | GPPU  | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

Legend: Shaded boxes = Not used by Watchdog Timer, - = unimplemented, read as '0', u = unchanged.

| Mnemonic,<br>Operands |                                | Description                                       | Cycles           | 12-Bit Opcode |      |      | Status   | Notes   |

|-----------------------|--------------------------------|---------------------------------------------------|------------------|---------------|------|------|----------|---------|

|                       |                                |                                                   |                  | MSb           |      | LSb  | Affected | Notes   |

| ADDWF                 | f, d                           | Add W and f                                       | 1                | 0001          | 11df | ffff | C, DC, Z | 1, 2, 4 |

| ANDWF                 | f, d                           | AND W with f                                      | 1                | 0001          | 01df | ffff | Z        | 2, 4    |

| CLRF                  | f                              | Clear f                                           | 1                | 0000          | 011f | ffff | Z        | 4       |

| CLRW                  | —                              | Clear W                                           | 1                | 0000          | 0100 | 0000 | Z        |         |

| COMF                  | f, d                           | Complement f                                      | 1                | 0010          | 01df | ffff | Z        |         |

| DECF                  | f, d                           | Decrement f                                       | 1                | 0000          | 11df | ffff | Z        | 2, 4    |

| DECFSZ                | f, d                           | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010          | 11df | ffff | None     | 2, 4    |

| INCF                  | f, d                           | Increment f                                       | 1                | 0010          | 10df | ffff | Z        | 2, 4    |

| INCFSZ                | f, d                           | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011          | 11df | ffff | None     | 2, 4    |

| IORWF                 | f, d                           | Inclusive OR W with f                             | 1                | 0001          | 00df | ffff | Z        | 2, 4    |

| MOVF                  | f, d                           | Move f                                            | 1                | 0010          | 00df | ffff | Z        | 2, 4    |

| MOVWF                 | f                              | Move W to f                                       | 1                | 0000          | 001f | ffff | None     | 1, 4    |

| NOP                   | _                              | No Operation                                      | 1                | 0000          | 0000 | 0000 | None     |         |

| RLF                   | f, d                           | Rotate left f through Carry                       | 1                | 0011          | 01df | ffff | С        | 2, 4    |

| RRF                   | f, d                           | Rotate right f through Carry                      | 1                | 0011          | 00df | ffff | С        | 2, 4    |

| SUBWF                 | f, d                           | Subtract W from f                                 | 1                | 0000          | 10df | ffff | C, DC, Z | 1, 2, 4 |

| SWAPF                 | f, d                           | Swap f                                            | 1                | 0011          | 10df | ffff | None     | 2, 4    |

| XORWF                 | f, d                           | Exclusive OR W with f                             | 1                | 0001          | 10df | ffff | Z        | 2, 4    |

|                       |                                | BIT-ORIENTED FILE REGISTE                         |                  | ATIONS        |      |      |          |         |

| BCF                   | f, b                           | Bit Clear f                                       | 1                | 0100          | bbbf | ffff | None     | 2, 4    |

| BSF                   | f, b                           | Bit Set f                                         | 1                | 0101          | bbbf | ffff | None     | 2, 4    |

| BTFSC                 | f, b                           | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110          | bbbf | ffff | None     | -       |

| BTFSS                 | f, b                           | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111          | bbbf | ffff | None     |         |

|                       | LITERAL AND CONTROL OPERATIONS |                                                   |                  |               |      |      |          |         |

| ANDLW                 | k                              | AND literal with W                                | 1                | 1110          | kkkk | kkkk | Z        |         |

| CALL                  | k                              | Call Subroutine                                   | 2                | 1001          | kkkk | kkkk | None     | 1       |

| CLRWDT                |                                | Clear Watchdog Timer                              | 1                | 0000          | 0000 | 0100 | TO, PD   |         |

| GOTO                  | k                              | Unconditional branch                              | 2                | 101k          | kkkk | kkkk | None     |         |

| IORLW                 | k                              | Inclusive OR literal with W                       | 1                | 1101          | kkkk | kkkk | Z        |         |

| MOVLW                 | k                              | Move literal to W                                 | 1                | 1100          | kkkk | kkkk | None     |         |

| OPTION                | _                              | Load OPTION register                              | 1                | 0000          | 0000 | 0010 | None     |         |

| RETLW                 | k                              | Return, place Literal in W                        | 2                | 1000          | kkkk | kkkk | None     |         |

| SLEEP                 | _                              | Go into Standby mode                              | 1                | 0000          | 0000 | 0011 | TO, PD   |         |

| TRIS                  | f                              | Load TRIS register                                | 1                | 0000          | 0000 | 0fff | None     | 3       |

| XORLW                 | k                              | Exclusive OR literal to W                         | 1                |               | kkkk |      | Z        | -       |

| Note 1                |                                | it of the program counter will be forced to a fai |                  |               |      |      |          |         |

#### TABLE 10-2: INSTRUCTION SET SUMMARY

**Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. See Section 4.7 "Program Counter".

2: When an I/O register is modified as a function of itself (e.g. MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6, causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

**4:** If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

(W) .XOR.  $k \rightarrow (W)$

The contents of the W register are XOR'ed with the 8-bit literal 'k'. The result is placed in the W

Ζ

register.

| TRIS             | Load TRIS Register                         | XORWF            | Exclusive OR W with f                                                                                                                              |  |  |

|------------------|--------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] TRIS f                             | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                         |  |  |

| Operands:        | f = 6                                      | Operands:        | $0 \le f \le 31$                                                                                                                                   |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f          |                  | $d \in [0,1]$                                                                                                                                      |  |  |

| Status Affected: | None                                       | Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                 |  |  |

| Description:     | TRIS register 'f' (f = 6 or 7) is          | Status Affected: | Z                                                                                                                                                  |  |  |

|                  | loaded with the contents of the W register | Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is |  |  |

| XORLW            | Exclusive OR literal with W                |                  | stored back in register 'f'.                                                                                                                       |  |  |

| Syntax:          | [ <i>label</i> ] XORLW k                   |                  | ç                                                                                                                                                  |  |  |

| Operands:        | $0 \le k \le 255$                          |                  |                                                                                                                                                    |  |  |

Operation:

Description:

Status Affected:

### 11.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 11.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 12.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                         | 40°C to +125°C                     |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                    | 65°C to +150°C                     |

| Voltage on VDD with respect to Vss                                                                                     | 0 to +6.5V                         |

| Voltage on MCLR with respect to Vss                                                                                    | 0 to +13.5V                        |

| Voltage on all other pins with respect to Vss                                                                          | 0.3V to (VDD + 0.3V)               |

| Total power dissipation <sup>(1)</sup>                                                                                 | 800 mW                             |

| Max. current out of Vss pin                                                                                            | 80 mA                              |

| Max. current into Vod pin                                                                                              | 80 mA                              |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                           | ±20 mA                             |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                         | ±20 mA                             |

| Max. output current sunk by any I/O pin                                                                                | 25 mA                              |

| Max. output current sourced by any I/O pin                                                                             | 25 mA                              |

| Max. output current sourced by I/O port                                                                                | 75 mA                              |

| Max. output current sunk by I/O port                                                                                   | 75 mA                              |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-\Sigma$ | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 12.2 DC Characteristics: PIC10F200/202/204/206 (Extended)

| DC CHARACTERISTICS |      |                                               | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C (extended) |                     |            |          |                          |  |  |

|--------------------|------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|----------|--------------------------|--|--|

| Param.<br>No.      | Sym. | Characteristic                                | Min.                                                                                                                         | Тур. <sup>(1)</sup> | Max.       | Units    | Conditions               |  |  |

| D001               | Vdd  | Supply Voltage                                | 2.0                                                                                                                          |                     | 5.5        | V        | See Figure 12-1          |  |  |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | 1.5*                                                                                                                         |                     | _          | V        | Device in Sleep mode     |  |  |

| D003               | VPOR | VDD Start Voltage<br>to ensure Power-on Reset | —                                                                                                                            | Vss                 | _          | V        |                          |  |  |

| D004               | SVDD | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05*                                                                                                                        | —                   |            | V/ms     |                          |  |  |

|                    | Idd  | Supply Current <sup>(3)</sup>                 |                                                                                                                              |                     |            |          |                          |  |  |

| D010               |      |                                               | _                                                                                                                            | 175<br>0.63         | 275<br>1.1 | μA<br>mA | VDD = 2.0V<br>VDD = 5.0V |  |  |

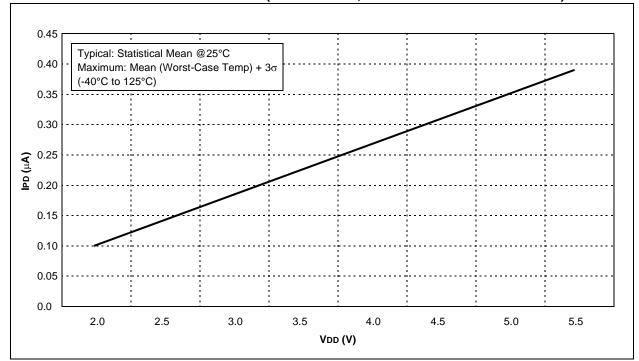

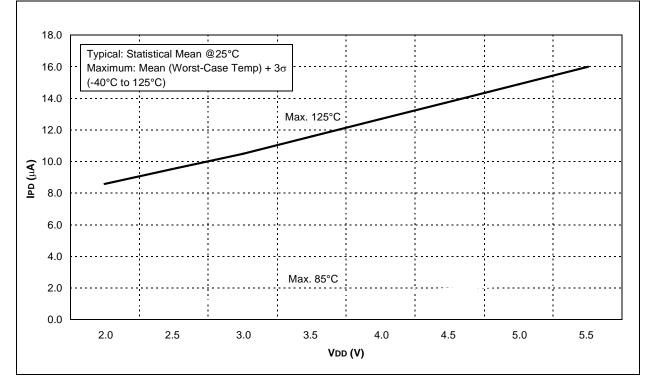

|                    | IPD  | Power-down Current <sup>(4)</sup>             |                                                                                                                              |                     |            |          |                          |  |  |

| D020               |      |                                               | _                                                                                                                            | 0.1<br>0.35         | 9<br>15    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |

|                    | IWDT | WDT Current <sup>(5)</sup>                    |                                                                                                                              | 1                   |            |          |                          |  |  |

| D022               |      |                                               | _                                                                                                                            | 1.0<br>7            | 18<br>22   | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |

|                    | Ісмр | Comparator Current <sup>(5)</sup>             |                                                                                                                              | 1                   |            | 1        |                          |  |  |

| D023               |      |                                               | _                                                                                                                            | 12<br>42            | 27<br>85   | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |

|                    | VREF | Internal Reference Current <sup>(5,6)</sup>   |                                                                                                                              |                     |            |          |                          |  |  |

| D024               |      |                                               | —                                                                                                                            | 85<br>175           | 120<br>200 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are: All I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

- 4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS.

- **5:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled.

- 6: Measured with the Comparator enabled.

### FIGURE 13-2: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO                  | [X] <sup>(1)</sup> - X /XX<br>T International Temperature Package<br>Option Range                                                                                | XXX<br>Pattern | Examples:<br>a) PIC10F202T - E/OT<br>Tape and Reel<br>Extended temperature<br>SOT-23 package (Pb-free)                                                                                                                              |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC10F200<br>PIC10F202<br>PIC10F204<br>PIC10F206<br>PIC10F200T (Tape & Reel)<br>PIC10F202T (Tape & Reel)<br>PIC10F204T (Tape & Reel)<br>PIC10F206T (Tape & Reel) |                | <ul> <li>b) PIC10F200 - I/P<br/>Industrial temperature,<br/>PDIP package (Pb-free)</li> <li>c) PIC10F204 - I/MC<br/>Industrial temperature<br/>DFN package (Pb-free)</li> </ul>                                                     |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                                                    |                |                                                                                                                                                                                                                                     |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended)                                                        |                | Note 1: Tape and Reel identifier only appears in the                                                                                                                                                                                |

| Package:                 | P = 300 mil PDIP (Pb-free)<br>OT = SOT-23, 6-LD (Pb-free)<br>MC = DFN, 8-LD 2x3 (Pb-free)                                                                        |                | catalog part number description. This<br>identifier is used for ordering purposes and is<br>not printed on the device package. Check<br>with your Microchip Sales Office for package<br>availability with the Tape and Reel option. |

| Pattern:                 | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                        |                |                                                                                                                                                                                                                                     |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2004-2014, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63276-597-0

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.