Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 4MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 3                                                                       |

| Program Memory Size        | 768B (512 x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 24 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f206-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC10F200/202/204/206 devices from Microchip Technology are low-cost, high-performance, 8-bit, fully-static, Flash-based CMOS microcontrollers. They employ a RISC architecture with only 33 single-word/ single-cycle instructions. All instructions are single cycle (1  $\mu$ s) except for program branches, which take two cycles. The PIC10F200/202/204/206 devices deliver performance in an order of magnitude higher than their competitors in the same price category. The 12-bit wide instructions are highly symmetrical, resulting in a typical 2:1 code compression over other 8-bit microcontrollers in its class. The easy-to-use and easy to remember instruction set reduces development time significantly.

The PIC10F200/202/204/206 products are equipped with special features that reduce system cost and power requirements. The Power-on Reset (POR) and Device Reset Timer (DRT) eliminate the need for external Reset circuitry. INTRC Internal Oscillator mode is provided, thereby preserving the limited number of I/O available. Power-Saving Sleep mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC10F200/202/204/206 devices are available in cost-effective Flash, which is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in Flash programmable microcontrollers, while benefiting from the Flash programmable flexibility.

The PIC10F200/202/204/206 products are supported by a full-featured macro assembler, a software simulator, an in-circuit debugger, a 'C' compiler, a low-cost development programmer and a full featured programmer. All the tools are supported on IBM<sup>®</sup> PC and compatible machines.

## 1.1 Applications

The PIC10F200/202/204/206 devices fit in applications ranging from personal care appliances and security systems to low-power remote transmitters/receivers. The Flash technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make these microcontrollers well suited for applications with space limitations. Low cost, low power, high performance, ease-of-use and I/O flexibility make the PIC10F200/202/204/206 devices very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, logic and PLDs in larger systems and coprocessor applications).

|             |                                            | PIC10F200                       | PIC10F202                       | PIC10F204                       | PIC10F206                       |

|-------------|--------------------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| Clock       | Maximum Frequency of Operation (MHz)       | 4                               | 4                               | 4                               | 4                               |

| Memory      | Flash Program Memory                       | 256                             | 512                             | 256                             | 512                             |

|             | Data Memory (bytes)                        | 16                              | 24                              | 16                              | 24                              |

| Peripherals | Timer Module(s)                            | TMR0                            | TMR0                            | TMR0                            | TMR0                            |

|             | Wake-up from Sleep on Pin Change           | Yes                             | Yes                             | Yes                             | Yes                             |

|             | Comparators                                | 0                               | 0                               | 1                               | 1                               |

| Features    | I/O Pins                                   | 3                               | 3                               | 3                               | 3                               |

|             | Input-Only Pins                            | 1                               | 1                               | 1                               | 1                               |

|             | Internal Pull-ups                          | Yes                             | Yes                             | Yes                             | Yes                             |

|             | In-Circuit Serial Programming <sup>™</sup> | Yes                             | Yes                             | Yes                             | Yes                             |

|             | Number of Instructions                     | 33                              | 33                              | 33                              | 33                              |

|             | Packages                                   | 6-pin SOT-23<br>8-pin PDIP, DFN |

#### TABLE 1-1: PIC10F200/202/204/206 DEVICES

The PIC10F200/202/204/206 devices have Power-on Reset, selectable Watchdog Timer, selectable code-protect, high I/O current capability and precision internal oscillator.

The PIC10F200/202/204/206 devices use serial programming with data pin GP0 and clock pin GP1.

| Name             | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                                                                                   |

|------------------|----------|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/ICSPDAT/CIN+ | GP0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                             |

|                  | ICSPDAT  | ST            | CMOS           | In-Circuit Serial Programming <sup>™</sup> data pin.                                                                                                                                                                                                                          |

|                  | CIN+     | AN            | _              | Comparator input (PIC10F204/206 only).                                                                                                                                                                                                                                        |

| GP1/ICSPCLK/CIN- | GP1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                             |

|                  | ICSPCLK  | ST            | CMOS           | In-Circuit Serial Programming clock pin.                                                                                                                                                                                                                                      |

|                  | CIN-     | AN            | _              | Comparator input (PIC10F204/206 only).                                                                                                                                                                                                                                        |

| GP2/T0CKI/COUT/  | GP2      | TTL           | CMOS           | Bidirectional I/O pin.                                                                                                                                                                                                                                                        |

| FOSC4            | T0CKI    | ST            | _              | Clock input to TMR0.                                                                                                                                                                                                                                                          |

|                  | COUT     |               | CMOS           | Comparator output (PIC10F204/206 only).                                                                                                                                                                                                                                       |

|                  | FOSC4    |               | CMOS           | Oscillator/4 output.                                                                                                                                                                                                                                                          |

| GP3/MCLR/Vpp     | GP3      | TTL           | —              | Input pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                                                                                         |

|                  | MCLR     | ST            | _              | Master Clear (Reset). When configured as MCLR, this pin is<br>an active-low Reset to the device. Voltage on GP3/MCLR/VPP<br>must not exceed VDD during normal device operation or the<br>device will enter Programming mode. Weak pull-up always on<br>if configured as MCLR. |

|                  | Vpp      | ΗV            | —              | Programming voltage input.                                                                                                                                                                                                                                                    |

| Vdd              | Vdd      | Р             | _              | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                       |

| Vss              | Vss      | Р             | —              | Ground reference for logic and I/O pins.                                                                                                                                                                                                                                      |

| TABLE 3-2: | PIC10F200/202/204/206 PINOUT DESCRIPTION |

|------------|------------------------------------------|

|            |                                          |

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, AN = Analog input

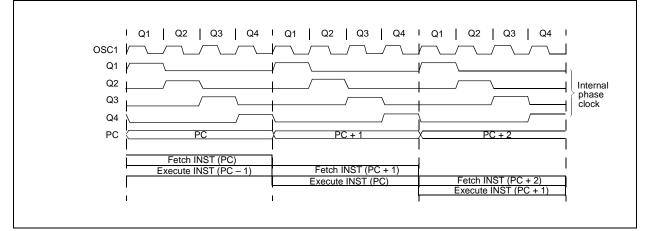

# 3.1 Clocking Scheme/Instruction Cycle

The clock is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3 and Q4. Internally, the PC is incremented every Q1 and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-3 and Example 3-1.

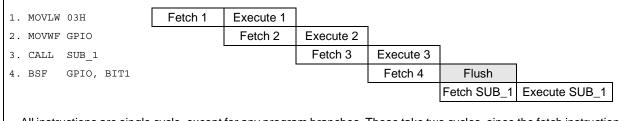

### 3.2 Instruction Flow/Pipelining

An instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles, since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

# 4.0 MEMORY ORGANIZATION

The PIC10F200/202/204/206 memories are organized into program memory and data memory. Data memory banks are accessed using the File Select Register (FSR).

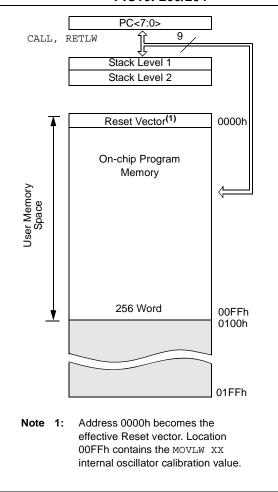

# 4.1 Program Memory Organization for the PIC10F200/204

The PIC10F200/204 devices have a 9-bit Program Counter (PC) capable of addressing a  $512 \times 12$  program memory space.

Only the first  $256 \times 12$  (0000h-00FFh) for the PIC10F200/204 are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wraparound within the first  $256 \times 12$  space (PIC10F200/204). The effective Reset vector is at 0000h (see Figure 4-1). Location 00FFh (PIC10F200/204) contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC10F200/204

#### **TABLE 5-2:** SUMMARY OF PORT REGISTERS

| Address | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2     | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|----------|-------|-------|-------|-------|---------|-----------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRISGPIO | _     | _     |       | —     | I/O Con | trol Regi | ster  |       | 1111                          | 1111                         |

| N/A     | OPTION   | GPWU  | GPPU  | TOCS  | TOSE  | PSA     | PS2       | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03h     | STATUS   | GPWUF | CWUF  | _     | TO    | PD      | Z         | DC    | С     | 00-1 1xxx                     | qq-q quuu(1), (2)            |

| 06h     | GPIO     |       | —     | —     |       | GP3     | GP2       | GP1   | GP0   | xxxx                          | uuuu                         |

Shaded cells are not used by PORT registers, read as '0', - = unimplemented, read as '0', x = unknown, u = unchanged, Legend: q = depends on condition.

г

Note 1: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

2: If Reset was due to wake-up on comparator change, then bit 6 = 1. All other Resets will cause bit 6 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 **BIDIRECTIONAL I/O PORTS**

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and rewrite the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 2 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit 2 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit 0), and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential Read-Modify-Write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired OR", "wired AND"). The resulting high output currents may damage the chip.

| EXAMPLE 5-1: | READ-MODIFY-WRITE  |

|--------------|--------------------|

|              | INSTRUCTIONS ON AN |

|              | I/O PORT           |

| ;<br>;  |         | (. | PIO latch | GPIO pins            |

|---------|---------|----|-----------|----------------------|

| ;       |         | _  |           |                      |

| BCF     | GPIO,   | 1; | pp01      | pp11                 |

| BCF     | GPIO,   | 0; | pp10      | pp11                 |

| MOVLW   | 007h;   |    |           |                      |

| TRIS    | GPIO    | ;  | pp10      | pp11                 |

| ;       |         |    |           |                      |

| Note 1: | The use | r  |           | ed the pin values to |

#### 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

# PIC10F200/202/204/206

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        |           | · ·                 |

|--------|-----------|---------------------|

| CLRWDT |           | ;Clear WDT and      |

|        |           | ;prescaler          |

| MOVLW  | `xxx0xxx' | ;Select TMR0, new   |

|        |           | ;prescale value and |

|        |           | ;clock source       |

| OPTION |           |                     |

|        |           |                     |

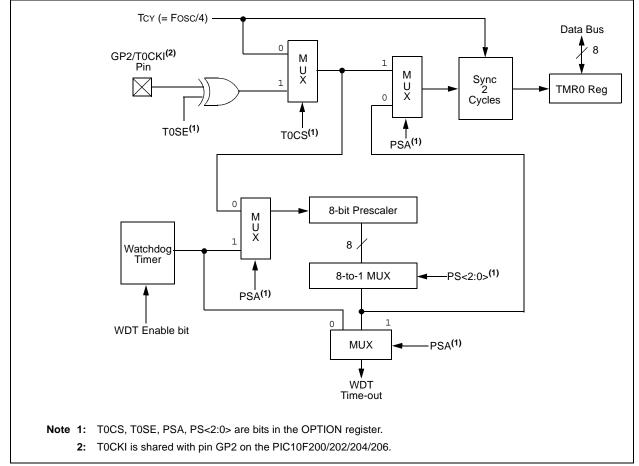

# FIGURE 6-5: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# 8.0 COMPARATOR MODULE

The comparator module contains one Analog comparator. The inputs to the comparator are multiplexed with GP0 and GP1 pins. The output of the comparator can be placed on GP2.

The CMCON0 register, shown in Register 8-1, controls the comparator operation. A block diagram of the comparator is shown in Figure 8-1.

#### REGISTER 8-1: CMCON0 REGISTER

| R-1    | R/W-1  | R/W-1 | R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|---------|-------|-------|-------|-------|

| CMPOUT | COUTEN | POL   | CMPT0CS | CMPON | CNREF | CPREF | CWU   |

| bit 7  |        |       |         |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7  |    | CMPOUT: Comparator Output bit                                                                                                     |

|--------|----|-----------------------------------------------------------------------------------------------------------------------------------|

|        |    | 1 = VIN + > VIN-                                                                                                                  |

|        |    | $0 = VIN + \langle VIN - UIN \rangle$                                                                                             |

| bit 6  |    | <b>COUTEN:</b> Comparator Output Enable bit <sup>(1, 2)</sup>                                                                     |

|        |    | 1 = Output of comparator is NOT placed on the COUT pin                                                                            |

| h:+ 7  |    | <ul> <li>0 = Output of comparator is placed in the COUT pin</li> <li>POL: Comparator Output Polarity bit<sup>(2)</sup></li> </ul> |

| bit 5  |    |                                                                                                                                   |

|        |    | <ul> <li>1 = Output of comparator not inverted</li> <li>0 = Output of comparator inverted</li> </ul>                              |

| bit 4  |    | <b>CMPT0CS</b> : Comparator TMR0 Clock Source bit <sup>(2)</sup>                                                                  |

|        |    | 1 = TMR0 clock source selected by T0CS control bit                                                                                |

|        |    | 0 = Comparator output used as TMR0 clock source                                                                                   |

| bit 3  |    | CMPON: Comparator Enable bit                                                                                                      |

|        |    | 1 = Comparator is on                                                                                                              |

|        |    | 0 = Comparator is off                                                                                                             |

| bit 2  |    | <b>CNREF:</b> Comparator Negative Reference Select bit <sup>(2)</sup>                                                             |

|        |    | $1 = \text{CIN-pin}^{(3)}$                                                                                                        |

| L.1. A |    | 0 = Internal voltage reference                                                                                                    |

| bit 1  |    | <b>CPREF:</b> Comparator Positive Reference Select bit <sup>(2)</sup><br>1 = CIN+ pin <sup>(3)</sup>                              |

|        |    | 0 = CIN+ pint(3)                                                                                                                  |

| bit 0  |    | <b>CWU</b> : Comparator Wake-up on Change Enable bit <sup>(2)</sup>                                                               |

|        |    | 1 = Wake-up on comparator change is disabled                                                                                      |

|        |    | 0 = Wake-up on comparator change is enabled.                                                                                      |

| Note   | 1: | Overrides T0CS bit for TRIS control of GP2.                                                                                       |

|        | 2: | When the comparator is turned on, these control bits assert themselves. When the comparator is off, these                         |

|        |    | bits have no effect on the device operation and the other control registers have precedence.                                      |

|        | 3: | PIC10F204/206 only.                                                                                                               |

**3:** PIC10F204/206 only.

# PIC10F200/202/204/206

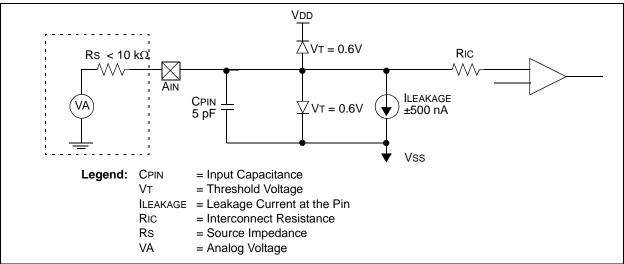

#### FIGURE 8-3: ANALOG INPUT MODE

| Address | Name     | Bit 7  | Bit 6  | Bit 5 | Bit 4   | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>All Other<br>Resets |

|---------|----------|--------|--------|-------|---------|----------------------|-------|-------|-------|-----------------|---------------------------------|

| 03h     | STATUS   | GPWUF  | CWUF   | _     | TO      | PD                   | Z     | DC    | С     | 00-1 1xxx       | qq0q quuu                       |

| 07h     | CMCON0   | CMPOUT | COUTEN | POL   | CMPT0CS | CMPON                | CNREF | CPREF | CWU   | 1111 1111       | uuuu uuuu                       |

| N/A     | TRISGPIO | —      | _      | _     | —       | I/O Control Register |       |       |       | 1111            | 1111                            |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0', q = Depends on condition.

| —                                       | STATUS Address: 03h | PCL Address: 02h |

|-----------------------------------------|---------------------|------------------|

| Power-on Reset                          | 00-1 1xxx           | 1111 1111        |

| MCLR Reset during normal operation      | 000u uuuu           | 1111 1111        |

| MCLR Reset during Sleep                 | 0001 0uuu           | 1111 1111        |

| WDT Reset during Sleep                  | 0000 0uuu           | 1111 1111        |

| WDT Reset normal operation              | 0000 uuuu           | 1111 1111        |

| Wake-up from Sleep on pin change        | 1001 Ouuu           | 1111 1111        |

| Wake-up from Sleep on comparator change | 0101 Ouuu           | 1111 1111        |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

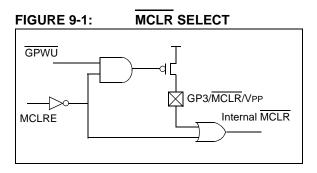

## 9.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external  $\overline{MCLR}$  function. When programmed, the  $\overline{MCLR}$  function is tied to the internal VDD and the pin is assigned to be a I/O. See Figure 9-1.

#### 9.4 Power-on Reset (POR)

The PIC10F200/202/204/206 devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as GP3. An internal weak pull-up resistor is implemented using a transistor (refer to Table 12-2 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Section 12.0 "Electrical Characteristics" for details.

When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 9-2.

The Power-on Reset circuit and the Device Reset Timer (see Section 9.5 "Device Reset Timer (DRT)") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 18 ms, it will reset the Reset latch and thus end the on-chip Reset signal.

A power-up example where MCLR is held low is shown in Figure 9-3. VDD is allowed to rise and stabilize before bringing MCLR high. The chip will actually come out of Reset TDRT msec after MCLR goes high.

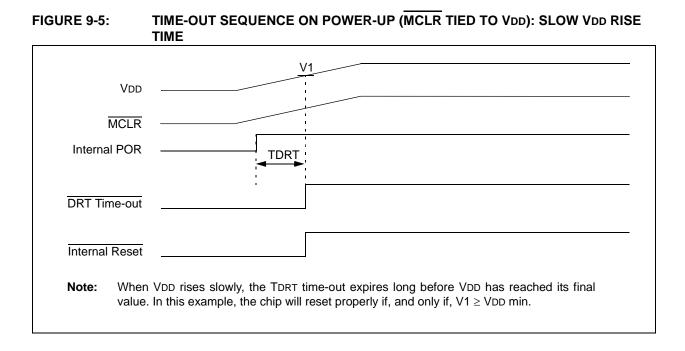

In Figure 9-4, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3). The VDD is stable before the Start-up Timer times out and there is no problem in getting a proper Reset. However, Figure 9-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the Start-up Timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 9-4).

For additional information, refer to Application Notes AN522 *"Power-up Considerations"*, (DS00522) and AN607 *"Power-up Trouble Shooting"*, (DS0000607).

Note: When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

#### 9.10 Program Verification/Code Protection

If the code protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (Reset vector) can be read, regardless of the code protection bit setting.

# 9.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify.

Use only the lower four bits of the ID locations and always program the upper eight bits as '0's.

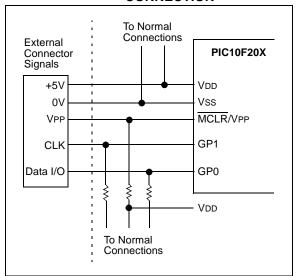

# 9.12 In-Circuit Serial Programming™

The PIC10F200/202/204/206 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1 becomes the programming clock and GP0 becomes the programming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 16 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC10F200/202/204/206 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-10.

#### FIGURE 9-10:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING™ CONNECTION

# PIC10F200/202/204/206

| RETLW            | Return with literal in W                                                                               | SLEEP            | Enter SLEEP Mode                                                                                                  |  |

|------------------|--------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                               | Syntax:          | [ label ] SLEEP                                                                                                   |  |

| Operands:        | $0 \leq k \leq 255$                                                                                    | Operands:        | None                                                                                                              |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                           | Operation:       | 00h $\rightarrow$ WDT;<br>0 $\rightarrow$ WDT prescaler;                                                          |  |

| Status Affected: | None                                                                                                   |                  | $1 \rightarrow \overline{\text{TO}};$                                                                             |  |

| Description:     | The W register is loaded with the 8-bit literal 'k'. The program                                       | Status Affected: | $0 \rightarrow \overline{PD}$<br>TO, PD, RBWUF                                                                    |  |

|                  | counter is loaded from the top of<br>the stack (the return address). This<br>is a 2-cycle instruction. | Description:     | Time-out Status bit (TO) <u>is s</u> et. The<br>Power-down Status bit (PD) is<br>cleared.<br>RBWUF is unaffected. |  |

|                  |                                                                                                        |                  | The WDT and its prescaler are<br>cleared.                                                                         |  |

|                  |                                                                                                        |                  | The processor is put into Sleep mode with the oscillator stopped.                                                 |  |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RLF f,d |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'.<br>$\carrow \carrow \carr$ |         |  |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                      |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                  |

| Status Affected: | C, DC, Z                                                                                                                                                                                        |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is '0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

See Section 9.9 "Power-down Mode (Sleep)" for more details.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                       |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                            |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                         |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                          |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is placed in register 'f'. |

# 11.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 11.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 11.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 11.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

| DC CH         | DC CHARACTERISTICS |                                               |       | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +85°C (industrial) |      |       |                      |  |  |

|---------------|--------------------|-----------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------|--|--|

| Param.<br>No. | Sym.               | Characteristic                                | Min.  | Тур. <sup>(1)</sup>                                                                                                           | Max. | Units | Conditions           |  |  |

| D001          | Vdd                | Supply Voltage                                | 2.0   |                                                                                                                               | 5.5  | V     | See Figure 12-1      |  |  |

| D002          | Vdr                | RAM Data Retention Voltage <sup>(2)</sup>     | 1.5*  |                                                                                                                               |      | V     | Device in Sleep mode |  |  |

| D003          | Vpor               | VDD Start Voltage<br>to ensure Power-on Reset | —     | Vss                                                                                                                           | —    | V     |                      |  |  |

| D004          | SVDD               | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05* | —                                                                                                                             | —    | V/ms  |                      |  |  |

|               | Idd                | Supply Current <sup>(3)</sup>                 |       |                                                                                                                               |      |       |                      |  |  |

| D010          |                    |                                               | —     | 175                                                                                                                           | 275  | μΑ    | VDD = 2.0V           |  |  |

|               |                    |                                               | —     | 0.63                                                                                                                          | 1.1  | mA    | VDD = 5.0V           |  |  |

|               | IPD                | Power-down Current <sup>(4)</sup>             |       |                                                                                                                               |      |       |                      |  |  |

| D020          |                    |                                               | -     | 0.1                                                                                                                           | 1.2  | μΑ    | VDD = 2.0V           |  |  |

|               |                    |                                               | —     | 0.35                                                                                                                          | 2.4  | μA    | VDD = 5.0V           |  |  |

|               | IWDT               | WDT Current <sup>(5)</sup>                    |       |                                                                                                                               |      |       |                      |  |  |

| D022          |                    |                                               | -     | 1.0                                                                                                                           | 3    | μΑ    | VDD = 2.0V           |  |  |

|               |                    |                                               | —     | 7                                                                                                                             | 16   | μA    | VDD = 5.0V           |  |  |

|               | ICMP               | Comparator Current <sup>(5)</sup>             |       |                                                                                                                               |      |       |                      |  |  |

| D023          |                    |                                               | —     | 12                                                                                                                            | 23   | μΑ    | VDD = 2.0V           |  |  |

|               |                    |                                               | —     | 44                                                                                                                            | 80   | μΑ    | VDD = 5.0V           |  |  |

|               | IVREF              | Internal Reference Current <sup>(5,6)</sup>   |       |                                                                                                                               |      |       |                      |  |  |

| D024          |                    |                                               | —     | 85                                                                                                                            | 115  | μΑ    | VDD = 2.0V           |  |  |

|               |                    |                                               |       | 175                                                                                                                           | 195  | μA    | VDD = 5.0V           |  |  |

#### 12.1 DC Characteristics: PIC10F200/202/204/206 (Industrial)

These parameters are characterized but not tested.

- **Note 1:** Data in the Typical ("Typ.") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are:

- All I/O pins tri-stated, pulled to VSS, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified. b) For standby current measurements, the conditions are the same, except that the device is in Sleep

- mode.

- 4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS.

- **5:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled.

- 6: Measured with the comparator enabled.

### 12.2 DC Characteristics: PIC10F200/202/204/206 (Extended)

| DC CHA        | DC CHARACTERISTICS |                                               |       |                     | Standard Operating Conditions (unless otherwise specified)Operating Temperature -40°C $\leq$ TA $\leq$ +125°C (extended) |          |                          |  |  |  |  |

|---------------|--------------------|-----------------------------------------------|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|--|--|--|--|

| Param.<br>No. | Sym.               | Characteristic                                | Min.  | Тур. <sup>(1)</sup> | Max.                                                                                                                     | Units    | Conditions               |  |  |  |  |

| D001          | Vdd                | Supply Voltage                                | 2.0   |                     | 5.5                                                                                                                      | V        | See Figure 12-1          |  |  |  |  |

| D002          | Vdr                | RAM Data Retention<br>Voltage <sup>(2)</sup>  | 1.5*  |                     | _                                                                                                                        | V        | Device in Sleep mode     |  |  |  |  |

| D003          | VPOR               | VDD Start Voltage<br>to ensure Power-on Reset | —     | Vss                 | _                                                                                                                        | V        |                          |  |  |  |  |

| D004          | SVDD               | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05* | —                   | _                                                                                                                        | V/ms     |                          |  |  |  |  |

|               | Idd                | Supply Current <sup>(3)</sup>                 |       |                     |                                                                                                                          |          |                          |  |  |  |  |

| D010          |                    |                                               | _     | 175<br>0.63         | 275<br>1.1                                                                                                               | μA<br>mA | VDD = 2.0V<br>VDD = 5.0V |  |  |  |  |

|               | IPD                | Power-down Current <sup>(4)</sup>             |       |                     |                                                                                                                          |          |                          |  |  |  |  |

| D020          |                    |                                               | _     | 0.1<br>0.35         | 9<br>15                                                                                                                  | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |  |

|               | IWDT               | WDT Current <sup>(5)</sup>                    |       |                     |                                                                                                                          |          |                          |  |  |  |  |

| D022          |                    |                                               | _     | 1.0<br>7            | 18<br>22                                                                                                                 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |  |

|               | ICMP               | Comparator Current <sup>(5)</sup>             |       | 1                   |                                                                                                                          | 1        |                          |  |  |  |  |

| D023          |                    |                                               |       | 12<br>42            | 27<br>85                                                                                                                 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |  |

|               | VREF               | Internal Reference Current <sup>(5,6</sup>    | 5)    |                     |                                                                                                                          |          |                          |  |  |  |  |

| D024          |                    |                                               | —     | 85<br>175           | 120<br>200                                                                                                               | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |  |  |  |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are: All I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

- 4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS.

- **5:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled.

- 6: Measured with the Comparator enabled.

#### TABLE 12-4: RESET, WATCHDOG TIMER AND DEVICE RESET TIMER – PIC10F200/202/204/206

| AC CHARACTERISTICS |                     |                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)}\\ \mbox{Operating Temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)}\\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)}\\ \mbox{Operating Voltage VDD range is described in Section 12.1 "DC Characteristics: PIC10F200/202/204/206 \mbox{ (Industrial)}"\\ \end{array}$ |                     |          |          |                                                  |  |

|--------------------|---------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------|----------|--------------------------------------------------|--|

| Param.<br>No.      | Svm. Characteristic |                                                  |                                                                                                                                                                                                                                                                                                                                                                                                  | Тур. <sup>(1)</sup> | Max.     | Units    | Conditions                                       |  |

| 30                 | Тмс <sub>L</sub>    | MCLR Pulse Width (low)                           | 2*<br>5*                                                                                                                                                                                                                                                                                                                                                                                         | _                   |          | μS<br>μS | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |  |

| 31                 | Twdt                | Watchdog Timer Time-out<br>Period (no prescaler) | 10<br>10                                                                                                                                                                                                                                                                                                                                                                                         | 16<br>16            | 29<br>31 | ms<br>ms | VDD = 5.0V (industrial)<br>VDD = 5.0V (extended) |  |

| 32                 | Tdrt                | Device Reset Timer Period (standard)             | 10<br>10                                                                                                                                                                                                                                                                                                                                                                                         | 16<br>16            | 29<br>31 | ms<br>ms | VDD = 5.0V (industrial)<br>VDD = 5.0V (extended) |  |

| 34                 | Tioz                | I/O High-impedance from MCLR low                 | _                                                                                                                                                                                                                                                                                                                                                                                                | _                   | 2*       | μS       |                                                  |  |

\* These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

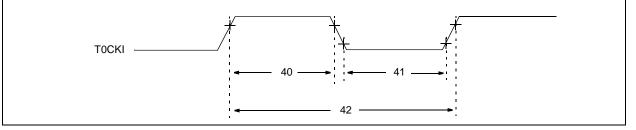

#### FIGURE 12-4: TIMER0 CLOCK TIMINGS – PIC10F200/202/204/206

#### TABLE 12-5: TIMER0 CLOCK REQUIREMENTS - PIC10F200/202/204/206

| AC CHARACTERISTICS |      |                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                 |      |       |            |                                                                |  |

|--------------------|------|------------------|------------------------------------------------------|---------------------------------|------|-------|------------|----------------------------------------------------------------|--|

| Param.<br>No.      | Sym. | Characte         | Min.                                                 | Тур. <sup>(1)</sup>             | Max. | Units | Conditions |                                                                |  |

| 40                 | Tt0H | T0CKI High Pulse | No Prescaler                                         | 0.5 Tcy + 20*                   | —    |       | ns         |                                                                |  |

|                    |      | Width            | With Prescaler                                       | 10*                             | _    |       | ns         |                                                                |  |

| 41                 | Tt0L | T0CKI Low Pulse  | No Prescaler                                         | 0.5 TCY + 20*                   | —    | _     | ns         |                                                                |  |

|                    |      | Width            | With Prescaler                                       | 10*                             | —    | _     | ns         |                                                                |  |

| 42                 | Tt0P | T0CKI Period     |                                                      | 20 or $\frac{T_{CY} + 40^*}{N}$ | —    |       | ns         | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

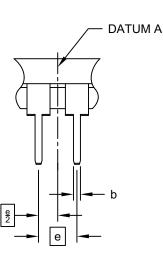

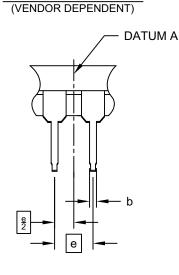

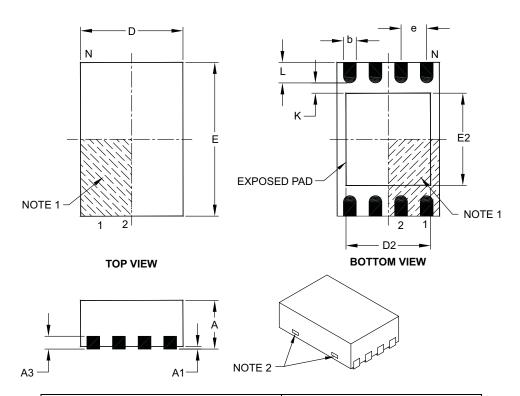

# 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

ALTERNATE LEAD DESIGN

| Units                      |    | INCHES   |      |      |

|----------------------------|----|----------|------|------|

| Dimension Limits           |    | MIN      | NOM  | MAX  |

| Number of Pins             | N  |          | 8    |      |

| Pitch                      | е  | .100 BSC |      |      |

| Top to Seating Plane       | Α  | -        | -    | .210 |

| Molded Package Thickness   | A2 | .115     | .130 | .195 |

| Base to Seating Plane      | A1 | .015     | -    | -    |

| Shoulder to Shoulder Width | E  | .290     | .310 | .325 |

| Molded Package Width       | E1 | .240     | .250 | .280 |