Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 010110                   |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 3                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 24 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f206t-e-ot |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

By executing the OPTION instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

#### **REGISTER 4-2: OPTION REGISTER**

| Note: | If TRIS bit is set to '0', the wake-up on    |  |  |  |

|-------|----------------------------------------------|--|--|--|

|       | change and pull-up functions are disabled    |  |  |  |

|       | for that pin (i.e., note that TRIS overrides |  |  |  |

|       | Option control of GPPU and GPWU).            |  |  |  |

Note: If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

| W-1         | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1 |

|-------------|------|------|------|-----|-----|-----|-----|

| GPWU        | GPPU | T0CS | T0SE | PSA | PS2 | PS1 | PS0 |

| bit 7 bit 0 |      |      |      |     |     |     |     |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

1:16

1:32

1:64

1:128

| 1 :     |                                                               |  |  |  |  |  |  |

|---------|---------------------------------------------------------------|--|--|--|--|--|--|

| bit 7   | <b>GPWU:</b> Enable Wake-up on Pin Change bit (GP0, GP1, GP3) |  |  |  |  |  |  |

|         | 1 = Disabled                                                  |  |  |  |  |  |  |

|         | 0 = Enabled                                                   |  |  |  |  |  |  |

| bit 6   | GPPU: Enable Weak Pull-ups bit (GP0, GP1, GP3)                |  |  |  |  |  |  |

|         | 1 = Disabled                                                  |  |  |  |  |  |  |

|         | 0 = Enabled                                                   |  |  |  |  |  |  |

| bit 5   | TOCS: Timer0 Clock Source Select bit                          |  |  |  |  |  |  |

|         | 1 = Transition on T0CKI pin (overrides TRIS on the T0CKI pin) |  |  |  |  |  |  |

|         | 0 = Transition on internal instruction cycle clock, Fosc/4    |  |  |  |  |  |  |

| bit 4   | T0SE: Timer0 Source Edge Select bit                           |  |  |  |  |  |  |

|         | 1 = Increment on high-to-low transition on the TOCKI pin      |  |  |  |  |  |  |

|         | 0 = Increment on low-to-high transition on the T0CKI pin      |  |  |  |  |  |  |

| bit 3   | PSA: Prescaler Assignment bit                                 |  |  |  |  |  |  |

|         | 1 = Prescaler assigned to the WDT                             |  |  |  |  |  |  |

|         | 0 = Prescaler assigned to Timer0                              |  |  |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                           |  |  |  |  |  |  |

|         | Bit Value Timer0 Rate WDT Rate                                |  |  |  |  |  |  |

|         | 000 1:2 1:1                                                   |  |  |  |  |  |  |

|         | 001 1:4 1:2                                                   |  |  |  |  |  |  |

|         | 010 1:8 1:4                                                   |  |  |  |  |  |  |

|         | 011 1:16 1:8                                                  |  |  |  |  |  |  |

1:32

1:64

1 : 128 1 : 256

100

101

110 111

### 6.0 TIMER0 MODULE AND TMR0 REGISTER (PIC10F200/202)

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select:

- Edge select for external clock

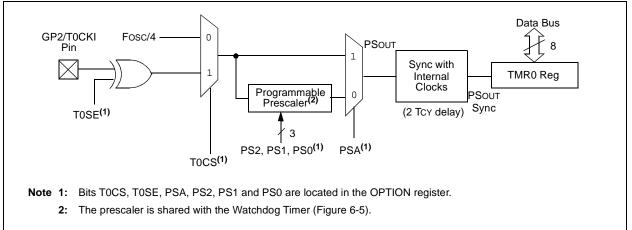

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the T0CS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 with an External Clock (PIC10F200/202)".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit, PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, 1:256 are selectable. **Section 6.2 "Prescaler**" details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

#### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| Program<br>Counter)    | PC - 1           | Y PC             | PC + 1      | ( PC + 2 )             | PC + 3                 | (PC + 4)               | ( PC + 5 )                 | PC + 6                     |

|------------------------|------------------|------------------|-------------|------------------------|------------------------|------------------------|----------------------------|----------------------------|

| nstruction<br>Fetch    | 1                | MOVWF TMR0       | MOVF TMR0,W | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W            | MOVF TMR0,W                |                            |

| limer0                 | (Υ               | T0 + 1 χ         | T0 + 2      |                        | NT0 X                  | χ                      | NT0 + 1)                   | NT0 + 2                    |

| nstruction<br>Executed | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | Write TMR0  | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 + 2 |

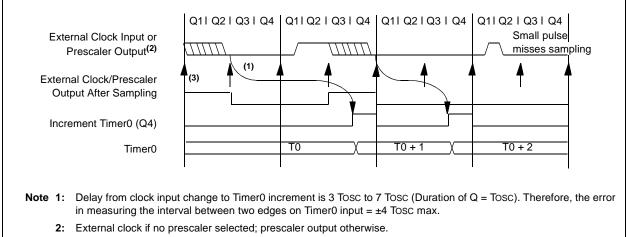

#### 7.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 7-4 shows the delay from the external clock edge to the timer incrementing.

**3:** The arrows indicate the points in time where sampling occurs.

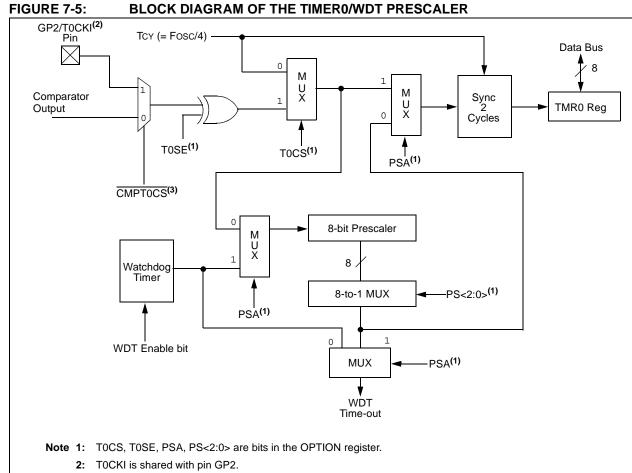

#### 7.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see Figure 9-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|

|       | Timer0 module or the WDT, but not both. |  |  |  |  |  |  |

|       | Thus, a prescaler assignment for the    |  |  |  |  |  |  |

|       | Timer0 module means that there is no    |  |  |  |  |  |  |

|       | prescaler for the WDT and vice versa.   |  |  |  |  |  |  |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

#### 7.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

| EXAMPLE 7-1: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (TIMER0 $\rightarrow$ WDT) |

| CLRWDT | ;Clear WDT                          |

|--------|-------------------------------------|

| CLRF   | TMR0 ;Clear TMR0 & Prescaler        |

| MOVLW  | `00xx1111'b;These 3 lines (5, 6, 7) |

| OPTION | ;are required only if               |

|        | ;desired                            |

| CLRWDT | ;PS<2:0> are 000 or 001             |

| MOVLW  | '00xx1xxx'b;Set Postscaler to       |

| OPTION | ;desired WDT rate                   |

|        |                                     |

To change the prescaler from the WDT to the Timer0 module, use the sequence shown in Example 7.2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT→TIMER0)

|        |            | · /                 |

|--------|------------|---------------------|

| CLRWDT |            | ;Clear WDT and      |

|        |            | ;prescaler          |

| MOVLW  | `xxxx0xxx' | ;Select TMR0, new   |

|        |            | ;prescale value and |

|        |            | ;clock source       |

| OPTION |            |                     |

|        |            |                     |

3: Bit CMPT0CS is located in the CMCON0 register.

### 8.0 COMPARATOR MODULE

The comparator module contains one Analog comparator. The inputs to the comparator are multiplexed with GP0 and GP1 pins. The output of the comparator can be placed on GP2.

The CMCON0 register, shown in Register 8-1, controls the comparator operation. A block diagram of the comparator is shown in Figure 8-1.

#### REGISTER 8-1: CMCON0 REGISTER

| R-1         | R/W-1  | R/W-1 | R/W-1   | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------|--------|-------|---------|-------|-------|-------|-------|

| CMPOUT      | COUTEN | POL   | CMPT0CS | CMPON | CNREF | CPREF | CWU   |

| bit 7 bit 0 |        |       |         |       |       |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| I | oit 7         | CMPOUT: Comparator Output bit                                                                                          |

|---|---------------|------------------------------------------------------------------------------------------------------------------------|

|   |               | 1 = VIN + > VIN-                                                                                                       |

|   |               | 0 = VIN + < VIN - (4.2)                                                                                                |

| I | oit 6         | <b>COUTEN:</b> Comparator Output Enable bit <sup>(1, 2)</sup>                                                          |

|   |               | 1 = Output of comparator is NOT placed on the COUT pin                                                                 |

|   |               | 0 = Output of comparator is placed in the COUT pin                                                                     |

| 1 | oit 5         | POL: Comparator Output Polarity bit <sup>(2)</sup>                                                                     |

|   |               | <ul> <li>1 = Output of comparator not inverted</li> <li>0 = Output of comparator inverted</li> </ul>                   |

|   | oit 4         | CMPT0CS: Comparator TMR0 Clock Source bit <sup>(2)</sup>                                                               |

| 1 | JIL 4         | 1 = TMR0 clock source selected by T0CS control bit                                                                     |

|   |               | 0 = Comparator output used as TMR0 clock source                                                                        |

| I | oit 3         | CMPON: Comparator Enable bit                                                                                           |

|   |               | 1 = Comparator is on                                                                                                   |

|   |               | 0 = Comparator is off                                                                                                  |

| I | oit 2         | CNREF: Comparator Negative Reference Select bit <sup>(2)</sup>                                                         |

|   |               | 1 = CIN- pin <sup>(3)</sup>                                                                                            |

|   |               | 0 = Internal voltage reference                                                                                         |

| I | oit 1         | <b>CPREF:</b> Comparator Positive Reference Select bit <sup>(2)</sup>                                                  |

|   |               | $1 = \text{CIN} + \text{pin}^{(3)}$                                                                                    |

|   |               | $0 = \text{CIN-pin}^{(3)}$                                                                                             |

| 1 | oit 0         | <b>CWU:</b> Comparator Wake-up on Change Enable bit <sup>(2)</sup>                                                     |

|   |               | <ul> <li>1 = Wake-up on comparator change is disabled</li> <li>0 = Wake-up on comparator change is enabled.</li> </ul> |

|   | Note 1:       | Overrides T0CS bit for TRIS control of GP2.                                                                            |

|   | 101e 1.<br>2: | When the comparator is turned on, these control bits assert themselves. When the comparator is off, these              |

|   | ۷.            | bits have no effect on the device operation and the other control registers have precedence.                           |

|   | 3:            | PIC10F204/206 only.                                                                                                    |

**3:** PIC10F204/206 only.

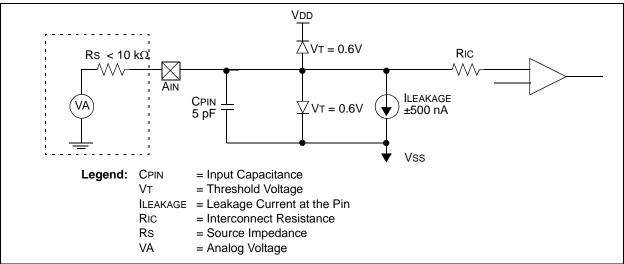

#### FIGURE 8-3: ANALOG INPUT MODE

| Address | Name     | Bit 7  | Bit 6  | Bit 5 | Bit 4   | Bit 3     | Bit 2      | Bit 1 | Bit 0 | Value on<br>POR | Value on<br>All Other<br>Resets |

|---------|----------|--------|--------|-------|---------|-----------|------------|-------|-------|-----------------|---------------------------------|

| 03h     | STATUS   | GPWUF  | CWUF   | _     | TO      | PD        | Z          | DC    | С     | 00-1 1xxx       | qq0q quuu                       |

| 07h     | CMCON0   | CMPOUT | COUTEN | POL   | CMPT0CS | CMPON     | CNREF      | CPREF | CWU   | 1111 1111       | uuuu uuuu                       |

| N/A     | TRISGPIO | —      | _      | _     | —       | I/O Contr | ol Registe | er    |       | 1111            | 1111                            |

**Legend:** x = Unknown, u = Unchanged, - = Unimplemented, read as '0', q = Depends on condition.

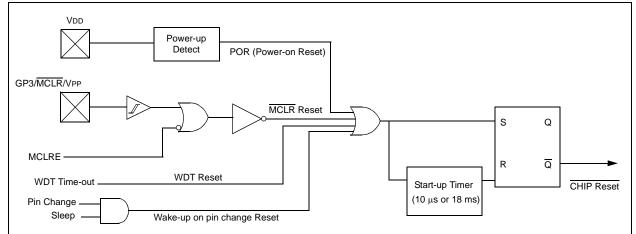

#### FIGURE 9-2: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

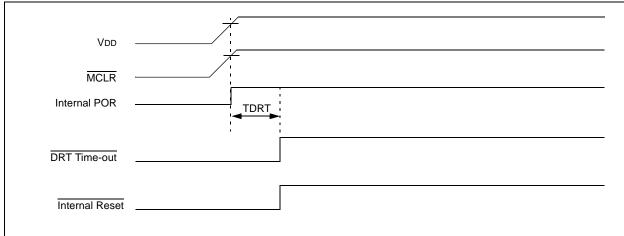

#### FIGURE 9-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

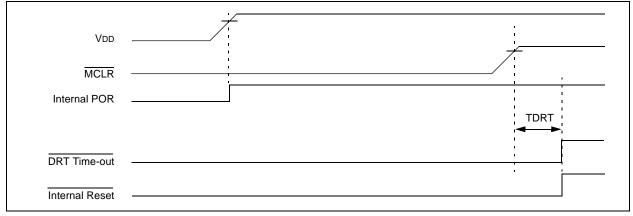

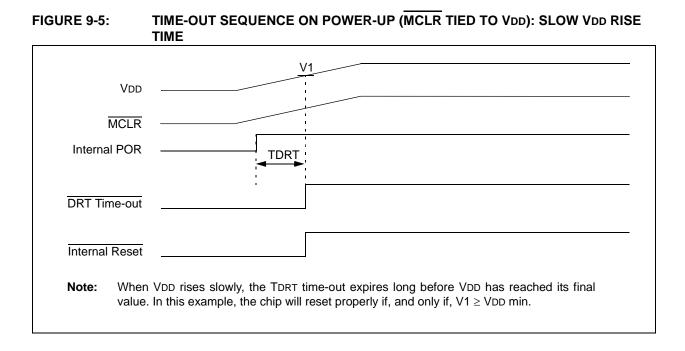

### 9.5 Device Reset Timer (DRT)

On the PIC10F200/202/204/206 devices, the DRT runs any time the device is powered-up.

The DRT operates on an internal oscillator. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

The on-chip DRT keeps the devices in a Reset condition for approximately 18 ms after MCLR has reached a logic high (VIH MCLR) level. Programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases. This allows savings in cost-sensitive and/ or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset Time delays will vary from chip-tochip due to VDD, temperature and process variation. See AC parameters for details.

Reset sources are POR, MCLR, WDT time-out and wake-up on pin change. See **Section 9.9.2** "**Wake-up from Sleep**", Notes 1, 2 and 3.

TABLE 9-3: DRT PERIOD

| Oscillator | POR Reset       | Subsequent<br>Resets |  |

|------------|-----------------|----------------------|--|

| INTOSC     | 18 ms (typical) | 10 μs (typical)      |  |

### 9.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the internal 4 MHz oscillator. This means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or Sleep, a WDT Reset or wake-up Reset, generates a device Reset.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset.

The WDT can be permanently disabled by programming the configuration WDTE as a '0' (see **Section 9.1 "Configuration Bits"**). Refer to the PIC10F200/202/204/206 Programming Specifications to determine how to access the Configuration Word.

### 9.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst-case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 9.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device Reset.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum Sleep time before a WDT wake-up Reset.

### 9.7 Time-out Sequence, Power-down and <u>Wake-up</u> from Sleep Status Bits (TO, PD, GPWUF, CWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , GPWUF and CWUF bits in the STATUS register can be tested to determine if a Reset condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$ , Watchdog Timer (WDT) Reset, wake-up on comparator change or wake-up on pin change.

# TABLE 9-5: TO, PD, GPWUF, CWUF STATUS AFTER RESET

| CWUF | GPWUF | то | PD | Reset Caused By                         |

|------|-------|----|----|-----------------------------------------|

| 0    | 0     | 0  | 0  | WDT wake-up from Sleep                  |

| 0    | 0     | 0  | u  | WDT time-out (not from Sleep)           |

| 0    | 0     | 1  | 0  | MCLR wake-up from Sleep                 |

| 0    | 0     | 1  | 1  | Power-up                                |

| 0    | 0     | u  | u  | MCLR not during Sleep                   |

| 0    | 1     | 1  | 0  | Wake-up from Sleep on pin change        |

| 1    | 0     | 1  | 0  | Wake-up from Sleep on comparator change |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: The TO, PD, GPWUF and CWUF bits maintain their status (u) until a Reset occurs. A low-pulse on the MCLR input does not change the TO, PD, GPWUF or CWUF Status bits.

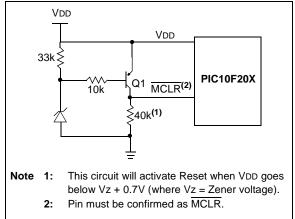

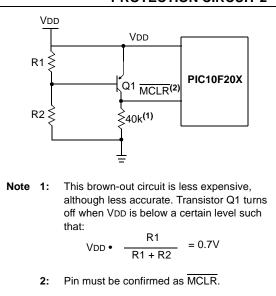

### 9.8 Reset on Brown-out

A Brown-out Reset is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

To reset PIC10F200/202/204/206 devices when a Brown-out Reset occurs, external brown-out protection circuits may be built, as shown in Figure 9-7 and Figure 9-8.

#### FIGURE 9-7: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 9-8: BROWN-OUT PROTECTION CIRCUIT 2

| ADDWF            | Add W and f                                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ADDWF f,d                                                                                                                                                               |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                        |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                                    |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                          |  |  |  |

| Description:     | Add the contents of the W register<br>and register 'f'. If 'd' is '0', the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |  |  |  |

| BCF              | Bit Clear f                                                        |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [label] BCF f,b                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                          |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is cleared.                                |

| ANDLW            | AND literal with W                                                                                            |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                      |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |

| Operation:       | (W).AND. (k) $\rightarrow$ (W)                                                                                |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |

| Description:     | The contents of the W register are AND'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |

| BSF              | Bit Set f                                                          |

|------------------|--------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                          |

| Status Affected: | None                                                               |

| Description:     | Bit 'b' in register 'f' is set.                                    |

| ANDWF            | AND W with f                                                                                                                                                                              |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                                                         |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                            |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                                                                                         |  |  |  |

| Description:     | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is '0',<br>the result is stored in the W register.<br>If 'd' is '1', the result is stored back<br>in register 'f'. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                    |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] BTFSC f,b                                                                                                                                                                            |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                           |  |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                         |  |  |

| Status Affected: | None                                                                                                                                                                                         |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next instruction is skipped.                                                                                                                     |  |  |

|                  | If bit 'b' is '0', then the next<br>instruction fetched during the<br>current instruction execution is<br>discarded, and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |  |  |

| RETLW            | Return with literal in W                                                                               | SLEEP            | Enter SLEEP Mode                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                               | Syntax:          | [ label ] SLEEP                                                                                       |

| Operands:        | $0 \leq k \leq 255$                                                                                    | Operands:        | None                                                                                                  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                           | Operation:       | 00h $\rightarrow$ WDT;<br>0 $\rightarrow$ WDT prescaler;                                              |

| Status Affected: | None                                                                                                   |                  | $1 \rightarrow \overline{\text{TO}};$                                                                 |

| Description:     | The W register is loaded with the 8-bit literal 'k'. The program                                       | Status Affected: | $0 \rightarrow \overline{PD}$<br>TO, PD, RBWUF                                                        |

|                  | counter is loaded from the top of<br>the stack (the return address). This<br>is a 2-cycle instruction. | Description:     | Time-out Status bit $(\overline{TO})$ is set. The Power-down Status bit $(\overline{PD})$ is cleared. |

|                  |                                                                                                        |                  | RBWUF is unaffected.                                                                                  |

|                  |                                                                                                        |                  | The WDT and its prescaler are<br>cleared.                                                             |

|                  |                                                                                                        |                  | The processor is put into Sleep mode with the oscillator stopped.                                     |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                          |     |     |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                            | RLF | f,d |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                       |     |     |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                |     |     |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |     |     |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is stored back in<br>register 'f'. |     |     |  |  |  |  |

| SUBWF            | Subtract W from f                                                                                                                                                                               |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                  |  |  |  |  |  |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                        |  |  |  |  |  |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is '0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |

See Section 9.9 "Power-down Mode (Sleep)" for more details.

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                            |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

|                  | C register 'f'                                                                                                                                                                                                        |  |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                         |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                          |  |  |  |  |

| Status Affected: | None                                                                                                                                                               |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |  |

# 12.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                         | 40°C to +125°C                     |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                    | 65°C to +150°C                     |

| Voltage on VDD with respect to Vss                                                                                     | 0 to +6.5V                         |

| Voltage on MCLR with respect to Vss                                                                                    | 0 to +13.5V                        |

| Voltage on all other pins with respect to Vss                                                                          | 0.3V to (VDD + 0.3V)               |

| Total power dissipation <sup>(1)</sup>                                                                                 | 800 mW                             |

| Max. current out of Vss pin                                                                                            | 80 mA                              |

| Max. current into Vod pin                                                                                              | 80 mA                              |

| Input clamp current, Iк (VI < 0 or VI > VDD)                                                                           | ±20 mA                             |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                                                         | ±20 mA                             |

| Max. output current sunk by any I/O pin                                                                                | 25 mA                              |

| Max. output current sourced by any I/O pin                                                                             | 25 mA                              |

| Max. output current sourced by I/O port                                                                                | 75 mA                              |

| Max. output current sunk by I/O port                                                                                   | 75 mA                              |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-\Sigma$ | Voh) x Ioh} + $\Sigma$ (Vol x Iol) |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

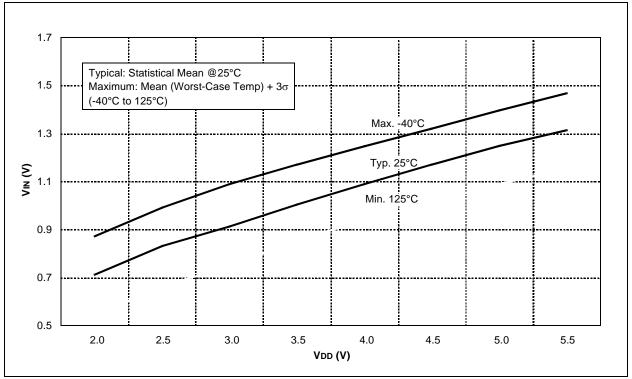

#### 12.2 DC Characteristics: PIC10F200/202/204/206 (Extended)

| DC CHARACTERISTICS |      |                                               | Standard Operating Conditions (unless otherwise specified)Operating Temperature -40°C $\leq$ TA $\leq$ +125°C (extended) |                     |            |          |                          |

|--------------------|------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------|------------|----------|--------------------------|

| Param.<br>No.      | Sym. | Characteristic                                | Min.                                                                                                                     | Тур. <sup>(1)</sup> | Max.       | Units    | Conditions               |

| D001               | Vdd  | Supply Voltage                                | 2.0                                                                                                                      |                     | 5.5        | V        | See Figure 12-1          |

| D002               | Vdr  | RAM Data Retention<br>Voltage <sup>(2)</sup>  | 1.5*                                                                                                                     |                     | —          | V        | Device in Sleep mode     |

| D003               | VPOR | VDD Start Voltage<br>to ensure Power-on Reset | —                                                                                                                        | Vss                 | —          | V        |                          |

| D004               | SVDD | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05*                                                                                                                    | —                   | —          | V/ms     |                          |

|                    | Idd  | Supply Current <sup>(3)</sup>                 |                                                                                                                          | 1                   |            |          |                          |

| D010               |      |                                               | _                                                                                                                        | 175<br>0.63         | 275<br>1.1 | μA<br>mA | VDD = 2.0V<br>VDD = 5.0V |

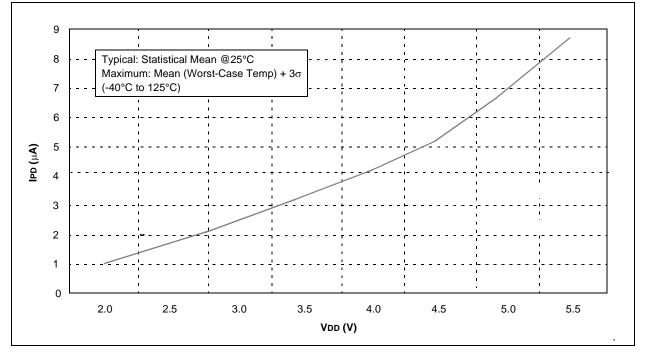

|                    | IPD  | Power-down Current <sup>(4)</sup>             |                                                                                                                          | 1                   |            |          |                          |

| D020               |      |                                               | _                                                                                                                        | 0.1<br>0.35         | 9<br>15    | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |

|                    | Iwdt | WDT Current <sup>(5)</sup>                    |                                                                                                                          | 1                   |            |          |                          |

| D022               |      |                                               | _                                                                                                                        | 1.0<br>7            | 18<br>22   | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |

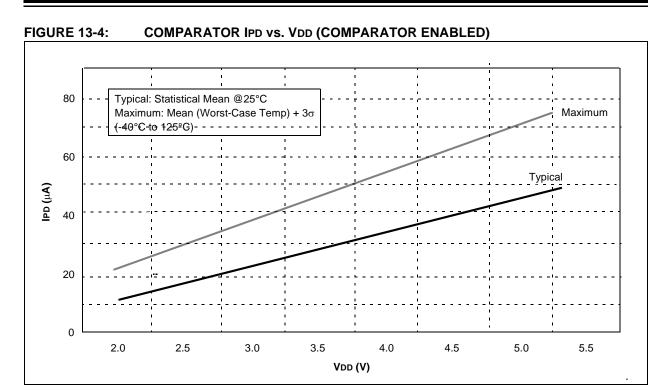

|                    | Ісмр | Comparator Current <sup>(5)</sup>             |                                                                                                                          | 1                   |            | 1        |                          |

| D023               |      |                                               | _                                                                                                                        | 12<br>42            | 27<br>85   | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |

|                    | VREF | Internal Reference Current <sup>(5,)</sup>    | 6)                                                                                                                       |                     |            |          |                          |

| D024               |      |                                               | —                                                                                                                        | 85<br>175           | 120<br>200 | μΑ<br>μΑ | VDD = 2.0V<br>VDD = 5.0V |

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ.") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- **3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are: All I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

- 4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS.

- **5:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled.

- 6: Measured with the Comparator enabled.

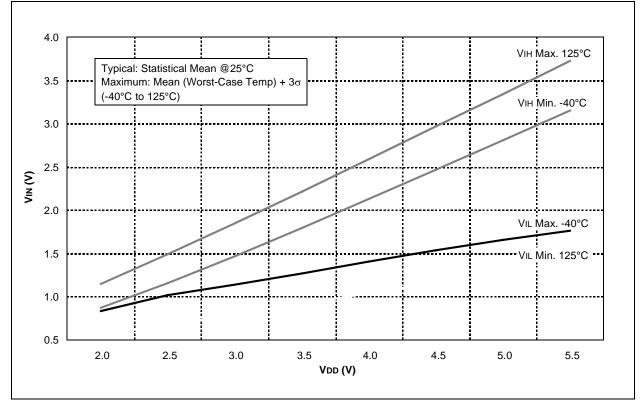

#### 12.3 DC Characteristics: PIC10F200/202/204/206 (Industrial, Extended)

| DC CHARACTERISTICS |      |                                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |             |       |                                                |

|--------------------|------|---------------------------------------------|------------------------------------------------------|-------|-------------|-------|------------------------------------------------|

| Param.<br>No.      | Sym. | Characteristic                              | Min.                                                 | Тур.† | Max.        | Units | Conditions                                     |

|                    | VIL  | Input Low Voltage                           |                                                      |       |             |       |                                                |

|                    |      | I/O ports:                                  |                                                      |       |             |       |                                                |

| D030               |      | with TTL buffer                             | Vss                                                  | —     | 0.8         | V     | For all $4.5V \le VDD \le 5.5V$                |

| D030A              |      |                                             | Vss                                                  | —     | 0.15<br>Vdd | V     |                                                |

| D031               |      | with Schmitt Trigger<br>buffer              | Vss                                                  | —     | 0.2 Vdd     | V     |                                                |

| D032               |      | MCLR, T0CKI                                 | Vss                                                  |       | 0.2 Vdd     | V     |                                                |

|                    | Vih  | Input High Voltage                          |                                                      |       |             |       |                                                |

|                    |      | I/O ports:                                  |                                                      |       |             |       |                                                |

| D040               |      | with TTL buffer                             | 2.0                                                  | —     | Vdd         | V     | $4.5V \leq V\text{DD} \leq 5.5V$               |

| D040A              |      |                                             | 0.25 VDD + 0.8                                       | —     | Vdd         | V     | Otherwise                                      |

| D041               |      | with Schmitt Trigger<br>buffer              | 0.8Vdd                                               | —     | Vdd         | V     | For entire VDD range                           |

| D042               |      | MCLR, TOCKI                                 | 0.8Vdd                                               | —     | Vdd         | V     |                                                |

| D070               | IPUR | GPIO weak pull-up<br>current <sup>(3)</sup> | 50                                                   | 250   | 400         | μA    | VDD = 5V, VPIN = VSS                           |

|                    | lı∟  | Input Leakage Current <sup>(1, 2</sup>      | 2)                                                   |       |             |       |                                                |

| D060               |      | I/O ports                                   | —                                                    | ±0.1  | ± 1         | μA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance |

| D061               |      | GP3/MCLR <sup>(3)</sup>                     | —                                                    | ±0.7  | ± 5         | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$       |

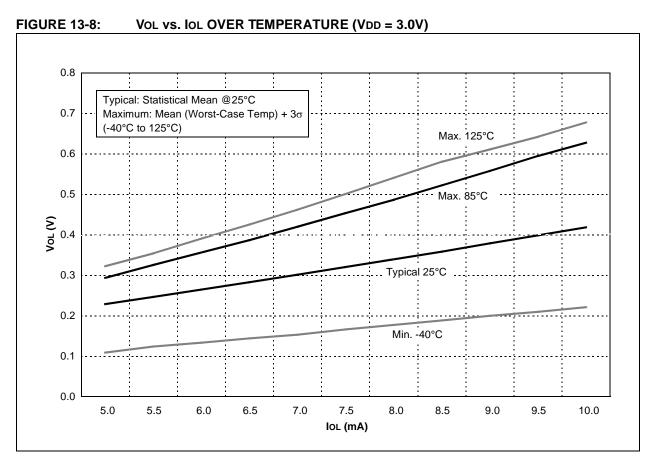

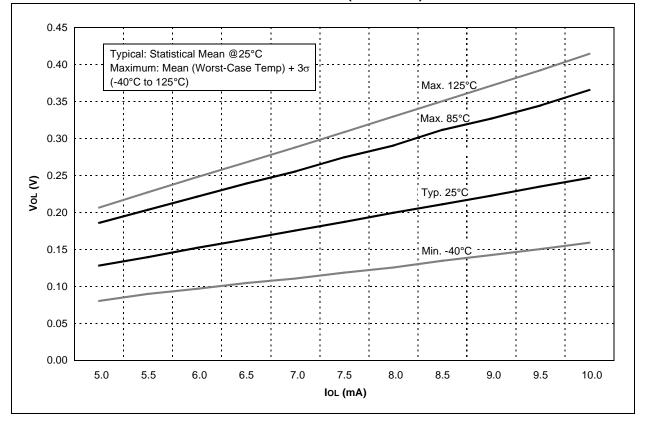

|                    |      | Output Low Voltage                          |                                                      |       |             |       |                                                |

| D080               |      | I/O ports                                   | —                                                    | —     | 0.6         | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C    |

| D080A              |      |                                             | —                                                    | —     | 0.6         | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C   |

|                    |      | Output High Voltage                         |                                                      |       |             |       |                                                |

| D090               |      | I/O ports <sup>(2)</sup>                    | VDD - 0.7                                            |       | _           | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C   |

| D090A              |      |                                             | Vdd - 0.7                                            | —     | —           | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C  |

|                    |      | Capacitive Loading Specs                    | s on Output Pins                                     |       |             |       |                                                |

| D101               |      | All I/O pins                                |                                                      |       | 50*         | pF    |                                                |

† Data in "Typ." column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

\* These parameters are for design guidance only and are not tested.

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**2:** Negative current is defined as coming out of the pin.

**3:** This specification applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

© 2004-2014 Microchip Technology Inc.

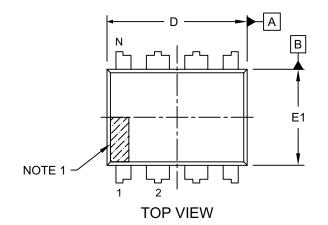

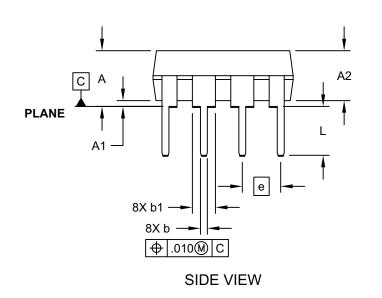

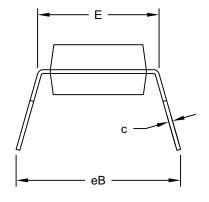

# 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**END VIEW**

Microchip Technology Drawing No. C04-018D Sheet 1 of 2

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support