Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8051                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 33MHz                                                                  |

| Connectivity               | EBI/EMI, UART/USART                                                    |

| Peripherals                | POR                                                                    |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 44-LCC (J-Lead)                                                        |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p80c32x2fa-512 |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

## **DESCRIPTION**

The Philips microcontrollers described in this data sheet are high-performance static 80C51 designs incorporating Philips' high-density CMOS technology with operation from 2.7 V to 5.5 V. They support both 6-clock and 12-clock operation.

The P8xC31X2/51X2 and P8xC32X2/52X2/54X2/58X2 contain 128 byte RAM and 256 byte RAM respectively, 32 I/O lines, three 16-bit counter/timers, a six-source, four-priority level nested interrupt structure, a serial I/O port for either multi-processor communications, I/O expansion or full duplex UART, and on-chip oscillator and clock circuits.

In addition, the devices are low power static designs which offer a wide range of operating frequencies down to zero. Two software

selectable modes of power reduction — idle mode and power-down mode — are available. The idle mode freezes the CPU while allowing the RAM, timers, serial port, and interrupt system to continue functioning. The power-down mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative. Since the design is static, the clock can be stopped without loss of user data. Then the execution can be resumed from the point the clock was stopped.

## **SELECTION TABLE**

For applications requiring more ROM and RAM, as well as more on-chip peripherals, see the P89C66x and P89C51Rx2 data sheets.

| Туре     |      | Mem | ory |       |             | Tim | ers |    | Se   | rial In | terfac | es  |              |          |                          |                     |                       |                        |                                                |                                  |                                  |

|----------|------|-----|-----|-------|-------------|-----|-----|----|------|---------|--------|-----|--------------|----------|--------------------------|---------------------|-----------------------|------------------------|------------------------------------------------|----------------------------------|----------------------------------|

|          | RAM  | ROM | OTP | Flash | # of Timers | PWM | PCA | WD | UART | 12C     | CAN    | SPI | ADC bits/ch. | I/O Pins | Interrupts<br>(External) | Program<br>Security | Default Clock<br>Rate | Optional<br>Clock Rate | Max.<br>Freq.<br>at 6-clk<br>/ 12-clk<br>(MHz) | Freq.<br>Range<br>at 3V<br>(MHz) | Freq.<br>Range<br>at 5V<br>(MHz) |

| P87C58X2 | 256B | -   | 32K | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P80C58X2 | 256B | 32K | -   | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P87C54X2 | 256B | -   | 16K | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P80C54X2 | 256B | 16K | -   | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P87C52X2 | 256B | -   | 8K  | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P80C52X2 | 256B | 8K  | -   | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P87C51X2 | 128B | -   | 4K  | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P80C51X2 | 128B | 4K  | -   | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | ~                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P80C32X2 | 256B | -   | -   | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | -                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

| P80C31X2 | 128B | -   | -   | -     | 3           | -   | -   | -  | ~    | -       | -      | -   | -            | 32       | 6 (2)                    | -                   | 12-clk                | 6-clk                  | 30/33                                          | 0–16                             | 0-30/33                          |

#### NOTE:

2003 Jan 24 2 853-2337 29260

<sup>1.</sup> I<sup>2</sup>C = Inter-Integrated Circuit Bus; CAN = Controller Area Network; SPI = Serial Peripheral Interface; PCA = Programmable Counter Array; ADC = Analog-to-Digital Converter; PWM = Pulse Width Modulation

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

# P80C3xX2; P80C5xX2; P87C5xX2

#### **FEATURES**

- 80C51 Central Processing Unit

- 4 kbytes ROM/EPROM (P80/P87C51X2)

- 8 kbytes ROM/EPROM (P80/P87C52X2)

- 16 kbytes ROM/EPROM (P80/P87C54X2)

- 32 kbytes ROM/EPROM (P80/P87C58X2)

- 128 byte RAM (P80/P87C51X2 and P80C31X2)

- 256 byte RAM (P80/P87C52/54X2/58X2 and P80C32X2)

- Boolean processor

- Fully static operation

- Low voltage (2.7 V to 5.5 V at 16 MHz) operation

- 12-clock operation with selectable 6-clock operation (via software or via parallel programmer)

- Memory addressing capability

- Up to 64 kbytes ROM and 64 kbytes RAM

- Power control modes:

- Clock can be stopped and resumed

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- Two speed ranges at V<sub>CC</sub> = 5 V

- 0 to 30 MHz with 6-clock operation

- 0 to 33 MHz with 12-clock operation

- PLCC, DIP, TSSOP or LQFP packages

- Extended temperature ranges

- Dual Data Pointers

- Security bits:

- ROM (2 bits)

- OTP (3 bits)

- Encryption array 64 bytes

- Four interrupt priority levels

- Six interrupt sources

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Three 16-bit timers/counters T0, T1 (standard 80C51) and additional T2 (capture and compare)

- Programmable clock-out pin

- Asynchronous port reset

- Low EMI (inhibit ALE, slew rate controlled outputs, and 6-clock mode)

- Wake-up from Power Down by an external interrupt.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

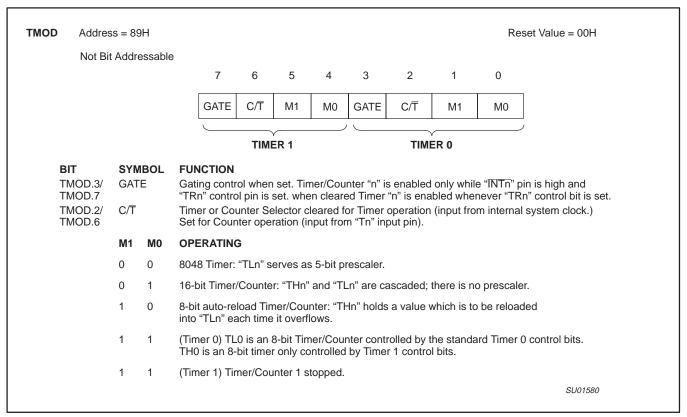

Figure 1. Timer/Counter 0/1 Mode Control (TMOD) Register

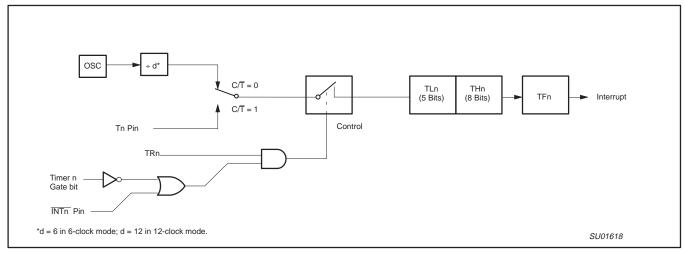

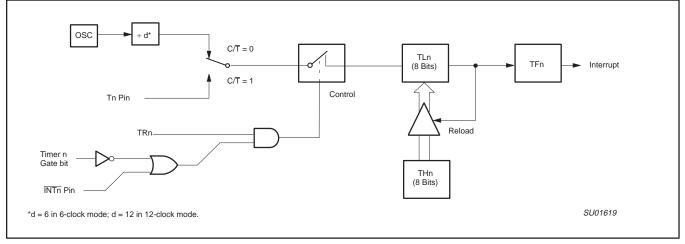

Figure 2. Timer/Counter 0/1 Mode 0: 13-Bit Timer/Counter

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

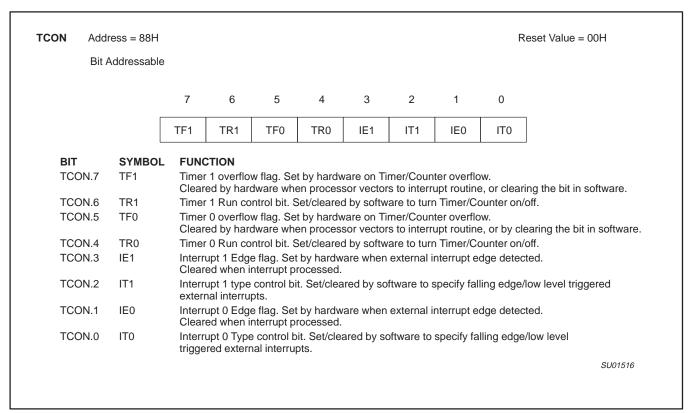

Figure 3. Timer/Counter 0/1 Control (TCON) Register

Figure 4. Timer/Counter 0/1 Mode 2: 8-Bit Auto-Reload

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

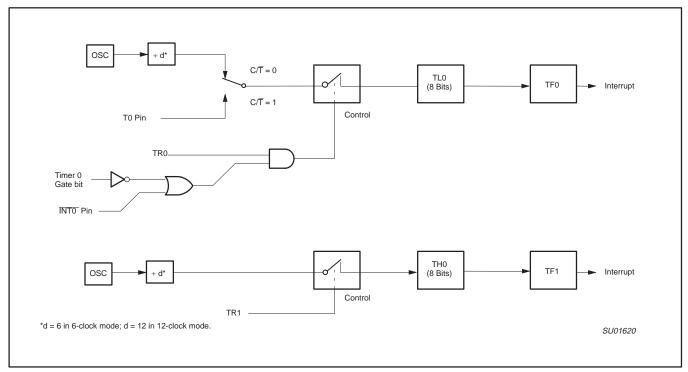

Figure 5. Timer/Counter 0 Mode 3: Two 8-Bit Counters

#### **TIMER 2 OPERATION**

## Timer 2

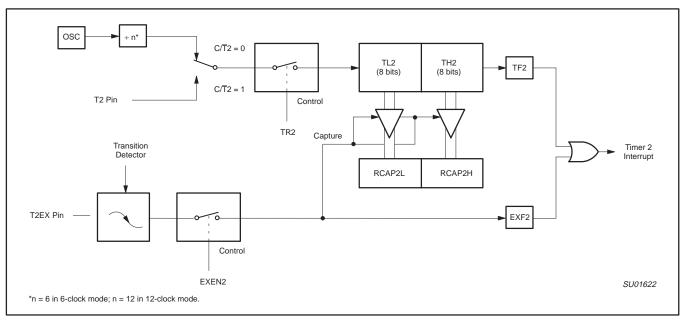

Timer 2 is a 16-bit Timer/Counter which can operate as either an event timer or an event counter, as selected by C/T2 in the special function register T2CON (see Figure 6). Timer 2 has three operating modes: Capture, Auto-reload (up or down counting), and Baud Rate Generator, which are selected by bits in the T2CON as shown in Table 4.

## **Capture Mode**

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2=0, then timer 2 is a 16-bit timer or counter (as selected by C/T2 in T2CON) which, upon overflowing, sets bit TF2, the timer 2 overflow bit. This bit can be used to generate an interrupt (by enabling the Timer 2 interrupt bit in the IE register). If EXEN2=1, Timer 2 operates as described above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2 (like TF2) can generate an interrupt (which vectors to the same location as Timer 2 overflow interrupt. The Timer 2 interrupt service routine can interrogate TF2 and EXF2 to determine which event caused the interrupt). The capture mode is illustrated in Figure 7 (There is no reload value for TL2 and TH2 in this mode. Even when a capture event occurs from T2EX, the counter keeps on counting T2EX pin transitions or osc/12 (12-clock Mode) or osc/6 (6-clock Mode) pulses).

## **Auto-Reload Mode (Up or Down Counter)**

In the 16-bit auto-reload mode, Timer 2 can be configured as either a timer or counter (C/T2 in T2CON), then programmed to count up or down. The counting direction is determined by bit DCEN (Down

Counter Enable) which is located in the T2MOD register (see Figure 8). After reset, DCEN=0 which means Timer 2 will default to counting up. If DCEN is set, Timer 2 can count up or down depending on the value of the T2EX pin.

Figure 9 shows Timer 2 which will count up automatically since DCEN=0. In this mode there are two options selected by bit EXEN2 in T2CON register. If EXEN2=0, then Timer 2 counts up to 0FFFFH and sets the TF2 (Overflow Flag) bit upon overflow. This causes the Timer 2 registers to be reloaded with the 16-bit value in RCAP2L and RCAP2H. The values in RCAP2L and RCAP2H are preset by software.

If EXEN2=1, then a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at input T2EX. This transition also sets the EXF2 bit. The Timer 2 interrupt, if enabled, can be generated when either TF2 or EXF2 are 1.

In Figure 10 DCEN=1 which enables Timer 2 to count up or down. This mode allows pin T2EX to control the direction of count. When a logic 1 is applied at pin T2EX, Timer 2 will count up. Timer 2 will overflow at 0FFFFH and set the TF2 flag, which can then generate an interrupt, if the interrupt is enabled. This timer overflow also causes the 16-bit value in RCAP2L and RCAP2H to be reloaded into the timer registers TL2 and TH2.

A logic 0 applied to pin T2EX causes Timer 2 to count down. The timer will underflow when TL2 and TH2 become equal to the value stored in RCAP2L and RCAP2H. A Timer 2 underflow sets the TF2 flag and causes 0FFFFH to be reloaded into the timer registers TL2 and TH2.

The external flag EXF2 toggles when Timer 2 underflows or overflows. This EXF2 bit can be used as a 17th bit of resolution if needed. The EXF2 flag does not generate an interrupt in this mode of operation.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

Figure 7. Timer 2 in Capture Mode

| T2MOD                                                                                                     | Address = 0       | СЭН     |                        |               |               |               |      | Reset va | lue = XXXX XX00E                         |

|-----------------------------------------------------------------------------------------------------------|-------------------|---------|------------------------|---------------|---------------|---------------|------|----------|------------------------------------------|

|                                                                                                           | Not Bit Addre     | essable |                        |               |               |               |      |          |                                          |

|                                                                                                           | 7                 | 6       | 5                      | 4             | 3             | 2             | 1    | 0        |                                          |

|                                                                                                           | _                 |         | _                      | _             | _             | _             | T2OE | DCEN     |                                          |

| Symbol                                                                                                    | Position          |         | Function  Not implemen | nted, reserve | ed for future | use.*         |      |          |                                          |

| T2OE                                                                                                      | T2MOD.1           |         | Гimer 2 Outp           | •             |               |               |      |          |                                          |

| DCEN T2MOD.0 Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/down counter. |                   |         |                        |               |               | as an up/down |      |          |                                          |

|                                                                                                           | ase, the reset or |         |                        |               |               |               |      |          | oke new features.<br>n a reserved bit is |

|                                                                                                           |                   |         |                        |               |               |               |      |          |                                          |

Figure 8. Timer 2 Mode (T2MOD) Control Register

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

## **FULL-DUPLEX ENHANCED UART**

## Standard UART operation

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the register. (However, if the first byte still hasn't been read by the time reception of the second byte is complete, one of the bytes will be lost.) The serial port receive and transmit registers are both accessed at Special Function Register SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register.

The serial port can operate in 4 modes:

Mode 0: Serial data enters and exits through RxD. TxD outputs the shift clock. 8 bits are transmitted/received (LSB first). The baud rate is fixed at 1/12 the oscillator frequency in 12-clock mode or 1/6 the oscillator frequency in 6-clock mode.

Mode 1: 10 bits are transmitted (through TxD) or received (through RxD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in Special Function Register SCON. The baud rate is variable.

Mode 2: 11 bits are transmitted (through TxD) or received (through RxD): start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On Transmit, the 9th data bit (TB8 in SCON) can be assigned the value of 0 or 1. Or, for example, the parity bit (P, in the PSW) could be moved into TB8. On receive, the 9th data bit goes into RB8 in Special Function Register SCON, while the stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency in 12-clock mode or 1/16 or 1/32 the oscillator frequency in 6-clock mode.

Mode 3: 11 bits are transmitted (through TxD) or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respects except baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. Reception is initiated in the other modes by the incoming start bit if REN = 1.

## **Multiprocessor Communications**

Modes 2 and 3 have a special provision for multiprocessor communications. In these modes, 9 data bits are received. The 9th one goes into RB8. Then comes a stop bit. The port can be programmed such that when the stop bit is received, the serial port interrupt will be activated only if RB8 = 1. This feature is enabled by setting bit SM2 in SCON. A way to use this feature in multiprocessor systems is as follows:

When the master processor wants to transmit a block of data to one of several slaves, it first sends out an address byte which identifies the target slave. An address byte differs from a data byte in that the 9th bit is 1 in an address byte and 0 in a data byte. With SM2 = 1, no slave will be interrupted by a data byte. An address byte, however, will interrupt all slaves, so that each slave can examine the received byte and see if it is being addressed. The addressed slave will clear its SM2 bit and prepare to receive the data bytes that will be coming.

The slaves that weren't being addressed leave their SM2s set and go on about their business, ignoring the coming data bytes.

SM2 has no effect in Mode 0, and in Mode 1 can be used to check the validity of the stop bit. In a Mode 1 reception, if SM2 = 1, the receive interrupt will not be activated unless a valid stop bit is received.

### **Serial Port Control Register**

The serial port control and status register is the Special Function Register SCON, shown in Figure 12. This register contains not only the mode selection bits, but also the 9th data bit for transmit and receive (TB8 and RB8), and the serial port interrupt bits (TI and RI).

#### **Baud Rates**

The baud rate in Mode 0 is fixed: Mode 0 Baud Rate = Oscillator Frequency / 12 (12-clock mode) or / 6 (6-clock mode). The baud rate in Mode 2 depends on the value of bit SMOD in Special Function Register PCON. If SMOD = 0 (which is the value on reset), and the port pins in 12-clock mode, the baud rate is 1/64 the oscillator frequency. If SMOD = 1, the baud rate is 1/32 the oscillator frequency. In 6-clock mode, the baud rate is 1/32 or 1/16 the oscillator frequency, respectively.

Mode 2 Baud Rate =

$$\frac{2^{\text{SMOD}}}{n} \times \text{(Oscillator Frequency)}$$

Where:

n = 64 in 12-clock mode, 32 in 6-clock mode

The baud rates in Modes 1 and 3 are determined by the Timer 1 or Timer 2 overflow rate.

#### **Using Timer 1 to Generate Baud Rates**

When Timer 1 is used as the baud rate generator (T2CON.RCLK = 0, T2CON.TCLK = 0), the baud rates in Modes 1 and 3 are determined by the Timer 1 overflow rate and the value of SMOD as follows:

Mode 1. 3 Baud Rate =

$$\frac{2^{\text{SMOD}}}{n} \times \text{(Timer 1 Overflow Rate)}$$

Where:

n = 32 in 12-clock mode, 16 in 6-clock mode

The Timer 1 interrupt should be disabled in this application. The Timer itself can be configured for either "timer" or "counter" operation, and in any of its 3 running modes. In the most typical applications, it is configured for "timer" operation, in the auto-reload mode (high nibble of TMOD = 0010B). In that case the baud rate is given by the formula:

Mode 1, 3 Baud Rate =

$$\frac{2^{\text{SMOD}}}{n} \times \frac{\text{Oscillator Frequency}}{12 \times [256-(\text{TH1})]}$$

Where:

n = 32 in 12-clock mode, 16 in 6-clock mode

One can achieve very low baud rates with Timer 1 by leaving the Timer 1 interrupt enabled, and configuring the Timer to run as a 16-bit timer (high nibble of TMOD = 0001B), and using the Timer 1 interrupt to do a 16-bit software reload. Figure 13 lists various commonly used baud rates and how they can be obtained from Timer 1.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

shifted to the left one position. The value that comes in from the right is the value that was sampled at the P3.0 pin at S5P2 of the same machine cycle.

As data bits come in from the right, 1s shift out to the left. When the 0 that was initially loaded into the rightmost position arrives at the leftmost position in the shift register, it flags the RX Control block to do one last shift and load SBUF. At S1P1 of the 10th machine cycle after the write to SCON that cleared RI, RECEIVE is cleared as RI is set.

#### More About Mode 1

Ten bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in SCON. In the 80C51 the baud rate is determined by the Timer 1 or Timer 2 overflow rate.

Figure 15 shows a simplified functional diagram of the serial port in Mode 1, and associated timings for transmit receive.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads a 1 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission actually commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that.

As data bits shift out to the right, zeros are clocked in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 10th divide-by-16 rollover after "write to SBUF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written into the input shift register. Resetting the divide-by-16 counter aligns its rollovers with the boundaries of the incoming bit times.

The 16 states of the counter divide each bit time into 16ths. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RxD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done for noise rejection. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. This is to provide rejection of false start bits. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in mode 1 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI. The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated.:

- 1. R1 = 0, and

- 2. Either SM2 = 0, or the received stop bit = 1.

If either of these two conditions is not met, the received frame is irretrievably lost. If both conditions are met, the stop bit goes into RB8, the 8 data bits go into SBUF, and RI is activated. At this time,

whether the above conditions are met or not, the unit goes back to looking for a 1-to-0 transition in RxD.

#### More About Modes 2 and 3

Eleven bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8) can be assigned the value of 0 or 1. On receive, the 9the data bit goes into RB8 in SCON. The baud rate is programmable to either 1/32 or 1/64 (12-clock mode) or 1/16 or 1/32 the oscillator frequency (6-clock mode) the oscillator frequency in Mode 2. Mode 3 may have a variable baud rate generated from Timer 1 or Timer 2.

Figures 16 and 17 show a functional diagram of the serial port in Modes 2 and 3. The receive portion is exactly the same as in Mode 1. The transmit portion differs from Mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND, which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that. The first shift clocks a 1 (the stop bit) into the 9th bit position of the shift register. Thereafter, only zeros are clocked in. Thus, as data bits shift out to the right, zeros are clocked in from the left. When TB8 is at the output position of the shift register, then the stop bit is just to the left of TB8, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 11th divide-by-16 rollover after "write to SUBF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written to the input shift register.

At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of R-D. The value accepted is the value that was seen in at least 2 of the 3 samples. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in Modes 2 and 3 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI.

The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated.

- 1. RI = 0, and

- 2. Either SM2 = 0, or the received 9th data bit = 1.

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits go into SBUF. One bit time later, whether the above conditions were met or not, the unit goes back to looking for a 1-to-0 transition at the RxD input.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

## **Interrupt Priority Structure**

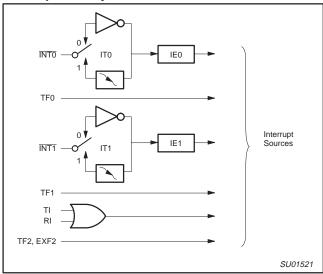

Figure 21. Interrupt Sources

## Interrupts

The devices described in this data sheet provide six interrupt sources. These are shown in Figure 21. The External Interrupts INTO and INTT can each be either level-activated or transition-activated, depending on bits ITO and IT1 in Register TCON. The flags that actually generate these interrupts are bits IEO and IE1 in TCON. When an external interrupt is generated, the flag that generated it is cleared by the hardware when the service routine is vectored to only if the interrupt was transition-activated. If the interrupt was level-activated, then the external requesting source is what controls the request flag, rather than the on-chip hardware.

The Timer 0 and Timer 1 Interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers (except see Timer 0 in Mode 3). When a timer interrupt is generated, the flag that generated it is cleared by the on-chip hardware when the service routine is vectored to.

The Serial Port Interrupt is generated by the logical OR of RI and TI. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine will normally have to determine whether it was RI or TI that generated the interrupt, and the bit will have to be cleared in software.

All of the bits that generate interrupts can be set or cleared by software, with the same result as though it had been set or cleared by hardware. That is, interrupts can be generated or pending interrupts can be canceled in software.

Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE (Figure 22). IE also contains a global disable bit,  $\overline{\text{EA}}$ , which disables all interrupts at once.

#### **Priority Level Structure**

Each interrupt source can also be individually programmed to one of four priority levels by setting or clearing bits in Special Function Registers IP (Figure 23) and IPH (Figure 24). A lower-priority interrupt can itself be interrupted by a higher-priority interrupt, but not by another interrupt of the same level. A high-priority level 3 interrupt can't be interrupted by any other interrupt source.

If two request of different priority levels are received simultaneously, the request of higher priority level is serviced. If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence as follows:

## Source Priority Within Level

1. IE0 (External Int 0) (highest)

- 2. TF0 (Timer 0)

- 3. IE1 (External Int 1)

- 4. TF1 (Timer 1)

- 5. RI+TI (UART)

- 6. TF2, EXF2 (Timer 2) (lowest)

Note that the "priority within level" structure is only used to resolve simultaneous requests of the same priority level.

The IP and IPH registers contain a number of unimplemented bits. User software should not write 1s to these positions, since they may be used in other 80C51 Family products.

### **How Interrupts Are Handled**

The interrupt flags are sampled at S5P2 of every machine cycle. The samples are polled during the following machine cycle. If one of the flags was in a set condition at S5P2 of the preceding cycle, the polling cycle will find it and the interrupt system will generate an LCALL to the appropriate service routine, provided this hardware-generated LCALL is not blocked by any of the following conditions:

- An interrupt of equal or higher priority level is already in progress.

- 2. The current (polling) cycle is not the final cycle in the execution of the instruction in progress.

- The instruction in progress is RETI or any write to the IE or IP registers.

Any of these three conditions will block the generation of the LCALL to the interrupt service routine. Condition 2 ensures that the instruction in progress will be completed before vectoring to any service routine. Condition 3 ensures that if the instruction in progress is RETI or any access to IE or IP, then at least one more instruction will be executed before any interrupt is vectored to.

The polling cycle is repeated with each machine cycle, and the values polled are the values that were present at S5P2 of the previous machine cycle. Note that if an interrupt flag is active but not being responded to for one of the above conditions, if the flag is not still active when the blocking condition is removed, the denied interrupt will not be serviced. In other words, the fact that the interrupt flag was once active but not serviced is not remembered. Every polling cycle is new.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

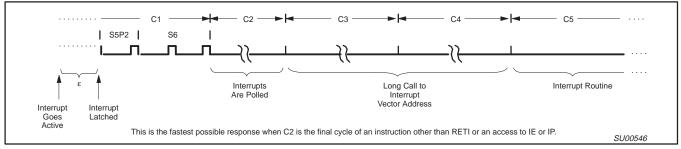

Figure 25. Interrupt Response Timing Diagram

The polling cycle/LCALL sequence is illustrated in Figure 25.

Note that if an interrupt of higher priority level goes active prior to S5P2 of the machine cycle labeled C3 in Figure 25, then in accordance with the above rules it will be vectored to during C5 and C6, without any instruction of the lower priority routine having been executed.

Thus the processor acknowledges an interrupt request by executing a hardware-generated LCALL to the appropriate servicing routine. In some cases it also clears the flag that generated the interrupt, and in other cases it doesn't. It never clears the Serial Port flag. This has to be done in the user's software. It clears an external interrupt flag (IE0 or IE1) only if it was transition-activated. The hardware-generated LCALL pushes the contents of the Program Counter on to the stack (but it does not save the PSW) and reloads the PC with an address that depends on the source of the interrupt being vectored to, as shown in Table 8.

Execution proceeds from that location until the RETI instruction is encountered. The RETI instruction informs the processor that this interrupt routine is no longer in progress, then pops the top two bytes from the stack and reloads the Program Counter. Execution of the interrupted program continues from where it left off.

Note that a simple RET instruction would also have returned execution to the interrupted program, but it would have left the interrupt control system thinking an interrupt was still in progress, making future interrupts impossible.

### **External Interrupts**

The external sources can be programmed to be level-activated or transition-activated by setting or clearing bit IT1 or IT0 in Register TCON. If ITx = 0, external interrupt x is triggered by a detected low at the  $\overline{\text{INTx}}$  pin. If ITx = 1, external interrupt x is edge triggered. In this mode if successive samples of the  $\overline{\text{INTx}}$  pin show a high in one cycle and a low in the next cycle, interrupt request flag IEx in TCON is set. Flag bit IEx then requests the interrupt.

Since the external interrupt pins are sampled once each machine cycle, an input high or low should hold for at least 12 oscillator periods to ensure sampling. If the external interrupt is transition-activated, the external source has to hold the request pin high for at least one cycle, and then hold it low for at least one cycle. This is done to ensure that the transition is seen so that interrupt request flag IEx will be set. IEx will be automatically cleared by the CPU when the service routine is called.

If the external interrupt is level-activated, the external source has to hold the request active until the requested interrupt is actually generated. Then it has to deactivate the request before the interrupt

service routine is completed, or else another interrupt will be generated.

## **Response Time**

The INTO and INTT levels are inverted and latched into IEO and IE1 at S5P2 of every machine cycle. The values are not actually polled by the circuitry until the next machine cycle. If a request is active and conditions are right for it to be acknowledged, a hardware subroutine call to the requested service routine will be the next instruction to be executed. The call itself takes two cycles. Thus, a minimum of three complete machine cycles elapse between activation of an external interrupt request and the beginning of execution of the first instruction of the service routine. Figure 25 shows interrupt response timings.

A longer response time would result if the request is blocked by one of the 3 previously listed conditions. If an interrupt of equal or higher priority level is already in progress, the additional wait time obviously depends on the nature of the other interrupt's service routine. If the instruction in progress is not in its final cycle, the additional wait time cannot be more the 3 cycles, since the longest instructions (MUL and DIV) are only 4 cycles long, and if the instruction in progress is RETI or an access to IE or IP, the additional wait time cannot be more than 5 cycles (a maximum of one more cycle to complete the instruction in progress, plus 4 cycles to complete the next instruction if the instruction is MUL or DIV).

Thus, in a single-interrupt system, the response time is always more than 3 cycles and less than 9 cycles.

As previously mentioned, the derivatives described in this data sheet have a four-level interrupt structure. The corresponding registers are IE, IP and IPH. (See Figures 22, 23, and 24.) The IPH (Interrupt Priority High) register makes the four-level interrupt structure possible.

The function of the IPH SFR is simple and when combined with the IP SFR determines the priority of each interrupt. The priority of each interrupt is determined as shown in the following table:

| PRIORI" | TY BITS | INTERRUPT PRIORITY LEVEL   |  |  |  |

|---------|---------|----------------------------|--|--|--|

| IPH.x   | IP.x    | INTERROPT PRIORITY LEVEL   |  |  |  |

| 0       | 0       | Level 0 (lowest priority)  |  |  |  |

| 0       | 1       | Level 1                    |  |  |  |

| 1       | 0       | Level 2                    |  |  |  |

| 1       | 1       | Level 3 (highest priority) |  |  |  |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced, the new interrupt will wait until it is finished before being serviced. If a lower priority level

interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.

Table 8. Interrupt Table

| SOURCE               | POLLING PRIORITY | REQUEST BITS | HARDWARE CLEAR?                       | VECTOR ADDRESS |

|----------------------|------------------|--------------|---------------------------------------|----------------|

| External interrupt 0 | 1                | IE0          | N (L) <sup>1</sup> Y (T) <sup>2</sup> | 03H            |

| Timer 0              | 2                | TF0          | Υ                                     | 0BH            |

| External interrupt 1 | 3                | IE1          | N (L) Y (T)                           | 13H            |

| Timer 1              | 4                | TF1          | Υ                                     | 1BH            |

| UART                 | 5                | RI, TI       | N                                     | 23H            |

| Timer 2              | 6                | TF2, EXF2    | N                                     | 2BH            |

#### NOTES:

- 1. L = Level activated

- 2. T = Transition activated

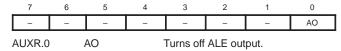

#### Reduced EMI

All port pins have slew rate controlled outputs. This is to limit noise generated by quickly switching output signals. The slew rate is factory set to approximately 10 ns rise and fall times.

## **Reduced EMI Mode**

The AO bit (AUXR.0) in the AUXR register when set disables the ALE output.

# AUXR (8EH)

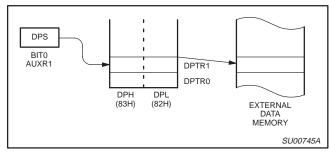

## **Dual DPTR**

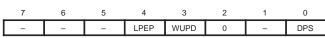

The dual DPTR structure (see Figure 26) enables a way to specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 that allows the program code to switch between them.

New Register Name: AUXR1#

SFR Address: A2HReset Value: xxx000x0B

## AUXR1 (A2H)

Where:

DPS = AUXR1/bit0 = Switches between DPTR0 and DPTR1.

| Select Reg | DPS |

|------------|-----|

| DPTR0      | 0   |

| DPTR1      | 1   |

The DPS bit status should be saved by software when switching between DPTR0 and DPTR1.

Note that bit 2 is not writable and is always read as a zero. This allows the DPS bit to be quickly toggled simply by executing an INC DPTR instruction without affecting the WUPD or LPEP bits.

Figure 26.

#### **DPTR Instructions**

The instructions that refer to DPTR refer to the data pointer that is currently selected using the AUXR1/bit 0 register. The six instructions that use the DPTR are as follows:

| INC DPTR          | Increments the data pointer by 1          |

|-------------------|-------------------------------------------|

| MOV DPTR, #data16 | Loads the DPTR with a 16-bit constant     |

| MOV A, @ A+DPTR   | Move code byte relative to DPTR to ACC    |

| MOVX A, @ DPTR    | Move external RAM (16-bit address) to ACC |

| MOVX @ DPTR , A   | Move ACC to external RAM (16-bit address) |

| JMP @ A + DPTR    | Jump indirect relative to DPTR            |

The data pointer can be accessed on a byte-by-byte basis by specifying the low or high byte in an instruction which accesses the SFRs. See application note AN458 for more details.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

#### DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = 0 °C to +70 °C or -40 °C to +85 °C;  $V_{CC}$  = 2.7 V to 5.5 V;  $V_{SS}$  = 0 V (16 MHz max. CPU clock)

| SYMBOL           | PARAMETER                                                                               | TEST<br>CONDITIONS                                                | LIMITS                   |      |                          | UNIT |

|------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|------|--------------------------|------|

|                  |                                                                                         |                                                                   | MIN                      | TYP1 | MAX                      | 7    |

| V <sub>IL</sub>  | Input low voltage <sup>11</sup>                                                         | 4.0 V < V <sub>CC</sub> < 5.5 V                                   | -0.5                     |      | 0.2 V <sub>CC</sub> -0.1 | V    |

|                  |                                                                                         | 2.7 V < V <sub>CC</sub> < 4.0 V                                   | -0.5                     |      | 0.7 V <sub>CC</sub>      | V    |

| V <sub>IH</sub>  | Input high voltage (ports 0, 1, 2, 3, EA)                                               | -                                                                 | 0.2 V <sub>CC</sub> +0.9 |      | V <sub>CC</sub> +0.5     | V    |

| V <sub>IH1</sub> | Input high voltage, XTAL1, RST <sup>11</sup>                                            | -                                                                 | 0.7 V <sub>CC</sub>      |      | V <sub>CC</sub> +0.5     | V    |

| V <sub>OL</sub>  | Output low voltage, ports 1, 2, 8                                                       | $V_{CC} = 2.7 \text{ V}; I_{OL} = 1.6 \text{ mA}^2$               | _                        |      | 0.4                      | V    |

| V <sub>OL1</sub> | Output low voltage, port 0, ALE, PSEN <sup>8, 7</sup>                                   | $V_{CC} = 2.7 \text{ V}; I_{OL} = 3.2 \text{ mA}^2$               | -                        |      | 0.4                      | V    |

| V <sub>OH</sub>  | Output high voltage, ports 1, 2, 3 <sup>3</sup>                                         | $V_{CC} = 2.7 \text{ V; } I_{OH} = -20 \mu A$                     | V <sub>CC</sub> – 0.7    |      | -                        | V    |

|                  |                                                                                         | $V_{CC} = 4.5 \text{ V; } I_{OH} = -30 \mu\text{A}$               | V <sub>CC</sub> - 0.7    |      | -                        | V    |

| V <sub>OH1</sub> | Output high voltage (port 0 in external bus mode), ALE <sup>9</sup> , PSEN <sup>3</sup> | $V_{CC} = 2.7 \text{ V}; I_{OH} = -3.2 \text{ mA}$                | V <sub>CC</sub> – 0.7    |      | -                        | V    |

| I <sub>IL</sub>  | Logical 0 input current, ports 1, 2, 3                                                  | V <sub>IN</sub> = 0.4 V                                           | <b>-1</b>                |      | -50                      | μΑ   |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 36                                       | V <sub>IN</sub> = 2.0 V; See note 4                               | -                        |      | -650                     | μΑ   |

| I <sub>LI</sub>  | Input leakage current, port 0                                                           | $0.45 < V_{IN} < V_{CC} - 0.3$                                    | _                        |      | ±10                      | μΑ   |

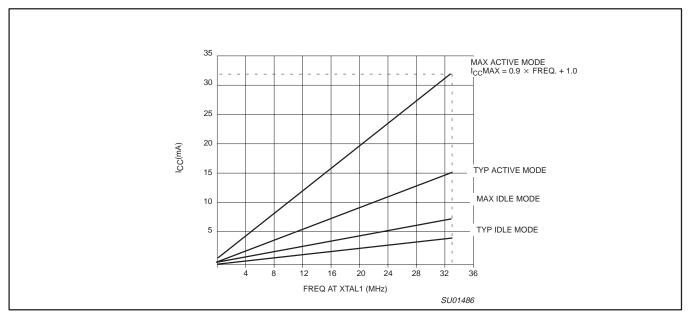

| I <sub>CC</sub>  | Power supply current (see Figure 34 and Source Code):                                   |                                                                   |                          |      |                          |      |

|                  | Active mode @ 16 MHz                                                                    |                                                                   |                          |      |                          | μΑ   |

|                  | Idle mode @ 16 MHz                                                                      |                                                                   |                          |      |                          | μΑ   |

|                  | Power-down mode or clock stopped (see Figure 30 for conditions) 12                      | T <sub>amb</sub> = 0 °C to 70 °C                                  |                          | 2    | 30                       | μΑ   |

|                  |                                                                                         | $T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$ |                          | 3    | 50                       | μΑ   |

| $V_{RAM}$        | RAM keep-alive voltage                                                                  | -                                                                 | 1.2                      |      |                          | V    |

| R <sub>RST</sub> | Internal reset pull-down resistor                                                       | -                                                                 | 40                       |      | 225                      | kΩ   |

| C <sub>IO</sub>  | Pin capacitance <sup>10</sup> (except EA)                                               | -                                                                 | _                        |      | 15                       | pF   |

## NOTES:

- 1. Typical ratings are not guaranteed. Values listed are based on tests conducted on limited number of samples at room temperature.

- Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the VOI s of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8 V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. IOL can exceed these conditions provided that no single output sinks more than 5 mA and no more than two outputs exceed the test conditions.

- 3. Capacitive loading on ports 0 and 2 may cause the VOH on ALE and PSEN to momentarily fall below the VCC-0.7 specification when the address bits are stabilizing.

- 4. Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when  $V_{\mbox{\scriptsize IN}}$  is approximately 2 V.

- See Figures 36 through 39 for I<sub>CC</sub> test conditions and Figure 34 for I<sub>CC</sub> vs. Frequency 12-clock mode characteristics:

$I_{CC}$  = 1.0 mA + 0.9 mA × FREQ.[MHz] Active mode (operating): Active mode (reset):  $I_{CC} = 7.0 \text{ mA} + 0.5 \text{ mA} \times \text{FREQ.[MHz]}$

- Idle mode:  $I_{CC} = 1.0 \text{ mA} + 0.18 \text{ mA} \times \text{FREQ}.[\text{MHz}]$ 6. This value applies to  $I_{amb} = 0 \text{ °C}$  to +70 °C. For  $I_{amb} = -40 \text{ °C}$  to +85 °C,  $I_{TL} = -750 \text{ }\mu\text{A}$ .

7. Load capacitance for port 0, ALE, and  $\overline{PSEN} = 100 \text{ pF}$ , load capacitance for all other outputs = 80 pF.

- Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows: Maximum I<sub>OL</sub> per port pin: 15 mA (\*NOTE: This is 85 °C specification.) Maximum I<sub>OL</sub> per port pin:

Maximum IOL per 8-bit port: 26 mA Maximum total I<sub>OI</sub> for all outputs: 71 mA

If IoL exceeds the test condition, Vol may exceed the related specification. Pins are not guaranteed to sink current greater than the listed

- 9. ALE is tested to  $V_{OH1}$ , except when ALE is off then  $V_{OH}$  is the voltage specification.

- 10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25 pF. Pin capacitance of ceramic package is less than 15 pF

- 11. To improve noise rejection a nominal 100 ns glitch rejection circuitry has been added to the RST pin, and a nominal 15 ns glitch rejection circuitry has been added to the INTO and INTO pins. Previous devices provided only an inherent 5 ns of glitch rejection.

- 12. Power down mode for 3 V range: Commercial Temperature Range typ: 0.5 μA, max. 20 μA; Industrial Temperature Range typ. 1.0 μA, max. 30 μA;

2003 Jan 24 38

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 5 V ±10% OPERATION)

$T_{amb} = 0 \, ^{\circ}C \text{ to } +70 \, ^{\circ}C \text{ or } -40 \, ^{\circ}C \text{ to } +85 \, ^{\circ}C \text{ ; } V_{CC} = 5 \, \text{V} \pm 10\%, \, \, V_{SS} = 0 \, \text{V}^{1,2,3,4,5}$

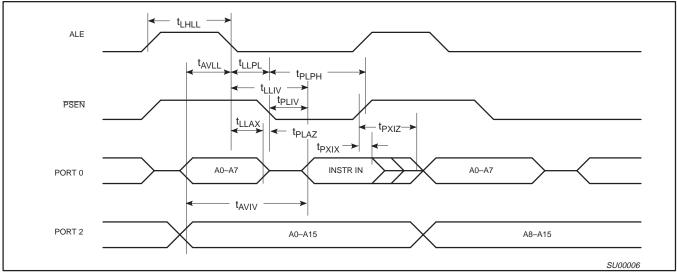

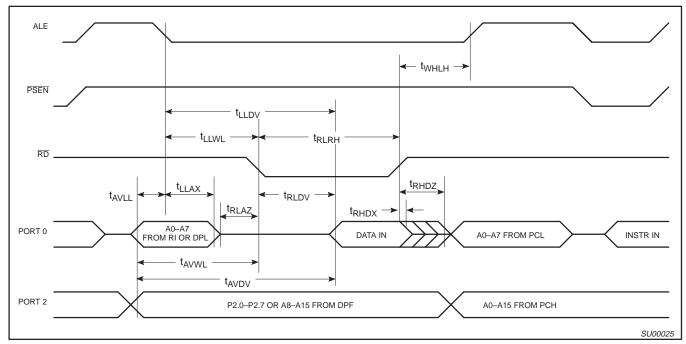

| Symbol              | Figure | Parameter                                | Limits                    |                                       | 16 MHz | Clock  | Unit |

|---------------------|--------|------------------------------------------|---------------------------|---------------------------------------|--------|--------|------|

|                     |        |                                          | MIN                       | MAX                                   | MIN    | MAX    | 7    |

| 1/t <sub>CLCL</sub> | 31     | Oscillator frequency                     | 0                         | 30                                    | -      | _      | MHz  |

| LHLL                | 27     | ALE pulse width                          | t <sub>CLCL</sub> -8      | _                                     | 54.5   | _      | ns   |

| t <sub>AVLL</sub>   | 27     | Address valid to ALE low                 | 0.5 t <sub>CLCL</sub> -13 | _                                     | 18.25  | _      | ns   |

| t <sub>LLAX</sub>   | 27     | Address hold after ALE low               | 0.5 t <sub>CLCL</sub> -20 | _                                     | 11.25  | -      | ns   |

| t <sub>LLIV</sub>   | 27     | ALE low to valid instruction in          | _                         | 2 t <sub>CLCL</sub> -35               | _      | 90     | ns   |

| t <sub>LLPL</sub>   | 27     | ALE low to PSEN low                      | 0.5 t <sub>CLCL</sub> -10 | _                                     | 21.25  | -      | ns   |

| t <sub>PLPH</sub>   | 27     | PSEN pulse width                         | 1.5 t <sub>CLCL</sub> -10 | _                                     | 83.75  | -      | ns   |

| t <sub>PLIV</sub>   | 27     | PSEN low to valid instruction in         | -                         | 1.5 t <sub>CLCL</sub> -35             | _      | 58.75  | ns   |

| t <sub>PXIX</sub>   | 27     | Input instruction hold after PSEN        | 0                         | _                                     | 0      | -      | ns   |

| t <sub>PXIZ</sub>   | 27     | Input instruction float after PSEN       | _                         | 0.5 t <sub>CLCL</sub> -10             | _      | 21.25  | ns   |

| t <sub>AVIV</sub>   | 27     | Address to valid instruction in          | _                         | 2.5 t <sub>CLCL</sub> -35             | _      | 121.25 | ns   |

| t <sub>PLAZ</sub>   | 27     | PSEN low to address float                | _                         | 10                                    | -      | 10     | ns   |

| Data Men            | nory   |                                          |                           |                                       |        |        |      |

| t <sub>RLRH</sub>   | 28     | RD pulse width                           | 3 t <sub>CLCL</sub> –20   | _                                     | 167.5  | -      | ns   |

| t <sub>WLWH</sub>   | 29     | WR pulse width                           | 3 t <sub>CLCL</sub> -20   | _                                     | 167.5  | -      | ns   |

| t <sub>RLDV</sub>   | 28     | RD low to valid data in                  | -                         | 2.5 t <sub>CLCL</sub> -35             | _      | 121.25 | ns   |

| t <sub>RHDX</sub>   | 28     | Data hold after RD                       | 0                         | _                                     | 0      | -      | ns   |

| t <sub>RHDZ</sub>   | 28     | Data float after RD                      | _                         | t <sub>CLCL</sub> -10                 | -      | 52.5   | ns   |

| t <sub>LLDV</sub>   | 28     | ALE low to valid data in                 | _                         | 4 t <sub>CLCL</sub> -35               | _      | 215    | ns   |

| t <sub>AVDV</sub>   | 28     | Address to valid data in                 | _                         | 4.5 t <sub>CLCL</sub> -35             | _      | 246.25 | ns   |

| t <sub>LLWL</sub>   | 28, 29 | ALE low to RD or WR low                  | 1.5 t <sub>CLCL</sub> -15 | 1.5 t <sub>CLCL</sub> +15             | 78.75  | 108.75 | ns   |

| t <sub>AVWL</sub>   | 28, 29 | Address valid to WR low or RD low        | 2 t <sub>CLCL</sub> -15   | _                                     | 110    | _      | ns   |

| t <sub>QVWX</sub>   | 29     | Data valid to WR transition              | 0.5 t <sub>CLCL</sub> -25 | _                                     | 6.25   | -      | ns   |

| t <sub>WHQX</sub>   | 29     | Data hold after WR                       | 0.5 t <sub>CLCL</sub> -15 | _                                     | 16.25  | -      | ns   |

| t <sub>QVWH</sub>   | 29     | Data valid to WR high                    | 3.5 t <sub>CLCL</sub> -5  | _                                     | 213.75 | -      | ns   |

| t <sub>RLAZ</sub>   | 28     | RD low to address float                  | _                         | 0                                     | _      | 0      | ns   |

| twhLH               | 28, 29 | RD or WR high to ALE high                | 0.5 t <sub>CLCL</sub> -10 | 0.5 t <sub>CLCL</sub> +10             | 21.25  | 41.25  | ns   |

| External (          | Clock  | -                                        |                           |                                       |        |        |      |

| t <sub>CHCX</sub>   | 31     | High time                                | 0.4 t <sub>CLCL</sub>     | t <sub>CLCL</sub> - t <sub>CLCX</sub> | _      | -      | ns   |

| t <sub>CLCX</sub>   | 31     | Low time                                 | 0.4 t <sub>CLCL</sub>     | t <sub>CLCL</sub> - t <sub>CHCX</sub> | _      | -      | ns   |

| t <sub>CLCH</sub>   | 31     | Rise time                                | _                         | 5                                     | _      | -      | ns   |

| tCHCL               | 31     | Fall time                                | _                         | 5                                     | _      | -      | ns   |

| Shift regi          | ster   |                                          |                           |                                       |        |        |      |

| t <sub>XLXL</sub>   | 30     | Serial port clock cycle time             | 6 t <sub>CLCL</sub>       | _                                     | 375    | -      | ns   |

| t <sub>QVXH</sub>   | 30     | Output data setup to clock rising edge   | 5 t <sub>CLCL</sub> –25   | _                                     | 287.5  | -      | ns   |

| t <sub>XHQX</sub>   | 30     | Output data hold after clock rising edge | t <sub>CLCL</sub> -15     | _                                     | 47.5   | -      | ns   |

| t <sub>XHDX</sub>   | 30     | Input data hold after clock rising edge  | 0                         | _                                     | 0      | -      | ns   |

| t <sub>XHDV</sub>   | 30     | Clock rising edge to input data valid    | _                         | 5 t <sub>CLCL</sub> -133              | _      | 179.5  | ns   |

#### NOTES:

- 1. Parameters are valid over operating temperature range unless otherwise specified.

- 2. Load capacitance for port 0, ALE, and PSEN=100 pF, load capacitance for all outputs = 80 pF

- 3. Interfacing the microcontroller to devices with float time up to 45ns is permitted. This limited bus contention will not cause damage to port 0 drivers.

- 4. Parts are guaranteed by design to operate down to 0 Hz.

- 5. Data shown in the table are the best mathematical models for the set of measured values obtained in tests. If a particular parameter calculated at a customer specified frequency has a negative value, it should be considered equal to zero.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 2.7 V TO 5.5 V OPERATION)

$T_{amb}$  = 0 °C to +70 °C or -40 °C to +85 °C ;  $V_{CC}$ =2.7 V to 5.5 V,  $V_{SS}$  = 0 V<sup>1,2,3,4,5</sup>

| Symbol              | Figure | Parameter                                | Limits                    |                                       | 16 MHz ( | Unit   |     |

|---------------------|--------|------------------------------------------|---------------------------|---------------------------------------|----------|--------|-----|

|                     |        |                                          | MIN                       | MAX                                   | MIN      | MAX    | 7   |

| 1/t <sub>CLCL</sub> | 31     | Oscillator frequency                     | 0                         | 16                                    | -        | _      | MHz |

| t <sub>LHLL</sub>   | 27     | ALE pulse width                          | t <sub>CLCL</sub> -10     | _                                     | 52.5     | _      | ns  |

| t <sub>AVLL</sub>   | 27     | Address valid to ALE low                 | 0.5 t <sub>CLCL</sub> -15 | _                                     | 16.25    | _      | ns  |

| t <sub>LLAX</sub>   | 27     | Address hold after ALE low               | 0.5 t <sub>CLCL</sub> -25 | T-                                    | 6.25     | -      | ns  |

| t <sub>LLIV</sub>   | 27     | ALE low to valid instruction in          | _                         | 2 t <sub>CLCL</sub> -55               | _        | 70     | ns  |

| t <sub>LLPL</sub>   | 27     | ALE low to PSEN low                      | 0.5 t <sub>CLCL</sub> -15 | T-                                    | 16.25    | -      | ns  |

| t <sub>PLPH</sub>   | 27     | PSEN pulse width                         | 1.5 t <sub>CLCL</sub> -15 | _                                     | 78.75    | _      | ns  |

| t <sub>PLIV</sub>   | 27     | PSEN low to valid instruction in         | _                         | 1.5 t <sub>CLCL</sub> -55             | _        | 38.75  | ns  |

| t <sub>PXIX</sub>   | 27     | Input instruction hold after PSEN        | 0                         | _                                     | 0        | _      | ns  |

| t <sub>PXIZ</sub>   | 27     | Input instruction float after PSEN       | _                         | 0.5 t <sub>CLCL</sub> -10             | _        | 21.25  | ns  |

| t <sub>AVIV</sub>   | 27     | Address to valid instruction in          | _                         | 2.5 t <sub>CLCL</sub> -50             | _        | 101.25 | ns  |

| t <sub>PLAZ</sub>   | 27     | PSEN low to address float                | _                         | 10                                    | _        | 10     | ns  |

| Data Men            | nory   |                                          |                           |                                       |          |        |     |

| t <sub>RLRH</sub>   | 28     | RD pulse width                           | 3 t <sub>CLCL</sub> -25   | _                                     | 162.5    | _      | ns  |

| t <sub>WLWH</sub>   | 29     | WR pulse width                           | 3 t <sub>CLCL</sub> -25   | _                                     | 162.5    | _      | ns  |

| t <sub>RLDV</sub>   | 28     | RD low to valid data in                  | _                         | 2.5 t <sub>CLCL</sub> -50             | -        | 106.25 | ns  |

| t <sub>RHDX</sub>   | 28     | Data hold after RD                       | 0                         | _                                     | 0        | _      | ns  |

| t <sub>RHDZ</sub>   | 28     | Data float after RD                      | _                         | t <sub>CLCL</sub> -20                 | _        | 42.5   | ns  |

| t <sub>LLDV</sub>   | 28     | ALE low to valid data in                 | _                         | 4 t <sub>CLCL</sub> -55               | _        | 195    | ns  |

| t <sub>AVDV</sub>   | 28     | Address to valid data in                 | _                         | 4.5 t <sub>CLCL</sub> -50             | _        | 231.25 | ns  |

| t <sub>LLWL</sub>   | 28, 29 | ALE low to RD or WR low                  | 1.5 t <sub>CLCL</sub> -20 | 1.5 t <sub>CLCL</sub> +20             | 73.75    | 113.75 | ns  |

| t <sub>AVWL</sub>   | 28, 29 | Address valid to WR low or RD low        | 2 t <sub>CLCL</sub> -20   | _                                     | 105      | _      | ns  |

| t <sub>QVWX</sub>   | 29     | Data valid to WR transition              | 0.5 t <sub>CLCL</sub> -30 | -                                     | 1.25     | _      | ns  |

| t <sub>WHQX</sub>   | 29     | Data hold after WR                       | 0.5 t <sub>CLCL</sub> -20 | _                                     | 11.25    | _      | ns  |

| t <sub>QVWH</sub>   | 29     | Data valid to WR high                    | 3.5 t <sub>CLCL</sub> -10 | 1-                                    | 208.75   | _      | ns  |

| t <sub>RLAZ</sub>   | 28     | RD low to address float                  | _                         | 0                                     | _        | 0      | ns  |

| twhlh               | 28, 29 | RD or WR high to ALE high                | 0.5 t <sub>CLCL</sub> -15 | 0.5 t <sub>CLCL</sub> +15             | 16.25    | 46.25  | ns  |

| External            | Clock  |                                          |                           | 0.00                                  |          |        |     |

| t <sub>CHCX</sub>   | 31     | High time                                | 0.4 t <sub>CLCL</sub>     | t <sub>CLCL</sub> - t <sub>CLCX</sub> | -        | _      | ns  |

| t <sub>CLCX</sub>   | 31     | Low time                                 | 0.4 t <sub>CLCL</sub>     | t <sub>CLCL</sub> - t <sub>CHCX</sub> | _        | _      | ns  |

| t <sub>CLCH</sub>   | 31     | Rise time                                | -                         | 5                                     | -        | _      | ns  |

| t <sub>CHCL</sub>   | 31     | Fall time                                | _                         | 5                                     | _        | _      | ns  |

| Shift regi          | ster   |                                          | •                         | •                                     |          |        |     |

| t <sub>XLXL</sub>   | 30     | Serial port clock cycle time             | 6 t <sub>CLCL</sub>       | _                                     | 375      | _      | ns  |

| t <sub>QVXH</sub>   | 30     | Output data setup to clock rising edge   | 5 t <sub>CLCL</sub> -25   | _                                     | 287.5    | -      | ns  |

| t <sub>XHQX</sub>   | 30     | Output data hold after clock rising edge | t <sub>CLCL</sub> -15     | 1-                                    | 47.5     | _      | ns  |

| t <sub>XHDX</sub>   | 30     | Input data hold after clock rising edge  | 0                         | -                                     | 0        | _      | ns  |

| t <sub>XHDV</sub>   | 30     | Clock rising edge to input data valid    | _                         | 5 t <sub>CLCL</sub> -133              | -        | 179.5  | ns  |

#### NOTES:

- 1. Parameters are valid over operating temperature range unless otherwise specified.

- 2. Load capacitance for port 0, ALE, and PSEN=100 pF, load capacitance for all outputs = 80 pF

- 3. Interfacing the microcontroller to devices with float time up to 45ns is permitted. This limited bus contention will not cause damage to port 0 drivers.

- 4. Parts are guaranteed by design to operate down to 0 Hz.

- 5. Data shown in the table are the best mathematical models for the set of measured values obtained in tests. If a particular parameter calculated at a customer specified frequency has a negative value, it should be considered equal to zero.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

## **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

A - Address

C - Clock

D - Input data

H - Logic level high

I – Instruction (program memory contents)

L - Logic level low, or ALE

P - PSEN

Q - Output data

R - RD signal

t - Time

V - Valid

W- WR signal

X - No longer a valid logic level

Z - Float

**Examples:** t<sub>AVLL</sub> = Time for address valid to ALE low.

$t_{LLPL}$  =Time for ALE low to  $\overline{PSEN}$  low.

Figure 27. External Program Memory Read Cycle

Figure 28. External Data Memory Read Cycle

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

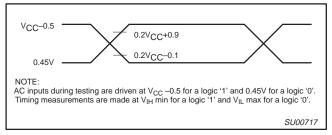

VLOAD VLOAD+0.1V TIMING REFERENCE POINTS VOH-0.1V NOTE: For timing purposes, a port is no longer floating when a 100mV change from load voltage occurs, and begins to float when a 100mV change from the loaded VOH/VOL level occurs.  $I_{OH}/I_{OL} \ge \pm 20$ mA.

Figure 32. AC Testing Input/Output

Figure 33. Float Waveform

Figure 34. I<sub>CC</sub> vs. FREQ for 12-clock operation Valid only within frequency specifications of the specified operating voltage

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz) P80C3xX2; P80C5xX2; P87C5xX2

```

##

as31 version V2.10

/ *js* /

##

##

##

source file: idd_ljmp1.asm

list file: idd_ljmp1.lst

created Fri Apr 20 15:51:40 2001

##

#0000

# AUXR equ 08Eh

#0000

# CKCON equ 08Fh

#

#0000

# org 0

# LJMP_LABEL:

AUXR,#001h ; turn off ALE LJMP_LABEL ; jump to end of address space

0000 /75;/8E;/01;

MOV

#

0003 /02;/FF;/FD;

#

LJMP

0005 /00;

NOP

#FFFD

# org Offfdh

# LJMP_LABEL:

FFFD /02;/FD;FF;

#

LJMP LJMP_LABEL

# ;

NOP

#

#

SU01499

```

Figure 35. Source code used in measuring  $I_{\mbox{\scriptsize DD}}$  operational

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

## 80C54X2 ROM CODE SUBMISSION

When submitting a ROM code for the 80C54X2, the following must be specified:

- 1. 16 kbyte user ROM data

- 2. 64 byte ROM encryption key

- 3. ROM security bits.

| ADDRESS        | CONTENT | BIT(S) | COMMENT                                                           |

|----------------|---------|--------|-------------------------------------------------------------------|

| 0000H to 3FFFH | DATA    | 7:0    | User ROM Data                                                     |

| 4000H to 403FH | KEY     | 7:0    | ROM Encryption Key<br>FFH = no encryption                         |

| 4040H          | SEC     | 0      | ROM Security Bit 1<br>0 = enable security<br>1 = disable security |

| 4040H          | SEC     | 1      | ROM Security Bit 2<br>0 = enable security<br>1 = disable security |

Security Bit 1: When programmed, this bit has two effects on masked ROM parts:

- 1. External MOVC is disabled, and

- 2. EA is latched on Reset.

Security Bit 2: When programmed, this bit inhibits Verify User ROM.

NOTE: Security Bit 2 cannot be enabled unless Security Bit 1 is enabled.

If the ROM Code file does not include the options, the following information must be included with the ROM code.

For each of the following, check the appropriate box, and send to Philips along with the code:

| Security Bit #1: | ☐ Enabled | ☐ Disabled                        |

|------------------|-----------|-----------------------------------|

| Security Bit #2: | ☐ Enabled | ☐ Disabled                        |

| Encryption:      | □ No      | ☐ Yes If Yes, must send key file. |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

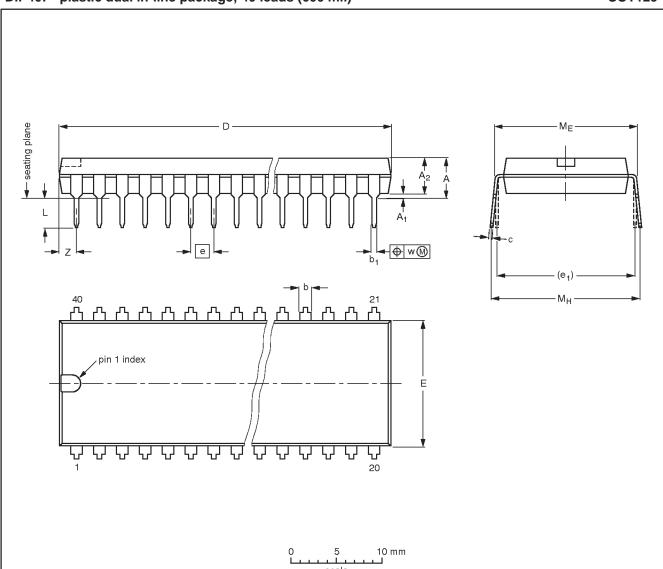

# DIP40: plastic dual in-line package; 40 leads (600 mil)

SOT129-1

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | Мн             | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|-------|--------------------------|

| mm     | 4.7       | 0.51                   | 4                      | 1.70<br>1.14   | 0.53<br>0.38   | 0.36<br>0.23   | 52.5<br>51.5     | 14.1<br>13.7     | 2.54 | 15.24          | 3.60<br>3.05 | 15.80<br>15.24 | 17.42<br>15.90 | 0.254 | 2.25                     |

| inches | 0.19      | 0.02                   | 0.16                   | 0.067<br>0.045 | 0.021<br>0.015 | 0.014<br>0.009 | 2.067<br>2.028   | 0.56<br>0.54     | 0.1  | 0.6            | 0.14<br>0.12 | 0.62<br>0.60   | 0.69<br>0.63   | 0.01  | 0.089                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE  |        | REFEF  | EUROPEAN  | ISSUE DATE |            |                                 |  |

|----------|--------|--------|-----------|------------|------------|---------------------------------|--|

| VERSION  | IEC    | JEDEC  | JEITA     |            | PROJECTION | ISSUE DATE                      |  |

| SOT129-1 | 051G08 | MO-015 | SC-511-40 |            |            | <del>99-12-27</del><br>03-02-13 |  |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# **REVISION HISTORY**

| Rev | Date     | Description                                                            |

|-----|----------|------------------------------------------------------------------------|

| _6  | 20030124 | Product data (9397 750 10995); ECN 853-2337 29260 of 06 December 2002  |