Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8051                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 33MHz                                                                  |

| Connectivity               | EBI/EMI, UART/USART                                                    |

| Peripherals                | POR                                                                    |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | -                                                                      |

| Program Memory Type        | ROMIess                                                                |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

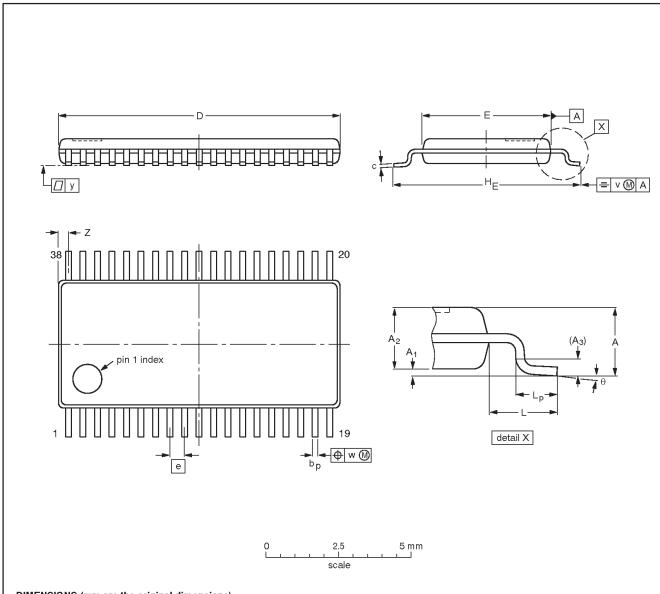

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p80c32x2fn-112 |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# **PIN DESCRIPTIONS**

|                 |       | PIN N        | UMBER         |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------|-------|--------------|---------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MNEMONIC        | DIP   | PLCC         | LQFP          | TSSOP | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| V <sub>SS</sub> | 20    | 22           | 16            | 9     | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| V <sub>CC</sub> | 40    | 44           | 38            | 29    | ı    | <b>Power Supply:</b> This is the power supply voltage for normal, idle, and power-down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| P0.0-0.7        | 39–32 | 43–36        | 37–30         | 28–21 | I/O  | Port 0: Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s. Port 0 also outputs the code bytes during program verification and received code bytes during EPROM programming. External pull-ups are required during program verification.                                                                                                                                                                                                                                                                                                                                   |  |

| P1.0-P1.7       | 1–8   | 2–9          | 40–44,<br>1–3 | 30–37 | I/O  | Port 1: Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins thave 1s written to them are pulled high by the internal pull-ups and can be used inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 1 areceives the low-order address byte during program memory verification. Alternation functions for Port 1 include:                                                                                                                                                                                                                                                                                                                                                                                |  |

|                 | 1     | 2            | 40            | 30    | I/O  | T2 (P1.0): Timer/Counter 2 external count input/clockout (see Programmable Clock-Out)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                 | 2     | 3            | 41            | 31    | 1    | T2EX (P1.1): Timer/Counter 2 Reload/Capture/Direction control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| P2.0-P2.7       | 21–28 | 24–31        | 18–25         | 10–17 | I/O  | Port 2: Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register. Some Port 2 pins receive the high order address bits during EPROM programming and verification. |  |

| P3.0-P3.7       | 10–17 | 11,<br>13–19 | 5,<br>7–13    | 1–6   | I/O  | <b>Port 3</b> : Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: I <sub>IL</sub> ). Port 3 also serves the special features of the 80C51 family, as listed below:                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                 | 10    | 11           | 5             | 1     | ı    | RxD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                 | 11    | 13           | 7             | 2     | 0    | TxD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                 | 12    | 14           | 8             |       | ı    | ĪNTŌ (P3.2): External interrupt <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                 | 13    | 15           | 9             | 3     | ı    | INT1 (P3.3): External interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                 | 14    | 16           | 10            | 4     | ı    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                 | 15    | 17           | 11            |       | ı    | T1 (P3.5): Timer 1 external input <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                 | 16    | 18           | 12            | 5     | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                 | 17    | 19           | 13            | 6     | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| RST             | 9     | 10           | 4             | 38    | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

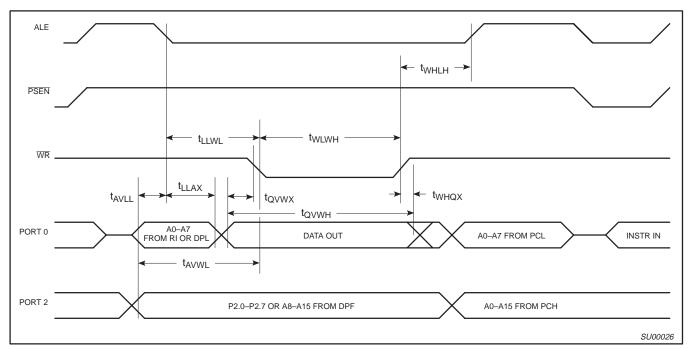

| ALE/PROG        | 30    | 33           | 27            | 19    | 0    | Address Latch Enable/Program Pulse: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 (12-clock Mode) or 1/3 (6-clock Mode) the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction.                                                                                                                                                                                                                                                                |  |

$80C51\ 8\text{-bit}$  microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

|                    |     | PIN N | JMBER |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----|-------|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | DIP | PLCC  | LQFP  | TSSOP | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PSEN               | 29  | 32    | 26    | 18    | 0    | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                              |

| EA/V <sub>PP</sub> | 31  | 35    | 29    | 20    | I    | External Access Enable/Programming Supply Voltage: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to 0FFFH/1FFFH/3FFFH/7FFFH. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than the on-chip ROM/OTP. This pin also receives the 12.75 V programming supply voltage (VPP) during EPROM programming. If security bit 1 is programmed, EA will be internally latched on Reset. |

| XTAL1              | 19  | 21    | 15    | 8     | ı    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL2              | 18  | 20    | 14    | 7     | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# NOTES:

To avoid "latch-up" effect at power-on, the voltage on any pin at any time must not be higher than  $V_{CC}$  + 0.5 V or  $V_{SS}$  – 0.5 V, respectively. 1. Absent in the TSSOP38 package.

2003 Jan 24 11

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

#### **OSCILLATOR CHARACTERISTICS**

## Using the oscillator

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator, as shown in the logic symbol.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. However, minimum and maximum high and low times specified in the data sheet must be observed.

## **Clock Control Register (CKCON)**

This device provides control of the 6-clock/12-clock mode by both an SFR bit (bit X2 in register CKCON and an OTP bit (bit OX2). When X2 is 0, 12-clock mode is activated. By setting this bit to 1, the system is switching to 6-clock mode. Having this option implemented as SFR bit, it can be accessed anytime and changed to either value. Changing X2 from 0 to 1 will result in executing user code at twice the speed, since all system time intervals will be divided by 2. Changing back from 6-clock to 12-clock mode will slow down running code by a factor of 2.

The OTP clock control bit (OX2) activates the 6-clock mode when programmed using a parallel programmer, superceding the X2 bit (CKCON.0). Please also see Table 2 below.

Table 2.

| OX2 clock mode bit (can only be set by parallel programmer) | X2 bit<br>(CKCON.0) | CPU clock mode          |  |

|-------------------------------------------------------------|---------------------|-------------------------|--|

| erased                                                      | 0                   | 12-clock mode (default) |  |

| erased                                                      | 1                   | 6-clock mode            |  |

| programmed                                                  | Х                   | 6-clock mode            |  |

# **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to be output on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- to output a 50% duty cycle clock ranging from 61 Hz to 4 MHz at a 16 MHz operating frequency in 12-clock mode (122 Hz to 8 MHz in 6-clock mode).

To configure the Timer/Counter 2 as a clock generator, bit C/T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

$\frac{\text{Oscillator Frequency}}{\text{n} \times (65536-\text{RCAP2H}, \text{RCAP2L})}$

#### Where:

n = 2 in 6-clock mode, 4 in 12-clock mode.

(RCAP2H,RCAP2L) = the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock

generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will be the same.

#### **RESET**

A reset is accomplished by holding the RST pin HIGH for at least two machine cycles (24 oscillator periods in 12-clock and 12 oscillator periods in 6-clock mode), while the oscillator is running. To insure a reliable power-up reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. After the reset, the part runs in 12-clock mode, unless it has been set to 6-clock operation using a parallel programmer.

## **LOW POWER MODES**

### **Stop Clock Mode**

The static design enables the clock speed to be reduced down to 0 MHz (stopped). When the oscillator is stopped, the RAM and Special Function Registers retain their values. This mode allows step-by-step utilization and permits reduced system power consumption by lowering the clock frequency down to any value. For lowest power consumption the Power Down mode is suggested.

#### Idle Mode

In idle mode (see Table 3), the CPU puts itself to sleep while all of the on-chip peripherals stay active. The instruction to invoke the idle mode is the last instruction executed in the normal operating mode before the idle mode is activated. The CPU contents, the on-chip RAM, and all of the special function registers remain intact during this mode. The idle mode can be terminated either by any enabled interrupt (at which time the process is picked up at the interrupt service routine and continued), or by a hardware reset which starts the processor in the same manner as a power-on reset.

## **Power-Down Mode**

To save even more power, a Power Down mode (see Table 3) can be invoked by software. In this mode, the oscillator is stopped and the instruction that invoked Power Down is the last instruction executed. The on-chip RAM and Special Function Registers retain their values down to 2.0 V and care must be taken to return  $V_{CC}$  to the minimum specified operating voltages before the Power Down Mode is terminated.

Either a hardware reset or external interrupt can be used to exit from Power Down. Reset redefines all the SFRs but does not change the on-chip RAM. An external interrupt allows both the SFRs and the on-chip RAM to retain their values. WUPD (AUXR1.3–Wakeup from Power Down) enables or disables the wakeup from power down with external interrupt. Where:

WUPD = 0: Disable WUPD = 1: Enable

To properly terminate Power Down, the reset or external interrupt should not be executed before  $V_{CC}$  is restored to its normal operating level and must be held active long enough for the oscillator to restart and stabilize (normally less than 10 ms).

To terminate Power Down with an external interrupt, INTO or INT1 must be enabled and configured as level-sensitive. Holding the pin low restarts the oscillator but bringing the pin back high completes the exit. Once the interrupt is serviced, the next instruction to be executed after RETI will be the one following the instruction that put the device into Power Down.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

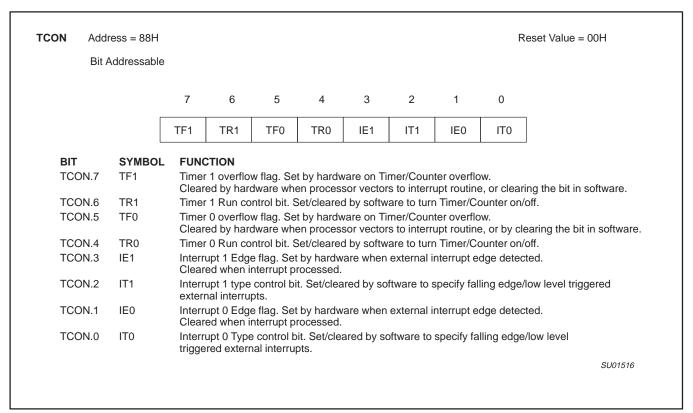

Figure 3. Timer/Counter 0/1 Control (TCON) Register

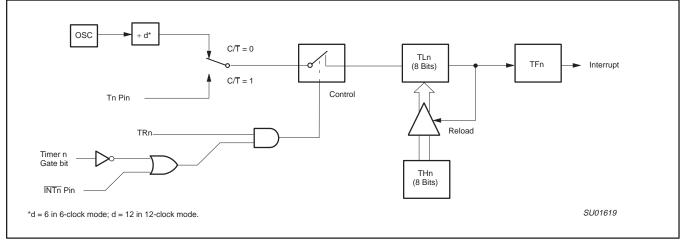

Figure 4. Timer/Counter 0/1 Mode 2: 8-Bit Auto-Reload

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

**Table 4. Timer 2 Operating Modes**

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit Auto-reload  |

| 0           | 1      | 1   | 16-bit Capture      |

| 1           | Х      | 1   | Baud rate generator |

| Х           | Х      | 0   | (off)               |

|        | ddress =<br>t Address |            |                                                                                                                                                                                                                                                                                                                                       |                           |              |                                |                             | ŀ                         | Reset Value                   | = 00H                                              |

|--------|-----------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|--------------------------------|-----------------------------|---------------------------|-------------------------------|----------------------------------------------------|

|        |                       | 7          | 6                                                                                                                                                                                                                                                                                                                                     | 5                         | 4            | 3                              | 2                           | 1                         | 0                             |                                                    |

|        |                       | TF2        | EXF2                                                                                                                                                                                                                                                                                                                                  | RCLK                      | TCLK         | EXEN2                          | TR2                         | C/T2                      | CP/RL2                        |                                                    |

| Symbol | Positi                | on Na      | me and Sig                                                                                                                                                                                                                                                                                                                            | nificance                 |              |                                |                             |                           |                               |                                                    |

| TF2    | T2CO                  |            | ner 2 overflo                                                                                                                                                                                                                                                                                                                         |                           |              | overflow and                   | d must be c                 | leared by so              | oftware. TF2                  | will not be set                                    |

| EXF2   | T2CO                  | EX<br>inte | Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 will cause the CPU to vector to the Timer 2 interrupt routine. EXF2 must be cleared by software. EXF2 does not cause an interrupt in up/down counter mode (DCEN = 1). |                           |              |                                |                             |                           |                               |                                                    |

| RCLK   | T2CO                  |            | ceive clock f<br>modes 1 and                                                                                                                                                                                                                                                                                                          |                           |              |                                |                             |                           |                               | r its receive clock                                |

| TCLK   | T2CO                  |            | ansmit clock<br>modes 1 and                                                                                                                                                                                                                                                                                                           |                           |              |                                |                             |                           |                               | or its transmit clocl<br>ck.                       |

| EXEN2  | T2CO                  | tra        | ner 2 externa<br>nsition on T2<br>ore events a                                                                                                                                                                                                                                                                                        | EX if Timer               | g. When se   | t, allows a ca                 | apture or re<br>lock the se | load to occurial port. EX | ur as a result<br>EN2 = 0 cau | of a negative<br>ses Timer 2 to                    |

| TR2    | T2CO                  | N.2 Sta    | art/stop contr                                                                                                                                                                                                                                                                                                                        | ol for Timer              | 2. A logic 1 | starts the tir                 | mer.                        |                           |                               |                                                    |

| C/T2   | T2CO                  | N.1 Tin    |                                                                                                                                                                                                                                                                                                                                       | nternal time              | r (OSĆ/12 ir | n 12-clock m<br>falling edge t |                             | C/6 in 6-cloc             | ck mode)                      |                                                    |

| CP/RL2 | T2CO                  | cle<br>EX  | ared, auto-re                                                                                                                                                                                                                                                                                                                         | eloads will onen either R | ccur either  | with Timer 2                   | overflows                   | or negative               | transitions a                 | EXEN2 = 1. When<br>T2EX when<br>ced to auto-reload |

Figure 6. Timer/Counter 2 (T2CON) Control Register

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

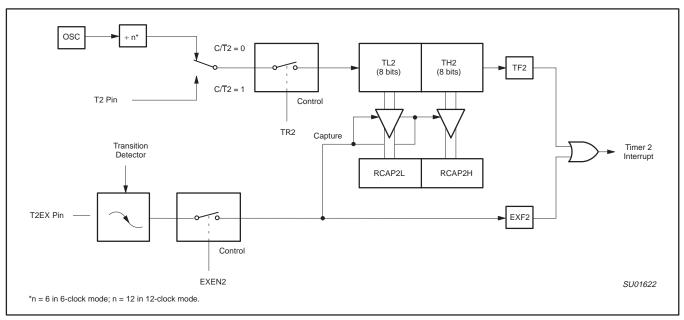

Figure 7. Timer 2 in Capture Mode

| T2MOD  | Address = 0       | СЭН     |                        |               |               |               |             | Reset va     | lue = XXXX XX00E                         |

|--------|-------------------|---------|------------------------|---------------|---------------|---------------|-------------|--------------|------------------------------------------|

|        | Not Bit Addre     | essable |                        |               |               |               |             |              |                                          |

|        | 7                 | 6       | 5                      | 4             | 3             | 2             | 1           | 0            |                                          |

|        | _                 |         | _                      | _             | _             | _             | T2OE        | DCEN         |                                          |

| Symbol | Position          |         | Function  Not implemen | nted, reserve | ed for future | use.*         |             |              |                                          |

| T2OE   | T2MOD.1           |         | Гimer 2 Outp           | •             |               |               |             |              |                                          |

| DCEN   | T2MOD.0           |         | Down Count counter.    | Enable bit. \ | When set, th  | is allows Tir | mer 2 to be | configured a | as an up/down                            |

|        | ase, the reset or |         |                        |               |               |               |             |              | oke new features.<br>n a reserved bit is |

|        |                   |         |                        |               |               |               |             |              |                                          |

Figure 8. Timer 2 Mode (T2MOD) Control Register

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

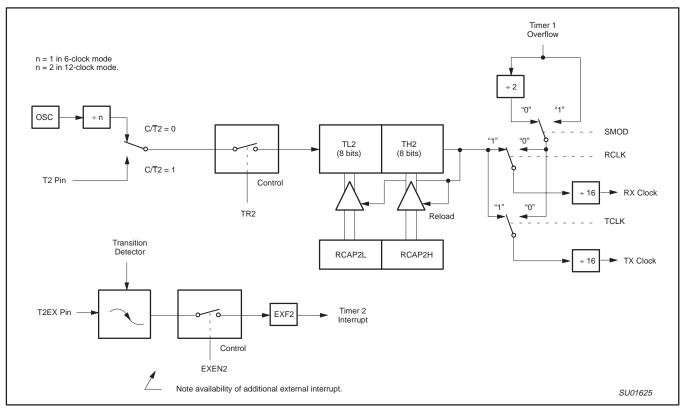

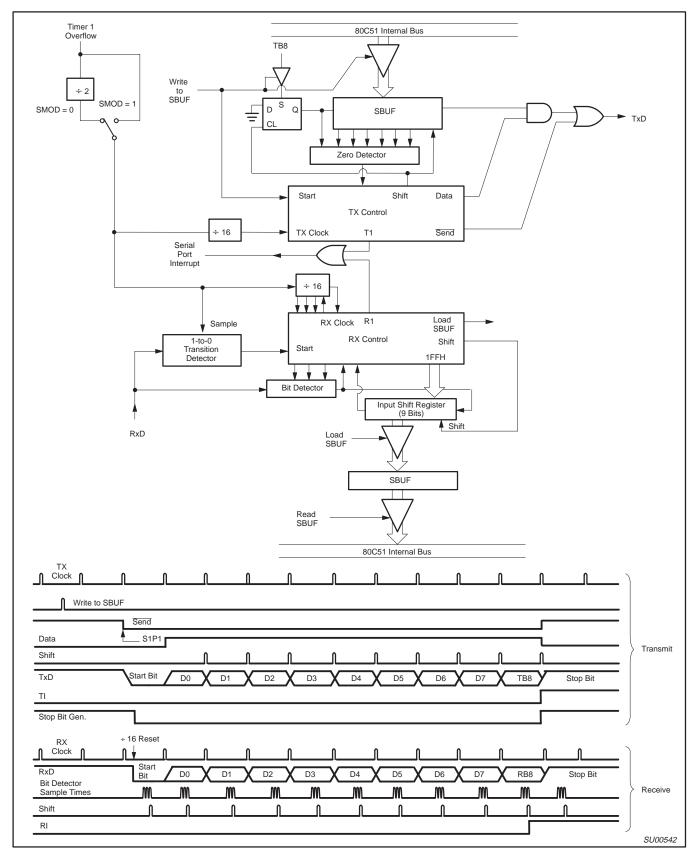

Figure 11. Timer 2 in Baud Rate Generator Mode

# **Baud Rate Generator Mode**

Bits TCLK and/or RCLK in T2CON (Table 4) allow the serial port transmit and receive baud rates to be derived from either Timer 1 or Timer 2. When TCLK= 0, Timer 1 is used as the serial port transmit baud rate generator. When TCLK= 1, Timer 2 is used as the serial port transmit baud rate generator. RCLK has the same effect for the serial port receive baud rate. With these two bits, the serial port can have different receive and transmit baud rates – one generated by Timer 1, the other by Timer 2.

Figure 11 shows the Timer 2 in baud rate generation mode. The baud rate generation mode is like the auto-reload mode, in that a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2H and RCAP2L, which are preset by software.

The baud rates in modes 1 and 3 are determined by Timer 2's overflow rate given below:

Modes 1 and 3 Baud Rates =

$$\frac{\text{Timer 2 Overflow Rate}}{16}$$

The timer can be configured for either "timer" or "counter" operation. In many applications, it is configured for "timer" operation (C/T2=0). Timer operation is different for Timer 2 when it is being used as a baud rate generator.

Usually, as a timer it would increment every machine cycle (i.e., 1/6 the oscillator frequency in 6-clock mode or 1/12 the oscillator frequency in 12-clock mode). As a baud rate generator, it increments at the oscillator frequency in 6-clock mode or at 1/2 the oscillator frequency in 12-clock mode. Thus the baud rate formula is as follows:

Modes 1 and 3 Baud Rates =

Oscillator Frequency

[n × [65536 – (RCAP2H, RCAP2L)]]

Where:

n = 16 in 6-clock mode, 32 in 12-clock mode.

(RCAP2H, RCAP2L)= The content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

The Timer 2 as a baud rate generator mode shown in Figure 11 is valid only if RCLK and/or TCLK = 1 in T2CON register. Note that a rollover in TH2 does not set TF2, and will not generate an interrupt. Thus, the Timer 2 interrupt does not have to be disabled when Timer 2 is in the baud rate generator mode. Also if the EXEN2 (T2 external enable flag) is set, a 1-to-0 transition in T2EX (Timer/counter 2 trigger input) will set EXF2 (T2 external flag) but will not cause a reload from (RCAP2H, RCAP2L) to (TH2,TL2). Therefore when Timer 2 is in use as a baud rate generator, T2EX can be used as an additional external interrupt, if needed.

When Timer 2 is in the baud rate generator mode, one should not try to read or write TH2 and TL2. As a baud rate generator, Timer 2 is incremented every state time (osc/2) or asynchronously from pin T2; under these conditions, a read or write of TH2 or TL2 may not be accurate. The RCAP2 registers may be read, but should not be written to, because a write might overlap a reload and cause write and/or reload errors. The timer should be turned off (clear TR2) before accessing the Timer 2 or RCAP2 registers.

Table 5 shows commonly used baud rates and how they can be obtained from Timer 2.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

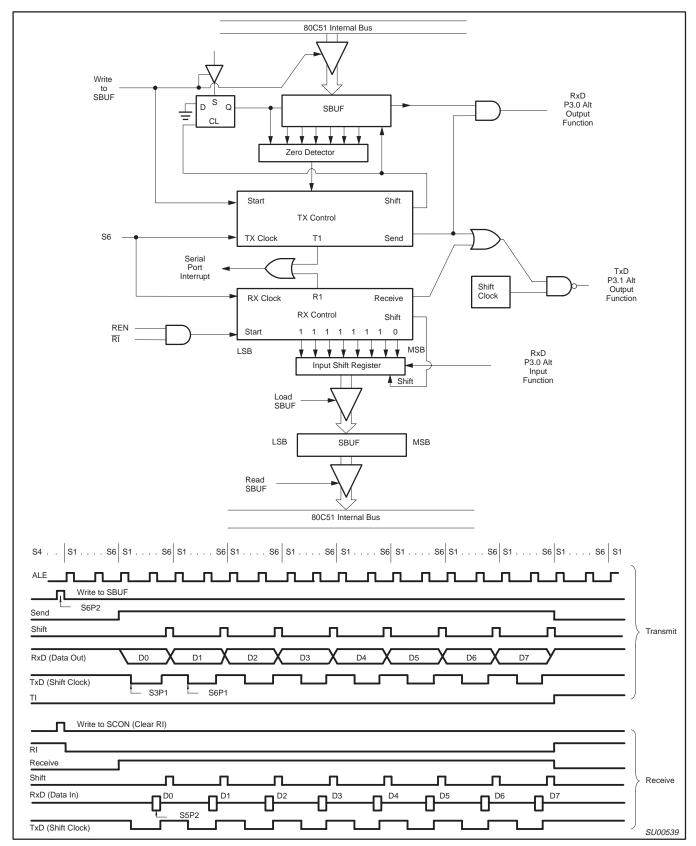

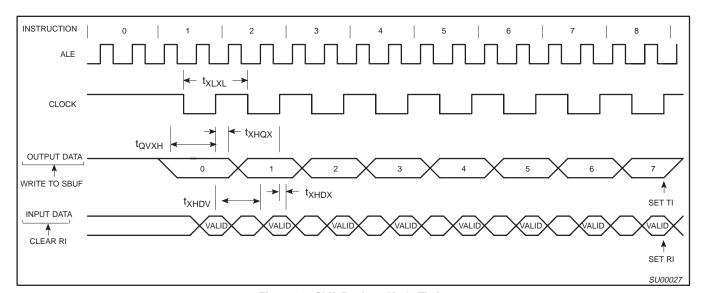

Figure 14. Serial Port Mode 0

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

Figure 17. Serial Port Mode 3

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

|                                            | lress = 98H<br>Addressable |                    |                          |                               |                                     |                            |                               |                      | Reset Value = 0000 0000E                                                                                      |

|--------------------------------------------|----------------------------|--------------------|--------------------------|-------------------------------|-------------------------------------|----------------------------|-------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|

|                                            | 7                          | 6                  | 5                        | 4                             | 3                                   | 2                          | 1                             | 0                    |                                                                                                               |

|                                            | SMC                        | /FE SM1            | SM2                      | REN                           | TB8                                 | RB8                        | TI                            | RI                   |                                                                                                               |

|                                            | (SMO                       | D0 = 0/1)*         | •                        | '                             |                                     |                            |                               |                      |                                                                                                               |

| Symbol                                     | Position                   | Function           | on                       |                               |                                     |                            |                               |                      |                                                                                                               |

| FE                                         | SCON.7                     | cleared            |                          | ames but sho                  |                                     |                            |                               |                      | etected. The FE bit is not must be set to enable                                                              |

| SM0                                        | SCON.7                     | Serial F           | ort Mode I               | Bit 0, (SMOD                  | 0  must = 0  to                     | access bit                 | SM0)                          |                      |                                                                                                               |

| SM1                                        | SCON.6                     | Serial F           | ort Mode I               | Bit 1                         |                                     |                            | ,                             |                      |                                                                                                               |

|                                            |                            | SM0                | SM1                      | Mode                          | Description                         | Bau                        | d Rate**                      |                      |                                                                                                               |

|                                            |                            | 0                  | 0<br>1                   | 0<br>1                        | shift register<br>8-bit UART        | f <sub>OSC</sub>           | ,                             | mode) or             | f <sub>OSC</sub> /6 (6-clk mode)                                                                              |

|                                            |                            | 1                  | 0                        | 2                             | 9-bit UART                          | fosc                       |                               |                      | <sub>SC</sub> /16 (6-clock mode) or                                                                           |

|                                            |                            | 1                  | 1                        | 3                             | 9-bit UART                          | varia                      | ble                           | ,                    |                                                                                                               |

| SM2                                        | SCON.5                     | unless t<br>Broadc | he receive<br>ast Addres | d 9th data bi<br>s. In Mode 1 | t (RB8) is 1, ir<br>, if SM2 = 1 th | dicating a<br>en RI will r | n address, a<br>not be activa | and the reated unles | 2 = 1 then RI will not be set<br>eceived byte is a Given or<br>ss a valid stop bit was<br>0, SM2 should be 0. |

| REN                                        | SCON.4                     | Enables            | s serial rec             | eption. Set b                 | y software to                       | enable rec                 | eption. Clea                  | r by soft            | ware to disable reception.                                                                                    |

| TB8                                        | SCON.3                     | The 9th            | data bit th              | at will be trai               | nsmitted in Mo                      | des 2 and                  | 3. Set or cl                  | ear by so            | oftware as desired.                                                                                           |

| RB8                                        | SCON.2                     | was red            |                          |                               | bit that was re                     | eceived. In                | Mode 1, if                    | SM2 = 0,             | RB8 is the stop bit that                                                                                      |

| TI                                         | SCON.1                     |                    |                          |                               | nardware at th<br>, in any serial t |                            |                               |                      | de 0, or at the beginning of by software.                                                                     |

| RI                                         | SCON.0                     |                    | time in the              |                               |                                     |                            |                               |                      | e 0, or halfway through the<br>Must be cleared by                                                             |

| TES:<br>MOD0 is locate<br>asc = oscillator |                            |                    |                          |                               |                                     |                            |                               |                      | SU0162                                                                                                        |

Figure 18. SCON: Serial Port Control Register

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# AC ELECTRICAL CHARACTERISTICS (12-CLOCK MODE, 2.7 V TO 5.5 V OPERATION)

$T_{amb} = 0$  °C to +70 °C or -40 °C to +85 °C :  $V_{CC} = 2.7$  V to 5.5 V.  $V_{SS} = 0$  V<sup>1,2,3,4</sup>

| Symbol              | Figure | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Limits                   |                                       | 16 MHz | Clock | Unit |

|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------|--------|-------|------|

|                     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MIN                      | MAX                                   | MIN    | MAX   | ٦    |

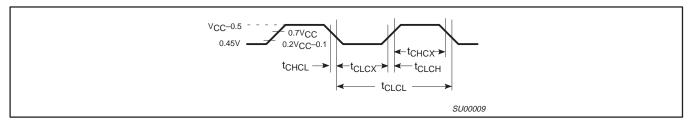

| 1/t <sub>CLCL</sub> | 31     | Oscillator frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0                        | 16                                    | _      | _     | MHz  |

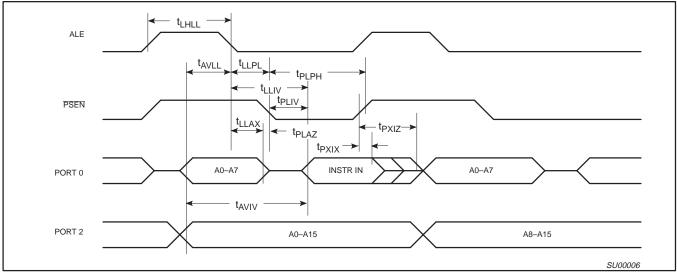

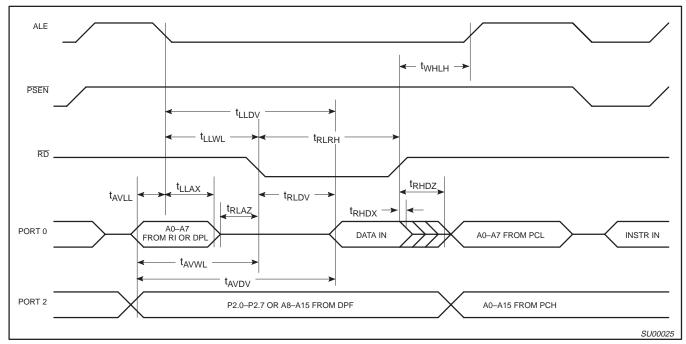

| t <sub>LHLL</sub>   | 27     | ALE pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2t <sub>CLCL</sub> -10   | _                                     | 115    | _     | ns   |

| t <sub>AVLL</sub>   | 27     | Address valid to ALE low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | t <sub>CLCL</sub> -15    | _                                     | 47.5   | -     | ns   |

| t <sub>LLAX</sub>   | 27     | Address hold after ALE low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t <sub>CLCL</sub> –25    | -                                     | 37.5   | _     | ns   |

| t <sub>LLIV</sub>   | 27     | ALE low to valid instruction in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                        | 4 t <sub>CLCL</sub> -55               | _      | 195   | ns   |

| t <sub>LLPL</sub>   | 27     | ALE low to PSEN low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | t <sub>CLCL</sub> -15    | -                                     | 47.5   | _     | ns   |

| t <sub>PLPH</sub>   | 27     | PSEN pulse width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3 t <sub>CLCL</sub> -15  | _                                     | 172.5  | _     | ns   |