Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | 8051                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 33MHz                                                                  |

| Connectivity               | EBI/EMI, UART/USART                                                    |

| Peripherals                | POR                                                                    |

| Number of I/O              | 32                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | OTP                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | -                                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-DIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p87c52x2bn-112 |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

# P80C3xX2; P80C5xX2; P87C5xX2

### **FEATURES**

- 80C51 Central Processing Unit

- 4 kbytes ROM/EPROM (P80/P87C51X2)

- 8 kbytes ROM/EPROM (P80/P87C52X2)

- 16 kbytes ROM/EPROM (P80/P87C54X2)

- 32 kbytes ROM/EPROM (P80/P87C58X2)

- 128 byte RAM (P80/P87C51X2 and P80C31X2)

- 256 byte RAM (P80/P87C52/54X2/58X2 and P80C32X2)

- Boolean processor

- Fully static operation

- Low voltage (2.7 V to 5.5 V at 16 MHz) operation

- 12-clock operation with selectable 6-clock operation (via software or via parallel programmer)

- Memory addressing capability

- Up to 64 kbytes ROM and 64 kbytes RAM

- Power control modes:

- Clock can be stopped and resumed

- Idle mode

- Power-down mode

- CMOS and TTL compatible

- Two speed ranges at V<sub>CC</sub> = 5 V

- 0 to 30 MHz with 6-clock operation

- 0 to 33 MHz with 12-clock operation

- PLCC, DIP, TSSOP or LQFP packages

- Extended temperature ranges

- Dual Data Pointers

- Security bits:

- ROM (2 bits)

- OTP (3 bits)

- Encryption array 64 bytes

- Four interrupt priority levels

- Six interrupt sources

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Three 16-bit timers/counters T0, T1 (standard 80C51) and additional T2 (capture and compare)

- Programmable clock-out pin

- Asynchronous port reset

- Low EMI (inhibit ALE, slew rate controlled outputs, and 6-clock mode)

- Wake-up from Power Down by an external interrupt.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

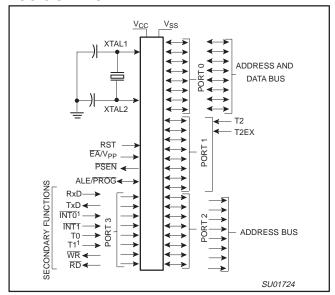

# LOGIC SYMBOL

NOTE:

1. INTO/P3.2 and T1/P3.5 are absent in the TSSOP38 package.

# PLASTIC DUAL IN-LINE PACKAGE PIN CONFIGURATIONS

$80C51\ 8\text{-bit}$  microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

|                    |     | PIN N | JMBER |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----|-------|-------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC           | DIP | PLCC  | LQFP  | TSSOP | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PSEN               | 29  | 32    | 26    | 18    | 0    | Program Store Enable: The read strobe to external program memory. When the device is executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.                                                                                                                                                                              |

| EA/V <sub>PP</sub> | 31  | 35    | 29    | 20    | I    | External Access Enable/Programming Supply Voltage: EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to 0FFFH/1FFFH/3FFFH/7FFFH. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than the on-chip ROM/OTP. This pin also receives the 12.75 V programming supply voltage (VPP) during EPROM programming. If security bit 1 is programmed, EA will be internally latched on Reset. |

| XTAL1              | 19  | 21    | 15    | 8     | ı    | <b>Crystal 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTAL2              | 18  | 20    | 14    | 7     | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# NOTES:

To avoid "latch-up" effect at power-on, the voltage on any pin at any time must not be higher than  $V_{CC}$  + 0.5 V or  $V_{SS}$  – 0.5 V, respectively. 1. Absent in the TSSOP38 package.

2003 Jan 24 11

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

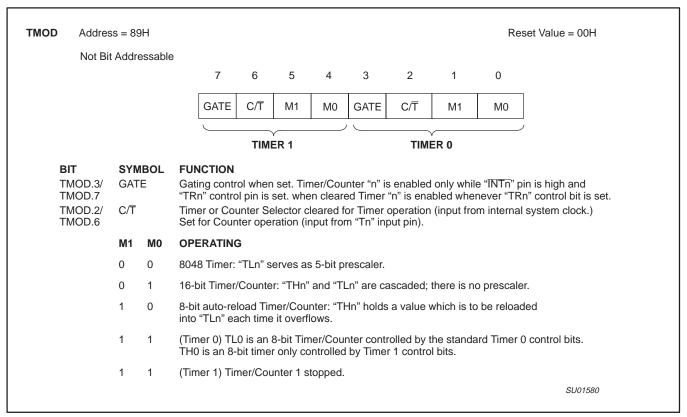

Figure 1. Timer/Counter 0/1 Mode Control (TMOD) Register

Figure 2. Timer/Counter 0/1 Mode 0: 13-Bit Timer/Counter

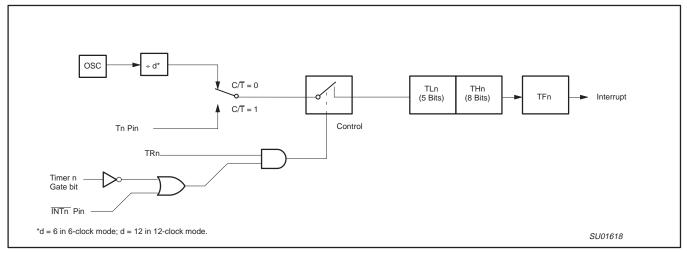

Figure 14. Serial Port Mode 0

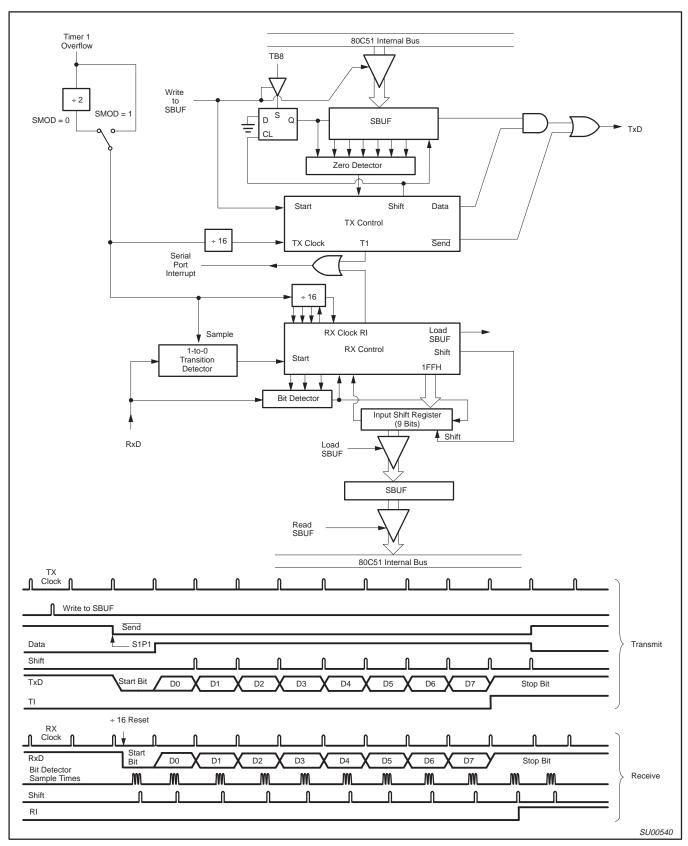

Figure 15. Serial Port Mode 1

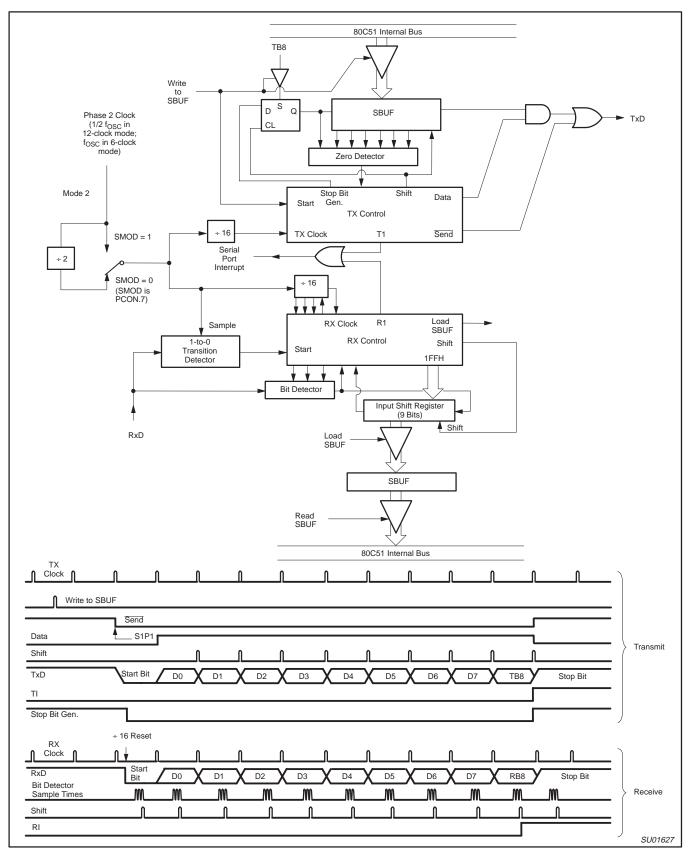

Figure 16. Serial Port Mode 2

P80C3xX2; P80C5xX2; P87C5xX2

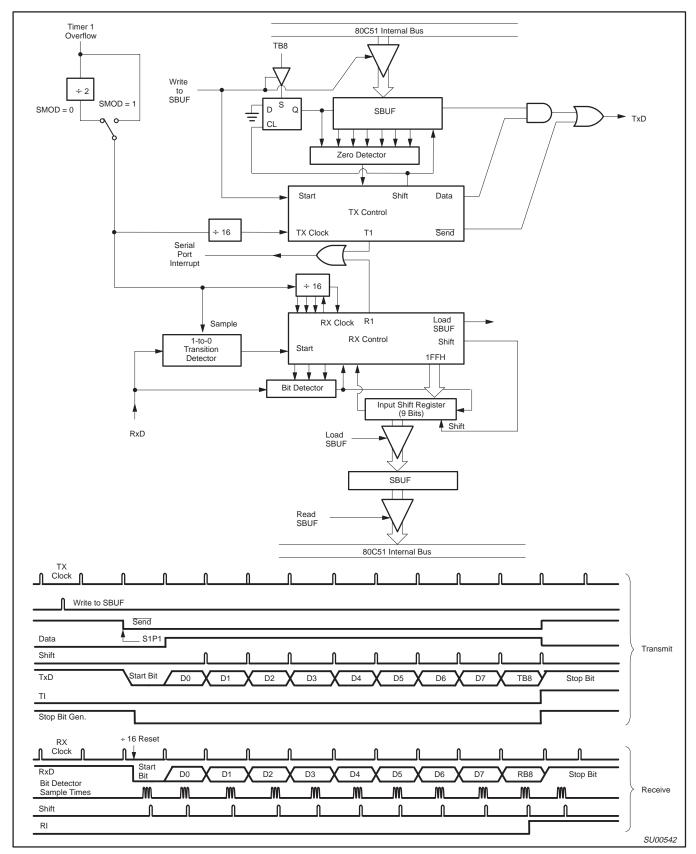

Figure 17. Serial Port Mode 3

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# **Enhanced UART operation**

In addition to the standard operation modes, the UART can perform framing error detect by looking for missing stop bits, and automatic address recognition. The UART also fully supports multiprocessor communication.

When used for framing error detect the UART looks for missing stop bits in the communication. A missing bit will set the FE bit in the SCON register. The FE bit shares the SCON.7 bit with SM0 and the function of SCON.7 is determined by PCON.6 (SMOD0) (see Figure 18). If SMOD0 is set then SCON.7 functions as FE. SCON.7 functions as SM0 when SMOD0 is cleared. When used as FE SCON.7 can only be cleared by software. Refer to Figure 19.

## **Automatic Address Recognition**

Automatic Address Recognition is a feature which allows the UART to recognize certain addresses in the serial bit stream by using hardware to make the comparisons. This feature saves a great deal of software overhead by eliminating the need for the software to examine every serial address which passes by the serial port. This feature is enabled by setting the SM2 bit in SCON. In the 9 bit UART modes, mode 2 and mode 3, the Receive Interrupt flag (RI) will be automatically set when the received byte contains either the "Given" address or the "Broadcast" address. The 9 bit mode requires that the 9th information bit is a 1 to indicate that the received information is an address and not data. Automatic address recognition is shown in Figure 20.

The 8 bit mode is called Mode 1. In this mode the RI flag will be set if SM2 is enabled and the information received has a valid stop bit following the 8 address bits and the information is either a Given or Broadcast address.

Mode 0 is the Shift Register mode and SM2 is ignored.

Using the Automatic Address Recognition feature allows a master to selectively communicate with one or more slaves by invoking the Given slave address or addresses. All of the slaves may be contacted by using the Broadcast address. Two special Function Registers are used to define the slave's address, SADDR, and the address mask, SADEN. SADEN is used to define which bits in the SADDR are to be used and which bits are "don't care". The SADEN mask can be logically ANDed with the SADDR to create the "Given" address which the master will use for addressing each of the slaves. Use of the Given address allows multiple slaves to be recognized while excluding others. The following examples will help to show the versatility of this scheme:

Slave 0 SADDR = 1100 0000

SADEN = 1111 1101Given = 1100 00X0 Slave 1 SADDR = 1100 0000 SADEN = 1111 1110 Given = 1100 000X

In the above example SADDR is the same and the SADEN data is used to differentiate between the two slaves. Slave 0 requires a 0 in bit 0 and it ignores bit 1. Slave 1 requires a 0 in bit 1 and bit 0 is ignored. A unique address for Slave 0 would be 1100 0010 since slave 1 requires a 0 in bit 1. A unique address for slave 1 would be 1100 0001 since a 1 in bit 0 will exclude slave 0. Both slaves can be selected at the same time by an address which has bit 0 = 0 (for slave 0) and bit 1 = 0 (for slave 1). Thus, both could be addressed with 1100 0000.

In a more complex system the following could be used to select slaves 1 and 2 while excluding slave 0:

| Slave 0 | SADDR | = | 1100 0000 |

|---------|-------|---|-----------|

|         | SADEN | = | 1111 1001 |

|         | Given | = | 1100 0XX0 |

| Slave 1 | SADDR | = | 1110 0000 |

|         | SADEN | = | 1111 1010 |

|         | Given | = | 1110 0X0X |

| Slave 2 | SADDR | = | 1110 0000 |

|         | SADEN | = | 1111 1100 |

|         | Given | = | 1110 00XX |

In the above example the differentiation among the 3 slaves is in the lower 3 address bits. Slave 0 requires that bit 0=0 and it can be uniquely addressed by 1110 0110. Slave 1 requires that bit 1=0 and it can be uniquely addressed by 1110 and 0101. Slave 2 requires that bit 2=0 and its unique address is 1110 0011. To select Slaves 0 and 1 and exclude Slave 2 use address 1110 0100, since it is necessary to make bit 2=1 to exclude slave 2.

The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zeros in this result are trended as don't-cares. In most cases, interpreting the don't-cares as ones, the broadcast address will be FF hexadecimal.

Upon reset SADDR (SFR address 0A9H) and SADEN (SFR address 0B9H) are leaded with 0s. This produces a given address of all "don't cares" as well as a Broadcast address of all "don't cares". This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard 80C51 type UART drivers which do not make use of this feature.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# **Interrupt Priority Structure**

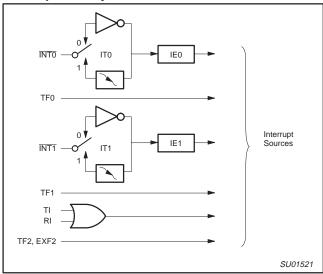

Figure 21. Interrupt Sources

# Interrupts

The devices described in this data sheet provide six interrupt sources. These are shown in Figure 21. The External Interrupts INTO and INTT can each be either level-activated or transition-activated, depending on bits ITO and IT1 in Register TCON. The flags that actually generate these interrupts are bits IEO and IE1 in TCON. When an external interrupt is generated, the flag that generated it is cleared by the hardware when the service routine is vectored to only if the interrupt was transition-activated. If the interrupt was level-activated, then the external requesting source is what controls the request flag, rather than the on-chip hardware.

The Timer 0 and Timer 1 Interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/Counter registers (except see Timer 0 in Mode 3). When a timer interrupt is generated, the flag that generated it is cleared by the on-chip hardware when the service routine is vectored to.

The Serial Port Interrupt is generated by the logical OR of RI and TI. Neither of these flags is cleared by hardware when the service routine is vectored to. In fact, the service routine will normally have to determine whether it was RI or TI that generated the interrupt, and the bit will have to be cleared in software.

All of the bits that generate interrupts can be set or cleared by software, with the same result as though it had been set or cleared by hardware. That is, interrupts can be generated or pending interrupts can be canceled in software.

Each of these interrupt sources can be individually enabled or disabled by setting or clearing a bit in Special Function Register IE (Figure 22). IE also contains a global disable bit,  $\overline{\text{EA}}$ , which disables all interrupts at once.

### **Priority Level Structure**

Each interrupt source can also be individually programmed to one of four priority levels by setting or clearing bits in Special Function Registers IP (Figure 23) and IPH (Figure 24). A lower-priority interrupt can itself be interrupted by a higher-priority interrupt, but not by another interrupt of the same level. A high-priority level 3 interrupt can't be interrupted by any other interrupt source.

If two request of different priority levels are received simultaneously, the request of higher priority level is serviced. If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence as follows:

# Source Priority Within Level

1. IE0 (External Int 0)

(highest)

- 2. TF0 (Timer 0)

- 3. IE1 (External Int 1)

- 4. TF1 (Timer 1)

- 5. RI+TI (UART)

- 6. TF2, EXF2 (Timer 2) (lowest)

Note that the "priority within level" structure is only used to resolve simultaneous requests of the same priority level.

The IP and IPH registers contain a number of unimplemented bits. User software should not write 1s to these positions, since they may be used in other 80C51 Family products.

# **How Interrupts Are Handled**

The interrupt flags are sampled at S5P2 of every machine cycle. The samples are polled during the following machine cycle. If one of the flags was in a set condition at S5P2 of the preceding cycle, the polling cycle will find it and the interrupt system will generate an LCALL to the appropriate service routine, provided this hardware-generated LCALL is not blocked by any of the following conditions:

- An interrupt of equal or higher priority level is already in progress.

- 2. The current (polling) cycle is not the final cycle in the execution of the instruction in progress.

- The instruction in progress is RETI or any write to the IE or IP registers.

Any of these three conditions will block the generation of the LCALL to the interrupt service routine. Condition 2 ensures that the instruction in progress will be completed before vectoring to any service routine. Condition 3 ensures that if the instruction in progress is RETI or any access to IE or IP, then at least one more instruction will be executed before any interrupt is vectored to.

The polling cycle is repeated with each machine cycle, and the values polled are the values that were present at S5P2 of the previous machine cycle. Note that if an interrupt flag is active but not being responded to for one of the above conditions, if the flag is not still active when the blocking condition is removed, the denied interrupt will not be serviced. In other words, the fact that the interrupt flag was once active but not serviced is not remembered. Every polling cycle is new.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

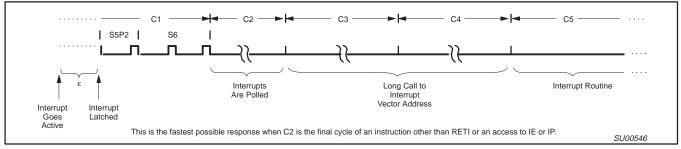

Figure 25. Interrupt Response Timing Diagram

The polling cycle/LCALL sequence is illustrated in Figure 25.

Note that if an interrupt of higher priority level goes active prior to S5P2 of the machine cycle labeled C3 in Figure 25, then in accordance with the above rules it will be vectored to during C5 and C6, without any instruction of the lower priority routine having been executed.

Thus the processor acknowledges an interrupt request by executing a hardware-generated LCALL to the appropriate servicing routine. In some cases it also clears the flag that generated the interrupt, and in other cases it doesn't. It never clears the Serial Port flag. This has to be done in the user's software. It clears an external interrupt flag (IE0 or IE1) only if it was transition-activated. The hardware-generated LCALL pushes the contents of the Program Counter on to the stack (but it does not save the PSW) and reloads the PC with an address that depends on the source of the interrupt being vectored to, as shown in Table 8.

Execution proceeds from that location until the RETI instruction is encountered. The RETI instruction informs the processor that this interrupt routine is no longer in progress, then pops the top two bytes from the stack and reloads the Program Counter. Execution of the interrupted program continues from where it left off.

Note that a simple RET instruction would also have returned execution to the interrupted program, but it would have left the interrupt control system thinking an interrupt was still in progress, making future interrupts impossible.

### **External Interrupts**

The external sources can be programmed to be level-activated or transition-activated by setting or clearing bit IT1 or IT0 in Register TCON. If ITx = 0, external interrupt x is triggered by a detected low at the  $\overline{\text{INTx}}$  pin. If ITx = 1, external interrupt x is edge triggered. In this mode if successive samples of the  $\overline{\text{INTx}}$  pin show a high in one cycle and a low in the next cycle, interrupt request flag IEx in TCON is set. Flag bit IEx then requests the interrupt.

Since the external interrupt pins are sampled once each machine cycle, an input high or low should hold for at least 12 oscillator periods to ensure sampling. If the external interrupt is transition-activated, the external source has to hold the request pin high for at least one cycle, and then hold it low for at least one cycle. This is done to ensure that the transition is seen so that interrupt request flag IEx will be set. IEx will be automatically cleared by the CPU when the service routine is called.

If the external interrupt is level-activated, the external source has to hold the request active until the requested interrupt is actually generated. Then it has to deactivate the request before the interrupt

service routine is completed, or else another interrupt will be generated.

# **Response Time**

The INTO and INTO levels are inverted and latched into IEO and IE1 at S5P2 of every machine cycle. The values are not actually polled by the circuitry until the next machine cycle. If a request is active and conditions are right for it to be acknowledged, a hardware subroutine call to the requested service routine will be the next instruction to be executed. The call itself takes two cycles. Thus, a minimum of three complete machine cycles elapse between activation of an external interrupt request and the beginning of execution of the first instruction of the service routine. Figure 25 shows interrupt response timings.

A longer response time would result if the request is blocked by one of the 3 previously listed conditions. If an interrupt of equal or higher priority level is already in progress, the additional wait time obviously depends on the nature of the other interrupt's service routine. If the instruction in progress is not in its final cycle, the additional wait time cannot be more the 3 cycles, since the longest instructions (MUL and DIV) are only 4 cycles long, and if the instruction in progress is RETI or an access to IE or IP, the additional wait time cannot be more than 5 cycles (a maximum of one more cycle to complete the instruction in progress, plus 4 cycles to complete the next instruction if the instruction is MUL or DIV).

Thus, in a single-interrupt system, the response time is always more than 3 cycles and less than 9 cycles.

As previously mentioned, the derivatives described in this data sheet have a four-level interrupt structure. The corresponding registers are IE, IP and IPH. (See Figures 22, 23, and 24.) The IPH (Interrupt Priority High) register makes the four-level interrupt structure possible.

The function of the IPH SFR is simple and when combined with the IP SFR determines the priority of each interrupt. The priority of each interrupt is determined as shown in the following table:

| PRIORI" | TY BITS | INTERRUPT PRIORITY LEVEL   |  |  |  |  |

|---------|---------|----------------------------|--|--|--|--|

| IPH.x   | IP.x    | INTERROPT PRIORITY LEVEL   |  |  |  |  |

| 0       | 0       | Level 0 (lowest priority)  |  |  |  |  |

| 0       | 1       | Level 1                    |  |  |  |  |

| 1       | 0       | Level 2                    |  |  |  |  |

| 1       | 1       | Level 3 (highest priority) |  |  |  |  |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# **ABSOLUTE MAXIMUM RATINGS**1, 2, 3

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on EA/V <sub>PP</sub> pin to V <sub>SS</sub>                                         | 0 to +13.0             | V    |

| Voltage on any other pin to V <sub>SS</sub>                                                  | -0.5 to +6.5           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

### NOTES:

1. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise

Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

# **AC ELECTRICAL CHARACTERISTICS**

$T_{amb} = 0$ °C to +70°C or -40°C to +85°C

|                     |        |                      |                |                         | CLOCK FREQUENCY<br>RANGE |     |      |

|---------------------|--------|----------------------|----------------|-------------------------|--------------------------|-----|------|

| SYMBOL              | FIGURE | PARAMETER            | OPERATING MODE | POWER SUPPLY<br>VOLTAGE | MIN                      | MAX | UNIT |

| 1/t <sub>CLCL</sub> | 31     | Oscillator frequency | 6-clock        | 5 V ± 10%               | 0                        | 30  | MHz  |

|                     |        |                      | 6-clock        | 2.7 V to 5.5 V          | 0                        | 16  | MHz  |

|                     |        |                      | 12-clock       | 5 V ± 10%               | 0                        | 33  | MHz  |

|                     |        |                      | 12-clock       | 2.7 V to 5.5 V          | 0                        | 16  | MHz  |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz) P80C3xX2; P80C5xX2; P87C5xX2

### DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = 0 °C to +70 °C or -40 °C to +85 °C;  $V_{CC}$  = 5 V ±10%;  $V_{SS}$  = 0 V (30/33 MHz max. CPU clock)

| SYMBOL           | PARAMETER                                                                               | TEST<br>CONDITIONS                                                | LIMITS                   |                  |                          | UNIT |

|------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|------------------|--------------------------|------|

|                  |                                                                                         |                                                                   | MIN                      | TYP <sup>1</sup> | MAX                      | 7    |

| V <sub>IL</sub>  | Input low voltage <sup>11</sup>                                                         | 4.5 V < V <sub>CC</sub> < 5.5 V                                   | -0.5                     |                  | 0.2 V <sub>CC</sub> -0.1 | V    |

| V <sub>IH</sub>  | Input high voltage (ports 0, 1, 2, 3, EA)                                               | -                                                                 | 0.2 V <sub>CC</sub> +0.9 |                  | V <sub>CC</sub> +0.5     | V    |

| V <sub>IH1</sub> | Input high voltage, XTAL1, RST <sup>11</sup>                                            | -                                                                 | 0.7 V <sub>CC</sub>      |                  | V <sub>CC</sub> +0.5     | V    |

| V <sub>OL</sub>  | Output low voltage, ports 1, 2, 3 8                                                     | $V_{CC} = 4.5 \text{ V}; I_{OL} = 1.6 \text{ mA}^2$               | -                        |                  | 0.4                      | V    |

| V <sub>OL1</sub> | Output low voltage, port 0, ALE, PSEN 7, 8                                              | $V_{CC} = 4.5 \text{ V}; I_{OL} = 3.2 \text{ mA}^2$               | _                        |                  | 0.4                      | V    |

| V <sub>OH</sub>  | Output high voltage, ports 1, 2, 3 3                                                    | $V_{CC} = 4.5 \text{ V}; I_{OH} = -30 \mu\text{A}$                | V <sub>CC</sub> – 0.7    |                  | -                        | V    |

| V <sub>OH1</sub> | Output high voltage (port 0 in external bus mode), ALE <sup>9</sup> , PSEN <sup>3</sup> | $V_{CC} = 4.5 \text{ V}; I_{OH} = -3.2 \text{ mA}$                | V <sub>CC</sub> - 0.7    |                  | _                        | V    |

| I <sub>IL</sub>  | Logical 0 input current, ports 1, 2, 3                                                  | V <sub>IN</sub> = 0.4 V                                           | -1                       |                  | -50                      | μΑ   |

| I <sub>TL</sub>  | Logical 1-to-0 transition current, ports 1, 2, 36                                       | V <sub>IN</sub> = 2.0 V; See note 4                               | -                        |                  | -650                     | μΑ   |

| I <sub>LI</sub>  | Input leakage current, port 0                                                           | $0.45 < V_{IN} < V_{CC} - 0.3$                                    | -                        |                  | ±10                      | μΑ   |

| I <sub>CC</sub>  | Power supply current (see Figure 34): Active mode (see Note 5) Idle mode (see Note 5)   |                                                                   |                          |                  |                          |      |

|                  | Power-down mode or clock stopped (see Figure 39 for conditions)                         | T <sub>amb</sub> = 0 °C to 70 °C                                  |                          | 2                | 30                       | μΑ   |

|                  |                                                                                         | $T_{amb} = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$ |                          | 3                | 50                       | μΑ   |

| $V_{RAM}$        | RAM keep-alive voltage                                                                  | _                                                                 | 1.2                      |                  |                          | V    |

| R <sub>RST</sub> | Internal reset pull-down resistor                                                       | _                                                                 | 40                       |                  | 225                      | kΩ   |

| C <sub>IO</sub>  | Pin capacitance <sup>10</sup> (except EA)                                               | _                                                                 | _                        |                  | 15                       | pF   |

### NOTES:

- 1. Typical ratings are not guaranteed. The values listed are at room temperature, 5 V.

- 2. Capacitive loading on ports 0 and 2 may cause spurious noise to be superimposed on the V<sub>OL</sub>s of ALE and ports 1 and 3. The noise is due to external bus capacitance discharging into the port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100 pF), the noise pulse on the ALE pin may exceed 0.8 V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input. I<sub>OL</sub> can exceed these conditions provided that no single output sinks more than 5 mA and no more than two outputs exceed the test conditions.

- 3. Capacitive loading on ports 0 and 2 may cause the V<sub>OH</sub> on ALE and PSEN to momentarily fall below the V<sub>CC</sub>-0.7 specification when the address bits are stabilizing.

- Pins of ports 1, 2 and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2 V.

- 5. See Figures 36 through 39 for  $I_{CC}$  test conditions and Figure 34 for  $I_{CC}$  vs. Frequency.

12-clock mode characteristics:

- 6. This value applies to  $T_{amb} = 0^{\circ}C$  to  $+70^{\circ}C$ . For  $T_{amb} = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $I_{TL} = -750 \,\mu\text{A}$ .

- 7. Load capacitance for port 0, ALE, and  $\overline{\text{PSEN}} = 100 \, \text{pF}$ , load capacitance for all other outputs = 80 pF.

- 8. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 15 mA (\*NOTE: This is 85 °C specification.)

Maximum I<sub>OL</sub> per 8-bit port: 26 mA

Maximum I<sub>OL</sub> per 8-bit port: 26 mA Maximum total I<sub>OL</sub> for all outputs: 71 mA

If I<sub>OL</sub> exceeds the test condition, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 9. ALE is tested to V<sub>OH1</sub>, except when ALE is off then V<sub>OH</sub> is the voltage specification.

- 10. Pin capacitance is characterized but not tested. Pin capacitance is less than 25 pF. Pin capacitance of ceramic package is less than 15 pF (except EA is 25 pF).

- 11. To improve noise rejection a nominal 100 ns glitch rejection circuitry has been added to the RST pin, and a nominal 15 ns glitch rejection circuitry has been added to the INTO and INTO pins. Previous devices provided only an inherent 5 ns of glitch rejection.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# AC ELECTRICAL CHARACTERISTICS (12-CLOCK MODE, 2.7 V TO 5.5 V OPERATION)

$T_{amb} = 0$  °C to +70 °C or -40 °C to +85 °C;  $V_{CC} = 2.7$  V to 5.5 V,  $V_{SS} = 0$  V<sup>1,2,3,4</sup>

| Symbol              | Figure | Parameter                                | Limits                   |                                       | 16 MHz   | Clock | Unit |  |

|---------------------|--------|------------------------------------------|--------------------------|---------------------------------------|----------|-------|------|--|

|                     |        |                                          | MIN                      | MAX                                   | MIN      | MAX   | ٦    |  |

| 1/t <sub>CLCL</sub> | 31     | Oscillator frequency                     | 0                        | 16                                    | -        | _     | MHz  |  |

| tLHLL               | 27     | ALE pulse width                          | 2t <sub>CLCL</sub> -10   | _                                     | 115      | _     | ns   |  |

| t <sub>AVLL</sub>   | 27     | Address valid to ALE low                 | t <sub>CLCL</sub> -15    | _                                     | 47.5     | _     | ns   |  |

| t <sub>LLAX</sub>   | 27     | Address hold after ALE low               | t <sub>CLCL</sub> -25    | _                                     | 37.5     | _     | ns   |  |

| t <sub>LLIV</sub>   | 27     | ALE low to valid instruction in          | _                        | 4 t <sub>CLCL</sub> -55               | _        | 195   | ns   |  |

| t <sub>LLPL</sub>   | 27     | ALE low to PSEN low                      | t <sub>CLCL</sub> -15    | -                                     | 47.5     | _     | ns   |  |

| t <sub>PLPH</sub>   | 27     | PSEN pulse width                         | 3 t <sub>CLCL</sub> -15  | _                                     | 172.5    | _     | ns   |  |

| t <sub>PLIV</sub>   | 27     | PSEN low to valid instruction in         | -                        | 3 t <sub>CLCL</sub> -55               | -        | 132.5 | ns   |  |

| t <sub>PXIX</sub>   | 27     | Input instruction hold after PSEN        | 0                        | -                                     | 0        | _     | ns   |  |

| t <sub>PXIZ</sub>   | 27     | Input instruction float after PSEN       | _                        | t <sub>CLCL</sub> -10                 | 1-       | 52.5  | ns   |  |

| t <sub>AVIV</sub>   | 27     | Address to valid instruction in          | _                        | 5 t <sub>CLCL</sub> –50               | -        | 262.5 | ns   |  |

| t <sub>PLAZ</sub>   | 27     | PSEN low to address float                | _                        | 10                                    | -        | 10    | ns   |  |

| Data Mem            |        |                                          | 1                        | 1                                     |          | ı     |      |  |

| t <sub>RLRH</sub>   | 28     | RD pulse width                           | 6 t <sub>CLCL</sub> -25  | _                                     | 350      | _     | ns   |  |

| t <sub>WLWH</sub>   | 29     | WR pulse width                           | 6 t <sub>CLCL</sub> -25  | _                                     | 350      | _     | ns   |  |

| t <sub>RLDV</sub>   | 28     | RD low to valid data in                  | -                        | 5 t <sub>CLCL</sub> -50               | -        | 262.5 | ns   |  |

| t <sub>RHDX</sub>   | 28     | Data hold after RD                       | 0                        | -                                     | 0        | _     | ns   |  |

| t <sub>RHDZ</sub>   | 28     | Data float after RD                      | _                        | 2 t <sub>CLCL</sub> –20               | _        | 105   | ns   |  |

| t <sub>LLDV</sub>   | 28     | ALE low to valid data in                 | _                        | 8 t <sub>CLCL</sub> –55               | _        | 445   | ns   |  |

| t <sub>AVDV</sub>   | 28     | Address to valid data in                 | _                        | 9 t <sub>CLCL</sub> –50               | -        | 512.5 | ns   |  |

| t <sub>LLWL</sub>   | 28, 29 | ALE low to RD or WR low                  | 3 t <sub>CLCL</sub> -20  | 3 t <sub>CLCL</sub> +20               | 167.5    | 207.5 | ns   |  |

| t <sub>AVWL</sub>   | 28, 29 | Address valid to WR low or RD low        | 4 t <sub>CLCL</sub> -20  | -                                     | 230      | _     | ns   |  |

| t <sub>QVWX</sub>   | 29     | Data valid to WR transition              | t <sub>CLCL</sub> –30    | 1_                                    | 32.5     | _     | ns   |  |

| t <sub>WHQX</sub>   | 29     | Data hold after WR                       | t <sub>CLCL</sub> –20    | 1_                                    | 42.5     | _     | ns   |  |

| t <sub>QVWH</sub>   | 29     | Data valid to WR high                    | 7 t <sub>CLCL</sub> -10  | 1_                                    | 427.5    | _     | ns   |  |

| t <sub>RLAZ</sub>   | 28     | RD low to address float                  | -                        | 0                                     | _        | 0     | ns   |  |

| t <sub>WHLH</sub>   | 28, 29 | RD or WR high to ALE high                | t <sub>CLCL</sub> –15    | t <sub>CLCL</sub> +15                 | 47.5     | 77.5  | ns   |  |

| External (          |        |                                          | T-OLOL 19                | T-CLCL - 1-5                          | 1        | 1     | 1    |  |

| t <sub>CHCX</sub>   | 31     | High time                                | 0.32 t <sub>CLCL</sub>   | t <sub>CLCL</sub> - t <sub>CLCX</sub> | 1_       | 1_    | ns   |  |

| t <sub>CLCX</sub>   | 31     | Low time                                 | 0.32 t <sub>CLCL</sub>   | t <sub>CLCL</sub> - t <sub>CHCX</sub> | _        | _     | ns   |  |

| t <sub>CLCH</sub>   | 31     | Rise time                                | -                        | 5                                     | <u> </u> | _     | ns   |  |

| tCHCL               | 31     | Fall time                                | _                        | 5                                     | 1_       | _     | ns   |  |

| Shift regis         |        | 1. 4 4                                   |                          | 1 -                                   |          |       | 1    |  |

| t <sub>XLXL</sub>   | 30     | Serial port clock cycle time             | 12 t <sub>CLCL</sub>     | T_                                    | 750      | _     | ns   |  |

| t <sub>QVXH</sub>   | 30     | Output data setup to clock rising edge   | 10 t <sub>CLCL</sub> –25 | <del> </del>                          | 600      | _     | ns   |  |

| t <sub>XHQX</sub>   | 30     | Output data hold after clock rising edge | 2 t <sub>CLCL</sub> –15  | 1_                                    | 110      | _     | ns   |  |

| t <sub>XHDX</sub>   | 30     | Input data hold after clock rising edge  | 0                        |                                       | 0        | _     | ns   |  |

| *VUDY               | 30     | Clock rising edge to input data valid    |                          | 10 t <sub>CLCL</sub> -133             | _        | 492   | ns   |  |

- Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all outputs = 80 pF

- 3. Interfacing the microcontroller to devices with float time up to 45 ns is permitted. This limited bus contention will not cause damage to port 0

4. Parts are guaranteed by design to operate down to 0 Hz.

2003 Jan 24 41

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE, 5 V ±10% OPERATION)

$T_{amb}$  = 0 °C to +70 °C or -40 °C to +85 °C ;  $V_{CC}$  = 5 V ±10%,  $V_{SS}$  = 0 V<sup>1,2,3,4,5</sup>

| Symbol              | Figure | Parameter                                | Limits                    |                                       | 16 MHz ( | Clock  | Unit |

|---------------------|--------|------------------------------------------|---------------------------|---------------------------------------|----------|--------|------|

|                     |        |                                          | MIN                       | MAX                                   | MIN      | MAX    | 7    |

| 1/t <sub>CLCL</sub> | 31     | Oscillator frequency                     | 0                         | 30                                    | -        | -      | MHz  |

| t <sub>LHLL</sub>   | 27     | ALE pulse width                          | t <sub>CLCL</sub> -8      | _                                     | 54.5     | _      | ns   |

| t <sub>AVLL</sub>   | 27     | Address valid to ALE low                 | 0.5 t <sub>CLCL</sub> -13 | _                                     | 18.25    | _      | ns   |

| t <sub>LLAX</sub>   | 27     | Address hold after ALE low               | 0.5 t <sub>CLCL</sub> -20 | 1-                                    | 11.25    | _      | ns   |

| t <sub>LLIV</sub>   | 27     | ALE low to valid instruction in          | _                         | 2 t <sub>CLCL</sub> -35               | -        | 90     | ns   |

| t <sub>LLPL</sub>   | 27     | ALE low to PSEN low                      | 0.5 t <sub>CLCL</sub> -10 | -                                     | 21.25    | _      | ns   |

| t <sub>PLPH</sub>   | 27     | PSEN pulse width                         | 1.5 t <sub>CLCL</sub> -10 | -                                     | 83.75    | _      | ns   |

| t <sub>PLIV</sub>   | 27     | PSEN low to valid instruction in         | _                         | 1.5 t <sub>CLCL</sub> -35             | -        | 58.75  | ns   |

| t <sub>PXIX</sub>   | 27     | Input instruction hold after PSEN        | 0                         | _                                     | 0        | -      | ns   |

| t <sub>PXIZ</sub>   | 27     | Input instruction float after PSEN       | _                         | 0.5 t <sub>CLCL</sub> -10             | _        | 21.25  | ns   |

| t <sub>AVIV</sub>   | 27     | Address to valid instruction in          | _                         | 2.5 t <sub>CLCL</sub> -35             | -        | 121.25 | ns   |

| t <sub>PLAZ</sub>   | 27     | PSEN low to address float                | _                         | 10                                    | <b> </b> | 10     | ns   |

| Data Men            | nory   |                                          | l .                       |                                       |          |        |      |

| t <sub>RLRH</sub>   | 28     | RD pulse width                           | 3 t <sub>CLCL</sub> -20   | _                                     | 167.5    | _      | ns   |

| t <sub>WLWH</sub>   | 29     | WR pulse width                           | 3 t <sub>CLCL</sub> -20   | _                                     | 167.5    | _      | ns   |

| t <sub>RLDV</sub>   | 28     | RD low to valid data in                  | _                         | - 2.5 t <sub>CLCL</sub> -35           |          | 121.25 | ns   |

| t <sub>RHDX</sub>   | 28     | Data hold after RD                       | 0                         | _                                     | 0        | _      | ns   |

| t <sub>RHDZ</sub>   | 28     | Data float after RD                      | _                         | t <sub>CLCL</sub> -10                 | -        | 52.5   | ns   |

| t <sub>LLDV</sub>   | 28     | ALE low to valid data in                 | _                         | 4 t <sub>CLCL</sub> -35               | _        | 215    | ns   |

| t <sub>AVDV</sub>   | 28     | Address to valid data in                 | _                         | 4.5 t <sub>CLCL</sub> -35             | _        | 246.25 | ns   |

| t <sub>LLWL</sub>   | 28, 29 | ALE low to RD or WR low                  | 1.5 t <sub>CLCL</sub> -15 | 1.5 t <sub>CLCL</sub> +15             | 78.75    | 108.75 | ns   |

| t <sub>AVWL</sub>   | 28, 29 | Address valid to WR low or RD low        | 2 t <sub>CLCL</sub> -15   | _                                     | 110      | _      | ns   |

| t <sub>QVWX</sub>   | 29     | Data valid to WR transition              | 0.5 t <sub>CLCL</sub> -25 | -                                     | 6.25     | _      | ns   |

| t <sub>WHQX</sub>   | 29     | Data hold after WR                       | 0.5 t <sub>CLCL</sub> -15 | -                                     | 16.25    | _      | ns   |

| t <sub>QVWH</sub>   | 29     | Data valid to WR high                    | 3.5 t <sub>CLCL</sub> -5  | 1-                                    | 213.75   | _      | ns   |

| t <sub>RLAZ</sub>   | 28     | RD low to address float                  | _                         | 0                                     | _        | 0      | ns   |

| twhLH               | 28, 29 | RD or WR high to ALE high                | 0.5 t <sub>CLCL</sub> -10 | 0.5 t <sub>CLCL</sub> +10             | 21.25    | 41.25  | ns   |

| External (          | Clock  |                                          |                           |                                       |          |        |      |

| t <sub>CHCX</sub>   | 31     | High time                                | 0.4 t <sub>CLCL</sub>     | t <sub>CLCL</sub> - t <sub>CLCX</sub> | _        | _      | ns   |

| t <sub>CLCX</sub>   | 31     | Low time                                 | 0.4 t <sub>CLCL</sub>     | t <sub>CLCL</sub> - t <sub>CHCX</sub> | _        | _      | ns   |

| t <sub>CLCH</sub>   | 31     | Rise time                                | -                         | 5                                     | _        | _      | ns   |

| tCHCL               | 31     | Fall time                                | _                         | 5                                     | _        | -      | ns   |

| Shift regi          | ster   |                                          |                           |                                       |          |        |      |

| t <sub>XLXL</sub>   | 30     | Serial port clock cycle time             | 6 t <sub>CLCL</sub>       | _                                     | 375      | _      | ns   |

| t <sub>QVXH</sub>   | 30     | Output data setup to clock rising edge   | 5 t <sub>CLCL</sub> –25   | _                                     | 287.5    | _      | ns   |

| t <sub>XHQX</sub>   | 30     | Output data hold after clock rising edge | t <sub>CLCL</sub> -15     | _                                     | 47.5     | _      | ns   |

| t <sub>XHDX</sub>   | 30     | Input data hold after clock rising edge  | 0                         | _                                     | 0        | -      | ns   |

| t <sub>XHDV</sub>   | 30     | Clock rising edge to input data valid    | _                         | 5 t <sub>CLCL</sub> -133              | _        | 179.5  | ns   |

### NOTES:

- 1. Parameters are valid over operating temperature range unless otherwise specified.

- 2. Load capacitance for port 0, ALE, and PSEN=100 pF, load capacitance for all outputs = 80 pF

- 3. Interfacing the microcontroller to devices with float time up to 45ns is permitted. This limited bus contention will not cause damage to port 0 drivers.

- 4. Parts are guaranteed by design to operate down to 0 Hz.

- 5. Data shown in the table are the best mathematical models for the set of measured values obtained in tests. If a particular parameter calculated at a customer specified frequency has a negative value, it should be considered equal to zero.

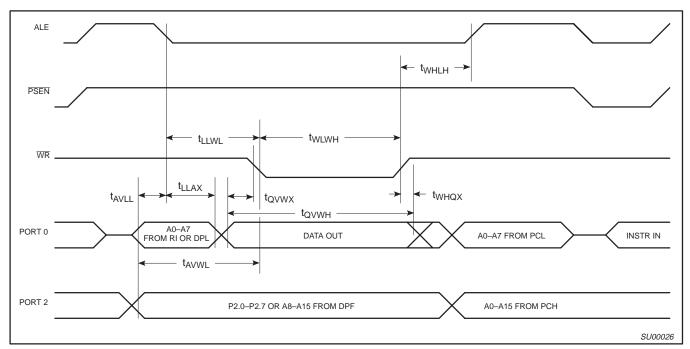

Figure 29. External Data Memory Write Cycle

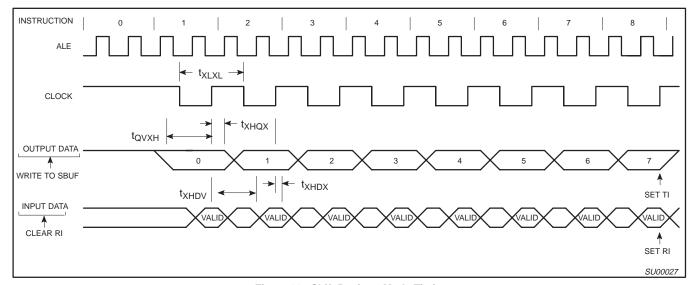

Figure 30. Shift Register Mode Timing

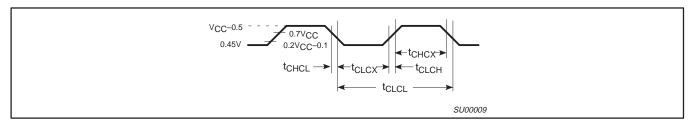

Figure 31. External Clock Drive

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

### **EPROM CHARACTERISTICS**

The OTP devices described in this data sheet can be programmed by using a modified Improved Quick-Pulse Programming  $^{\rm TM}$  algorithm. It differs from older methods in the value used for  $V_{\mbox{\footnotesize{PP}}}$  (programming supply voltage) and in the width and number of the ALE/ $\mbox{\footnotesize{PROG}}$  pulses.

The family contains two signature bytes that can be read and used by an EPROM programming system to identify the device. The signature bytes identify the device as being manufactured by Philips.

Table 9 shows the logic levels for reading the signature byte, and for programming the program memory, the encryption table, and the security bits. The circuit configuration and waveforms for quick-pulse programming are shown in Figures 40 and 41. Figure 42 shows the circuit configuration for normal program memory verification.

# **Quick-Pulse Programming**

The setup for microcontroller quick-pulse programming is shown in Figure 40. Note that the device is running with a 4 to 6 MHz oscillator. The reason the oscillator needs to be running is that the device is executing internal address and program data transfers.

The address of the EPROM location to be programmed is applied to ports 1 and 2, as shown in Figure 40. The code byte to be programmed into that location is applied to port 0. RST, PSEN and pins of ports 2 and 3 specified in Table 9 are held at the 'Program Code Data' levels indicated in Table 9. The ALE/PROG is pulsed low 5 times as shown in Figure 41.

To program the encryption table, repeat the 5 pulse programming sequence for addresses 0 through 1FH, using the 'Pgm Encryption Table' levels. Do not forget that after the encryption table is programmed, verification cycles will produce only encrypted data.

To program the security bits, repeat the 5 pulse programming sequence using the 'Pgm Security Bit' levels. After one security bit is programmed, further programming of the code memory and encryption table is disabled. However, the other security bits can still be programmed.

Note that the  $\overline{EA}/V_{PP}$  pin must not be allowed to go above the maximum specified  $V_{PP}$  level for any amount of time. Even a narrow glitch above that voltage can cause permanent damage to the

device. The  $\ensuremath{\text{V}_{\text{PP}}}$  source should be well regulated and free of glitches and overshoot.

# **Program Verification**

If security bits 2 and 3 have not been programmed, the on-chip program memory can be read out for program verification. The address of the program memory locations to be read is applied to ports 1 and 2 as shown in Figure 42. The other pins are held at the 'Verify Code Data' levels indicated in Table 9. The contents of the address location will be emitted on port 0. External pull-ups are required on port 0 for this operation.

If the 64 byte encryption table has been programmed, the data presented at port 0 will be the exclusive NOR of the program byte with one of the encryption bytes. The user will have to know the encryption table contents in order to correctly decode the verification data. The encryption table itself cannot be read out.

### Reading the Signature bytes

The signature bytes are read by the same procedure as a normal verification of locations 030h and 031h, except that P3.6 and P3.7 need to be pulled to a logic low. The values are:

(030h) = 15h; indicates manufacturer (Philips)

(031h) = 92h/97h/BBh/BDh; indicates P87C51X2/52X2/54X2/ 58X2.

# **Program/Verify Algorithms**

Any algorithm in agreement with the conditions listed in Table 9, and which satisfies the timing specifications, is suitable.

# **Security Bits**

With none of the security bits programmed the code in the program memory can be verified. If the encryption table is programmed, the code will be encrypted when verified. When only security bit 1 (see Table 10) is programmed, MOVC instructions executed from external program memory are disabled from fetching code bytes from the internal memory,  $\overline{EA}$  is latched on Reset and all further programming of the EPROM is disabled. When security bits 1 and 2 are programmed, in addition to the above, verify mode is disabled. When all three security bits are programmed, all of the conditions above apply and all external program memory execution is disabled.

## **Encryption Array**

64 bytes of encryption array are initially unprogrammed (all 1s).

<sup>™</sup>Trademark phrase of Intel Corporation.

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

# 80C54X2 ROM CODE SUBMISSION

When submitting a ROM code for the 80C54X2, the following must be specified:

- 1. 16 kbyte user ROM data

- 2. 64 byte ROM encryption key

- 3. ROM security bits.

| ADDRESS        | CONTENT | BIT(S) | COMMENT                                                           |

|----------------|---------|--------|-------------------------------------------------------------------|

| 0000H to 3FFFH | DATA    | 7:0    | User ROM Data                                                     |

| 4000H to 403FH | KEY     | 7:0    | ROM Encryption Key<br>FFH = no encryption                         |

| 4040H          | SEC     | 0      | ROM Security Bit 1<br>0 = enable security<br>1 = disable security |

| 4040H          | SEC     | 1      | ROM Security Bit 2<br>0 = enable security<br>1 = disable security |

Security Bit 1: When programmed, this bit has two effects on masked ROM parts:

- 1. External MOVC is disabled, and

- 2. EA is latched on Reset.

Security Bit 2: When programmed, this bit inhibits Verify User ROM.

NOTE: Security Bit 2 cannot be enabled unless Security Bit 1 is enabled.

If the ROM Code file does not include the options, the following information must be included with the ROM code.

For each of the following, check the appropriate box, and send to Philips along with the code:

| Security Bit #1: | ☐ Enabled | ☐ Disabled                        |

|------------------|-----------|-----------------------------------|

| Security Bit #2: | ☐ Enabled | ☐ Disabled                        |

| Encryption:      | □ No      | ☐ Yes If Yes, must send key file. |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

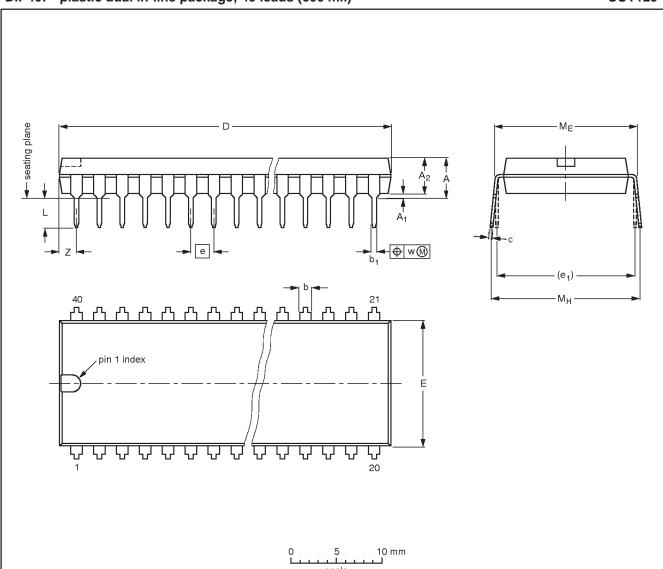

# DIP40: plastic dual in-line package; 40 leads (600 mil)

SOT129-1

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | Мн             | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|-------|--------------------------|

| mm     | 4.7       | 0.51                   | 4                      | 1.70<br>1.14   | 0.53<br>0.38   | 0.36<br>0.23   | 52.5<br>51.5     | 14.1<br>13.7     | 2.54 | 15.24          | 3.60<br>3.05 | 15.80<br>15.24 | 17.42<br>15.90 | 0.254 | 2.25                     |

| inches | 0.19      | 0.02                   | 0.16                   | 0.067<br>0.045 | 0.021<br>0.015 | 0.014<br>0.009 | 2.067<br>2.028   | 0.56<br>0.54     | 0.1  | 0.6            | 0.14<br>0.12 | 0.62<br>0.60   | 0.69<br>0.63   | 0.01  | 0.089                    |

### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE<br>VERSION |        | REFEF  | EUROPEAN  | ISSUE DATE |            |                                 |

|--------------------|--------|--------|-----------|------------|------------|---------------------------------|

|                    | IEC    | JEDEC  | JEITA     |            | PROJECTION | ISSUE DATE                      |

| SOT129-1           | 051G08 | MO-015 | SC-511-40 |            |            | <del>99-12-27</del><br>03-02-13 |

80C51 8-bit microcontroller family 4K/8K/16K/32K ROM/OTP, low voltage (2.7 to 5.5 V), low power, high speed (30/33 MHz)

P80C3xX2; P80C5xX2; P87C5xX2

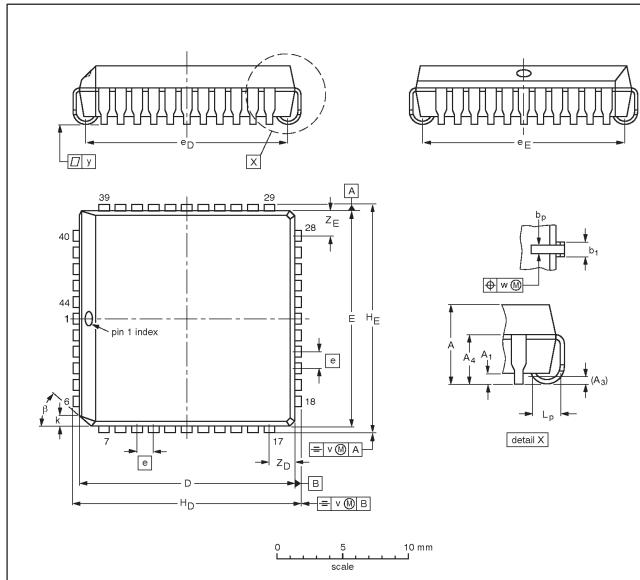

# PLCC44: plastic leaded chip carrier; 44 leads

SOT187-2

# DIMENSIONS (mm dimensions are derived from the original inch dimensions)

| UNIT   | А              | A <sub>1</sub><br>min. | A <sub>3</sub> | A <sub>4</sub><br>max. | bр             | b <sub>1</sub> | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | еD             | еE | н <sub>D</sub> | HE             | k | Lp           | v     | w     | у     |       | Z <sub>E</sub> <sup>(1)</sup><br>max. | β   |

|--------|----------------|------------------------|----------------|------------------------|----------------|----------------|------------------|------------------|------|----------------|----|----------------|----------------|---|--------------|-------|-------|-------|-------|---------------------------------------|-----|

| mm     | 4.57<br>4.19   | 0.51                   | 0.25           | 3.05                   | 0.53<br>0.33   | 0.81<br>0.66   |                  | 16.66<br>16.51   | 1.27 | 16.00<br>14.99 |    |                |                |   | 1.44<br>1.02 | 0.18  | 0.18  | 0.1   | 2.16  | 2.16                                  | 45° |

| inches | 0.180<br>0.165 | 0.02                   | 0.01           |                        | 0.021<br>0.013 |                |                  |                  |      | 0.63<br>0.59   |    |                | 0.695<br>0.685 |   |              | 0.007 | 0.007 | 0.004 | 0.085 |                                       |     |

### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE<br>VERSION |        | REFER  | EUROPEAN | ISSUE DATE |            |                                   |

|--------------------|--------|--------|----------|------------|------------|-----------------------------------|

|                    | IEC    | JEDEC  | JEITA    |            | PROJECTION | ISSUE DATE                        |

| SOT187-2           | 112E10 | MS-018 | EDR-7319 |            |            | <del>-99-12-27-</del><br>01-11-14 |