Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | F <sup>2</sup> MC-16FX                                                          |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 56MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SCI, UART/USART                      |

| Peripherals                | DMA, LVD, LVR, POR, PWM, WDT                                                    |

| Number of I/O              | 51                                                                              |

| Program Memory Size        | 160KB (160K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                       |

| Data Converters            | A/D 15x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb96f355asbpmc1-gse2 |

### **■ PIN FUNCTION DESCRIPTION**

## Pin Function description (1 of 2)

| Pin name | Feature               | Description                                                                    |

|----------|-----------------------|--------------------------------------------------------------------------------|

| ADn      | External bus          | External bus interface (multiplexed mode) address output and data input/output |

| ADTG_R   | ADC                   | Relocated A/D converter trigger input                                          |

| ALE      | External bus          | External bus Address Latch Enable output                                       |

| An       | External bus          | External bus address output                                                    |

| ANn      | ADC                   | A/D converter channel n input                                                  |

| AVcc     | Supply                | Analog circuits power supply                                                   |

| AVRH     | ADC                   | A/D converter high reference voltage input                                     |

| AVss     | Supply                | Analog circuits power supply                                                   |

| С        | Voltage regulator     | Internally regulated power supply stabilization capacitor pin                  |

| CKOTn    | Clock output function | Clock Output function n output                                                 |

| CKOTn_R  | Clock output function | Relocated Clock Output function n output                                       |

| CKOTXn   | Clock output function | Clock Output function n inverted output                                        |

| ECLK     | External bus          | External bus clock output                                                      |

| CSn_R    | External bus          | Relocated External bus chip select n output                                    |

| FRCKn    | Free Running Timer    | Free Running Timer n input                                                     |

| HAKX     | External bus          | External bus Hold Acknowledge                                                  |

| HRQ      | External bus          | External bus Hold Request                                                      |

| INn      | ICU                   | Input Capture Unit n input                                                     |

| INTn     | External Interrupt    | External Interrupt n input                                                     |

| INTn_R   | External Interrupt    | Relocated External Interrupt n input                                           |

| MDn      | Core                  | Input pins for specifying the operating mode.                                  |

| NMI_R    | External Interrupt    | Relocated Non-Maskable Interrupt input                                         |

| OUTn     | OCU                   | Output Compare Unit n waveform output                                          |

| Pxx_n    | GPIO                  | General purpose IO                                                             |

| PPGn     | PPG                   | Programmable Pulse Generator n output                                          |

| PPGn_R   | PPG                   | Relocated Programmable Pulse Generator n output                                |

| RDX      | External bus          | External bus interface read strobe output                                      |

| RDY      | External bus          | External bus interface external wait state request input                       |

|          |                       | !                                                                              |

## Pin Function description (2 of 2)

| Pin name | Feature      | Description                                                   |

|----------|--------------|---------------------------------------------------------------|

| RSTX     | Core         | Reset input                                                   |

| RXn      | CAN          | CAN interface n RX input                                      |

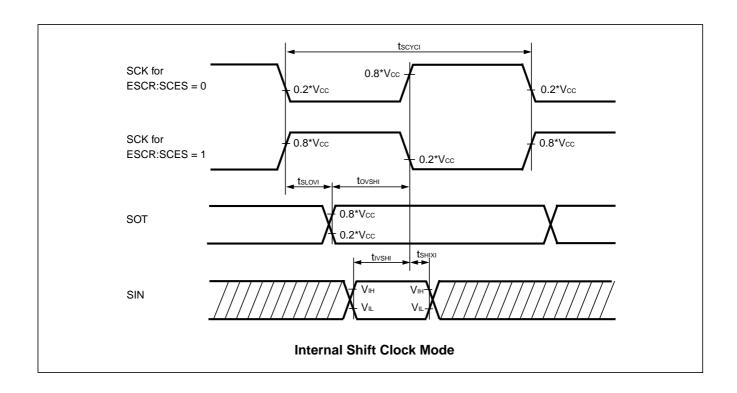

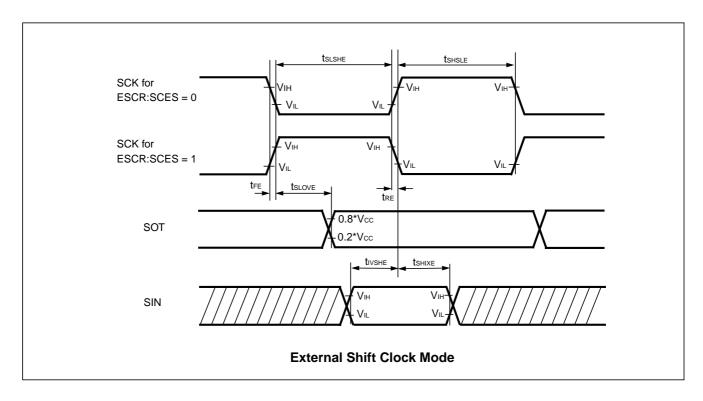

| SCKn     | USART        | USART n serial clock input/output                             |

| SCKn_R   | USART        | Relocated USART n serial clock input/output                   |

| SCLn     | I2C          | I2C interface n clock I/O input/output                        |

| SDAn     | I2C          | I2C interface n serial data I/O input/output                  |

| SINn     | USART        | USART n serial data input                                     |

| SINn_R   | USART        | Relocated USART n serial data input                           |

| SOTn     | USART        | USART n serial data output                                    |

| SOTn_R   | USART        | Relocated USART n serial data output                          |

| TINn     | Reload Timer | Reload Timer n event input                                    |

| TINn_R   | Reload Timer | Relocated Reload Timer n event input                          |

| TOTn     | Reload Timer | Reload Timer n output                                         |

| TOTn_R   | Reload Timer | Relocated Reload Timer n output                               |

| TTGn     | PPG          | Programmable Pulse Generator n trigger input                  |

| TTGn_R   | PPG          | Relocated Programmable Pulse Generator n trigger input        |

| TXn      | CAN          | CAN interface n TX output                                     |

| Vcc      | Supply       | Power supply                                                  |

| Vss      | Supply       | Power supply                                                  |

| WOT      | RTC          | Real Timer clock output                                       |

| WRHX     | External bus | External bus High byte write strobe output                    |

| WRLX/WRX | External bus | External bus Low byte / Word write strobe output              |

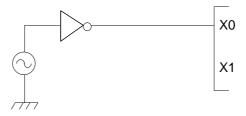

| X0       | Clock        | Oscillator input                                              |

| X0A      | Clock        | Subclock Oscillator input (only for devices with suffix "W")  |

| X1       | Clock        | Oscillator output                                             |

| X1A      | Clock        | Subclock Oscillator output (only for devices with suffix "W") |

## ■ USER ROM MEMORY MAP FOR FLASH DEVICES

|                                              |                           | MB96F353              | MB96F355               | MB96F356                                          |       |

|----------------------------------------------|---------------------------|-----------------------|------------------------|---------------------------------------------------|-------|

| Alternative mode<br>CPU address              | Flash memory mode address | Flash size<br>96kByte | Flash size<br>160kByte | Flash size<br>288kByte                            |       |

| FF:FFFFH                                     | 3F:FFFFн                  | S39 - 64K             | S39 - 64K              | S39 - 64K                                         |       |

| FF:0000 <sub>H</sub>                         | 3F:0000н                  | 000 0111              |                        |                                                   |       |

| FE:FFFFH                                     | 3E:FFFF#                  |                       | S38 - 64K              | S38 - 64K                                         |       |

| FE:0000H                                     | 3Е:0000н                  | _                     |                        |                                                   | Flash |

| FD:FFFF <sub>H</sub>                         | 3D:FFFF <sub>H</sub>      | 1                     |                        | S37 - 64K                                         |       |

| FD:0000H<br>FC:FFFFH                         | 3D:0000н<br>3C:FFFFн      | → ⊢                   | _                      |                                                   |       |

| FC:0000H                                     | 3C:0000н                  | 1                     |                        | S36 - 64K                                         |       |

| FB:FFFFH                                     | 3B:FFFF <sub>H</sub>      |                       | _                      |                                                   |       |

| FB:0000н                                     | 3B:0000н                  |                       |                        |                                                   |       |

| FA:FFFFH                                     | 3A:FFFF <sub>H</sub>      |                       | _                      |                                                   |       |

| FA:0000 <sub>H</sub>                         | 3А:0000н                  | 1                     |                        |                                                   |       |

| F9:FFFFH                                     | 39:FFFFн                  | <b>⊣</b> ⊢            | -                      | <del>                                      </del> |       |

| F9:0000н                                     | 39:0000н                  |                       |                        |                                                   |       |

| F8:FFFFH                                     | 38:FFFF <sub>H</sub>      | - <del> </del>        | -                      | <del>   </del>                                    |       |

| F8:0000 <sub>H</sub>                         | 38:0000 <sub>H</sub>      |                       |                        |                                                   |       |

| F7:FFFFH                                     | 37:FFFFH                  | <b>-</b>              |                        | <del>   </del>                                    |       |

| F7:0000н                                     | 37:0000н                  | 1                     |                        |                                                   |       |

| F6:FFFF                                      | 36:FFFF <sub>H</sub>      | External bus          |                        |                                                   |       |

| F6:0000 <sub>H</sub>                         | 36:0000н                  | External bus          | External bus           |                                                   |       |

| F5:FFFF                                      | 35:FFFFн                  | <b>-i</b>             | - External bus         | <del>   </del>                                    |       |

| F5:0000н                                     | 35:0000н                  |                       |                        | External bus                                      |       |

| F4:FFFF <sub>H</sub>                         | 34:FFFFн                  | _i                    |                        | External bus                                      |       |

| F4:0000 <sub>H</sub>                         | 34:0000н                  |                       |                        |                                                   |       |

| F3:FFFF <sub>H</sub>                         | 33:FFFFн                  | -i                    |                        |                                                   |       |

| F3:0000 <sub>H</sub>                         | 33:0000н                  |                       |                        |                                                   |       |

| F2:FFFF <sub>H</sub>                         | 32:FFFF <sub>H</sub>      |                       |                        |                                                   |       |

| F2:0000 <sub>H</sub>                         | 32:0000н                  |                       |                        |                                                   |       |

| F1:FFFF <sub>H</sub>                         | 31:FFFFн                  |                       |                        |                                                   |       |

| F1:0000н                                     | 31:0000н                  |                       |                        |                                                   |       |

| F0:FFFF <sub>H</sub>                         | 30:FFFFн                  |                       |                        |                                                   |       |

| F0:0000 <sub>H</sub>                         | 30:0000н                  |                       | _                      | <u> </u>                                          |       |

| E0:0000н                                     |                           |                       |                        |                                                   |       |

| DF:FFFF <sub>H</sub>                         |                           | Reserved              | Reserved               | Reserved                                          |       |

| DF:8000 <sub>H</sub>                         |                           |                       |                        |                                                   |       |

| DF:7FFFH                                     | 1F:7FFF <sub>H</sub>      | SA3 - 8K              | SA3 - 8K               | SA3 - 8K                                          |       |

| DF:6000H                                     | 1F:6000H                  |                       |                        |                                                   |       |

| DF:5FFFH                                     | 1F:5FFF <sub>H</sub>      | SA2 - 8K              | SA2 - 8K               | SA2 - 8K                                          |       |

| DF:4000 <sub>H</sub><br>DF:3FFF <sub>H</sub> | 1F:4000н<br>1F:3FFFн      | 1                     |                        |                                                   | Flash |

| DF:3FFFн<br>DF:2000н                         | 1F:3FFFн<br>1F:2000н      | SA1 - 8K              | SA1 - 8K               | SA1 - 8K                                          |       |

| DF:2000H<br>DF:1FFFH                         | 1F:2000н<br>1F:1FFFн      | 0.4.0.014.*           | 0.4.0. 014.*4          | 1 1 010 014                                       |       |

| DF:1FFFн<br>DF:0000н                         | 1F:0000н                  | SA0 - 8K *1           | SA0 - 8K *1            | SA0 - 8K *1                                       |       |

| DE:FFFFH                                     | IF.UUUUH                  |                       |                        | <b>₹ ├</b>                                        |       |

| DE:0000н                                     |                           | Reserved              | Reserved               | Reserved                                          |       |

| DF:0000□                                     |                           |                       |                        |                                                   |       |

## I/O map MB96(F)35x (19 of 28)

| Address | Register                                      | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------|-----------------------------------------------|------------------------------|-------------------------------|--------|

| 00058Fн | PPG10 - Control status register High          | PCNH10                       |                               | R/W    |

| 000590н | PPG11 - Timer register                        |                              | PTMR11                        | R      |

| 000591н | PPG11 - Timer register                        |                              |                               | R      |

| 000592н | PPG11 - Period setting register               |                              | PCSR11                        | W      |

| 000593н | PPG11 - Period setting register               |                              |                               | W      |

| 000594н | PPG11 - Duty cycle register                   |                              | PDUT11                        | W      |

| 000595н | PPG11 - Duty cycle register                   |                              |                               | W      |

| 000596н | PPG11 - Control status register Low           | PCNL11                       | PCN11                         | R/W    |

| 000597н | PPG11 - Control status register High          | PCNH11                       |                               | R/W    |

| 000598н | PPG15-PPG12 - General Control register 1 Low  | GCN1L3                       | GCN13                         | R/W    |

| 000599н | PPG15-PPG12 - General Control register 1 High | GCN1H3                       |                               | R/W    |

| 00059Ан | PPG15-PPG12 - General Control register 2 Low  | GCN2L3                       | GCN23                         | R/W    |

| 00059Вн | PPG15-PPG12 - General Control register 2 High | GCN2H3                       |                               | R/W    |

| 00059Сн | PPG12 - Timer register                        |                              | PTMR12                        | R      |

| 00059Dн | PPG12 - Timer register                        |                              |                               | R      |

| 00059Ен | PPG12 - Period setting register               |                              | PCSR12                        | W      |

| 00059Fн | PPG12 - Period setting register               |                              |                               | W      |

| 0005А0н | PPG12 - Duty cycle register                   |                              | PDUT12                        | W      |

| 0005А1н | PPG12 - Duty cycle register                   |                              |                               | W      |

| 0005А2н | PPG12 - Control status register Low           | PCNL12                       | PCN12                         | R/W    |

| 0005АЗн | PPG12 - Control status register High          | PCNH12                       |                               | R/W    |

| 0005А4н | PPG13 - Timer register                        |                              | PTMR13                        | R      |

| 0005А5н | PPG13 - Timer register                        |                              |                               | R      |

| 0005А6н | PPG13 - Period setting register               |                              | PCSR13                        | W      |

| 0005А7н | PPG13 - Period setting register               |                              |                               | W      |

| 0005А8н | PPG13 - Duty cycle register                   |                              | PDUT13                        | W      |

| 0005А9н | PPG13 - Duty cycle register                   |                              |                               | W      |

| 0005ААн | PPG13 - Control status register Low           | PCNL13                       | PCN13                         | R/W    |

| 0005АВн | PPG13 - Control status register High          | PCNH13                       |                               | R/W    |

| 0005АСн | PPG14 - Timer register                        |                              | PTMR14                        | R      |

### I/O map MB96(F)35x (22 of 28)

| Address             | Register                                          | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------------------|---------------------------------------------------|------------------------------|-------------------------------|--------|

| 0006Е2н             | External Bus - Area configuration register 1 Low  | EACL1                        | EAC1                          | R/W    |

| 0006ЕЗн             | External Bus - Area configuration register 1 High | EACH1                        |                               | R/W    |

| 0006Е4н             | External Bus - Area configuration register 2 Low  | EACL2                        | EAC2                          | R/W    |

| 0006Е5н             | External Bus - Area configuration register 2 High | EACH2                        |                               | R/W    |

| 0006Е6н             | External Bus - Area configuration register 3 Low  | EACL3                        | EAC3                          | R/W    |

| 0006Е7н             | External Bus - Area configuration register 3 High | EACH3                        |                               | R/W    |

| 0006Е8н             | External Bus - Area configuration register 4 Low  | EACL4                        | EAC4                          | R/W    |

| 0006Е9н             | External Bus - Area configuration register 4 High | EACH4                        |                               | R/W    |

| 0006ЕАн             | External Bus - Area configuration register 5 Low  | EACL5                        | EAC5                          | R/W    |

| 0006ЕВн             | External Bus - Area configuration register 5 High | EACH5                        |                               | R/W    |

| 0006ЕСн             | External Bus - Area select register 2             | EAS2                         |                               | R/W    |

| 0006ЕДн             | External Bus - Area select register 3             | EAS3                         |                               | R/W    |

| 0006ЕЕн             | External Bus - Area select register 4             | EAS4                         |                               | R/W    |

| 0006ЕГн             | External Bus - Area select register 5             | EAS5                         |                               | R/W    |

| 0006F0н             | External Bus - Mode register                      | EBM                          |                               | R/W    |

| 0006F1н             | External Bus - Clock and Function register        | EBCF                         |                               | R/W    |

| 0006F2н             | External Bus - Address output enable register 0   | EBAE0                        |                               | R/W    |

| 0006F3н             | External Bus - Address output enable register 1   | EBAE1                        |                               | R/W    |

| 0006F4н             | External Bus - Address output enable register 2   | EBAE2                        |                               | R/W    |

| 0006F5н             | External Bus - Control signal register            | EBCS                         |                               | R/W    |

| 0006F6н-<br>0007FFн | Reserved                                          |                              |                               | -      |

| 000800н             | CAN1 - Control register Low                       | CTRLRL1                      | CTRLR1                        | R/W    |

| 000801н             | CAN1 - Control register High (reserved)           | CTRLRH1                      |                               | R      |

| 000802н             | CAN1 - Status register Low                        | STATRL1                      | STATR1                        | R/W    |

| 000803н             | CAN1 - Status register High (reserved)            | STATRH1                      |                               | R      |

| 000804н             | CAN1 - Error Counter Low (Transmit)               | ERRCNTL1                     | ERRCNT1                       | R      |

| 000805н             | CAN1 - Error Counter High (Receive)               | ERRCNTH1                     |                               | R      |

| 000806н             | CAN1 - Bit Timing Register Low                    | BTRL1                        | BTR1                          | R/W    |

| 000807н             | CAN1 - Bit Timing Register High                   | BTRH1                        |                               | R/W    |

## I/O map MB96(F)35x (27 of 28)

| Address             | Register                                         | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------------------|--------------------------------------------------|------------------------------|-------------------------------|--------|

| 000926н-<br>00093Fн | Reserved                                         |                              |                               | -      |

| 000940н             | CAN2 - IF2 Command request register Low          | IF2CREQL2                    | IF2CREQ2                      | R/W    |

| 000941н             | CAN2 - IF2 Command request register High         | IF2CREQH2                    |                               | R/W    |

| 000942н             | CAN2 - IF2 Command Mask register Low             | IF2CMSKL2                    | IF2CMSK2                      | R/W    |

| 000943н             | CAN2 - IF2 Command Mask register High (reserved) | IF2CMSKH2                    |                               | R      |

| 000944н             | CAN2 - IF2 Mask 1 Register Low                   | IF2MSK1L2                    | IF2MSK12                      | R/W    |

| 000945н             | CAN2 - IF2 Mask 1 Register High                  | IF2MSK1H2                    |                               | R/W    |

| 000946н             | CAN2 - IF2 Mask 2 Register Low                   | IF2MSK2L2                    | IF2MSK22                      | R/W    |

| 000947н             | CAN2 - IF2 Mask 2 Register High                  | IF2MSK2H2                    |                               | R/W    |

| 000948н             | CAN2 - IF2 Arbitration 1 Register Low            | IF2ARB1L2                    | IF2ARB12                      | R/W    |

| 000949н             | CAN2 - IF2 Arbitration 1 Register High           | IF2ARB1H2                    |                               | R/W    |

| 00094Ан             | CAN2 - IF2 Arbitration 2 Register Low            | IF2ARB2L2                    | IF2ARB22                      | R/W    |

| 00094Вн             | CAN2 - IF2 Arbitration 2 Register High           | IF2ARB2H2                    |                               | R/W    |

| 00094Сн             | CAN2 - IF2 Message Control Register Low          | IF2MCTRL2                    | IF2MCTR2                      | R/W    |

| 00094Dн             | CAN2 - IF2 Message Control Register High         | IF2MCTRH2                    |                               | R/W    |

| 00094Ен             | CAN2 - IF2 Data A1 Low                           | IF2DTA1L2                    | IF2DTA12                      | R/W    |

| 00094Fн             | CAN2 - IF2 Data A1 High                          | IF2DTA1H2                    |                               | R/W    |

| 000950н             | CAN2 - IF2 Data A2 Low                           | IF2DTA2L2                    | IF2DTA22                      | R/W    |

| 000951н             | CAN2 - IF2 Data A2 High                          | IF2DTA2H2                    |                               | R/W    |

| 000952н             | CAN2 - IF2 Data B1 Low                           | IF2DTB1L2                    | IF2DTB12                      | R/W    |

| 000953н             | CAN2 - IF2 Data B1 High                          | IF2DTB1H2                    |                               | R/W    |

| 000954н             | CAN2 - IF2 Data B2 Low                           | IF2DTB2L2                    | IF2DTB22                      | R/W    |

| 000955н             | CAN2 - IF2 Data B2 High                          | IF2DTB2H2                    |                               | R/W    |

| 000956н-<br>00097Fн | Reserved                                         |                              |                               | -      |

| 000980н             | CAN2 - Transmission Request 1 Register Low       | TREQR1L2                     | TREQR12                       | R      |

| 000981н             | CAN2 - Transmission Request 1 Register High      | TREQR1H2                     |                               | R      |

| 000982н             | CAN2 - Transmission Request 2 Register Low       | TREQR2L2                     | TREQR22                       | R      |

| 000983н             | CAN2 - Transmission Request 2 Register High      | TREQR2H2                     |                               | R      |

### I/O map MB96(F)35x (28 of 28)

| Address             | Register                                 | Abbreviation<br>8-bit access | Abbreviation<br>16-bit access | Access |

|---------------------|------------------------------------------|------------------------------|-------------------------------|--------|

| 000984н-<br>00098Fн | Reserved                                 |                              |                               | -      |

| 000990н             | CAN2 - New Data 1 Register Low           | NEWDT1L2                     | NEWDT12                       | R      |

| 000991н             | CAN2 - New Data 1 Register High          | NEWDT1H2                     |                               | R      |

| 000992н             | CAN2 - New Data 2 Register Low           | NEWDT2L2                     | NEWDT22                       | R      |

| 000993н             | CAN2 - New Data 2 Register High          | NEWDT2H2                     |                               | R      |

| 000994н-<br>00099Fн | Reserved                                 |                              |                               | -      |

| 0009А0н             | CAN2 - Interrupt Pending 1 Register Low  | INTPND1L2                    | INTPND12                      | R      |

| 0009А1н             | CAN2 - Interrupt Pending 1 Register High | INTPND1H2                    |                               | R      |

| 0009А2н             | CAN2 - Interrupt Pending 2 Register Low  | INTPND2L2                    | INTPND22                      | R      |

| 0009АЗн             | CAN2 - Interrupt Pending 2 Register High | INTPND2H2                    |                               | R      |

| 0009А4н-<br>0009АFн | Reserved                                 |                              |                               | -      |

| 0009В0н             | CAN2 - Message Valid 1 Register Low      | MSGVAL1L2                    | MSGVAL12                      | R      |

| 0009В1н             | CAN2 - Message Valid 1 Register High     | MSGVAL1H2                    |                               | R      |

| 0009В2н             | CAN2 - Message Valid 2 Register Low      | MSGVAL2L2                    | MSGVAL22                      | R      |

| 0009ВЗн             | CAN2 - Message Valid 2 Register High     | MSGVAL2H2                    |                               | R      |

| 0009В4н-<br>0009СDн | Reserved                                 |                              |                               | -      |

| 0009СЕн             | CAN2 - Output enable register            | COER2                        |                               | R/W    |

| 0009CFн-<br>000BFFн | Reserved                                 |                              |                               | -      |

Note: Any write access to reserved addresses in the I/O map should not be performed. A read access to a reserved address results in reading 'X'.

Registers of resources which are described in this table, but which are not supported by the device, should also be handled as "Reserved".

### **■ HANDLING DEVICES**

### Special care is required for the following when handling the device:

- Latch-up prevention

- · Unused pins handling

- · External clock usage

- Unused sub clock signal

- Notes on PLL clock mode operation

- Power supply pins (Vcc/Vss)

- · Crystal oscillator circuit

- Turn on sequence of power supply to A/D converter and analog inputs

- Pin handling when not using the A/D converter

- Notes on energization

- Stabilization of power supply voltage

- · Serial communication

### 1. Latch-up prevention

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than Vcc or lower than Vss is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between Vcc pins and Vss pins.

Latch-up may increase the power supply current dramatically, causing thermal damages to the device.

### 2. Unused pins handling

Unused input pins can be left open when the input is disabled (corresponding bit of Port Input Enable register PIER = 0).

Leaving unused input pins open when the input is enabled may result in misbehavior and possible permanent damage of the device. They must therefore be pulled up or pulled down through resistors. To prevent latch-up, those resistors should be more than  $2 \text{ k}\Omega$ .

Unused bidirectional pins can be set either to the output state and be then left open, or to the input state with either input disabled or external pull-up/pull-down resistor as described above.

### 3. External clock usage

The permitted frequency range of an external clock depends on the oscillator type and configuration. See AC Characteristics for detailed modes and frequency limits. Single and opposite phase external clocks must be connected as follows:

### 1. Single phase external clock

• When using a single phase external clock, X0 (X0A) pin must be driven and X1 (X1A) pin left open.

$(T_A = -40$ °C to 125°C,  $V_{CC} = AV_{CC} = 3.0V$  to 5.5V,  $V_{SS} = AV_{SS} = 0V)$

| Barranatan                         | 0                                                                                      | O 1'' (-1 T )                                                                                  |        |      | Value |      | D                                       |

|------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|------|-------|------|-----------------------------------------|

| Parameter                          | Symbol                                                                                 | Condition (at T <sub>A</sub> )                                                                 | 1      | Тур  | Max   | Unit | Remarks                                 |

|                                    |                                                                                        | RC Sleep mode with CLKS1/2 = CLKP1/2 =                                                         | +25°C  | 0.08 | 0.2   | mA   | MB96F353/F355                           |

|                                    |                                                                                        | 100kHz,<br>SMCR:LPMSS = 0                                                                      | +125°C | 0.59 | 2.95  | 1117 | 100000000000000000000000000000000000000 |

|                                    |                                                                                        | (CLKMC, CLKPLL and CLKSC stopped. Voltage                                                      | +25°C  | 0.3  | 0.5   |      | MDOCESEC                                |

|                                    | Iccsrcl                                                                                | regulator in high power mode)                                                                  | +125°C | 0.8  | 3.3   | mA   | MB96F356                                |

| Power supply cur-                  | TOOSINGE                                                                               | RC Sleep mode with CLKS1/2 = CLKP1/2 =                                                         | +25°C  | 0.05 | 0.15  |      |                                         |

| rent in Sleep<br>modes*            |                                                                                        | 100kHz, SMCR:LPMSS = 1  (CLKMC, CLKPLL and CLKSC stopped. Voltage regulator in low power mode) |        | 0.56 | 2.9   | mA   | MB96F353/F355/<br>F356                  |

|                                    |                                                                                        | Sub Sleep mode with CLKS1/2 = CLKP1/2 =                                                        | +25°C  | 0.04 | 0.12  |      |                                         |

|                                    | Іссяѕив                                                                                | 32kHz<br>(CLKMC, CLKPLL and<br>CLKRC stopped)                                                  | +125°C | 0.54 | 2.9   | mA   | MB96F353/F355/<br>F356                  |

|                                    |                                                                                        | PLL Timer mode with                                                                            | +25°C  | 1.3  | 1.8   | mA   | MB96F353/F355                           |

|                                    | ICCTPLL                                                                                | CLKMC = 4MHz, CLKPLL<br>= 48MHz                                                                | +125°C | 1.9  | 4.8   | 1117 | 1010001 000/1 000                       |

|                                    | 10011 22                                                                               | (CLKRC and CLKSC stopped)                                                                      | +25°C  | 1.5  | 2     | mA   | MB96F356                                |

|                                    |                                                                                        | ,                                                                                              | +125°C | 2.1  | 5     |      |                                         |

|                                    |                                                                                        | Main Timer mode with CLKMC = 4MHz,                                                             | +25°C  | 0.11 | 0.2   | mA   | MB96F353/F355                           |

| Power supply cur-<br>rent in Timer |                                                                                        | SMCR:LPMSS = 0<br>(CLKPLL, CLKRC and                                                           | +125°C | 0.63 | 3     |      |                                         |

| modes*                             |                                                                                        | CLKSC stopped. Voltage regulator in high power                                                 | +25°C  | 0.35 | 0.5   | mA   | MB96F356                                |

|                                    | <b>I</b> CCTMAIN                                                                       | mode)                                                                                          | +125°C | 0.85 | 3.3   |      |                                         |

|                                    |                                                                                        | Main Timer mode with CLKMC = 4MHz,                                                             | +25°C  | 0.08 | 0.15  |      |                                         |

|                                    | SMCR:LPMSS = 1  (CLKPLL, CLKRC and CLKSC stopped. Voltage regulator in low power mode) |                                                                                                | +125°C | 0.6  | 2.9   | mA   | MB96F353/F355/<br>F356                  |

## **External Bus timing**

Note: The values given below are for an I/O driving strength IO<sub>drive</sub> = 5mA. If IO<sub>drive</sub> is 2mA, all the maximum output timing described in the different tables must then be increased by 10ns.

## **Basic Timing**

(T<sub>A</sub> = -40 °C to +125 °C, Vcc = 5.0 V  $\pm$  10%, Vss = 0.0 V, IO<sub>drive</sub> = 5mA, C<sub>L</sub> = 50pF)

| Parameter                 | Symbol         | Din                     | Pin Condition |          | lue      | Unit  | Remarks |

|---------------------------|----------------|-------------------------|---------------|----------|----------|-------|---------|

| Parameter                 | Symbol         | PIII                    | Condition     | Min      | Max      | Ullit | Nemarks |

|                           | <b>t</b> cyc   |                         |               | 25       | _        |       |         |

| ECLK                      | tchcl          | ECLK                    |               | tcyc/2-5 | tcyc/2+5 | ns    |         |

|                           | <b>t</b> clch  |                         |               | tcyc/2-5 | tcyc/2+5 |       |         |

|                           | <b>t</b> снсвн |                         |               | -20      | 20       |       |         |

| ECLK 	o                   | <b>t</b> CHCBL | CSn, UBX,               |               | -20      | 20       | nc    |         |

| UBX/ LBX / CSn time       | tсьсвн         | LBX, ECLK               | _             | -20      | 20       | ns    |         |

|                           | <b>t</b> clcbl |                         |               | -20      | 20       |       |         |

|                           | <b>t</b> chlh  | ALE ECIK                | ALE, ECLK —   | -10      | 10       | - ns  |         |

| ECLK 	o ALE time          | <b>t</b> CHLL  |                         |               | -10      | 10       |       |         |

| LOLK - ALL time           | <b>t</b> CLLH  | ALE, ECLK               |               | -10      | 10       | 115   |         |

|                           | tclll          |                         |               | -10      | 10       |       |         |

|                           | <b>t</b> CHAV  | A[23:16],               | A[23:16],     | -15      | 15       | ns    |         |

| ECLK → address valid time | tclav          | ECLK                    |               | -15      | 15       | 115   |         |

|                           | <b>t</b> CLADV | AD[15:0],               |               | -15      | 15       | ns    |         |

| tchadv                    |                | ECLK                    | _             | -15      | 15       | 1115  |         |

|                           | <b>t</b> chrwh |                         |               | -10      | 10       |       |         |

| ECLK 	o RDX /WRX time     | <b>t</b> CHRWL | RDX, WRX,<br>WRLX,WRHX, |               | -10      | 10       | ns    |         |

|                           | <b>t</b> clrwh | ECLK                    | ,VVKПA, —     | -10      | 10       |       |         |

|                           | tclrwl         |                         |               | -10      | 10       |       |         |

(TA = -40 °C to +125 °C, Vcc = 3.0 to 4.5V, Vss = 0.0 V, IOdrive = 5mA, CL = 50pF)

| Donomotor                                         | Sym-           | D:-            | Conditions                         | Va           | lue          | 11   | Remarks                |

|---------------------------------------------------|----------------|----------------|------------------------------------|--------------|--------------|------|------------------------|

| Parameter                                         | bol            | Pin            | Conditions                         | Min          | Max          | Unit |                        |

|                                                   | <b>t</b> avrl  | DDV 4[00:46]   | EACL:ACE=0                         | 3tcyc/2 - 20 | _            | ns   |                        |

| Valid address  ⇒ RDX ↓ time                       | LAVRL          | RDX, A[23:16]  | EACL:ACE=1                         | 5tcyc/2 - 20 | _            | 115  |                        |

| ⇒ KDX ↓ time                                      | tanun          | RDX, AD[15:0]  | EACL:ACE=0                         | tcyc - 20    | _            | ns   |                        |

|                                                   | <b>t</b> advrl | KDA, AD[15.0]  | EACL:ACE=1                         | 2tcyc - 20   | _            | 115  |                        |

|                                                   | tavdv          | A[23:16],      | EACL:ACE=0                         | _            | 3tcyc - 60   | ns   | w/o cycle              |

| Valid address<br>⇒ Valid data input               | LAVDV          | AD[15:0]       | EACL:ACE=1                         | _            | 4tcyc - 60   | 115  | extension              |

|                                                   | <b>t</b> advov | AD[15:0]       | EACL:ACE=0                         | _            | 5tcyc/2 - 60 | - ns | w/o cycle<br>extension |

|                                                   | <b>t</b> ADVDV | AD[15.0]       | EACL:ACE=1                         | _            | 7tcyc/2 - 60 |      |                        |

| RDX pulse width                                   | <b>t</b> rlrh  | RDX            | _                                  | 3tcyc/2 - 8  | _            | ns   | w/o cycle<br>extension |

| $RDX \downarrow \Rightarrow Valid \ data \ input$ | <b>t</b> RLDV  | RDX, AD[15:0]  | _                                  |              | 3tcyc/2 - 55 | ns   | w/o cycle<br>extension |

| $RDX \uparrow \Rightarrow Data hold time$         | <b>t</b> RHDX  | RDX, AD[15:0]  | _                                  | 0            |              | ns   |                        |

| Address valid $\Rightarrow$ Data hold time        | <b>t</b> AXDX  | A[23:16]       | _                                  | 0            | _            | ns   |                        |

| $RDX \uparrow \Rightarrow ALE \uparrow time$      | <b>t</b> RHLH  | DDY ALE        | EACL:STS=1 and EACL:ACE=1          | 3tcyc/2 – 15 | _            | ns   |                        |

| RDX   ⇒ ALE   time                                | I KHLH         | RDX, ALE       | other ECL:STS,<br>EACL:ACE setting | tcyc/2 - 15  | _            | 115  |                        |

| Valid address                                     | <b>t</b> avch  | A[23:16], ECLK |                                    | tcyc - 20    | _            | nc   |                        |

| ⇒ ECLK ↑ time                                     | tadvch         | AD[15:0], ECLK |                                    | tcyc/2 - 20  |              | ns   |                        |

| $RDX \downarrow \Rightarrow ECLK \uparrow time$   | <b>t</b> RLCH  | RDX, ECLK      |                                    | tcyc/2 - 15  |              | ns   |                        |

| $ALE \downarrow \Rightarrow RDX \downarrow time$  | <b>t</b> llrl  | ALE, RDX       | EACL:STS=0                         | tcyc/2 - 15  |              | ns   |                        |

|                                                   | LLLKL          | ALL, NOA       | EACL:STS=1                         | <b>– 15</b>  | _            | 113  |                        |

| ECLK <sup>↑</sup> ⇒ Valid data input              | <b>t</b> CHDV  | AD[15:0], ECLK | _                                  | _            | tcyc - 55    | ns   |                        |

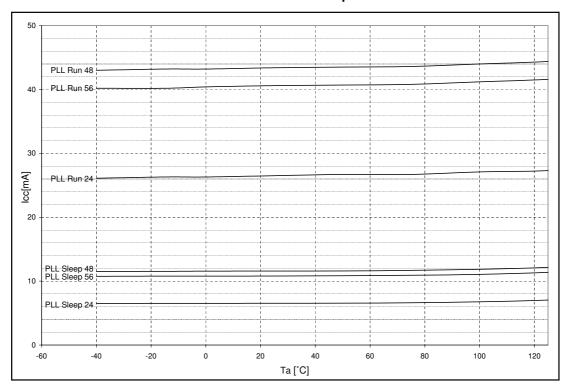

| Mode name     | Details                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC Sleep 2M   | RC Sleep mode current I <sub>CCSRCH</sub> with the following settings:  RC oscillator set to 2MHz (CKFCR:RCFS = 1)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 2MHz  Regulator in High Power Mode  Core voltage at 1.8V (VRCR:HPM[1:0] = 10 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped                         |

| RC Sleep 100k | RC Sleep mode current I <sub>CCSRCL</sub> with the following settings:  RC oscillator set to 100kHz (CKFCR:RCFS = 0)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 100kHz  Regulator in Low Power Mode A (SMCR:LPMSS = 1)  Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped |

| Sub Sleep     | Sub Sleep mode current I <sub>CCSSUB</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = f <sub>CLKP1</sub> = f <sub>CLKP2</sub> = 32kHz  • Regulator in Low Power Mode A (by hardware)  • Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  • PLL, RC oscillator and Main oscillator stopped                                           |

| PLL Timer 48  | PLL Timer mode current I <sub>CCTPLL</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 48MHz  • Regulator in High Power Mode  • Core voltage at 1.8V (VRCR:HPM[1:0] = 10 <sub>B</sub> )  • RC oscillator and Sub oscillator stopped                                                                                                            |

| Main Timer    | Main Timer mode current I <sub>CCTMAIN</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 4MHz  • Regulator in Low Power Mode A (SMCR:LPMSS = 1)  • Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  • PLL, RC oscillator and Sub oscillator stopped                                                                                  |

| RC Timer 2M   | RC Timer mode current I <sub>CCTRCH</sub> with the following settings:  RC oscillator set to 2MHz (CKFCR:RCFS = 1)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 2MHz  Regulator in Low Power Mode A (SMCR:LPMSS = 1)  Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped                                               |

| RC Timer 100k | RC Timer mode current I <sub>CCTRCL</sub> with the following settings:  RC oscillator set to 100kHz (CKFCR:RCFS = 0)  f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 100kHz  Regulator in Low Power Mode A (SMCR:LPMSS = 1)  Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  PLL, Main oscillator and Sub oscillator stopped                                           |

| Sub Timer     | Sub Timer mode current I <sub>CCTSUB</sub> with the following settings:  • f <sub>CLKS1</sub> = f <sub>CLKS2</sub> = 32kHz  • Regulator in Low Power Mode A (by hardware)  • Core voltage at 1.8V (VRCR:LPMA[2:0] = 110 <sub>B</sub> )  • PLL, RC oscillator and Main oscillator stopped                                                                                     |

| Mode name | Details                                                                                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop 1.8V | Stop mode current I <sub>CCH</sub> with the following settings:  Regulator in Low Power Mode B (by hardware)  Core voltage at 1.8V (VRCR:LPMB[2:0] = 110 <sub>B</sub> ) |

| Stop 1.2V | Stop mode current I <sub>CCH</sub> with the following settings:  Regulator in Low Power Mode B (by hardware)  Core voltage at 1.2V (VRCR:LPMB[2:0] = 000 <sub>B</sub> ) |

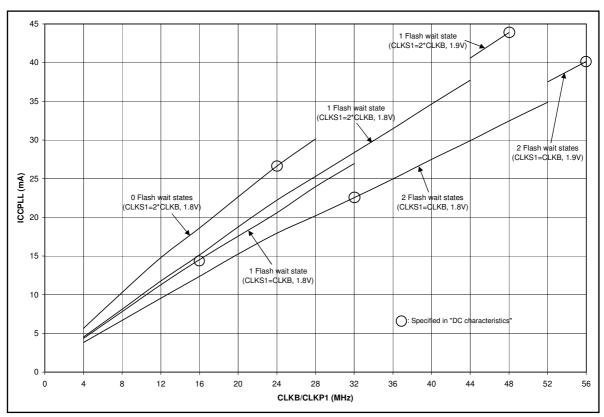

### MB96F353/F355 PLL Run and Sleep mode currents

### MB96F356 PLL Run mode currents

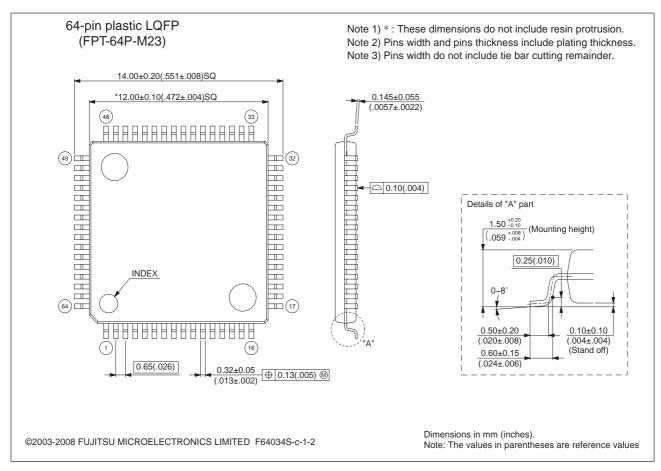

### ■ PACKAGE DIMENSION MB96(F)35x LQFP 64 - M23

| 64-pin plastic LQFP | Lead pitch                     | 0.65 mm              |

|---------------------|--------------------------------|----------------------|

|                     | Package width × package length | 12.0 × 12.0 mm       |

|                     | Lead shape                     | Gullwing             |

|                     | Sealing method                 | Plastic mold         |

|                     | Mounting height                | 1.70 mm MAX          |

|                     | Code<br>(Reference)            | P-LFQFP64-12×12-0.65 |

| (FPT-64P-M23)       |                                |                      |

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/

### **■** ORDERING INFORMATION

## **MCU** with CAN controller

| Part number                        | Flash/ROM            | Subclock | Persistent<br>Low Volt-<br>age Reset | Package                               |

|------------------------------------|----------------------|----------|--------------------------------------|---------------------------------------|

| MB96F353RSB PMC-GSE2               |                      | No       | -                                    | 64 pins Plastic LQFP<br>(FPT-64P-M23) |

| MB96F353RWB PMC-GSE2               | Floob A (OGKR)       | Yes      |                                      |                                       |

| MB96F353RSB PMC1-GSE2              | Flash A (96KB)       | No       |                                      | 64 pins Plastic LQFP                  |

| MB96F353RWB PMC1-GSE2              |                      | Yes      | No                                   | (FPT-64P-M24)                         |

| MB96F355RSB PMC-GSE2               |                      | No       | INO                                  | 64 pins Plastic LQFP                  |

| MB96F355RWB PMC-GSE2               |                      | Yes      |                                      | (FPT-64P-M23)                         |

| MB96F355RSB PMC1-GSE2              | Flash A (160KB)      | No       |                                      | 64 pins Plastic LQFP<br>(FPT-64P-M24) |

| MB96F355RWB PMC1-GSE2              |                      | Yes      |                                      |                                       |

| MB96F356YSB PMC-GSE2               |                      |          | Yes                                  |                                       |

| MB96F356RSB PMC-GSE2               |                      | No       | No                                   | 64 pins Plastic LQFP                  |

| MB96F356YWB PMC-GSE2               |                      | Vaa      | Yes                                  | (FPT-64P-M23)                         |

| MB96F356RWB PMC-GSE2               |                      | Yes      | No                                   |                                       |

| MB96F356YSB PMC1-GSE2              | Flash A (288KB)      | NI.      | Yes                                  |                                       |

| MB96F356RSB PMC1-GSE2              |                      | No       | No                                   | 64 pins Plastic LQFP                  |

| MB96F356YWB PMC1-GSE2              |                      | Yes      | Yes                                  | (FPT-64P-M24)                         |

| MB96F356RWB PMC1-GSE2              |                      |          | No                                   |                                       |

| MB96V300BRB-ES<br>(for evaluation) | Emulated by ext. RAM | Yes      | No                                   | 416 pin Plastic BGA<br>(BGA-416P-M02) |

| Revision | Date       | Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7        | 2010-06-24 | <ul> <li>AD converter IAIN spec improved: 1uA valid up to 105deg, 1.2uA above 105deg</li> <li>Low voltage detector: Detection levels of MB96F353/F355 updated</li> <li>Note added that PLL phase jitter spec does not include jitter coming from Main clock</li> <li>Note added in DC characteristics how to select driving strength of ports</li> <li>I2C AC spec updated: tof, Cb and tSP spec added, wrong footnotes and Condition removed</li> <li>I/O Circuit type: Note added for type "N" (slew rate control according to I2C spec)</li> <li>Example characteristics updated, new figures added showing dependency of PLL Run mode current on frequency</li> <li>Updated Power Supply current spec in Run/Sleep/Timer/Stop modes (new spec items in PLL Run/Sleep mode, small adjustment of most other values)</li> <li>Package dimension: Added the following sentence under the figure: "Please confirm the latest Package dimension by following URL. http://edevice.fujitsu.com/package/en-search/"</li> <li>AD converter: Impact of input pin capacitance and external capacitance added to formula for calculation of the sampling time</li> <li>Added specification of RC clock stabilization time</li> <li>Ordering information updated: MB96F353/F355**A -&gt; MB96F353/F355**B, the device development is finished</li> <li>Feature description I2C: '8-bit addressing' corrected to '7-bit addressing'</li> <li>Feature description PPG: 'Reload timer overflow as clock input' corrected to 'Reload timer underflow as clock input'</li> <li>ICCLVD specification updated, at 125deg typical value is 7uA and maximum value is 20uA</li> <li>Company name updated on the cover page: Fujitsu Microelectronics Limited -&gt; Fujitsu Semiconductor Limited</li> </ul> |

## **FUJITSU SEMICONDUCTOR LIMITED**

Nomura Fudosan Shin-yokohama Bldg. 10-23, Shin-yokohama 2-Chome, Kohoku-ku Yokohama Kanagawa 222-0033, Japan

Tel: +81-45-415-5858 http://jp.fujitsu.com/fsl/en/

For further information please contact:

### North and South America

FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://www.fma.fujitsu.com/

#### **Europe**

FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122 http://emea.fujitsu.com/microelectronics/

#### Korea

FUJITSU MICROELECTRONICS KOREA LTD. 206 Kosmo Tower Building, 1002 Daechi-Dong, Gangnam-Gu, Seoul 135-280, Republic of Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://kr.fujitsu.com/fmk/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LTD. 151 Lorong Chuan, #05-08 New Tech Park 556741 Singapore Tel: +65-6281-0770 Fax: +65-6281-0220 http://www.fmal.fujitsu.com/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China

Tel: +86-21-6146-3688 Fax: +86-21-6335-1605

http://cn.fujitsu.com/fmc/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road, Tsimshatsui, Kowloon, Hong Kong

Tel: +852-2377-0226 Fax: +852-2376-3269

http://cn.fujitsu.com/fmc/en/

Specifications are subject to change without notice. For further information please contact each office.

### All Rights Reserved.

The contents of this document are subject to change without notice.

Customers are advised to consult with sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU SEMICONDUCTOR device; FUJITSU SEMICONDUCTOR does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information.

FUJITSU SEMICONDUCTOR assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU SEMICONDUCTOR or any third party or does FUJITSU SEMICONDUCTOR warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU SEMICONDUCTOR assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU SEMICONDUCTOR will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of overcurrent levels and other abnormal operating conditions.

Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Edited: Sales Promotion Department