Welcome to <u>E-XFL.COM</u>

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 76                                                                               |

| Program Memory Size        | 320KB (320K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 34K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 110°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-100-8                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2361b40f80laahxuma1 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Summary of Features

### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XC236xB please contact your sales representative or local distributor.

This document describes several derivatives of the XC236xB group:

**Basic Device Types** are readily available and **Special Device Types** are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term XC236xB is used for all derivatives throughout this document.

### **Summary of Features**

# 1.1 Basic Device Types

Basic device types are available and can be ordered through Infineon's direct and/or distribution channels.

### Table 1 Synopsis of XC236xB Basic Device Types

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>      |

|--------------------------|-------------------------------|------------------------------|------------------------|----------------------------|-------------------------------|

| XC2365B-40F80LR          | 320 Kbytes                    | 16 Kbytes<br>16 Kbytes       |                        | 11 + 5                     | 3 CAN Node,<br>6 Serial Chan. |

1) The 80 MHz type is marked ...80L. The 40 MHz type is marked ...40L.

2) Specific information about the on-chip Flash memory in Table 3.

3) All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

Specific information about the available channels in Table 5. Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

### **General Device Information**

# 2 General Device Information

The XC236xB series (16/32-Bit Single-Chip Microcontroller

with 32-Bit Performance) is a part of the Infineon XC2000 Family of full-feature singlechip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

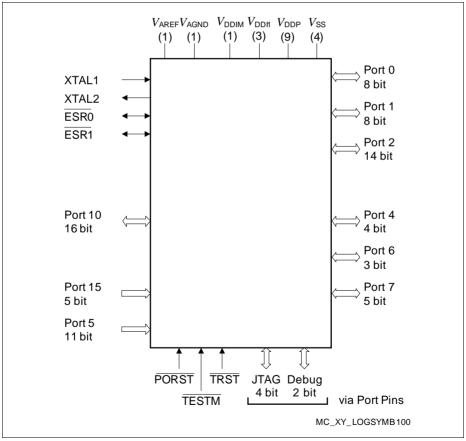

Figure 2 XC236xB Logic Symbol

### **General Device Information**

# 2.1 Pin Configuration and Definition

The pins of the XC236xB are described in detail in **Table 6**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

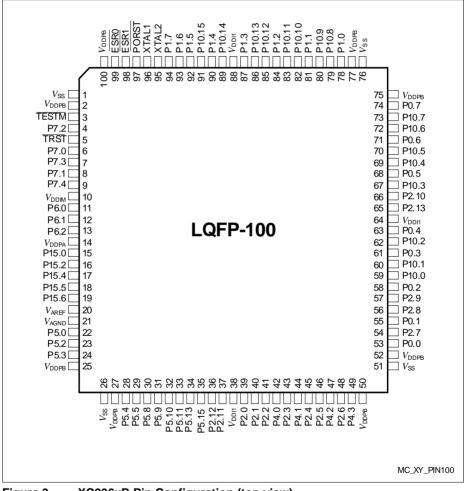

Figure 3 XC236xB Pin Configuration (top view)

### **General Device Information**

### **Key to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bit field PC in the associated register Px\_IOCRy. Output O0 is selected by setting the respective bit field PC to 1x00<sub>B</sub>, output O1 is selected by 1x01<sub>B</sub>, etc.

Output signal OH is controlled by hardware.

- **Type**: Indicates the pad type and its power supply domain (A, B, M, 1).

- St: Standard pad

- Sp: Special pad e.g. XTALx

- DP: Double pad can be used as standard or high speed pad

- In: Input only pad

- PS: Power supply pad

| Pin | Symbol | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TESTM  | I      | In/B | <b>Testmode Enable</b><br>Enables factory test modes, must be held HIGH for<br>normal operation (connect to $V_{\text{DDPB}}$ ).<br>An internal pull-up device will hold this pin high<br>when nothing is driving it.                                                                                                                                       |

| 4   | P7.2   | O0 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                               |

|     | EMUX0  | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                                                                                                                                                                                 |

|     | TDI_C  | IH     | St/B | JTAG Test Data Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.                                                                                                                                                                                                    |

| 5   | TRST   | 1      | In/B | Test-System Reset Input<br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XC236xB's debug system.<br>In this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pull-down device will hold this pin low<br>when nothing is driving it. |

### Table 6 Pin Definitions and Functions

# XC2361B, XC2363B, XC2364B, XC2365B XC2000 Family / Value Line

### **General Device Information**

| Table            | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                            |  |  |  |  |

|------------------|--------------------------------------------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin              | Symbol                                                 | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                   |  |  |  |  |

| 98               | ESR1                                                   | O0 / I | St/B | <b>External Service Request 1</b><br>After power-up, an internal weak pull-up device<br>holds this pin high when nothing is driving it.                                                                                                                                    |  |  |  |  |

|                  | RxDC0E                                                 | I      | St/B | CAN Node 0 Receive Data Input                                                                                                                                                                                                                                              |  |  |  |  |

|                  | U1C0_DX0F                                              | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                           |  |  |  |  |

|                  | U1C0_DX2C                                              | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                        |  |  |  |  |

|                  | U1C1_DX0C                                              | I      | St/B | USIC1 Channel 1 Shift Data Input                                                                                                                                                                                                                                           |  |  |  |  |

|                  | U1C1_DX2B                                              | I      | St/B | USIC1 Channel 1 Shift Control Input                                                                                                                                                                                                                                        |  |  |  |  |

|                  | U2C1_DX2C                                              | I      | St/B | USIC2 Channel 1 Shift Control Input                                                                                                                                                                                                                                        |  |  |  |  |

| 99               | ESR0                                                   | O0 / I | St/B | <b>External Service Request 0</b><br>After power-up, ESR0 operates as open-drain<br>bidirectional reset with a weak pull-up.                                                                                                                                               |  |  |  |  |

|                  | U1C0_DX0E                                              | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                           |  |  |  |  |

|                  | U1C0_DX2B                                              | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                        |  |  |  |  |

| 10               | V <sub>DDIM</sub>                                      | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.                                                                                                                                                       |  |  |  |  |

| 38,<br>64,<br>88 | V <sub>DDI1</sub>                                      | -      | PS/1 | <b>Digital Core Supply Voltage for Domain 1</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All V <sub>DDI1</sub> pins must be connected to each other.                                                                                        |  |  |  |  |

| 14               | V <sub>DDPA</sub>                                      | -      | PS/A | Digital Pad Supply Voltage for Domain A<br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The A/D_Converters and ports P5, P6 and<br>P15 are fed from supply voltage $V_{\text{DDPA}}$ . |  |  |  |  |

# 3 Functional Description

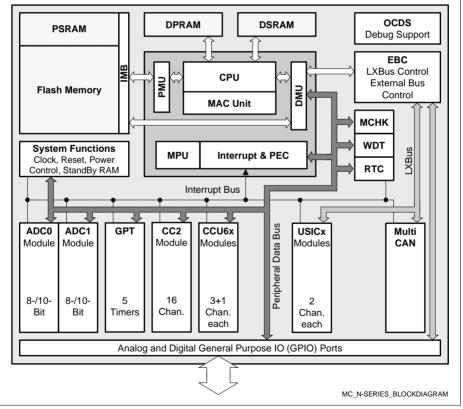

The architecture of the XC236xB combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC236xB.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC236xB.

Figure 4 Block Diagram

# 3.2 External Bus Controller

All external memory access operations are performed by a special on-chip External Bus Controller (EBC). The EBC also controls access to resources connected to the on-chip LXBus (MultiCAN and the USIC modules). The LXBus is an internal representation of the external bus that allows access to integrated peripherals and modules in the same way as to external components.

The EBC can be programmed either to Single Chip Mode, when no external memory is required, or to an external bus mode with the following selections<sup>1)</sup>:

- Address Bus Width with a range of 0 ... 24-bit

- Data Bus Width 8-bit or 16-bit

- Bus Operation Multiplexed or Demultiplexed

The bus interface uses Port 10 and Port 2 for addresses and data. In the demultiplexed bus modes, the lower addresses are output separately on Port 0 and Port 1. The number of active segment address lines is selectable, restricting the external address space to 8 Mbytes ... 64 Kbytes. This is required when interface lines shall be assigned to Port 2.

External  $\overline{CS}$  signals (address windows plus default) can be generated and output on Port 4 in order to save external glue logic. External modules can be directly connected to the common address/data bus and their individual select lines.

Important timing characteristics of the external bus interface are programmable (with registers TCONCSx/FCONCSx) to allow the user to adapt it to a wide range of different types of memories and external peripherals.

Access to very slow memories or modules with varying access times is supported by a special 'Ready' function. The active level of the control input signal is selectable.

In addition, up to four independent address windows may be defined (using registers ADDRSELx) to control access to resources with different bus characteristics. These address windows are arranged hierarchically where window 4 overrides window 3, and window 2 overrides window 1. All accesses to locations not covered by these four address windows are controlled by TCONCS0/FCONCS0. The currently active window can generate a chip select signal.

The external bus timing is based on the rising edge of the reference clock output CLKOUT. The external bus protocol is compatible with that of the standard C166 Family.

<sup>1)</sup> Bus modes are switched dynamically if several address windows with different mode settings are used.

With this hardware most XC236xB instructions are executed in a single machine cycle of 12.5 ns @ 80-MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC236xB instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

# 3.6 Interrupt System

The architecture of the XC236xB supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Using a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed. With the PEC just one cycle is 'stolen' from the current CPU activity to perform the PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC236xB has eight PEC channels, each with fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC236xB can react quickly to the occurrence of non-deterministic events.

### Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

### External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

### **Trap Processing**

The XC236xB provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

# 3.9 Capture/Compare Units CCU6x

The XC236xB types feature the CCU60, CCU61 unit(s).

CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

### **Timer 12 Features**

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

### **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

### **Additional Features**

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

With its maximum resolution of 2 system clock cycles, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The counting direction (up/down) for each timer can be programmed by software or altered dynamically with an external signal on a port pin (TxEUD<sup>1</sup>). Concatenation of the timers is supported with the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can also be used to clock the CAPCOM2 timers and to initiate a reload from the CAPREL register.

The CAPREL register can capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN); timer T5 may optionally be cleared after the capture procedure. This allows the XC236xB to measure absolute time differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) can also be generated upon transitions of GPT1 timer T3 inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental Interface Mode.

<sup>1)</sup> Exception: T5EUD is not connected to a pin.

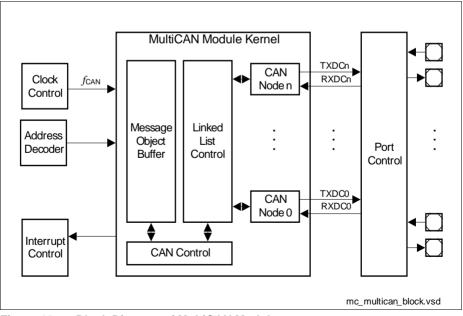

# 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

### 3.15 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

# 3.16 Watchdog Timer

The Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Watchdog Timer overflows, generating a prewarning interrupt and then a reset request.

The Watchdog Timer is a 16-bit timer clocked with the system clock divided by 16,384 or 256. The Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Watchdog Timer is reloaded and the prescaler is cleared.

Time intervals between 3.2  $\mu$ s and 13.4 s can be monitored (@ 80 MHz).

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

# 4 Electrical Parameters

The operating range for the XC236xB is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

| Parameter                                                       | Symbol                  | Values |      |                        | Unit | Note /                             |

|-----------------------------------------------------------------|-------------------------|--------|------|------------------------|------|------------------------------------|

|                                                                 |                         | Min.   | Тур. | Max.                   | -    | Test Condition                     |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR      | -30    | -    | -                      | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR      | -      | -    | 30                     | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$    | -10    | _    | 10                     | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -      | -    | 100                    | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\sf J}{\sf SR}$     | -40    | _    | 150                    | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$     | -65    | _    | 150                    | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | -0.5   | -    | 6.0                    | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}~{\rm SR}$   | -0.5   | -    | V <sub>DDP</sub> + 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

Table 12 Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

Note: Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

### Table 13Operating Conditions (cont'd)

| Parameter                                                       | Symbol                  | Values |                           |                           | Unit | Note /                                                              |

|-----------------------------------------------------------------|-------------------------|--------|---------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                 |                         | Min.   | Тур.                      | Max.                      |      | Test Condition                                                      |

| Overload current coupling factor for digital I/O pins           | K <sub>OVD</sub><br>CC  | -      | 1.0 x<br>10 <sup>-2</sup> | 3.0 x<br>10 <sup>-2</sup> | -    | <i>I</i> <sub>OV</sub> < 0 mA; not<br>subject to<br>production test |

|                                                                 |                         | -      | 1.0 x<br>10 <sup>-4</sup> | 5.0 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV}$ > 0 mA; not<br>subject to<br>production test           |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -      | -                         | 50                        | mA   | not subject to production test                                      |

| Digital core supply voltage for domain $M^{8)}$                 | V <sub>DDIM</sub><br>CC | -      | 1.5                       | -                         |      |                                                                     |

| Digital core supply voltage for domain $1^{8)}$                 | V <sub>DDI1</sub><br>CC | -      | 1.5                       | -                         |      |                                                                     |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | 3.0    | -                         | 5.5                       | V    |                                                                     |

| Digital ground voltage                                          | $V_{\rm SS}{\rm SR}$    | -      | 0                         | -                         | V    |                                                                     |

To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each V<sub>DDIM</sub> and V<sub>DDI1</sub> pin to keep the resistance of the board tracks below 2 Ohm. Connect all V<sub>DDI1</sub> pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

- 2) Use one Capacitor for each pin.

- This is the reference load. For bigger capacitive loads, use the derating factors listed in the pad properties section.

- 4) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability (C<sub>L</sub>).

- 5) The operating frequency range may be reduced for specific device types. This is indicated in the device designation (...FxxL). 80 MHz devices are marked ...F80L.

- 6) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>IHmax</sub> (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>ILmin</sub> ((I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed 50 mA. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1 (powered by V<sub>DDIM</sub>).

### 4.3 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XC236xB can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC236xB are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.7.4**.

# Table 33 External Bus Timing for Lower Voltage Range

| Parameter                                                                           | Symbol                    |      | Values | 5    | Unit | Note /<br>Test Condition |

|-------------------------------------------------------------------------------------|---------------------------|------|--------|------|------|--------------------------|

|                                                                                     |                           | Min. | Тур.   | Max. |      |                          |

| $\frac{\text{Output valid delay for }\overline{\text{RD}},}{\text{WR}(\text{L/H})}$ | <i>t</i> <sub>10</sub> CC | -    | 11     | 20   | ns   |                          |

| Output valid delay for<br>BHE, ALE                                                  | <i>t</i> <sub>11</sub> CC | _    | 10     | 21   | ns   |                          |

| Address output valid delay for A23 A0                                               | <i>t</i> <sub>12</sub> CC | _    | 11     | 22   | ns   |                          |

| Address output valid delay<br>for AD15 AD0 (MUX<br>mode)                            | t <sub>13</sub> CC        | _    | 10     | 22   | ns   |                          |

| Output valid delay for CS                                                           | t <sub>14</sub> CC        | -    | 10     | 13   | ns   |                          |

| Data output valid delay for<br>AD15 AD0 (write data,<br>MUX mode)                   | <i>t</i> <sub>15</sub> CC | _    | 10     | 22   | ns   |                          |

| Data output valid delay for<br>D15 D0 (write data,<br>DEMUX mode)                   | t <sub>16</sub> CC        | _    | 10     | 22   | ns   |                          |

| Output hold time for $\overline{RD}$ , WR(L/H)                                      | <i>t</i> <sub>20</sub> CC | -2   | 8      | 10   | ns   |                          |

| Output hold time for BHE, ALE                                                       | <i>t</i> <sub>21</sub> CC | -2   | 8      | 10   | ns   |                          |

| Address output hold time for AD15 AD0                                               | <i>t</i> <sub>23</sub> CC | -3   | 8      | 10   | ns   |                          |

| Output hold time for CS                                                             | t <sub>24</sub> CC        | -3   | 8      | 11   | ns   |                          |

| Data output hold time for<br>D15 D0 and AD15<br>AD0                                 | <i>t</i> <sub>25</sub> CC | -3   | 8      | 10   | ns   |                          |

| Input setup time for<br>READY, D15 D0, AD15<br>AD0                                  | <i>t</i> <sub>30</sub> SR | 29   | 17     | -    | ns   |                          |

| Input hold time READY,<br>D15 D0, AD15 AD0 <sup>1)</sup>                            | <i>t</i> <sub>31</sub> SR | 0    | -9     | -    | ns   |                          |

Read data are latched with the same internal clock edge that triggers the address change and the rising edge of RD. Address changes before the end of RD have no impact on (demultiplexed) read cycles. Read data can change after the rising edge of RD.

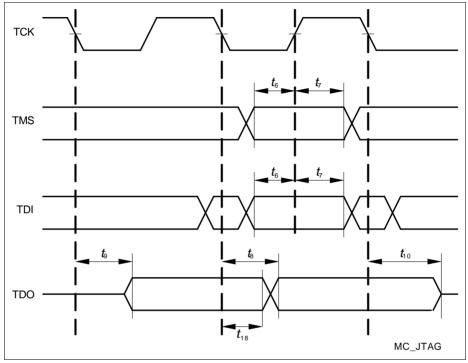

Figure 31 JTAG Timing

# XC2361B, XC2363B, XC2364B, XC2365B XC2000 Family / Value Line

### Package and Reliability

# Package Outlines

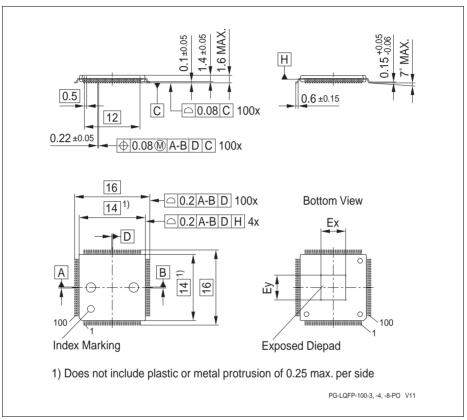

Figure 32 PG-LQFP-100-8/-15 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages