Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

E·XFl

| Product Status             | Not For New Designs                                                               |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | C1665V2                                                                           |

| Core Size                  | 16/32-Bit                                                                         |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI              |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Number of I/O              | 76                                                                                |

| Program Memory Size        | 320KB (320K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 34K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                         |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-100-8                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2365b40f80lrabkxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **General Device Information**

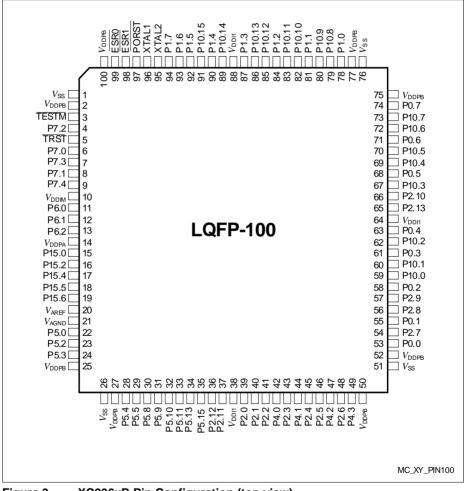

# 2.1 Pin Configuration and Definition

The pins of the XC236xB are described in detail in **Table 6**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

Figure 3 XC236xB Pin Configuration (top view)

#### **General Device Information**

| Tabl | e 6 Pin De     | efinitior  | is and | Functions (cont'd)                                                                                                                              |

|------|----------------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin  | Symbol         | Ctrl.      | Туре   | Function                                                                                                                                        |

| 36   | P2.12          | O0 / I     | St/B   | Bit 12 of Port 2, General Purpose Input/Output                                                                                                  |

|      | U0C0_SELO<br>4 | 01         | St/B   | USIC0 Channel 0 Select/Control 4 Output                                                                                                         |

|      | U0C1_SELO<br>3 | O2         | St/B   | USIC0 Channel 1 Select/Control 3 Output                                                                                                         |

|      | TXDC2          | 03         | St/B   | CAN Node 2 Transmit Data Output                                                                                                                 |

|      | READY          | IH         | St/B   | External Bus Interface READY Input                                                                                                              |

| 37   | P2.11          | O0 / I     | St/B   | Bit 11 of Port 2, General Purpose Input/Output                                                                                                  |

|      | U0C0_SELO<br>2 | 01         | St/B   | USIC0 Channel 0 Select/Control 2 Output                                                                                                         |

|      | U0C1_SELO<br>2 | 02         | St/B   | USIC0 Channel 1 Select/Control 2 Output                                                                                                         |

|      | BHE/WRH        | ОН         | St/B   | <b>External Bus Interf. High-Byte Control Output</b><br>Can operate either as Byte High Enable (BHE) or<br>as Write strobe for High Byte (WRH). |

| 39   | P2.0           | O0 / I     | St/B   | Bit 0 of Port 2, General Purpose Input/Output                                                                                                   |

|      | AD13           | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 13                                                                                                     |

|      | RxDC0C         | I          | St/B   | CAN Node 0 Receive Data Input                                                                                                                   |

|      | T5INB          | I          | St/B   | GPT12E Timer T5 Count/Gate Input                                                                                                                |

| 40   | P2.1           | O0 / I     | St/B   | Bit 1 of Port 2, General Purpose Input/Output                                                                                                   |

|      | TxDC0          | 01         | St/B   | CAN Node 0 Transmit Data Output                                                                                                                 |

|      | AD14           | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 14                                                                                                     |

|      | T5EUDB         | I          | St/B   | GPT12E Timer T5 External Up/Down Control<br>Input                                                                                               |

|      | ESR1_5         | I          | St/B   | ESR1 Trigger Input 5                                                                                                                            |

| 41   | P2.2           | O0 / I     | St/B   | Bit 2 of Port 2, General Purpose Input/Output                                                                                                   |

|      | TxDC1          | 01         | St/B   | CAN Node 1 Transmit Data Output                                                                                                                 |

|      | AD15           | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 15                                                                                                     |

|      | ESR2_5         | I          | St/B   | ESR2 Trigger Input 5                                                                                                                            |

#### **General Device Information**

| Table 6         Pin Definitions and Functions (cont'd) |                   |        |      |                                               |  |  |  |

|--------------------------------------------------------|-------------------|--------|------|-----------------------------------------------|--|--|--|

| Pin                                                    | Symbol            | Ctrl.  | Туре | Function                                      |  |  |  |

| 53                                                     | P0.0              | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output |  |  |  |

|                                                        | U1C0_DOUT         | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |  |

|                                                        | CCU61_CC6<br>0    | O3     | St/B | CCU61 Channel 0 IOutput                       |  |  |  |

|                                                        | A0                | ОН     | St/B | External Bus Interface Address Line 0         |  |  |  |

|                                                        | U1C0_DX0A         | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |  |

|                                                        | CCU61_CC6<br>0INA | I      | St/B | CCU61 Channel 0 Input                         |  |  |  |

|                                                        | ESR1_11           | I      | St/B | ESR1 Trigger Input 11                         |  |  |  |

| 54                                                     | P2.7              | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |  |

|                                                        | U0C1_SELO<br>0    | O1     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |  |

|                                                        | U0C0_SELO<br>1    | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |  |

|                                                        | CC2_CC20          | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |  |

|                                                        | A20               | ОН     | St/B | External Bus Interface Address Line 20        |  |  |  |

|                                                        | U0C1_DX2C         | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |  |

|                                                        | RxDC1C            | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |  |

|                                                        | ESR2_7            | I      | St/B | ESR2 Trigger Input 7                          |  |  |  |

| 55                                                     | P0.1              | O0 / I | St/B | Bit 1 of Port 0, General Purpose Input/Output |  |  |  |

|                                                        | U1C0_DOUT         | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |  |

|                                                        | TxDC0             | 02     | St/B | CAN Node 0 Transmit Data Output               |  |  |  |

|                                                        | CCU61_CC6<br>1    | O3     | St/B | CCU61 Channel 1 Output                        |  |  |  |

|                                                        | A1                | ОН     | St/B | External Bus Interface Address Line 1         |  |  |  |

|                                                        | U1C0_DX0B         | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |  |

|                                                        | CCU61_CC6<br>1INA | I      | St/B | CCU61 Channel 1 Input                         |  |  |  |

|                                                        | U1C0_DX1A         | I      | St/B | USIC1 Channel 0 Shift Clock Input             |  |  |  |

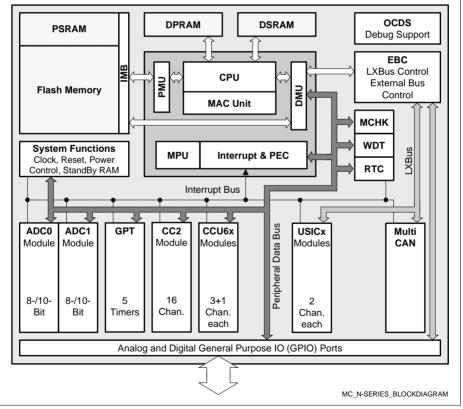

# 3 Functional Description

The architecture of the XC236xB combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC236xB.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC236xB.

Figure 4 Block Diagram

# 3.1 Memory Subsystem and Organization

The memory space of the XC236xB is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

| Address Area                   | Start Loc.           | End Loc.             | Area Size <sup>2)</sup>  | Notes               |

|--------------------------------|----------------------|----------------------|--------------------------|---------------------|

| IMB register space             | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes                |                     |

| Reserved                       | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | < 1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM            | E8'4000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 496 Kbytes               | Mirrors EPSRAM      |

| Emulated PSRAM                 | E8'0000 <sub>H</sub> | E8'3FFF <sub>H</sub> | up to<br>16 Kbytes       | With Flash timing   |

| Reserved for PSRAM             | E0'4000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 496 Kbytes               | Mirrors PSRAM       |

| PSRAM                          | E0'0000 <sub>H</sub> | E0'3FFF <sub>H</sub> | up to<br>16 Kbytes       | Program SRAM        |

| Reserved for Flash             | C5'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | 1,728 Kbytes             |                     |

| Flash 1                        | C4'0000 <sub>H</sub> | C4'FFFF <sub>H</sub> | 64 Kbytes                |                     |

| Flash 0                        | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes <sup>3)</sup> | Minus res. seg.     |

| External memory area           | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                 |                     |

| External IO area <sup>4)</sup> | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | 1,984 Kbytes             |                     |

| Reserved                       | 20'BC00 <sub>H</sub> | 20'FFFF <sub>H</sub> | 17 Kbytes                |                     |

| USIC0-2 alternate regs.        | 20'B000 <sub>H</sub> | 20'BBFF <sub>H</sub> | 3 Kbytes                 | Accessed via EBC    |

| MultiCAN alternate regs.       | 20'8000 <sub>H</sub> | 20'AFFF <sub>H</sub> | 12 Kbytes                | Accessed via EBC    |

| Reserved                       | 20'5800 <sub>H</sub> | 20'7FFF <sub>H</sub> | 10 Kbytes                |                     |

| USIC0–2 registers              | 20'4000 <sub>H</sub> | 20'57FF <sub>H</sub> | 6 Kbytes                 | Accessed via EBC    |

| Reserved                       | 20'6800 <sub>H</sub> | 20'7FFF <sub>H</sub> | 6 Kbytes                 |                     |

| MultiCAN registers             | 20'0000 <sub>H</sub> | 20'3FFF <sub>H</sub> | 16 Kbytes                | Accessed via EBC    |

| External memory area           | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | 1984 Kbytes              |                     |

| SFR area                       | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbytes               |                     |

| Dualport RAM (DPRAM)           | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                 |                     |

| Reserved for DPRAM             | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbytes                 |                     |

| ESFR area                      | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbytes               |                     |

| XSFR area                      | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                 |                     |

| Data SRAM (DSRAM)              | 00'A000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 16 Kbytes                |                     |

# Table 8 XC236xB Memory Map <sup>1)</sup>

# 3.2 External Bus Controller

All external memory access operations are performed by a special on-chip External Bus Controller (EBC). The EBC also controls access to resources connected to the on-chip LXBus (MultiCAN and the USIC modules). The LXBus is an internal representation of the external bus that allows access to integrated peripherals and modules in the same way as to external components.

The EBC can be programmed either to Single Chip Mode, when no external memory is required, or to an external bus mode with the following selections<sup>1)</sup>:

- Address Bus Width with a range of 0 ... 24-bit

- Data Bus Width 8-bit or 16-bit

- Bus Operation Multiplexed or Demultiplexed

The bus interface uses Port 10 and Port 2 for addresses and data. In the demultiplexed bus modes, the lower addresses are output separately on Port 0 and Port 1. The number of active segment address lines is selectable, restricting the external address space to 8 Mbytes ... 64 Kbytes. This is required when interface lines shall be assigned to Port 2.

External  $\overline{CS}$  signals (address windows plus default) can be generated and output on Port 4 in order to save external glue logic. External modules can be directly connected to the common address/data bus and their individual select lines.

Important timing characteristics of the external bus interface are programmable (with registers TCONCSx/FCONCSx) to allow the user to adapt it to a wide range of different types of memories and external peripherals.

Access to very slow memories or modules with varying access times is supported by a special 'Ready' function. The active level of the control input signal is selectable.

In addition, up to four independent address windows may be defined (using registers ADDRSELx) to control access to resources with different bus characteristics. These address windows are arranged hierarchically where window 4 overrides window 3, and window 2 overrides window 1. All accesses to locations not covered by these four address windows are controlled by TCONCS0/FCONCS0. The currently active window can generate a chip select signal.

The external bus timing is based on the rising edge of the reference clock output CLKOUT. The external bus protocol is compatible with that of the standard C166 Family.

<sup>1)</sup> Bus modes are switched dynamically if several address windows with different mode settings are used.

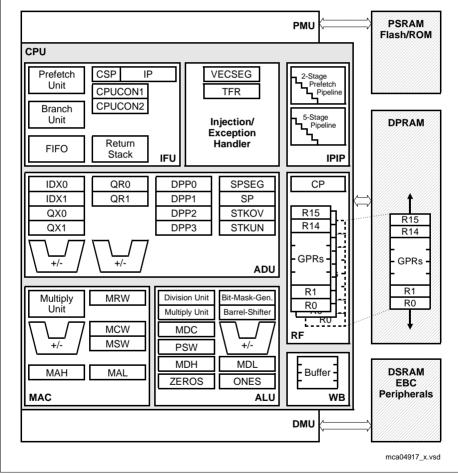

# 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

# Figure 5 CPU Block Diagram

# 3.6 Interrupt System

The architecture of the XC236xB supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Using a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed. With the PEC just one cycle is 'stolen' from the current CPU activity to perform the PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC236xB has eight PEC channels, each with fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC236xB can react quickly to the occurrence of non-deterministic events.

### Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

# External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

# **Trap Processing**

The XC236xB provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

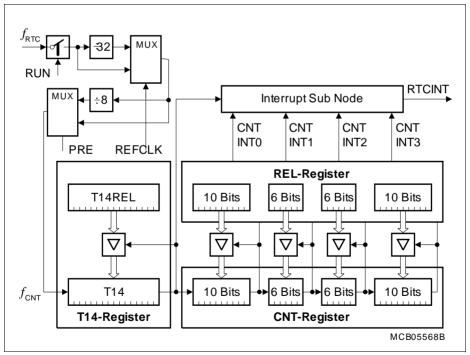

# 3.11 Real Time Clock

The Real Time Clock (RTC) module of the XC236xB can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

# Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

# 3.12 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 11 + 5 multiplexed input channels and a sample and hold circuit have been integrated on-chip. 4 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XC236xB support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

# 4.1.1 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XC236xB. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

| Parameter                                                        | Symbol                    |      | Values                    |                           | Unit | Note /<br>Test Condition                                            |

|------------------------------------------------------------------|---------------------------|------|---------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                  |                           | Min. | Тур.                      | Max.                      |      |                                                                     |

| Voltage Regulator Buffer<br>Capacitance for DMP_M                | $C_{\rm EVRM} \ { m SR}$  | 1.0  | -                         | 4.7                       | μF   | 1)                                                                  |

| Voltage Regulator Buffer<br>Capacitance for DMP_1                | $C_{\rm EVR1}$ SR         | 0.47 | -                         | 2.2                       | μF   | 2)1)                                                                |

| External Load<br>Capacitance                                     | $C_{L} \operatorname{SR}$ | -    | 20 <sup>3)</sup>          | -                         | pF   | pin out<br>driver= default<br>4)                                    |

| System frequency                                                 | $f_{\rm SYS}{\rm SR}$     | -    | -                         | 80                        | MHz  | 5)                                                                  |

| Overload current for analog inputs <sup>6)</sup>                 | $I_{\rm OVA}{\rm SR}$     | -2   | -                         | 5                         | mA   | not subject to production test                                      |

| Overload current for digital inputs <sup>6)</sup>                | I <sub>OVD</sub> SR       | -5   | -                         | 5                         | mA   | not subject to production test                                      |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC    | _    | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> < 0 mA; not<br>subject to<br>production test |

|                                                                  |                           | -    | 1.0 x<br>10 <sup>-6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | <i>I</i> <sub>OV</sub> > 0 mA; not<br>subject to<br>production test |

# Table 13 Operating Conditions

# Table 18 Switching Power Consumption

| Parameter                                                                    | Symbol                  |      | Values                      |                                           | Unit | Note /                                                              |

|------------------------------------------------------------------------------|-------------------------|------|-----------------------------|-------------------------------------------|------|---------------------------------------------------------------------|

|                                                                              |                         | Min. | Тур.                        | Max.                                      |      | Test Condition                                                      |

| Power supply current<br>(active) with all peripherals<br>active and EVVRs on | I <sub>SACT</sub><br>CC | -    | $6 + 0.6 \\ x f_{SYS}^{1)}$ | 8+1.0<br>x f <sub>SYS</sub> <sup>1)</sup> | mA   | power_mode=<br>active ;<br>voltage_range=<br>both <sup>2)3)4)</sup> |

| Power supply current in stopover mode, EVVRs on                              | I <sub>SSO</sub> CC     | -    | 0.7                         | 2.0                                       | mA   | power_mode=<br>stopover ;<br>voltage_range=<br>both <sup>4)</sup>   |

1)  $f_{SYS}$  in MHz

2) The pad supply voltage pins (V<sub>DDPB</sub>) provide the input current for the on-chip EVVRs and the current consumed by the pin output drivers. A small current is consumed because the drivers input stages are switched. In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to 3 + 0.6 x f<sub>SYS</sub>.

3) Please consider the additional conditions described in section "Active Mode Power Supply Current".

4) The pad supply voltage has only a minor influence on this parameter.

### Active Mode Power Supply Current

The actual power supply current in active mode not only depends on the system frequency but also on the configuration of the XC236xB's subsystem.

Besides the power consumed by the device logic the power supply pins also provide the current that flows through the pin output drivers.

A small current is consumed because the drivers' input stages are switched.

The IO power domains can be supplied separately. Power domain A ( $V_{\text{DDPA}}$ ) supplies the A/D converters and Port 6. Power domain B ( $V_{\text{DDPB}}$ ) supplies the on-chip EVVRs and all other ports.

During operation domain A draws a maximum current of 1.5 mA for each active A/D converter module from  $V_{\rm DDPA}$ .

In Fast Startup Mode (with the Flash modules deactivated), the typical current is reduced to  $3 + 0.6 \times f_{SYS}$  mA.

# 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XC236xB into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                 |                                         | Values       | S                                     | Unit | Note /                                   |

|-----------------------------------------------------------------------|------------------------|-----------------------------------------|--------------|---------------------------------------|------|------------------------------------------|

|                                                                       |                        | Min.                                    | Тур.         | Max.                                  |      | Test Condition                           |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                      | -            | 1                                     | %    | $\Delta T_{\rm J} \le 10^{\circ}{\rm C}$ |

| Internal clock source frequency                                       | $f_{\rm INT}{\rm CC}$  | 4.8                                     | 5.0          | 5.2                                   | MHz  |                                          |

| Wakeup clock source                                                   | $f_{\rm WU}$ CC        | 400                                     | -            | 700                                   | kHz  | FREQSEL= 00                              |

| frequency <sup>2)</sup>                                               |                        | 210                                     | -            | 390                                   | kHz  | FREQSEL= 01                              |

|                                                                       |                        | 140                                     | -            | 260                                   | kHz  | FREQSEL= 10                              |

|                                                                       |                        | 110                                     | -            | 200                                   | kHz  | FREQSEL= 11                              |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.5                                     | 2.0          | 2.4                                   | ms   | <i>f</i> <sub>₩U</sub> = 500 kHz         |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC    | 11 /<br>f <sub>WU</sub> <sup>3)</sup>   | -            | 12 /<br>f <sub>WU</sub> <sup>3)</sup> | μs   |                                          |

| Core voltage (PVC) supervision level                                  | $V_{\rm PVC}{ m CC}$   | V <sub>LV</sub> -<br>0.03               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.07 <sup>4)</sup>  | V    | 5)                                       |

| Supply watchdog (SWD)<br>supervision level                            | V <sub>SWD</sub><br>CC | V <sub>LV</sub> -<br>0.10 <sup>6)</sup> | $V_{\rm LV}$ | V <sub>LV</sub> + 0.15                | V    | voltage_range=<br>lower <sup>5)</sup>    |

|                                                                       |                        | V <sub>LV</sub> -<br>0.15               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.15                | V    | voltage_range=<br>upper <sup>5)</sup>    |

|                                                                       |                        | V <sub>LV</sub> -<br>0.30               | $V_{\rm LV}$ | V <sub>LV</sub> + 0.30                | V    | $V_{\rm LV}$ = 5.5 V <sup>5)</sup>       |

# Table 22 Various System Parameters

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

- This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

- 3)  $f_{WU}$  in MHz

- 4) This value includes a hysteresis of approximately 50 mV for rising voltage.

- 5)  $V_{\rm LV}$  = selected SWD voltage level

- 6) The limit  $V_{LV}$  0.10 V is valid for the OK1 level. The limit for the OK2 level is  $V_{LV}$  0.15 V.

# Conditions for t<sub>SPO</sub> Timing Measurement

The time required for the transition from **Power-on** to **Base** mode is called  $t_{SPO}$ . It is measured under the following conditions:

Precondition: The pad supply is valid, i.e.  $V_{\text{DDPB}}$  is above 3.0V and remains above 3.0V even though the XC236xB is starting up. No debugger is attached.

Start condition: Power-on reset is removed ( $\overline{PORST} = 1$ ).

End condition: External pin toggle caused by first user instruction executed from FLASH after startup.

# Conditions for t<sub>SSO</sub> Timing Measurement

The time required for the transition from **Stopover** to **Stopover Waked-Up** mode is called  $t_{SSO}$ . It is measured under the following conditions:

Precondition: The **Stopover** mode has been entered using the procedure defined in the Programmer's Guide.

Start condition: Pin toggle on ESR pin triggering the startup sequence.

End condition: External pin toggle caused by first user instruction executed from PSRAM after startup.

# 4.7.2 Definition of Internal Timing

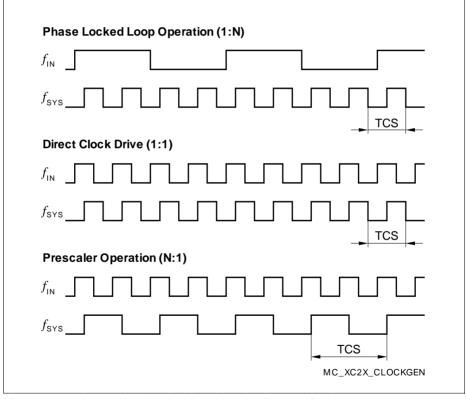

The internal operation of the XC236xB is controlled by the internal system clock  $f_{SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XC236xB.

Figure 19 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in **Figure 19** uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

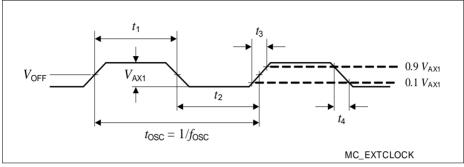

- 1) The amplitude voltage  $V_{AX1}$  refers to the offset voltage  $V_{OFF}$ . This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by  $V_{IX1}$ .

- 2) Overload conditions must not occur on pin XTAL1.

### Figure 21 External Clock Drive XTAL1

Note: For crystal or ceramic resonator operation, it is strongly recommended to measure the oscillation allowance (negative resistance) in the final target system (layout) to determine the optimum parameters for oscillator operation.

The manufacturers of crystals and ceramic resonators offer an oscillator evaluation service. This evaluation checks the crystal/resonator specification limits to ensure a reliable oscillator operation.

# 4.7.4 Pad Properties

The output pad drivers of the XC236xB can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . Therefore the following tables list the pad parameters for the upper voltage range and the lower voltage range, respectively.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 28** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}}$  typ. 5 V;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

| Parameter                                                       | Symbol                  |      | Values | 5    | Unit | Note /                      |

|-----------------------------------------------------------------|-------------------------|------|--------|------|------|-----------------------------|

|                                                                 |                         | Min. | Тур.   | Max. |      | Test Condition              |

| Maximum output driver<br>current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -    | -      | 4.0  | mA   | Driver_Strength<br>= Medium |

|                                                                 |                         | _    | -      | 10   | mA   | Driver_Strength<br>= Strong |

|                                                                 |                         | -    | -      | 0.5  | mA   | Driver_Strength<br>= Weak   |

| Nominal output driver<br>current (absolute value)               | I <sub>Onom</sub><br>CC | -    | -      | 1.0  | mA   | Driver_Strength<br>= Medium |

|                                                                 |                         | -    | -      | 2.5  | mA   | Driver_Strength<br>= Strong |

|                                                                 |                         | _    | -      | 0.1  | mA   | Driver_Strength<br>= Weak   |

Table 28 Standard Pad Parameters for Upper Voltage Range

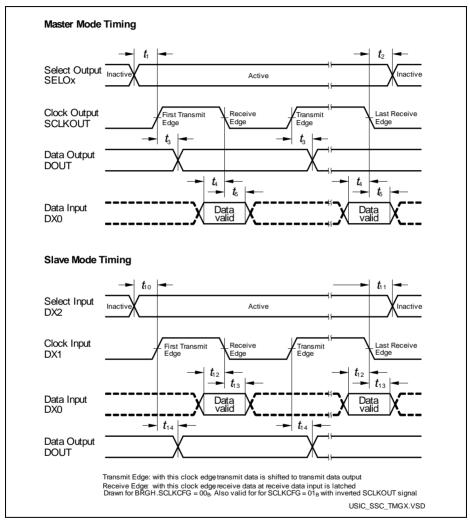

# Table 35 USIC SSC Master Mode Timing for Lower Voltage Range

| Parameter                                                               | Symbol            |                                        | Values |      |    | Note /         |

|-------------------------------------------------------------------------|-------------------|----------------------------------------|--------|------|----|----------------|

|                                                                         |                   | Min.                                   | Тур.   | Max. |    | Test Condition |

| Slave select output SELO<br>active to first SCLKOUT<br>transmit edge    | t <sub>1</sub> CC | t <sub>SYS</sub> -<br>10 <sup>1)</sup> | -      | -    | ns |                |

| Slave select output SELO<br>inactive after last<br>SCLKOUT receive edge | t <sub>2</sub> CC | t <sub>SYS</sub> -<br>9 <sup>1)</sup>  | -      | -    | ns |                |

| Data output DOUT valid time                                             | t <sub>3</sub> CC | -7                                     | -      | 11   | ns |                |

| Receive data input setup time to SCLKOUT receive edge                   | t <sub>4</sub> SR | 40                                     | -      | -    | ns |                |

| Data input DX0 hold time<br>from SCLKOUT receive<br>edge                | t <sub>5</sub> SR | -5                                     | -      | -    | ns |                |

1)  $t_{SYS} = 1 / f_{SYS}$

**Table 36** is valid under the following conditions:  $C_L = 20 \text{ pF}$ ; *SSC*= slave; voltage\_range= upper

### Table 36 USIC SSC Slave Mode Timing for Upper Voltage Range

|                                                                                   |                           |        | -    | -    | -    |                |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|                                                                                   |                           | Min.   | Тур. | Max. | -    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

#### Table 36 USIC SSC Slave Mode Timing for Upper Voltage Range (cont'd)

| Parameter                                                                      | Symbol                    |      | Values | S    | Unit | Note /<br>Test Condition |

|--------------------------------------------------------------------------------|---------------------------|------|--------|------|------|--------------------------|

|                                                                                |                           | Min. | Тур.   | Max. |      |                          |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>13</sub> SR | 5    | -      | -    | ns   |                          |

| Data output DOUT valid time                                                    | <i>t</i> <sub>14</sub> CC | 7    | -      | 33   | ns   |                          |

These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

**Table 37** is valid under the following conditions:  $C_L = 20 \text{ pF}$ ; *SSC*= slave ; voltage\_range= lower

| Parameter                                                                         | Symbol                    |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------------------------------|---------------------------|------|--------|------|------|----------------|

|                                                                                   |                           | Min. | Тур.   | Max. | 1    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7    | -      | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7    | -      | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7    | -      | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5    | -      | -    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 8    | -      | 41   | ns   |                |

#### Table 37 USIC SSC Slave Mode Timing for Lower Voltage Range

These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

Figure 26 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.