Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | HC08                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 8MHz                                                          |

| Connectivity               | -                                                             |

| Peripherals                | LVR, POR, PWM                                                 |

| Number of I/O              | 18                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                  |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 128 x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                   |

| Data Converters            | A/D 7x8b                                                      |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                |

| Supplier Device Package    | 20-SOIC                                                       |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908lb8cdwe |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 15.5.1                                                                                                                                                                                                                 | Fault Condition Input Pin                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 15.5.1.1                                                                                                                                                                                                               | Automatic Mode                                                                                                                                                                                                                                                                                                                                                                                           | 150                                                                                                   |

| 15.5.1.2                                                                                                                                                                                                               | Manual Mode                                                                                                                                                                                                                                                                                                                                                                                              | 151                                                                                                   |

| 15.5.2                                                                                                                                                                                                                 | Software Output Disable                                                                                                                                                                                                                                                                                                                                                                                  | 151                                                                                                   |

| 15.6 Initi                                                                                                                                                                                                             | alization and the PWMEN Bit                                                                                                                                                                                                                                                                                                                                                                              | 152                                                                                                   |

| 15.7 PW                                                                                                                                                                                                                | M Operation in Low-Power Modes                                                                                                                                                                                                                                                                                                                                                                           | 152                                                                                                   |

| 15.7.1                                                                                                                                                                                                                 | Wait Mode                                                                                                                                                                                                                                                                                                                                                                                                | 152                                                                                                   |

| 15.7.2                                                                                                                                                                                                                 | Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                | 153                                                                                                   |

| 15.8 Coi                                                                                                                                                                                                               | ntrol Logic Block                                                                                                                                                                                                                                                                                                                                                                                        | 153                                                                                                   |

| 15.8.1                                                                                                                                                                                                                 | PWM Counter Registers                                                                                                                                                                                                                                                                                                                                                                                    | 153                                                                                                   |

| 15.8.2                                                                                                                                                                                                                 | PWM Counter Modulo Registers                                                                                                                                                                                                                                                                                                                                                                             | 153                                                                                                   |

| 15.8.3                                                                                                                                                                                                                 | PWMx Value Registers                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |

| 15.8.4                                                                                                                                                                                                                 | PWM Control Register 1                                                                                                                                                                                                                                                                                                                                                                                   | 155                                                                                                   |

| 15.8.5                                                                                                                                                                                                                 | PWM Control Register 2                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 15.8.6                                                                                                                                                                                                                 | PWM Disable Mapping Write-Once Register                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                       |

| 15.8.7                                                                                                                                                                                                                 | Fault Control Register                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                       |

| 15.8.8                                                                                                                                                                                                                 | Fault Status Register                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

| 15.8.9                                                                                                                                                                                                                 | Fault Control Register 2                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 15.9 PW                                                                                                                                                                                                                | M Glossary                                                                                                                                                                                                                                                                                                                                                                                               | 160                                                                                                   |

|                                                                                                                                                                                                                        | Chapter 16                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|                                                                                                                                                                                                                        | Chapter 16                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|                                                                                                                                                                                                                        | Resets and Interrupts                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                       |

|                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |

|                                                                                                                                                                                                                        | oduction                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |

| 16.2 Res                                                                                                                                                                                                               | sets                                                                                                                                                                                                                                                                                                                                                                                                     | 163                                                                                                   |

| 16.2 Res                                                                                                                                                                                                               | setsEffects                                                                                                                                                                                                                                                                                                                                                                                              | 163<br>163                                                                                            |

| 16.2 Res<br>16.2.1<br>16.2.2                                                                                                                                                                                           | sets                                                                                                                                                                                                                                                                                                                                                                                                     | 163<br>163<br>163                                                                                     |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3                                                                                                                                                                                 | sets Effects External Reset Internal Reset                                                                                                                                                                                                                                                                                                                                                               | 163<br>163<br>163<br>163                                                                              |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1                                                                                                                                                                     | Sets Effects External Reset Internal Reset Power-On Reset (POR)                                                                                                                                                                                                                                                                                                                                          | 163<br>163<br>163<br>163                                                                              |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2                                                                                                                                                         | Sets  Effects  External Reset  Internal Reset  Power-On Reset (POR)  Computer Operating Properly (COP) Reset                                                                                                                                                                                                                                                                                             | 163<br>163<br>163<br>163<br>163<br>164                                                                |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3                                                                                                                                             | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset                                                                                                                                                                                                                                                                       | 163<br>163<br>163<br>163<br>163<br>164<br>164                                                         |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4                                                                                                                                 | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset                                                                                                                                                                                                                                                  | 163<br>163<br>163<br>163<br>164<br>164<br>164                                                         |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5                                                                                                                     | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset                                                                                                                                                                                                                            | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>164                                                  |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4                                                                                                           | Effects External Reset Internal Reset. Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register.                                                                                                                                                                    | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>164<br>165                                           |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte                                                                                              | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register.                                                                                                                                                                     | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>164<br>165                                           |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte                                                                                              | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register. errupts Effects                                                                                                                                                     | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166                                           |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte                                                                                              | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register. errupts Effects Sources                                                                                                                                             | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>166                                    |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte<br>16.3.1<br>16.3.2<br>16.3.2.1                                                              | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register. errupts Effects Sources Software Interrupt (SWI) Instruction                                                                                                        | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>167<br>169                             |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte<br>16.3.1<br>16.3.2<br>16.3.2.1<br>16.3.2.2                                                            | Effects External Reset Internal Reset. Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register. errupts Effects Sources Software Interrupt (SWI) Instruction Break Interrupt                                                                                       | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>166<br>167<br>169                      |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte<br>16.3.1<br>16.3.2<br>16.3.2.1<br>16.3.2.3                                                  | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register. errupts Effects Sources Software Interrupt (SWI) Instruction Break Interrupt IRQ Pin                                                                                | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>167<br>169<br>170                      |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.5<br>16.2.4<br>16.3 Inte<br>16.3.1<br>16.3.2<br>16.3.2.1<br>16.3.2.1<br>16.3.2.2                                                  | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register errupts Effects Sources Software Interrupt (SWI) Instruction Break Interrupt IRQ Pin Timer Interface Module (TIM)                                                    | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>167<br>169<br>170<br>170               |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte<br>16.3.1<br>16.3.2<br>16.3.2.1<br>16.3.2.1<br>16.3.2.2<br>16.3.2.3<br>16.3.2.4<br>16.3.2.5  | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register.  errupts Effects Sources Software Interrupt (SWI) Instruction Break Interrupt IRQ Pin Timer Interface Module (TIM) KBD0-KBD6 Pins                                   | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>167<br>169<br>170<br>170               |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3.1<br>16.3.2<br>16.3.2.1<br>16.3.2.1<br>16.3.2.2<br>16.3.2.3<br>16.3.2.3<br>16.3.2.4<br>16.3.2.5<br>16.3.2.6 | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register.  errupts Effects Sources Software Interrupt (SWI) Instruction Break Interrupt IRQ Pin Timer Interface Module (TIM) KBD0-KBD6 Pins Analog-to-Digital Converter (ADC) | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>167<br>169<br>170<br>170<br>170        |

| 16.2 Res<br>16.2.1<br>16.2.2<br>16.2.3<br>16.2.3.1<br>16.2.3.2<br>16.2.3.3<br>16.2.3.4<br>16.2.3.5<br>16.2.4<br>16.3 Inte<br>16.3.1<br>16.3.2<br>16.3.2.1<br>16.3.2.1<br>16.3.2.2<br>16.3.2.3<br>16.3.2.4<br>16.3.2.5  | Effects External Reset Internal Reset Power-On Reset (POR) Computer Operating Properly (COP) Reset Low-Voltage Inhibit (LVI) Reset Illegal Opcode Reset Illegal Address Reset System Integration Module (SIM) Reset Status Register.  errupts Effects Sources Software Interrupt (SWI) Instruction Break Interrupt IRQ Pin Timer Interface Module (TIM) KBD0-KBD6 Pins                                   | 163<br>163<br>163<br>163<br>164<br>164<br>164<br>165<br>166<br>167<br>169<br>170<br>170<br>170<br>170 |

## 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

## 6.3.7 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register 1 (CONFIG1). See Chapter 5 Configuration Register (CONFIG).

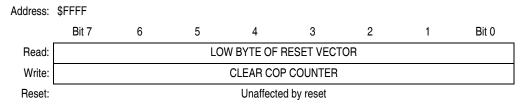

# 6.4 COP Control Register

The COP control register (COPCTL) is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

Figure 6-2. COP Control Register (COPCTL)

# 6.5 Interrupts

The COP does not generate CPU interrupt requests.

## 6.6 Monitor Mode

The COP is disabled in monitor mode when  $V_{TST}$  is present on the  $\overline{IRQ}$  pin.

#### 6.7 Low-Power Modes

The WAIT and STOP instructions put the microcontroller unit (MCU) in low power-consumption standby modes.

## 6.7.1 Wait Mode

The COP remains active during wait mode. If COP is enabled, a reset will occur at COP timeout.

#### 6.7.2 Stop Mode

Stop mode turns off the BUSCLKX4 input to the COP and clears the SIM counter. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

To prevent inadvertently turning off the COP with a STOP instruction, a configuration option is available that disables the STOP instruction. When the STOP bit in the configuration register has the STOP instruction disabled, execution of a STOP instruction results in an illegal opcode reset.

Table 7-2. Opcode Map

|            | Bit Mani             | pulation            | Branch             |                    |                     | Read-Mo             | dify-Write          |                    |                    | Cor                | itrol             |                   |                   |                   | Register          | /Memory           |                   |                   |                  |

|------------|----------------------|---------------------|--------------------|--------------------|---------------------|---------------------|---------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                  | DIR                 | REL                | DIR                | INH                 | INH                 | IX1                 | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                  | 3                  | 4                   | 5                   | 6                   | 9E6                | 7                  | 8                  | 9                 | A                 | В                 | С                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR | 4<br>BSET0<br>2 DIR | 3<br>BRA<br>2 REL  | 4<br>NEG<br>2 DIR  | 1<br>NEGA<br>1 INH  | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1   | 5<br>NEG<br>3 SP1  | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  | 3<br>BGE<br>2 REL | 2<br>SUB<br>2 IMM | 3<br>SUB<br>2 DIR | SUB<br>3 EXT      | 4<br>SUB<br>3 IX2 | 5<br>SUB<br>4 SP2 | 3<br>SUB<br>2 IX1 | 4<br>SUB<br>3 SP1 | 2<br>SUB<br>1 IX |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR | CBEQA<br>3 IMM      | CBEQX<br>3 IMM      | 5<br>CBEQ<br>3 IX1+ | 6<br>CBEQ<br>4 SP1 | 4<br>CBEQ<br>2 IX+ | 4<br>RTS<br>1 INH  |                   | 2<br>CMP<br>2 IMM | 3<br>CMP<br>2 DIR | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR | 4<br>BSET1<br>2 DIR | 3<br>BHI<br>2 REL  |                    | 5<br>MUL<br>1 INH   | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH   |                    | 2<br>DAA<br>1 INH  |                    |                   | SBC<br>2 IMM      |                   | 4<br>SBC<br>3 EXT | 4<br>SBC<br>3 IX2 | 5<br>SBC<br>4 SP2 | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | SBC<br>1 IX      |

| 3          | 5<br>BRCLR1<br>3 DIR | 4<br>BCLR1<br>2 DIR | 3<br>BLS<br>2 REL  | COM<br>2 DIR       | 1<br>COMA<br>1 INH  | COMX<br>1 INH       | 4<br>COM<br>2 IX1   | 5<br>COM<br>3 SP1  | COM<br>1 IX        | 9<br>SWI<br>1 INH  |                   | CPX<br>2 IMM      |                   |                   |                   |                   | 3<br>CPX<br>2 IX1 | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR | BSET2<br>2 DIR      | BCC<br>2 REL       |                    | 1<br>LSRA<br>1 INH  | 1<br>LSRX<br>1 INH  | 4<br>LSR<br>2 IX1   | 5<br>LSR<br>3 SP1  | 3<br>LSR<br>1 IX   | 2<br>TAP<br>1 INH  |                   | 2<br>AND<br>2 IMM |                   | 4<br>AND<br>3 EXT | 4<br>AND<br>3 IX2 |                   | 3<br>AND<br>2 IX1 | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR | 4<br>BCLR2<br>2 DIR | 3<br>BCS<br>2 REL  |                    | 3<br>LDHX<br>3 IMM  | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM  |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH | BIT<br>2 IMM      |                   | 4<br>BIT<br>3 EXT | 4<br>BIT<br>3 IX2 | 5<br>BIT<br>4 SP2 | 3<br>BIT<br>2 IX1 | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          |                      | BSET3<br>2 DIR      | 3<br>BNE<br>2 REL  |                    | 1<br>RORA<br>1 INH  | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1   | 5<br>ROR<br>3 SP1  | 3<br>ROR<br>1 IX   | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM |                   |                   |                   |                   | 3<br>LDA<br>2 IX1 | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          |                      | 2 DIR               | 3<br>BEQ<br>2 REL  |                    | 1<br>ASRA<br>1 INH  |                     | 4<br>ASR<br>2 IX1   | 5<br>ASR<br>3 SP1  | 3<br>ASR<br>1 IX   | 2<br>PSHA<br>1 INH |                   | AIS<br>2 IMM      |                   | 4<br>STA<br>3 EXT |                   |                   | 3<br>STA<br>2 IX1 | 4<br>STA<br>3 SP1 | STA<br>1 IX      |

| 8          |                      | BSET4<br>2 DIR      | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH  | 1<br>LSLX<br>1 INH  | 4<br>LSL<br>2 IX1   | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      |                   |                   | 4<br>EOR<br>3 IX2 |                   | 3<br>EOR<br>2 IX1 | 4<br>EOR<br>3 SP1 | EOR<br>1 IX      |

| 9          | _                    | 2 DIR               |                    | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH  | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1   | 5<br>ROL<br>3 SP1  | 3<br>ROL<br>1 IX   | PSHX<br>1 INH      |                   | ADC<br>2 IMM      |                   | 4<br>ADC<br>3 EXT | 4<br>ADC<br>3 IX2 | 5<br>ADC<br>4 SP2 |                   | 4<br>ADC<br>3 SP1 | ADC<br>1 IX      |

| A          | 5<br>BRSET5<br>3 DIR | 4<br>BSET5<br>2 DIR |                    | 4<br>DEC<br>2 DIR  | DECA<br>1 INH       |                     | 4<br>DEC<br>2 IX1   |                    | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH |                   | ORA<br>2 IMM      |                   | 4<br>ORA<br>3 EXT | _                 | _                 | 3<br>ORA<br>2 IX1 | 4<br>ORA<br>3 SP1 | ORA<br>1 IX      |

| В          | 5<br>BRCLR5<br>3 DIR | 2 DIR               |                    | 5<br>DBNZ<br>3 DIR | 3<br>DBNZA<br>2 INH | 3<br>DBNZX<br>2 INH | 5<br>DBNZ<br>3 IX1  |                    | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM |                   |                   | 4<br>ADD<br>3 IX2 | 5<br>ADD<br>4 SP2 |                   | 4<br>ADD<br>3 SP1 |                  |

| С          | BRSET6<br>3 DIR      | BSET6<br>2 DIR      |                    | INC<br>2 DIR       | 1<br>INCA<br>1 INH  | 1<br>INCX<br>1 INH  | 4<br>INC<br>2 IX1   | 5<br>INC<br>3 SP1  | INC<br>1 IX        | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR |                   | 4<br>JMP<br>3 IX2 |                   | 3<br>JMP<br>2 IX1 |                   | JMP<br>1 IX      |

| D          |                      | 2 DIR               |                    | 3<br>TST<br>2 DIR  | 1<br>TSTA<br>1 INH  |                     | 3<br>TST<br>2 IX1   | 4<br>TST<br>3 SP1  | 2<br>TST<br>1 IX   |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL |                   |                   |                   |                   | 5<br>JSR<br>2 IX1 |                   | 4<br>JSR<br>1 IX |

| E          | 5<br>BRSET7<br>3 DIR | 4<br>BSET7<br>2 DIR | 3<br>BIL<br>2 REL  |                    | 5<br>MOV<br>3 DD    | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD   |                    | 4<br>MOV<br>2 IX+D | STOP<br>1 INH      | *                 | 2<br>LDX<br>2 IMM |                   | 4<br>LDX<br>3 EXT |                   | 5<br>LDX<br>4 SP2 | 3<br>LDX<br>2 IX1 | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR | BCLR7<br>2 DIR      | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH  | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1   | 4<br>CLR<br>3 SP1  | CLR<br>1 IX        | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | STX<br>3 SP1      | STX<br>1 IX      |

INH Inherent IMM Immediate DIR Direct EXT Extended

REL Relative IX Indexed, No Offset IX1 Indexed, 8-Bit Offset IX2 Indexed, 16-Bit Offset

DD Direct-Direct IMD Immediate-Direct IX+D Indexed-Direct DIX+ Direct-Indexed \*Pre-byte for stack pointer indexed instructions

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment IX1+ Indexed, 1-Byte Offset with Post Increment

MSB LSB Low Byte of Opcode in Hexadecimal 0

High Byte of Opcode in Hexadecimal

5 Cycles

BRSET0 Opcode Mnemonic

3 DIR Number of Bytes / Addressing Mode

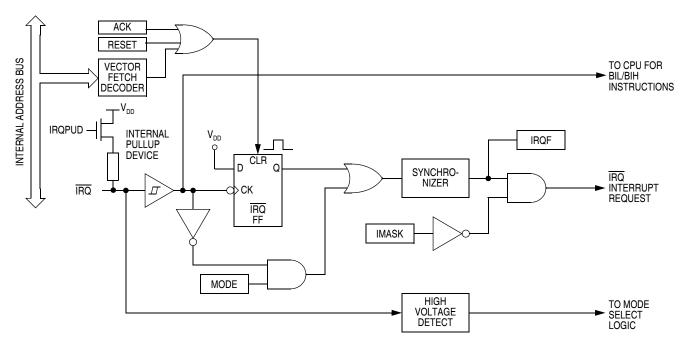

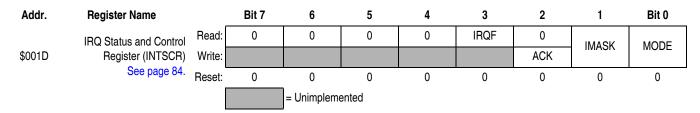

#### **External Interrupt (IRQ)**

Figure 8-1. IRQ Module Block Diagram

When an interrupt pin is both falling-edge and low-level triggered, the interrupt remains set until both of these events occur:

- Vector fetch or software clear

- Return of the interrupt pin to logic 1

The vector fetch or software clear may occur before or after the interrupt pin returns to logic 1. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

When set, the IMASK bit in the INTSCR masks all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

# **NOTE**The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests.

Figure 8-2. IRQ I/O Register Summary

# 8.4 IRQ Pin

A logic 0 on the  $\overline{IRQ}$  pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

MC68HC908LB8 Data Sheet, Rev. 1

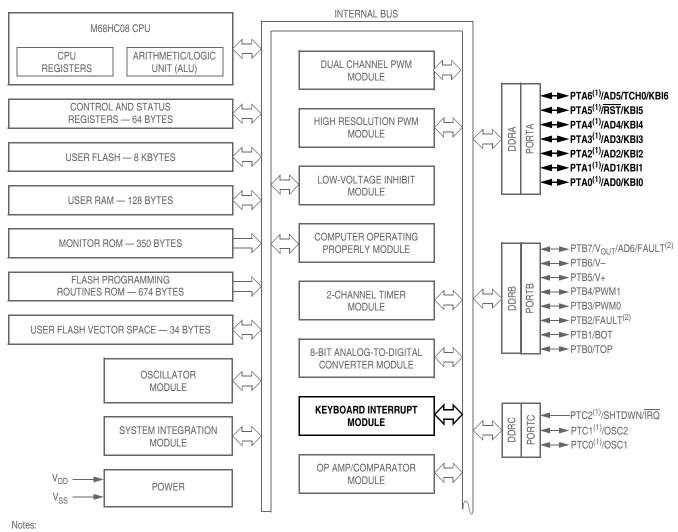

# **Chapter 9 Keyboard Interrupt Module (KBI)**

## 9.1 Introduction

The keyboard interrupt module (KBI) provides seven independently maskable external interrupts which are accessible via PTA0-PTA6. When a port pin is enabled for keyboard interrupt function, an internal pullup device is also enabled on the pin.

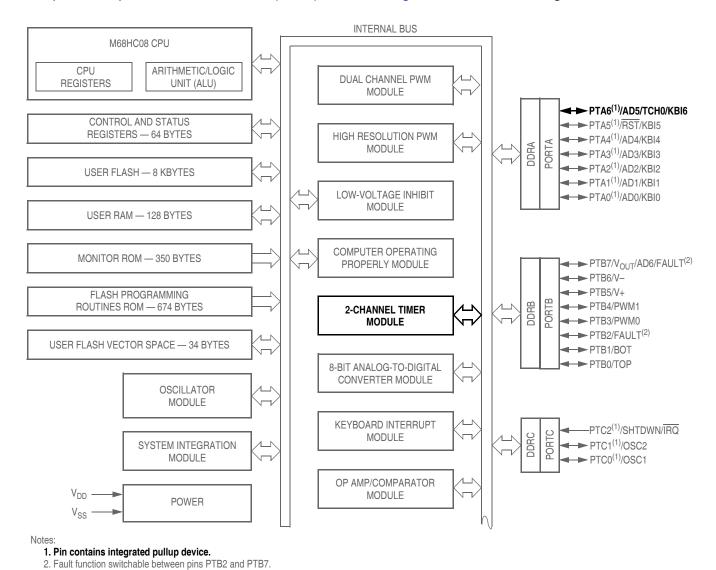

1. Pin contains integrated pullup device.

2. Fault function switchable between pins PTB2 and PTB7.

Figure 9-1. Block Diagram Highlighting KBI Block and Pins

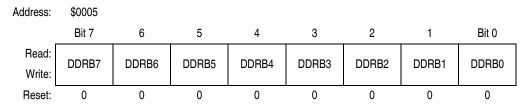

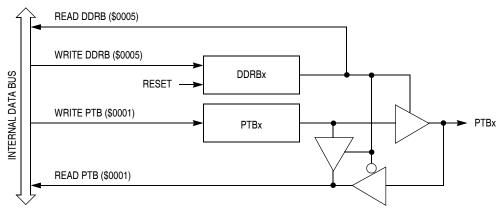

## 14.3.2 Data Direction Register B

Data direction register B (DDRB) determines whether each port B pin is an input or an output. Writing a 1 to a DDRB bit enables the output buffer for the corresponding port B pin; a 0 disables the output buffer.

Figure 14-7. Data Direction Register B (DDRB)

### DDRB7-DDRB0 — Data Direction Register B Bits

These read/write bits control port B data direction. Reset clears DDRB7–DDRB0, configuring all port B pins as inputs.

- 1 = Corresponding port B pin configured as output

- 0 = Corresponding port B pin configured as input

#### **NOTE**

Avoid glitches on port B pins by writing to the port B data register before changing data direction register B bits from 0 to 1.

Figure 14-8 shows the port B I/O logic.

Figure 14-8. Port B I/O Circuit

When bit DDRBx is a 1, reading address \$0001 reads the PTBx data latch. When bit DDRBx is a 0, reading address \$0001 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 14-2 summarizes the operation of the port B pins.

| DDRB<br>Bit | PTB<br>Bit       | to being                   |             | Accesses<br>to PTB |                          |  |  |

|-------------|------------------|----------------------------|-------------|--------------------|--------------------------|--|--|

| Dit.        |                  | IWIOGE                     | Read/Write  | Read               | Write                    |  |  |

| 0           | X <sup>(1)</sup> | Input, Hi-Z <sup>(2)</sup> | DDRB7-DDRB0 | Pin                | PTB7-PTB0 <sup>(3)</sup> |  |  |

| 1           | Х                | Output                     | DDRB7-DDRB0 | PTB7-PTB0          | PTB7-PTB0                |  |  |

#### NOTES:

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

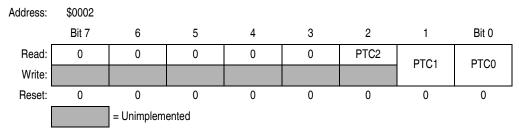

#### 14.4 Port C

Port C is a 3-bit, general-purpose bidirectional I/O port. Port C shares its pins with the oscillator (OSC) module, high resolution PWM (HRP), and the external interrupt module (IRQ). See Table 1-1 . Pin Functions for a description of the priority of these functions. Port C also has software configurable pullup devices if configured as an input port.

#### NOTE

PTC2 is input only.

When the  $\overline{\text{IRQ}}$  function is enabled in the configuration register 2 (CONFIG2), bit 2 of the port C data register (PTC) will always read 0. In this case, the BIH and BIL instructions can be used to read the logic level on the PTC2 pin. When the  $\overline{\text{IRQ}}$  function is disabled, these instructions will behave as if the PTC2 pin is a logic 1. However, reading bit 2 of PTC will read the actual logic level on the pin.

# 14.4.1 Port C Data Register

The port C data register (PTC) contains a data latch for each of the seven port C pins.

Figure 14-9. Port C Data Register (PTC)

#### PTC2-PTC0 — Port C Data Bits

These read/write bits are software-programmable. Data direction of each port C pin is under the control of the corresponding bit in data direction register C. Reset has no effect on port C data.

#### 14.4.2 Data Direction Register C

Data direction register C (DDRC) determines whether each port C pin is an input or an output. Writing a 1 to a DDRC bit enables the output buffer for the corresponding port C pin; a 0 disables the output buffer.

MC68HC908LB8 Data Sheet, Rev. 1

#### **Pulse Width Modulator with Fault Input (PWM)**

direction register. In order to read the states of the pins, the data direction register bit must be a 0.

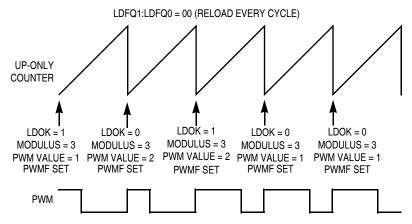

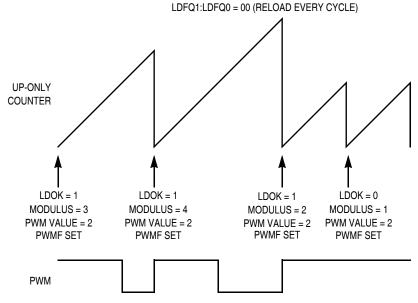

Figure 15-7. Edge-Aligned PWM Value Loading

Figure 15-8. Edge-Aligned Modulus Loading

#### 15.4.2 PWM Data Overflow and Underflow Conditions

The PWM value registers are 16-bit registers. Although the counter is only 12 bits, the user may write a 16-bit signed value to a PWM value register. As shown in Figure 15-4, if the PWM value is less than or equal to zero, the PWM will be inactive for the entire period. Conversely, if the PWM value is greater than or equal to the timer modulus, the PWM will be active for the entire period. Refer to Table 15-3.

Clearing the PWMEN bit before entering wait mode will reduce power consumption in wait mode because the counter, prescaler divider, and LDFQ divider will no longer be clocked. In addition, power will be reduced because the PWMs will no longer toggle.

## **15.7.2 Stop Mode**

When the microcontroller is put into stop mode via the STOP instruction, the PWM will stop functioning. The PWM0 and PWM1 outputs are set to logic 0. The STOP instruction does not affect the register conditions or the state of the PWM counters. When the MCU exits stop mode after an external interrupt the PWM resumes operation.

# 15.8 Control Logic Block

This subsection provides a description of the control logic block.

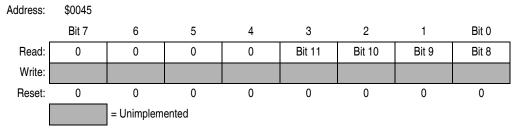

# 15.8.1 PWM Counter Registers

The PWM counter registers (PCNTH and PCNTL) display the 12-bit up-only counter. When the high byte of the counter is read, the lower byte is latched. PCNTL will hold this latched value until it is read. See Figure 15-14 and Figure 15-15.

Figure 15-14. PWM Counter Register High (PCNTH)

Figure 15-15. PWM Counter Register Low (PCNTL)

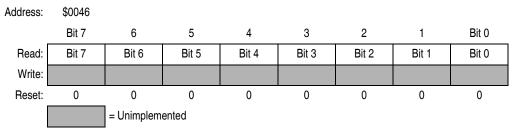

# 15.8.2 PWM Counter Modulo Registers

The PWM counter modulus registers (PMODH and PMODL) hold a 12-bit unsigned number that determines the maximum count for the up-only counter. The PWM period will equal the modulus. See Figure 15-16 and Figure 15-17.

Figure 17-2. SIM I/O Register Summary

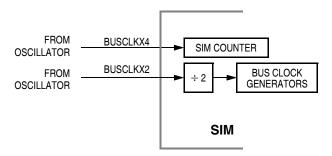

## 17.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 17-3.

Figure 17-3. SIM Clock Signals

# 17.2.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

# 17.2.2 Clock Start-Up from POR

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The RST pin is driven low by the SIM during this entire period. The IBUS clocks start upon completion of the time out.

# 17.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 17.6.2 Stop Mode.

MC68HC908LB8 Data Sheet, Rev. 1

#### System Integration Module (SIM)

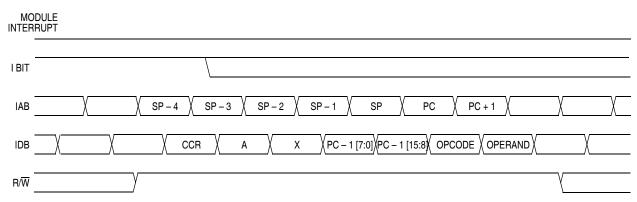

Figure 17-9. Interrupt Recovery Timing

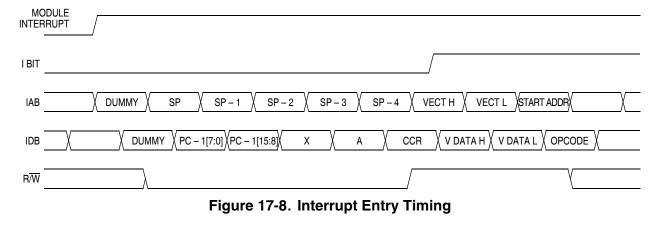

Interrupts are latched, and arbitration is performed in the SIM at the start of interrupt processing. The arbitration result is a constant that the CPU uses to determine which vector to fetch. Once an interrupt is latched by the SIM, no other interrupt can take precedence, regardless of priority, until the latched interrupt is serviced (or the I bit is cleared). See Figure 17-10.

#### 17.5.1.1 Hardware Interrupts

A hardware interrupt does not stop the current instruction. Processing of a hardware interrupt begins after completion of the current instruction. When the current instruction is complete, the SIM checks all pending hardware interrupts. If interrupts are not masked (I bit clear in the condition code register) and if the corresponding interrupt enable bit is set, the SIM proceeds with interrupt processing; otherwise, the next instruction is fetched and executed.

If more than one interrupt is pending at the end of an instruction execution, the highest priority interrupt is serviced first. Figure 17-11 demonstrates what happens when two interrupts are pending. If an interrupt is pending upon exit from the original interrupt service routine, the pending interrupt is serviced before the LDA instruction is executed.

#### **System Integration Module (SIM)**

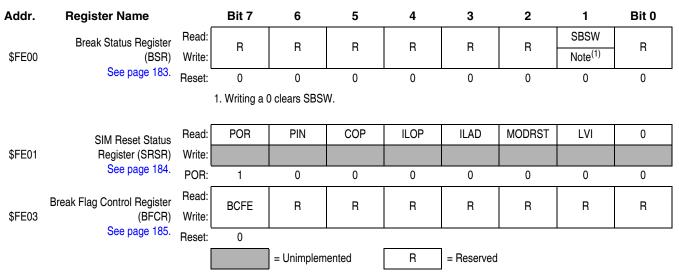

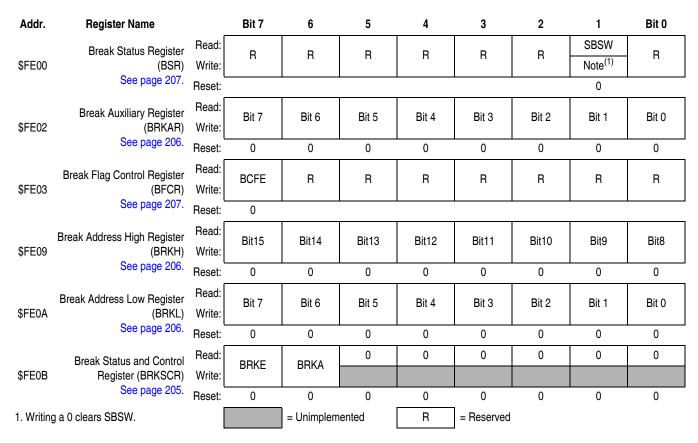

### SBSW — SIM Break Stop/Wait

This status bit is useful in applications requiring a return to wait mode after exiting from a break interrupt. Clear SBSW by writing a 0 to it. Reset clears SBSW.

- 1 = Wait mode was exited by break interrupt.

- 0 = Wait mode was not exited by break interrupt.

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it.

## 17.7.2 SIM Reset Status Register

This register contains six flags that show the source of the last reset provided all previous reset status bits have been cleared. Clear the SIM reset status register by reading it. A power-on reset sets the POR bit and clears all other bits in the register.

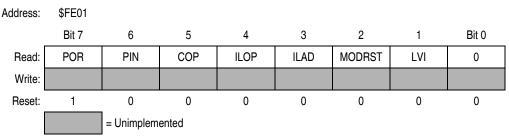

Figure 17-18. SIM Reset Status Register (SRSR)

#### POR — Power-On Reset Bit

- 1 = Last reset caused by POR circuit

- 0 = Read of SRSR

#### PIN — External Reset Bit

- 1 = Last reset caused by external reset pin (RST)

- 0 = POR or read of SRSR

### **COP** — Computer Operating Properly Reset Bit

- 1 = Last reset caused by COP counter

- 0 = POR or read of SRSR

#### ILOP — Illegal Opcode Reset Bit

- 1 = Last reset caused by an illegal opcode

- 0 = POR or read of SRSR

#### ILAD — Illegal Address Reset Bit (opcode fetches only)

- 1 = Last reset caused by an opcode fetch from an illegal address

- 0 = POR or read of SRSR

## **MODRST** — Monitor Mode Entry Module Reset Bit

- 1 = Last reset caused by monitor mode entry when vector locations \$FFFE and \$FFFF are \$FF after POR while  $\overline{IRQ} = V_{DD}$

- 0 = POR or read of SRSR

## LVI — Low-Voltage Inhibit Reset Bit

- 1 = Last reset caused by the LVI circuit

- 0 = POR or read of SRSR

# **Chapter 18 Timer Interface Module (TIM)**

## 18.1 Introduction

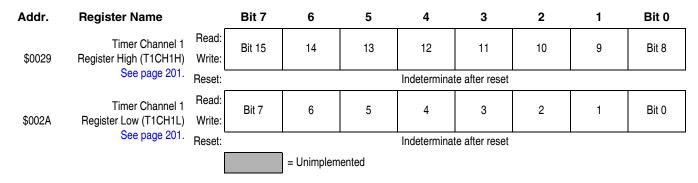

This section describes the timer interface (TIM) module. The TIM is a two-channel timer (only one of the channels is connected to an input/output pin) that provides a timing reference with input capture, output compare, and pulse-width-modulation (PWM) functions. Figure 18-2 is a block diagram of the TIM.

Figure 18-1. Block Diagram Highlighting TIM Block and Pins

#### **Timer Interface Module (TIM)**

Figure 18-3. TIM I/O Register Summary (Sheet 2 of 2)

#### 18.3.1 TIM Counter Prescaler

The TIM clock source can be one of the seven prescaler outputs. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register select the TIM clock source.

# 18.3.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter into the TIM channel registers, TCHxH:TCHxL. The polarity of the active edge is programmable. Input captures can generate TIM CPU interrupt requests.

# 18.3.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM can set, clear, or toggle the channel pin. Output compares can generate TIM CPU interrupt requests.

#### 18.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 18.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

#### **Timer Interface Module (TIM)**

The value in the TIM counter modulo registers and the selected prescaler output determines the frequency of the PWM output. The frequency of an 8-bit PWM signal is variable in 256 increments. Writing \$00FF (255) to the TIM counter modulo registers produces a PWM period of 256 times the internal bus clock period if the prescaler select value is \$000. See 18.8.1 TIM Status and Control Register.

The value in the TIM channel registers determines the pulse width of the PWM output. The pulse width of an 8-bit PWM signal is variable in 256 increments. Writing \$0080 (128) to the TIM channel registers produces a duty cycle of 128/256 or 50%.

## 18.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 18.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIM overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the

new value in the output compare interrupt routine. The output compare interrupt occurs at the end

of the current pulse. The interrupt routine has until the end of the PWM period to write the new

value.

- When changing to a longer pulse width, enable TIM overflow interrupts and write the new value in the TIM overflow interrupt routine. The TIM overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

## 18.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the TCH0 pin. The TIM channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIM channel 0 status and control register (TSC0) links channel 0 and channel 1. The TIM channel 0 registers initially control the pulse width on the TCH0 pin. Writing to the TIM channel 1 registers enables the TIM channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIM channel registers (0 or 1) that control the pulse width are the ones written to last. TSC0 controls and monitors the buffered PWM function, and TIM channel 1 status and control register (TSC1) is unused.

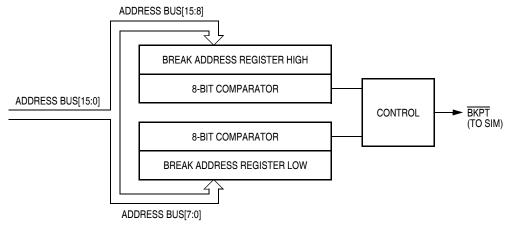

#### **Development Support**

Figure 19-1. Break Module Block Diagram

Figure 19-2. Break I/O Register Summary

## 19.2.1.1 Flag Protection During Break Interrupts

The system integration module (SIM) controls whether or not module status bits can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See 17.7.3 Break Flag Control Register and the **Break Interrupts** subsection for each module.

MC68HC908LB8 Data Sheet, Rev. 1

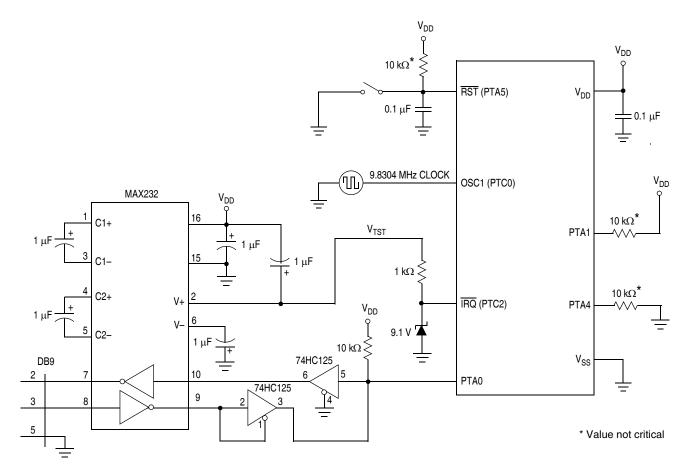

Figure 19-10. Normal Monitor Mode Circuit (External Clock, with High Voltage)

The monitor code has been updated from previous versions of the monitor code to allow enabling the internal oscillator to generate the internal clock. This addition, which is enabled when IRQ is held low out of reset, is intended to support serial communication/programming at 9600 baud in monitor mode by using the internal oscillator, and the internal oscillator user trim value OSCTRIM (FLASH location \$FFC0, if programmed) to generate the desired internal frequency (4.0 MHz). Since this feature is enabled only when IRQ is held low out of reset, it cannot be used when the reset vector is programmed (i.e., the value is not \$FFFF) because entry into monitor mode in this case requires  $V_{TST}$  on  $\overline{IRQ}$ .

Enter monitor mode with pin configuration shown in Figure 19-11 by pulling RST low and then high. The rising edge of RST latches monitor mode. Once monitor mode is latched, the values on the specified pins can change.

Once out of reset, the MCU waits for the host to send eight security bytes (see 19.3.2 Security). After the security bytes, the MCU sends a break signal (10 consecutive 0s) to the host, indicating that it is ready to receive a command.

Freescale Semiconductor 211

MC68HC908LB8 Data Sheet, Rev. 1

A brief description of each monitor mode command is given in Table 19-3 through Table 19-8.

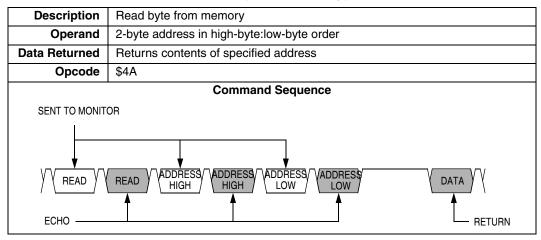

Table 19-3. READ (Read Memory) Command

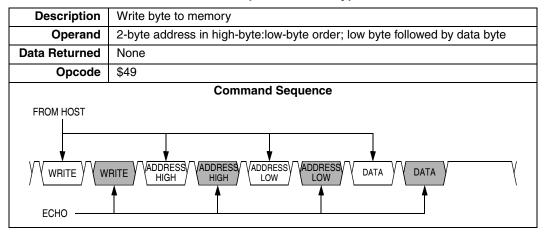

Table 19-4. WRITE (Write Memory) Command

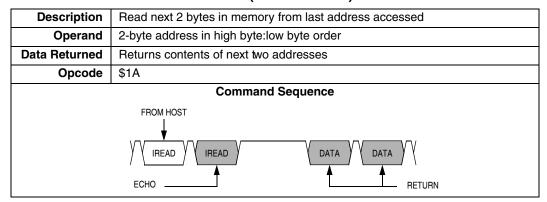

Table 19-5. IREAD (Indexed Read) Command

#### **Electrical Specifications**

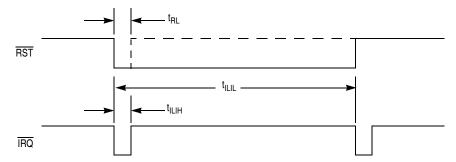

#### NOTES:

- V<sub>SS</sub> = 0 Vdc; timing shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub> unless otherwise noted.

Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

- 3. Minimum pulse width is for guaranteed interrupt. It is possible for a smaller pulse width to be recognized.

Figure 20-1. RST and IRQ Timing

# 20.7 Oscillator Characteristics

| Characteristic                                    | Symbol              | Min  | Тур                | Max  | Unit |

|---------------------------------------------------|---------------------|------|--------------------|------|------|

| Internal oscillator frequency (factory trimmed)   | f <sub>INTCLK</sub> | 15.2 | 16 <sup>(1)</sup>  | 16.8 | MHz  |

| Crystal frequency, XTALCLK                        | foscxclk            | 8    | _                  | 24   | MHz  |

| External RC oscillator frequency, RCCLK           | f <sub>RCCLK</sub>  | 2    | _                  | 12   | MHz  |

| External clock reference frequency <sup>(2)</sup> | foscxclk            | dc   | _                  | 32   | MHz  |

| Crystal load capacitance <sup>(3)</sup>           | CL                  | _    | 20                 | _    | pF   |

| Crystal fixed capacitance <sup>(2)</sup>          | C <sub>1</sub>      | _    | 2 x C <sub>L</sub> | _    | _    |

| Crystal tuning capacitance <sup>(2)</sup>         | C <sub>2</sub>      | _    | 2 x C <sub>L</sub> | _    | _    |

| Feedback bias resistor                            | R <sub>B</sub>      | _    | 10                 | _    | ΜΩ   |

| RC oscillator external resistor                   | R <sub>EXT</sub>    | S    | See Figure 20-     | -2   | _    |

#### NOTES:

- 1. Characterization shows that  $\pm$  3.5% could be achieved from -40 to 85 $^{\circ}$ C.

- 2. No more than 10% duty cycle deviation from 50%.

- 3. Consult crystal vendor data sheet.

# **Chapter 21 Ordering Information and Mechanical Specifications**

# 21.1 Introduction

This section provides ordering information for the MC68HC908GZ8 along with the dimensions for:

- 20-pin small outline intergrated circuit (SOIC) case 751D

- 20-pin plastic dual in-line package (PDIP) case 738

The following figures show the latest package drawings at the time of this publication. To make sure that you have the latest package specifications, contact your local Freescale Semiconductor Sales Office.

# 21.2 MC Order Numbers

Table 21-1. MC Order Numbers

| MC Order<br>Number | Operating<br>Temperature Range | Package              |

|--------------------|--------------------------------|----------------------|

| MC68HC908LB8CDWE   | -40°C to +85°C                 | 20-pin Small outline |

| MC68HC908LB8VDWE   | -40°C to +105°C                | integrated circuit   |

| MC68HC908LB8MDWE   | -40°C to +125°C                | (SOIC)               |

| MC68HC908LB8CPE    | -40°C to +85°C                 | 20-pin Plastic       |

| MC68HC908LB8VPE    | -40°C to +105°C                | dual In-line package |

| MC68HC908LB8MPE    | -40°C to +125°C                | (PDIP)               |

Temperature and package designators:

$C = -40^{\circ}C \text{ to } +85^{\circ}C$

$V = -40^{\circ}C \text{ to } + 105^{\circ}C$

$M = -40^{\circ}C \text{ to } + 125^{\circ}C$

DW = Small outline integrated circuit package (SOIC)

E = Leadfree

P = Plastic dual in-line package (PDIP)