Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |  |  |  |

|----------------------------|-------------------------------------------------------------------------|--|--|--|

| Product Status             | Obsolete                                                                |  |  |  |

| Core Processor             | HC08                                                                    |  |  |  |

| Core Size                  | 8-Bit                                                                   |  |  |  |

| Speed                      | 8MHz                                                                    |  |  |  |

| Connectivity               | -                                                                       |  |  |  |

| Peripherals                | LVR, POR, PWM                                                           |  |  |  |

| Number of I/O              | 18                                                                      |  |  |  |

| Program Memory Size        | 8KB (8K x 8)                                                            |  |  |  |

| Program Memory Type        | FLASH                                                                   |  |  |  |

| EEPROM Size                | -                                                                       |  |  |  |

| RAM Size                   | 128 x 8                                                                 |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                             |  |  |  |

| Data Converters            | A/D 7x8b                                                                |  |  |  |

| Oscillator Type            | Internal                                                                |  |  |  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |  |  |  |

| Mounting Type              | Through Hole                                                            |  |  |  |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |  |  |  |

| Supplier Device Package    | 20-DIP                                                                  |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908lb8mpe |  |  |  |

## **List of Sections**

| Chapter 1  | General Description                                | .17  |

|------------|----------------------------------------------------|------|

| Chapter 2  | Memory                                             | . 25 |

| Chapter 3  | Analog-to-Digital Converter (ADC)                  | . 45 |

| Chapter 4  | Op Amp/Comparator Module                           | .53  |

| Chapter 5  | Configuration Register (CONFIG)                    | .59  |

| Chapter 6  | Computer Operating Properly (COP) Module           | .63  |

| Chapter 7  | Central Processor Unit (CPU)                       | .67  |

| Chapter 8  | External Interrupt (IRQ)                           | .81  |

| Chapter 9  | Keyboard Interrupt Module (KBI)                    | . 85 |

| Chapter 10 | High Resolution PWM (HRP)                          | .91  |

| Chapter 11 | Low-Power Modes                                    | 13   |

| Chapter 12 | Low-Voltage Inhibit (LVI)1                         | 119  |

| Chapter 13 | Oscillator Module (OSC)                            | 23   |

| Chapter 14 | Input/Output (I/O) Ports1                          | 33   |

| Chapter 15 | Pulse Width Modulator with Fault Input (PWM)1      | 41   |

| Chapter 16 | Resets and Interrupts                              | 63   |

| Chapter 17 | System Integration Module (SIM)1                   | 71   |

| Chapter 18 | Timer Interface Module (TIM)                       | 87   |

| Chapter 19 | Development Support                                | 203  |

| Chapter 20 | Electrical Specifications                          | 221  |

| Chapter 21 | Ordering Information and Mechanical Specifications | 231  |

## Chapter 7 Central Processor Unit (CPU)

| 7.1            | Introduction                            | 67 |

|----------------|-----------------------------------------|----|

| 7.2            | Features                                | 67 |

| 7.3            | CPU Registers                           | 67 |

| 7.3.1          | Accumulator                             | 68 |

| 7.3.2          | Index Register                          |    |

| 7.3.3          | Stack Pointer                           |    |

| 7.3.4          | Program Counter                         |    |

| 7.3.5<br>7.4   | Condition Code Register                 |    |

|                | Arithmetic/Logic Unit (ALU)             |    |

| 7.5<br>7.5.1   | Low-Power Modes                         |    |

| 7.5.1<br>7.5.2 | Stop Mode                               |    |

| 7.6            | CPU During Break Interrupts             |    |

| 7.7            | Instruction Set Summary                 |    |

| 7.8            | Opcode Map                              |    |

|                |                                         |    |

|                | Chapter 8                               |    |

|                | External Interrupt (IRQ)                |    |

| 8.1            | Introduction                            |    |

| 8.2            | Features                                |    |

| 8.3            | Functional Description                  |    |

| 8.4            | IRQ Pin                                 |    |

| 8.5            | IRQ Module During Break Interrupts      |    |

| 8.6            | IRQ Status and Control Register         | 83 |

|                | Chapter 9                               |    |

|                | Keyboard Interrupt Module (KBI)         |    |

| 9.1            | Introduction                            | 85 |

| 9.2            | Features                                |    |

| 9.3            | Functional Description                  |    |

| 9.4            | Keyboard Initialization                 |    |

| 9.5            | Low-Power Modes                         | 88 |

| 9.5.1          | Wait Mode                               | 88 |

| 9.5.2          | Stop Mode                               | 88 |

| 9.6            | Keyboard Module During Break Interrupts | 88 |

| 9.7            | I/O Registers                           |    |

| 9.7.1          | Keyboard Status and Control Register    |    |

| 9.7.2          | Keyboard Interrupt Enable Register      | 89 |

|                | Chapter 10                              |    |

|                | High Resolution PWM (HRP)               |    |

| 10.1           | Introduction                            | 91 |

| 10.2           | Features                                |    |

|                |                                         |    |

|                |                                         |    |

#### Memory Bit 7 6 3 2 1 Bit 0 Addr. **Register Name** 5 4 0 0 Read: 0 0 0 0 Data Direction Register C DDRC1 DDRC0 \$0006 (DDRC) Write: See page 139. Reset: 0 0 0 0 0 0 0 0 \$0007 Unimplemented \$000C Read: Port A Input Pullup Enable PTA6PUE PTA5PUE PTA4PUE PTA3PUE PTA2PUE PTA1PUE PTA0PUE \$000D Register (PTAPUE) Write: See page 136. Reset: 0 0 0 0 0 0 0 0 0 0 0 Read: 0 Port C Input Pullup Enable OSC2EN PTCPUE2 PTCPUE1 PTCPUE0 \$000E Register (PTCPUE) Write: See page 140. Reset: 0 0 0 0 0 0 0 0 \$000F Unimplemented \$0019 0 0 0 **KEYF** Keyboard Status Read: 0 0 **IMASKK** MODEK and Control Register Write: **ACKK** \$001A (INTKBSCR) 0 0 0 0 0 0 Reset: 0 0 See page 89. Read: Keyboard Interrupt Enable KBIE4 KBIE3 KBIE6 KBIE5 KBIE2 KBIE1 KBIE0 \$001B Register (INTKBIER) Write: See page 90. Reset: 0 0 0 0 0 0 0 0 Read: 0 0 0 0 **IRQF** 0 IRQ Status and Control **IMASK** MODE ACK \$001D Register (INTSCR) Write: See page 84. Reset: 0 0 0 0 0 0 0 0 Configuration Register 2 Read: 0 0 **IRQPUD IRQEN** OSCOPT0 R OSCOPT1 **RSTEN** (CONFIG2)(1) Write: \$001E See page 60. 0<sup>(2)</sup> 0 0 0 0 0 Reset: 0 1. One-time writable register after each reset. 2. RSTEN reset to 0 by a power-on reset (POR) only. 0 Read: Configuration Register 1 **COPRS** LVIPWRD LVISTOP LVIRSTD **SSREC** STOP COPD (CONFIG1)(1) \$001F Write: See page 61. Reset: 0 0 0 1. One-time writable register after reach reset.

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 8)

R

U = Unaffected

= Reserved

= Unimplemented

= Buffered

Bold

37

Programming tools are available from Freescale Semiconductor. Contact your local Freescale Semiconductor representative for more information.

#### NOTE

A security feature prevents viewing of the FLASH contents. (1)

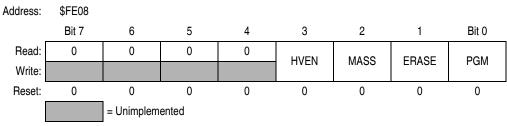

#### 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

Figure 2-3. FLASH Control Register (FLCR)

#### **HVEN** — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can only be set if either PGM = 1 or ERASE = 1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

Setting this read/write bit configures the 8-Kbyte FLASH array for mass erase operation.

- 1 = MASS erase operation selected

- 0 = PAGE erase operation selected

#### **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

#### **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

#### 2.6.2 FLASH Page Erase Operation

Use this step-by-step procedure to erase a page (64 bytes) of FLASH memory to read as logic 1. A page consists of 64 consecutive bytes starting from addresses \$XX00, \$XX40, \$XX80, or \$XXC0. The 34-byte user interrupt vectors area also forms a page. Any FLASH memory page can be erased alone, except for the 34-byte interrupt vectors page, which must be mass erased.

<sup>1.</sup> No security feature is absolutely secure. However, Freescale Semiconductor's strategy is to make reading or copying the FLASH difficult for unauthorized users.

MC68HC908LB8 Data Sheet, Rev. 1

#### **Central Processor Unit (CPU)**

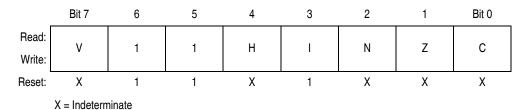

Figure 7-6. Condition Code Register (CCR)

#### V — Overflow Flag

The CPU sets the overflow flag when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow flag.

- 1 = Overflow

- 0 = No overflow

#### H — Half-Carry Flag

The CPU sets the half-carry flag when a carry occurs between accumulator bits 3 and 4 during an add-without-carry (ADD) or add-with-carry (ADC) operation. The half-carry flag is required for binary-coded decimal (BCD) arithmetic operations. The DAA instruction uses the states of the H and C flags to determine the appropriate correction factor.

- 1 = Carry between bits 3 and 4

- 0 = No carry between bits 3 and 4

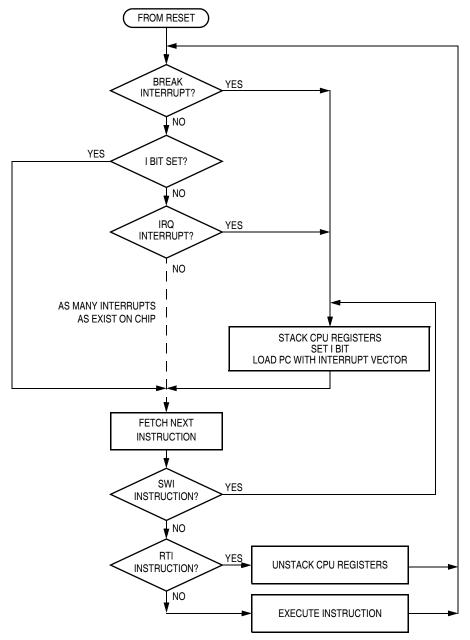

#### I — Interrupt Mask

When the interrupt mask is set, all maskable CPU interrupts are disabled. CPU interrupts are enabled when the interrupt mask is cleared. When a CPU interrupt occurs, the interrupt mask is set automatically after the CPU registers are saved on the stack, but before the interrupt vector is fetched.

- 1 = Interrupts disabled

- 0 = Interrupts enabled

#### NOTE

To maintain M6805 Family compatibility, the upper byte of the index register (H) is not stacked automatically. If the interrupt service routine modifies H, then the user must stack and unstack H using the PSHH and PULH instructions.

After the I bit is cleared, the highest-priority interrupt request is serviced first.

A return-from-interrupt (RTI) instruction pulls the CPU registers from the stack and restores the interrupt mask from the stack. After any reset, the interrupt mask is set and can be cleared only by the clear interrupt mask software instruction (CLI).

#### N — Negative flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

#### Z — Zero flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

- 1 = Zero result

- 0 = Non-zero result

Table 7-1. Instruction Set Summary (Sheet 4 of 7)

| Source<br>Form                                                                                           | Operation                           | Description                                                                                                                                                                 | Effect on CCR |   |   |          |    |   | Address                                             | Opcode                                           | Operand                    | les                                  |

|----------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---|---|----------|----|---|-----------------------------------------------------|--------------------------------------------------|----------------------------|--------------------------------------|

| Form                                                                                                     |                                     | ·                                                                                                                                                                           | ٧             | Н | I | N        | Z  | С | Adc                                                 | Opc                                              | odo                        | Cycles                               |

| DEC opr<br>DECA<br>DECX<br>DEC opr,X<br>DEC ,X<br>DEC opr,SP                                             | Decrement                           | $\begin{array}{c} M \leftarrow (M) - 1 \\ A \leftarrow (A) - 1 \\ X \leftarrow (X) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \\ M \leftarrow (M) - 1 \end{array}$ | t             | _ | _ | <b>‡</b> | ‡  | _ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3A<br>4A<br>5A<br>6A<br>7A<br>9E6A               | dd<br>ff<br>ff             | 4<br>1<br>1<br>4<br>3<br>5           |

| DIV                                                                                                      | Divide                              | A ← (H:A)/(X)<br>H ← Remainder                                                                                                                                              | _             | _ | _ | _        | Į. | ţ | INH                                                 | 52                                               |                            | 7                                    |

| EOR #opr<br>EOR opr<br>EOR opr,X<br>EOR opr,X<br>EOR,X<br>EOR opr,SP<br>EOR opr,SP                       | Exclusive OR M with A               | $A \leftarrow (A \oplus M)$                                                                                                                                                 | 0             | _ | _ | <b>‡</b> | 1  | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A8<br>B8<br>C8<br>D8<br>E8<br>F8<br>9EE8<br>9ED8 |                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| INC opr<br>INCA<br>INCX<br>INC opr,X<br>INC ,X<br>INC opr,SP                                             | Increment                           | $\begin{array}{c} M \leftarrow (M) + 1 \\ A \leftarrow (A) + 1 \\ X \leftarrow (X) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \\ M \leftarrow (M) + 1 \end{array}$ | ţ             | _ | _ | ‡        | 1  | _ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3C<br>4C<br>5C<br>6C<br>7C<br>9E6C               | dd<br>ff<br>ff             | 4<br>1<br>1<br>4<br>3<br>5           |

| JMP opr<br>JMP opr<br>JMP opr,X<br>JMP opr,X<br>JMP ,X                                                   | Jump                                | PC ← Jump Address                                                                                                                                                           | _             | _ | _ | _        | _  | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BC<br>CC<br>DC<br>EC<br>FC                       | dd<br>hh II<br>ee ff<br>ff | 2<br>3<br>4<br>3<br>2                |

| JSR opr<br>JSR opr<br>JSR opr,X<br>JSR opr,X<br>JSR ,X                                                   | Jump to Subroutine                  | PC $\leftarrow$ (PC) + $n$ ( $n$ = 1, 2, or 3)<br>Push (PCL); SP $\leftarrow$ (SP) - 1<br>Push (PCH); SP $\leftarrow$ (SP) - 1<br>PC $\leftarrow$ Unconditional Address     | _             | _ | _ | -        | -  | _ | DIR<br>EXT<br>IX2<br>IX1<br>IX                      | BD<br>CD<br>DD<br>ED<br>FD                       | dd<br>hh II<br>ee ff<br>ff | 4<br>5<br>6<br>5<br>4                |

| LDA #opr<br>LDA opr<br>LDA opr,<br>LDA opr,X<br>LDA opr,X<br>LDA opr,SP<br>LDA opr,SP<br>LDA opr,SP      | Load A from M                       | A ← (M)                                                                                                                                                                     | 0             | _ | _ | ‡        | ‡  | - | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A6<br>B6<br>C6<br>D6<br>E6<br>F6<br>9EE6<br>9ED6 |                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LDHX #opr<br>LDHX opr                                                                                    | Load H:X from M                     | H:X ← (M:M + 1)                                                                                                                                                             | 0             | - | _ | ‡        | 1  | - | IMM<br>DIR                                          | 45<br>55                                         | ii jj<br>dd                | 3<br>4                               |

| LDX #opr<br>LDX opr<br>LDX opr<br>LDX opr,X<br>LDX opr,X<br>LDX ,X<br>LDX ,X<br>LDX opr,SP<br>LDX opr,SP | Load X from M                       | X ← (M)                                                                                                                                                                     | 0             | _ | _ | 1        | 1  | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AE<br>BE<br>CE<br>DE<br>EE<br>FE<br>9EEE<br>9EDE |                            | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| LSL opr<br>LSLA<br>LSLX<br>LSL opr,X<br>LSL ,X<br>LSL opr,SP                                             | Logical Shift Left<br>(Same as ASL) | C ← 0 b0 b7 b0                                                                                                                                                              | 1             | _ | _ | ‡        | 1  | ‡ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff             | 4<br>1<br>1<br>4<br>3<br>5           |

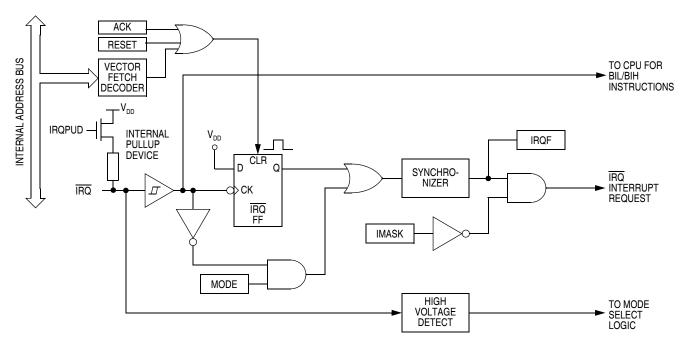

#### **External Interrupt (IRQ)**

Figure 8-1. IRQ Module Block Diagram

When an interrupt pin is both falling-edge and low-level triggered, the interrupt remains set until both of these events occur:

- Vector fetch or software clear

- Return of the interrupt pin to logic 1

The vector fetch or software clear may occur before or after the interrupt pin returns to logic 1. As long as the pin is low, the interrupt request remains pending. A reset will clear the latch and the MODE control bit, thereby clearing the interrupt even if the pin stays low.

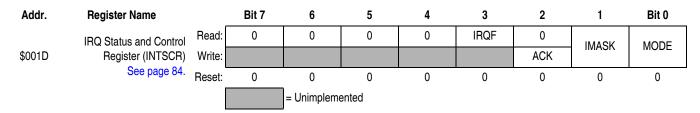

When set, the IMASK bit in the INTSCR masks all external interrupt requests. A latched interrupt request is not presented to the interrupt priority logic unless the IMASK bit is clear.

# **NOTE**The interrupt mask (I) in the condition code register (CCR) masks all interrupt requests, including external interrupt requests.

Figure 8-2. IRQ I/O Register Summary

#### 8.4 IRQ Pin

A logic 0 on the  $\overline{IRQ}$  pin can latch an interrupt request into the IRQ latch. A vector fetch, software clear, or reset clears the IRQ latch.

MC68HC908LB8 Data Sheet, Rev. 1

## Chapter 10 High Resolution PWM (HRP)

#### 10.1 Introduction

The High Resolution PWM (HRP) provides two complementary outputs that can be used to control half-bridge systems in, for example, light ballast applications. It uses a dithering control method to provide a high step resolution (3.906 ns from an 8 MHz input clock). It also provides a shutdown input that can be used to disable the outputs when a fault condition is detected in the application.

The pins supporting the HRP can be seen in Figure 10-1, and a block diagram of the HRP module is shown in Figure 10-3.

#### 10.2 Features

Features of the HRP include:

- One complementary output pair for driving a half bridge

- Dithering between two frequencies or duty cycles, for increased output resolution

- Automatic calculation of second frequency or duty cycle for output dithering

- Variable frequency mode with automatic 50% duty cycle calculation

- Variable duty cycle mode

- Programmable deadtime insertion

- Shutdown input for fast disabling of outputs

#### 10.3 Pin Name Conventions

The HRP shares two output pins with two port B input/output (I/O) pins and one input pin with one port C input pin.

**Table 10-1. Pin Naming Conventions**

| HRP Generic Pin Name | Full HRP Pin Name |

|----------------------|-------------------|

| TOP                  | PTB0/TOP          |

| ВОТ                  | PTB1/BOT          |

| SHTDWN               | PTC2/SHTDWN/IRQ   |

93

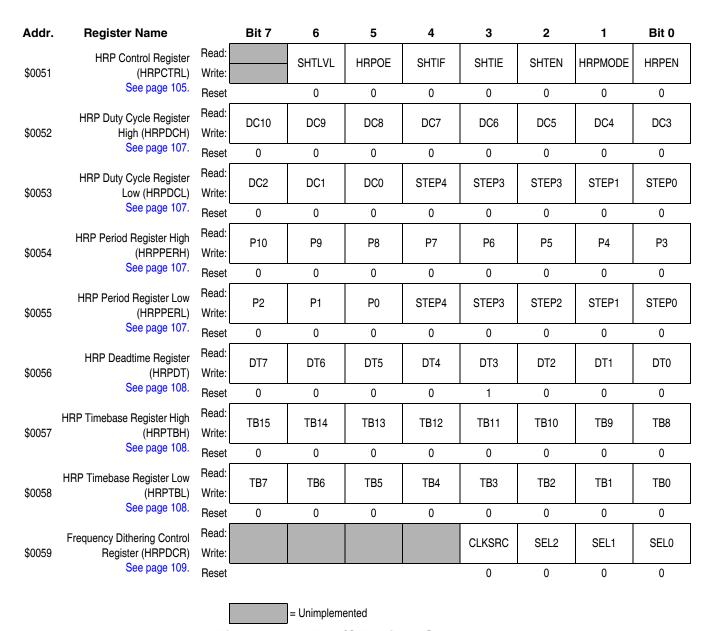

Figure 10-2. HRP I/O Register Summary

#### NOTE

When HRPMODE = 0, STEP[4:0] are mapped into the five least significant bits of the HRPPERL register.

When HRPMODE = 1, STEP[4:0] are mapped into the five least significant bits of the HRPDCL register.

### 10.4 Functional Description

Figure 10-3 provides a block diagram of the module.

MC68HC908LB8 Data Sheet, Rev. 1

Low-Voltage Inhibit (LVI)

#### **ECGST** — External Clock Status Bit

This read-only bit indicates whether or not an external clock source is engaged to drive the system clock.

- 1 = An external clock source engaged

- 0 = An external clock source disengaged

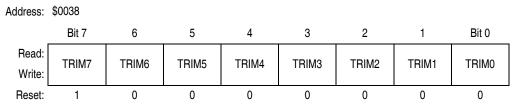

#### 13.8.2 Oscillator Trim Register (OSCTRIM)

Figure 13-5. Oscillator Trim Register (OSCTRIM)

#### TRIM7-TRIM0 — Internal Oscillator Trim Factor Bits

These read/write bits change the size of the internal capacitor used by the internal oscillator. By measuring the period of the internal clock and adjusting this factor accordingly, the frequency of the internal clock can be fine tuned. Increasing (decreasing) this factor by one increases (decreases) the period by appoximately 0.2% of the untrimmed period (the period for TRIM = \$80). The trimmed frequency is guaranteed not to vary by more than  $\pm 5\%$  over the full specified range of temperature and voltage. The reset value is \$80, which sets the frequency to 16 MHz (4.0 MHz bus speed)  $\pm 25\%$ .

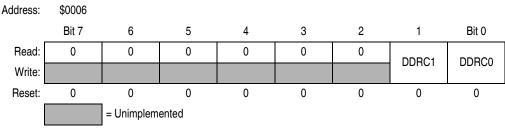

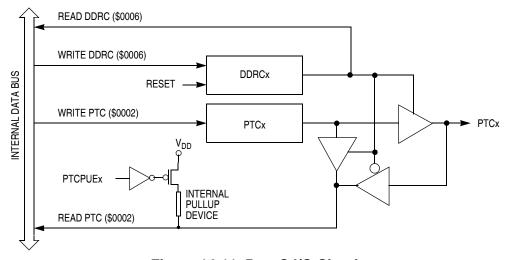

Figure 14-10. Data Direction Register C (DDRC)

#### DDRC1-DDRC0 — Data Direction Register C Bits

These read/write bits control port C data direction. Reset clears DDRC1–DDRC0, configuring all port C pins as inputs.

- 1 = Corresponding port C pin configured as output

- 0 = Corresponding port C pin configured as input

#### NOTE

Avoid glitches on port C pins by writing to the port C data register before changing data direction register C bits from 0 to 1.

Figure 14-11 shows the port C I/O logic.

Figure 14-11. Port C I/O Circuit

#### NOTE

Figure 14-11 does not apply to PTC2.

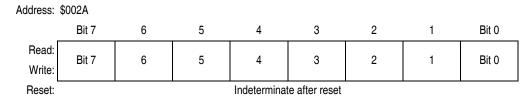

When bit DDRCx is a 1, reading address \$0002 reads the PTCx data latch. When bit DDRCx is a 0, reading address \$0002 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 14-3 summarizes the operation of the port C pins.

Pulse Width Modulator with Fault Input (PWM)

Figure 17-2. SIM I/O Register Summary

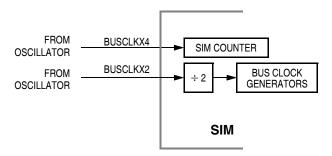

#### 17.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, BUSCLKX2, as shown in Figure 17-3.

Figure 17-3. SIM Clock Signals

#### 17.2.1 Bus Timing

In user mode, the internal bus frequency is the oscillator frequency (BUSCLKX4) divided by four.

#### 17.2.2 Clock Start-Up from POR

When the power-on reset module generates a reset, the clocks to the CPU and peripherals are inactive and held in an inactive phase until after the 4096 BUSCLKX4 cycle POR time out has completed. The RST pin is driven low by the SIM during this entire period. The IBUS clocks start upon completion of the time out.

#### 17.2.3 Clocks in Stop Mode and Wait Mode

Upon exit from stop mode by an interrupt or reset, the SIM allows BUSCLKX4 to clock the SIM counter. The CPU and peripheral clocks do not become active until after the stop delay time out. This time out is selectable as 4096 or 32 BUSCLKX4 cycles. See 17.6.2 Stop Mode.

MC68HC908LB8 Data Sheet, Rev. 1

Figure 17-10. Interrupt Processing

MC68HC908LB8 Data Sheet, Rev. 1 179 Freescale Semiconductor

#### **Timer Interface Module (TIM)**

Figure 18-3. TIM I/O Register Summary (Sheet 2 of 2)

#### 18.3.1 TIM Counter Prescaler

The TIM clock source can be one of the seven prescaler outputs. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register select the TIM clock source.

#### 18.3.2 Input Capture

With the input capture function, the TIM can capture the time at which an external event occurs. When an active edge occurs on the pin of an input capture channel, the TIM latches the contents of the TIM counter into the TIM channel registers, TCHxH:TCHxL. The polarity of the active edge is programmable. Input captures can generate TIM CPU interrupt requests.

### 18.3.3 Output Compare

With the output compare function, the TIM can generate a periodic pulse with a programmable polarity, duration, and frequency. When the counter reaches the value in the registers of an output compare channel, the TIM can set, clear, or toggle the channel pin. Output compares can generate TIM CPU interrupt requests.

#### 18.3.3.1 Unbuffered Output Compare

Any output compare channel can generate unbuffered output compare pulses as described in 18.3.3 Output Compare. The pulses are unbuffered because changing the output compare value requires writing the new value over the old value currently in the TIM channel registers.

An unsynchronized write to the TIM channel registers to change an output compare value could cause incorrect operation for up to two counter overflow periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that counter overflow period. Also, using a TIM overflow interrupt routine to write a new, smaller output compare value may cause the compare to be missed. The TIM may pass the new value before it is written.

Use the following methods to synchronize unbuffered changes in the output compare value on channel x:

When changing to a smaller value, enable channel x output compare interrupts and write the new

value in the output compare interrupt routine. The output compare interrupt occurs at the end of

the current output compare pulse. The interrupt routine has until the end of the counter overflow

period to write the new value.

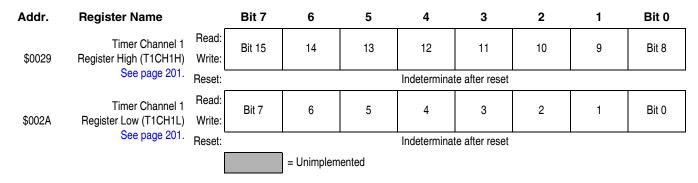

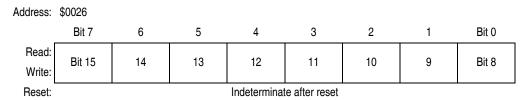

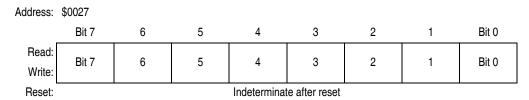

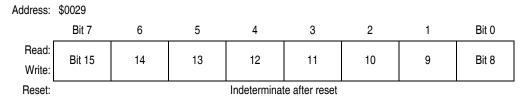

#### 18.8.5 TIM Channel Registers

These read/write registers contain the captured TIM counter value of the input capture function or the output compare value of the output compare function. The state of the TIM channel registers after reset is unknown.

In input capture mode (MSxB:MSxA = 0:0), reading the high byte of the TIM channel x registers (TCHxH) inhibits input captures until the low byte (TCHxL) is read.

In output compare mode (MSxB:MSxA  $\neq$  0:0), writing to the high byte of the TIM channel x registers (TCHxH) inhibits output compares until the low byte (TCHxL) is written.

Figure 18-13. TIM Channel 0 Register High (TCH0H)

Figure 18-14. TIM Channel 0 Register Low (TCH0L)

Figure 18-15. TIM Channel 1 Register High (TCH1H)

Figure 18-16. TIM Channel 1 Register Low (TCH1L)

205

#### 19.2.1.2 CPU During Break Interrupts

The CPU starts a break interrupt by:

- Loading the instruction register with the SWI instruction

- Loading the program counter with \$FFFC:\$FFFD (\$FEFC:\$FEFD in monitor mode)

The break interrupt begins after completion of the CPU instruction in progress. If the break address register match occurs on the last cycle of a CPU instruction, the break interrupt begins immediately.

#### 19.2.1.3 TIM During Break Interrupts

A break interrupt stops the timer counter.

#### 19.2.1.4 COP During Break Interrupts

The COP is disabled during a break interrupt with monitor mode when BDCOP bit is set in break auxiliary register (BRKAR).

#### 19.2.2 Break Module Registers

These registers control and monitor operation of the break module:

- Break status and control register (BRKSCR)

- Break address register high (BRKH)

- Break address register low (BRKL)

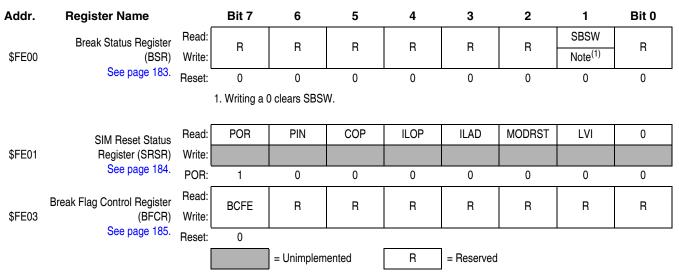

- Break status register (BSR)

- Break flag control register (BFCR)

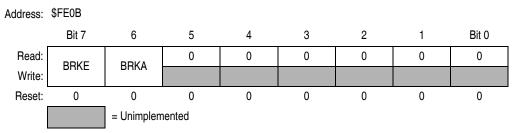

#### 19.2.2.1 Break Status and Control Register

The break status and control register (BRKSCR) contains break module enable and status bits.

Figure 19-3. Break Status and Control Register (BRKSCR)

#### **BRKE** — Break Enable Bit

This read/write bit enables breaks on break address register matches. Clear BRKE by writing a 0 to bit 7. Reset clears the BRKE bit.

- 1 = Breaks enabled on 16-bit address match

- 0 = Breaks disabled

#### BRKA — Break Active Bit

This read/write status and control bit is set when a break address match occurs. Writing a 1 to BRKA generates a break interrupt. Clear BRKA by writing a 0 to it before exiting the break routine. Reset clears the BRKA bit.

- 1 = Break address match

- 0 = No break address match

Freescale Semiconductor

#### MC68HC908LB8 Data Sheet, Rev. 1

#### **Development Support**

#### Notes:

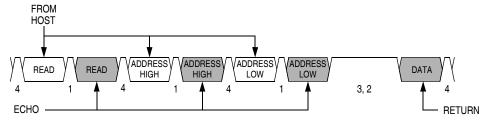

- 1 = Echo delay, approximately 2 bit times 2 = Data return delay, approximately 2 bit times 3 = Cancel command delay, 11 bit times 4 = Wait 1 bit time before sending next byte.

Figure 19-15. Read Transaction

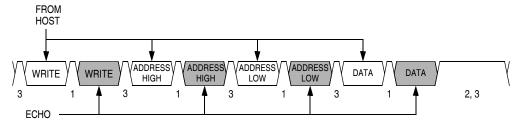

#### Notes:

- 1 = Echo delay, approximately 2 bit times 2 = Cancel command delay, 11 bit times 3 = Wait 1 bit time before sending next byte.

Figure 19-16. Write Transaction

#### NOTES:

- 1. f<sub>Bead</sub> is defined as the frequency range for which the FLASH memory can be read.

- 2. If the page erase time is longer than t<sub>Erase</sub> (min), there is no erase disturb, but it reduces the endurance of the FLASH

- 3. If the mass erase time is longer than t<sub>MErase</sub> (min), there is no erase disturb, but it reduces the endurance of the FLASH memory.

- 4. t<sub>RCV</sub> is defined as the time it needs before the FLASH can be read after turning off the high voltage charge pump, by clearing HVEN to 0.

- $5.\ t_{HV}$  is defined as the cumulative high voltage programming time to the same row before next erase.

- $t_{HV}$  must satisfy this condition:  $t_{NVS} + t_{NVH} + t_{PGS} + (t_{PROG} \times 32) \le t_{HV}$  maximum. 6. Typical endurance was evaluated for this product family. For additional information on how Freescale Semiconductor defines Typical Endurance, please refer to Engineering Bulletin EB619.

- 7. Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale Semiconductor defines Typical Data Retention, please refer to Engineering Bulletin EB618.