Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Obsolete                                                       |

| Core Processor             | XCore                                                          |

| Core Size                  | 32-Bit 24-Core                                                 |

| Speed                      | 4000MIPS                                                       |

| Connectivity               | USB                                                            |

| Peripherals                | -                                                              |

| Number of I/O              | 176                                                            |

| Program Memory Size        | 2MB (2M x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 512K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                   |

| Data Converters            | -                                                              |

| Oscillator Type            | External                                                       |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 374-LFBGA                                                      |

| Supplier Device Package    | 374-FBGA (18x18)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xuf224-512-fb374-c40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

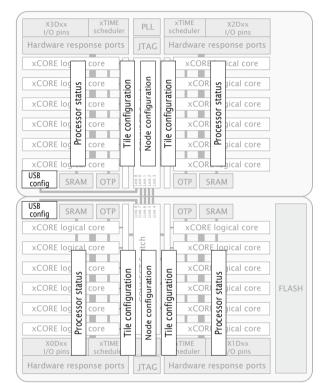

## 1 xCORE Multicore Microcontrollers

The xCORE200 Series is a comprehensive range of 32-bit multicore microcontrollers that brings the low latency and timing determinism of the xCORE architecture to mainstream embedded applications. Unlike conventional microcontrollers, xCORE multicore microcontrollers execute multiple real-time tasks simultaneously and communicate between tasks using a high speed network. Because xCORE multicore microcontrollers are completely deterministic, you can write software to implement functions that traditionally require dedicated hardware.

Figure 1: XUF224-512-FB374 block diagram

Key features of the XUF224-512-FB374 include:

- ► **Tiles**: Devices consist of one or more xCORE tiles. Each tile contains between five and eight 32-bit xCOREs with highly integrated I/O and on-chip memory.

- Logical cores Each logical core can execute tasks such as computational code, DSP code, control software (including logic decisions and executing a state machine) or software that handles I/O. Section 6.1

- xTIME scheduler The xTIME scheduler performs functions similar to an RTOS, in hardware. It services and synchronizes events in a core, so there is no requirement for interrupt handler routines. The xTIME scheduler triggers cores

XS2-UF24A-512-FB374

# 3 Pin Configuration

|    | 1                                       | 2                                                                    | 3                                            | 4     | 5      | 6                  | 7             | 8                                                      | 9                                                           | 10          | 11          | 12          | 13       | 14                      | 15           | 16                                     | 17    | 18                    | 19                      | 20                               | 21                                              |

|----|-----------------------------------------|----------------------------------------------------------------------|----------------------------------------------|-------|--------|--------------------|---------------|--------------------------------------------------------|-------------------------------------------------------------|-------------|-------------|-------------|----------|-------------------------|--------------|----------------------------------------|-------|-----------------------|-------------------------|----------------------------------|-------------------------------------------------|

| A  | GND                                     | VDDIO                                                                | X1D11                                        | X1D32 | X1D26  |                    | X1D41         | X0D31                                                  | X0D29                                                       | TDI         | VDDIO       | CLK         | TDO      | X3D32                   | X3D30        | VDDIOT                                 | X2D31 | X2D29                 | X2D32                   | VDDIO                            | GND                                             |

| в  | X0D37<br>X,42                           | X0D36                                                                | X1D10                                        | X1D33 | X1027  | X1D42              | X1D40         | X0D30                                                  | X0D28                                                       | X2D36       | GND         | RST_N       | тск      | X3D33                   | X3D31        | X3D27                                  | X2D30 | X2D28                 | X2D27<br>X,07           | X2D26<br>×.c?                    | <b>X2D35</b><br>X.07                            |

| с  | X0D39<br>X <sub>1</sub> C <sup>2</sup>  | X0D38<br>X <sub>1</sub> 2                                            | VDD                                          | X1030 | X1D28  | X1D43              | GND           | x0D33                                                  | x0D32                                                       | MODE1       | OTP<br>VCC  | TRST        | X3D10    | X3D29                   | GND          | X3D43                                  | x3D41 | X2D33                 | VDD                     | 12<br>X2D25<br>X,C)              | <sup>тк</sup><br>Х2D34<br>Х(1)                  |

| D  | X0D41<br>X,c_1                          | X0D40<br>X,L_1                                                       | 1К<br>X1D34<br>X <sub>1</sub> C <sub>0</sub> | X1031 | хі́D29 | GND                | VDDIO         | NC                                                     | GLOBAL<br>_DEBUG                                            | MODE0       |             | TMS         | X3D11    | X3D28                   | 45<br>X3D26  | X3D42                                  | X3D40 | 22A<br>X2D70<br>X,L_1 | X3D00<br>X,C            | 18<br>X3D01<br>X,L <sup>2</sup>  | X2D24<br>X,L <sup>1</sup>                       |

| E  | 00<br>X0D43<br>X(2)                     | 00<br>X0D42<br>X,C                                                   | X1D35<br>X <sub>0</sub> 25                   | VDD   | VDD    | GND                | VDDIO         | VDD                                                    | VDD                                                         |             |             |             | VDD      | VDD                     | VDDIO        | GND                                    | VDD   | VDD                   | 22A<br>X2D69<br>X,C)    | 3008<br>31,13<br>31,13           | X3D09<br>X.17                                   |

| F  | X1D36<br>X <sub>1</sub> L <sup>10</sup> | VDDIO                                                                | GND                                          | VDD   | VDD    | VDD                | VDD           | VDD                                                    | VDD                                                         | PLL<br>AGND | PLL<br>AVDD | VDD         | VDD      | VDD                     | VDD          | VDD                                    | VDD   | VDD                   | GND                     | VDDIO                            | 220A<br>X2D68<br>X,t <sup>2</sup>               |

| G  | X1D49                                   | $\overset{228}{\underset{X_{0}^{} L_{1}^{0}}{320}}$                  | 22A<br>X1D51<br>X(2)                         | NC    | NC     | Reserved           | Reserved      | Reserved                                               | Reserved<br>X,C_1^{(1)}                                     |             |             |             | Reserved | Reserved                | Reserved     | $\mathop{\text{Reserved}}_{X_i U_i^0}$ | NC    | NC                    | 22A<br>X2D67<br>X,2°    | 228<br>X2D66<br>X,C_1            | 22A<br>X2D65<br>X,L <sup>a</sup>                |

| н  | X1D53                                   | $\overset{2234}{\underset{X_{ij}L_{i}^{2}}{\overset{2234}}}$         | VDD                                          |       |        |                    |               |                                                        |                                                             |             |             |             |          |                         |              |                                        |       |                       | VDD                     | 22A<br>X2D63<br>X,L <sup>2</sup> | 22A<br>X2D64<br>X,L_5                           |

| J  | X1D54<br>X,17                           | X1D55<br>X(1)                                                        | VDD                                          |       | GND    | GND                | GND           | GND                                                    | GND                                                         |             |             |             | GND      | GND                     | GND          | GND                                    | GND   |                       | VDD                     | 22A<br>X2D62<br>X,L2             | 22A<br>X2D61<br>X,1,2                           |

| к  | X1D58<br>X <sub>1</sub> D58             | X1D57<br>X <sub>1</sub> C <sup>2</sup>                               | X1D56<br>X,C <sup>2</sup>                    |       | GND    | GND                | GND           | GND                                                    | GND                                                         |             |             |             | GND      | GND                     | GND          | GND                                    | GND   |                       | 22A<br>X2D56<br>X,C_1^2 | 22A<br>X2D57<br>X,C_1^4          | 220A<br>X2D58<br>X, L <sup>a</sup> <sub>0</sub> |

| L  | VDDIO                                   | GND                                                                  | X1D61<br>X(15                                |       | GND    | GND                | GND           | GND                                                    | GND                                                         |             |             |             | GND      | GND                     | GND          | GND                                    | GND   |                       | 22A<br>X2D55<br>X,0%    | GND                              | VDDIO                                           |

| м  | X1D64<br>X(1)                           | X1D63<br>X,L3                                                        | 22A<br>X1D62<br>X,L <sup>0</sup>             |       | GND    | GND                | GND           | GND                                                    | GND                                                         |             |             |             | GND      | GND                     | GND          | GND                                    | GND   |                       | 22A<br>X2D54<br>X,C?    | X2D53<br>x,c?                    | 22A<br>X2D52<br>X,1]                            |

| N  | X1D65<br>X,47                           | X1D66<br>X,C) <sup>20A</sup>                                         | VDD                                          |       | GND    | GND                | GND           | GND                                                    | GND                                                         |             |             |             | GND      | GND                     | GND          | GND                                    | GND   |                       | VDD                     | X2D50<br>X,L2                    | 22A<br>X2D51<br>X.12                            |

| Р  | X1D68                                   | X1267<br>X1267<br>X_121                                              | VDD                                          |       |        |                    |               |                                                        |                                                             |             |             |             |          |                         |              |                                        |       |                       | VDD                     | X3D06<br>X,C,                    | <b>X3D07</b><br>X,C,                            |

| R  | X1D69<br>X(1)                           | X1D70<br>X(L)                                                        | X1D37<br>X <sub>1</sub> L <sup>1</sup>       | NC    | NC     | NC                 | NC            | $\mathop{\text{Reserved}}_{X_i \zeta_i^c}^{4 \square}$ | $\mathop{\text{Reserved}}_{X, \mathcal{L}_1^{\mathcal{U}}}$ |             |             |             | Reserved | Reserved<br>X,Z_1^{(1)} | NC           | NC                                     | NC    | NC                    | 22A<br>X2D49<br>X,C     | X3D04<br>X,C_1^2                 | 400<br>X3D05<br>X,C_2                           |

| т  | X1D38                                   | VDDIO                                                                | GND                                          | VDD   | VDD    | VDD                | USB_<br>VDD_0 | VDD                                                    | VDD                                                         | VDD         | GND         | VDD         | VDD      | VDD                     | USB<br>VDD_1 | VDD                                    | VDD   | VDD                   | GND                     | VDDIO                            | 44.<br>X3D03<br>X,C <sup>0</sup>                |

| U  | X1D17                                   | X1D16                                                                | X1D39<br>X <sub>1</sub> L <sup>0</sup>       | VDD   | VDD    | GND                | VDDIO         | NC                                                     | VDD                                                         |             | VDDIO       |             | VDD      | VDD                     | VDDIO        | GND                                    | VDD   | VDD                   | NC                      | X2D19<br>X(2)                    | <b>X3D02</b><br>X,L <sup>0</sup>                |

| v  | X1D19<br>X(2)                           | X1D18<br>X121                                                        | X0D01<br>X,25                                | X0D02 | X0D08  | X0D11              | USB_<br>ID_0  | x1D14                                                  | и<br>Х1D25                                                  | X0D21       | NC          | 1H<br>X3D23 | X2D05    | x2D07                   | USB<br>ID_F  | NC                                     | x3D15 | x3D21                 | 15<br>X2D12             | X2D17<br>X(2)<br>X(2)            | X2D18                                           |

| w  | X0D10<br>X(L)                           | $\overset{^{1G}}{\underset{X_{i}\mathcal{L}_{i}^{H}}{\overset{1G}}}$ | USB<br>VDD33_<br>0                           | X0D03 | X0D09  | USB<br>RTUNE_<br>0 | GND           | x1D15                                                  | X0D14                                                       | X0D12       | X0D23       | X2D00       | x2D04    | 40<br>X2D06             | GND          | USB<br>RTUNE_<br>1                     | x3D14 | X3D20                 | USB<br>VDD33_<br>1      | X2D23                            | 40<br>X2D16<br>≍,L <sup>8</sup>                 |

| Y  | X1D23                                   | X0D00                                                                | X0D04                                        | X0D06 | X1D12  | USB<br>VBUS_0      | X1D24         | x1D20                                                  | X0D15                                                       | X0D13       | GND         | X2D11       | X2D02    | x2D08                   | X3D13        | VUSB<br>BUS_T                          | x2D14 | X2D20                 | X3D24                   | X2D13                            | X2D22                                           |

| AA | GND                                     | VDDIO                                                                | x0D05                                        | x0D07 | X1D13  | USB<br>DM_0        | USB<br>DP_0   | 40<br>X1D21                                            | x0D20                                                       | X0D22       | VDDIO       | X3D12       | X2D03    | x2D09                   | USB<br>DM_T  | USB<br>DP_T                            | x2D15 | x2D21                 | Х3D25                   | VDDIO                            | GND                                             |

-XMOS<sup>®</sup>-

6

(continued)

| Signal | Function                                      |                 |                 |                 |                   |                   | Type | Properties |

|--------|-----------------------------------------------|-----------------|-----------------|-----------------|-------------------|-------------------|------|------------|

| X1D64  | X <sub>0</sub> L2 <sup>1</sup>                |                 |                 |                 |                   | 32A <sup>13</sup> | I/0  | IO, PD     |

| X1D65  | X <sub>0</sub> L2 <sup>0</sup>                |                 |                 |                 |                   | 32A <sup>14</sup> | 1/0  | IO, PD     |

| X1D66  | X <sub>0</sub> L2 <sup>0</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>15</sup> | 1/0  | IO, PD     |

| X1D67  | X <sub>0</sub> L2 <sup>1</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>16</sup> | 1/0  | IO, PD     |

| X1D68  | X <sub>0</sub> L2 <sup>2</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>17</sup> | 1/0  | IO, PD     |

| X1D69  | X <sub>0</sub> L2 <sup>3</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>18</sup> | I/0  | IO, PD     |

| X1D70  | X <sub>0</sub> L2 <sup>4</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>19</sup> | I/O  | IO, PD     |

| X2D00  |                                               | 1A <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D02  |                                               |                 | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | 1/0  | IO, PD     |

| X2D03  |                                               |                 | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  | 32A <sup>21</sup> | I/O  | IO, PD     |

| X2D04  |                                               |                 | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/0  | IO, PD     |

| X2D05  |                                               |                 | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O  | IO, PD     |

| X2D06  |                                               |                 | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/O  | IO, PD     |

| X2D07  |                                               |                 | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O  | IO, PD     |

| X2D08  |                                               |                 | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O  | IO, PD     |

| X2D09  |                                               |                 | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O  | IO, PD     |

| X2D11  |                                               | 1D <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D12  |                                               | 1E <sup>0</sup> |                 |                 |                   |                   | I/0  | IO, PD     |

| X2D13  |                                               | 1F <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D14  |                                               |                 | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | 1/0  | IO, PD     |

| X2D15  |                                               |                 | 4C <sup>1</sup> | 8B1             | 16A <sup>9</sup>  | 32A <sup>29</sup> | 1/0  | IO, PD     |

| X2D16  | X <sub>2</sub> L4 <sup>4</sup> in             |                 | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> |                   | I/O  | IO, PD     |

| X2D17  | X <sub>2</sub> L4 <sup>3</sup> <sub>in</sub>  |                 | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | I/O  | IO, PD     |

| X2D18  | X <sub>2</sub> L4 <sup>2</sup> <sub>in</sub>  |                 | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | I/O  | IO, PD     |

| X2D19  | X <sub>2</sub> L4 <sup>1</sup> <sub>in</sub>  |                 | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | I/O  | IO, PD     |

| X2D20  |                                               |                 | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | I/O  | IO, PD     |

| X2D21  |                                               |                 | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup> | I/O  | IO, PD     |

| X2D22  |                                               | 1G <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D23  |                                               | 1H <sup>0</sup> |                 |                 |                   |                   | I/0  | IO, PD     |

| X2D24  | X <sub>2</sub> L7 <sup>0</sup>                | 11 <sup>0</sup> |                 |                 |                   |                   | I/0  | IO, PD     |

| X2D25  | X <sub>2</sub> L7 <sup>0</sup><br>out         | 1J <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D26  | $X_2L7_{out}^3$                               |                 | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | I/O  | IO, PD     |

| X2D27  | X <sub>2</sub> L7 <sup>4</sup> <sub>out</sub> |                 | 4E <sup>1</sup> | 8C1             | 16B <sup>1</sup>  |                   | I/O  | IO, PD     |

| X2D28  |                                               |                 | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/O  | IO, PD     |

| X2D29  |                                               |                 | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | I/O  | IO, PD     |

| X2D30  |                                               |                 | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | I/O  | IO, PD     |

| X2D31  |                                               |                 | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | I/O  | IO, PD     |

| X2D32  |                                               |                 | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | I/O  | IO, PD     |

| X2D33  |                                               |                 | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | I/O  | IO, PD     |

| X2D34  | $X_2L7_{out}^1$                               | 1K <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D35  | $X_2L7_{out}^2$                               | 1L <sup>0</sup> |                 |                 |                   |                   | I/O  | IO, PD     |

| X2D36  |                                               | 1M <sup>0</sup> |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | I/O  | IO, PD     |

| A2D30  | X <sub>2</sub> L5 <sup>4</sup>                |                 |                 |                 |                   |                   |      |            |

## 6 Product Overview

The XUF224-512-FB374 is a powerful device that consists of four xCORE Tiles, each comprising a flexible logical processing cores with tightly integrated I/O and on-chip memory.

#### 6.1 Logical cores

Each tile has 6 active logical cores, which issue instructions down a shared fivestage pipeline. Instructions from the active cores are issued round-robin. If up to five logical cores are active, each core is allocated a fifth of the processing cycles. If more than five logical cores are active, each core is allocated at least 1/n cycles (for *n* cores). Figure 3 shows the guaranteed core performance depending on the number of cores used.

Figure 3: Logical core performance

| ure 3: | Speed | MIPS      | Frequency Minimum MIPS per core (for <i>H</i> |     |     |     |     | 1 core | s) |  |  |

|--------|-------|-----------|-----------------------------------------------|-----|-----|-----|-----|--------|----|--|--|

| l core | grade |           |                                               | 1   | 2   | 3   | 4   | 5      | 6  |  |  |

| nance  | 20    | 2000 MIPS | 500 MHz                                       | 100 | 100 | 100 | 100 | 100    | 83 |  |  |

There is no way that the performance of a logical core can be reduced below these predicted levels (unless *priority threads* are used: in this case the guaranteed minimum performance is computed based on the number of priority threads as defined in the architecture manual). Because cores may be delayed on I/O, however, their unused processing cycles can be taken by other cores. This means that for more than five logical cores, the performance of each core is often higher than the predicted minimum but cannot be guaranteed.

The logical cores are triggered by events instead of interrupts and run to completion. A logical core can be paused to wait for an event.

## 6.2 xTIME scheduler

The xTIME scheduler handles the events generated by xCORE Tile resources, such as channel ends, timers and I/O pins. It ensures that all events are serviced and synchronized, without the need for an RTOS. Events that occur at the I/O pins are handled by the Hardware-Response ports and fed directly to the appropriate xCORE Tile. An xCORE Tile can also choose to wait for a specified time to elapse, or for data to become available on a channel.

Tasks do not need to be prioritised as each of them runs on their own logical xCORE. It is possible to share a set of low priority tasks on a single core using cooperative multitasking.

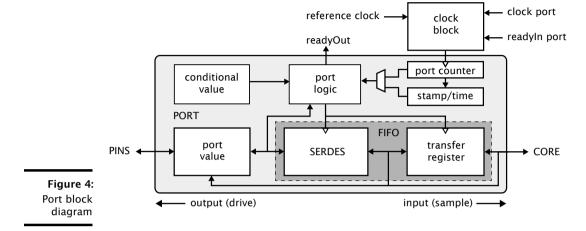

#### 6.3 Hardware Response Ports

Hardware Response ports connect an xCORE tile to one or more physical pins and as such define the interface between hardware attached to the XUF224-512-FB374, and the software running on it. A combination of 1 bit, 4 bit, 8 bit, 16 bit and 32 bit

ports are available. All pins of a port provide either output or input. Signals in different directions cannot be mapped onto the same port.

The port logic can drive its pins high or low, or it can sample the value on its pins, optionally waiting for a particular condition. Ports are accessed using dedicated instructions that are executed in a single processor cycle. xCORE-200 IO pins can be used as *open collector* outputs, where signals are driven low if a zero is output, but left high impedance if a one is output. This option is set on a per-port basis.

Data is transferred between the pins and core using a FIFO that comprises a SERDES and transfer register, providing options for serialization and buffered data.

Each port has a 16-bit counter that can be used to control the time at which data is transferred between the port value and transfer register. The counter values can be obtained at any time to find out when data was obtained, or used to delay I/O until some time in the future. The port counter value is automatically saved as a timestamp, that can be used to provide precise control of response times.

The ports and xCONNECT links are multiplexed onto the physical pins. If an xConnect Link is enabled, the pins of the underlying ports are disabled. If a port is enabled, it overrules ports with higher widths that share the same pins. The pins on the wider port that are not shared remain available for use when the narrower port is enabled. Ports always operate at their specified width, even if they share pins with another port.

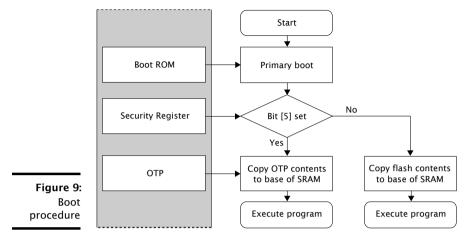

## 6.4 Clock blocks

xCORE devices include a set of programmable clocks called clock blocks that can be used to govern the rate at which ports execute. Each xCORE tile has six clock blocks: the first clock block provides the tile reference clock and runs at a default frequency of 100MHz; the remaining clock blocks can be set to run at different frequencies. The xCORE Tile boot procedure is illustrated in Figure 9. If bit 5 of the security register (*see*  $\S9.1$ ) is set, the device boots from OTP. Otherwise, the device boots from the internal flash.

The boot image has the following format:

- ► A 32-bit program size *s* in words.

- Program consisting of  $s \times 4$  bytes.

- A 32-bit CRC, or the value 0x0D15AB1E to indicate that no CRC check should be performed.

The program size and CRC are stored least significant byte first. The program is loaded into the lowest memory address of RAM, and the program is started from that address. The CRC is calculated over the byte stream represented by the program size and the program itself. The polynomial used is 0xEDB88320 (IEEE 802.3); the CRC register is initialized with 0xFFFFFFFF and the residue is inverted to produce the CRC.

#### 8.1 Security register

The security register enables security features on the xCORE tile. The features shown in Figure 10 provide a strong level of protection and are sufficient for providing strong IP security.

## 9 Memory

#### 9.1 OTP

Each xCORE Tile integrates 8 KB one-time programmable (OTP) memory along with a security register that configures system wide security features. The OTP holds data in four sectors each containing 512 rows of 32 bits which can be used to

| Feature               | Bit  | Description                                                                                                                                                                                                                                |

|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable JTAG          | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                     |

| Disable Link access 1 |      | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island"<br>with other tiles free for non-secure user application<br>code. |

| Secure Boot           | 5    | The xCORE Tile is forced to boot from address 0 of the OTP, allowing the xCORE Tile boot ROM to be bypassed ( <i>see</i> §8).                                                                                                              |

| Redundant rows        | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                             |

| Sector Lock 0         | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                       |

| Sector Lock 1         | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                       |

| Sector Lock 2         | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                       |

| Sector Lock 3         | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                       |

| OTP Master Lock       | 12   | Disable OTP programming completely: disables up<br>dates to all sectors and security register.                                                                                                                                             |

| Disable JTAG-OTP      | 13   | Disable all (read & write) access from the JTAG inter face to this OTP.                                                                                                                                                                    |

| Disable Global Debug  | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                        |

|                       | 2115 | General purpose software accessable security register available to end-users.                                                                                                                                                              |

|                       | 3122 | General purpose user programmable JTAG UserIE code extension.                                                                                                                                                                              |

Figure 10: Security register features

implement secure bootloaders and store encryption keys. Data for the security register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

#### 9.2 SRAM

Each xCORE Tile integrates a single 128KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

-XMOS-

## 10 USB PHY

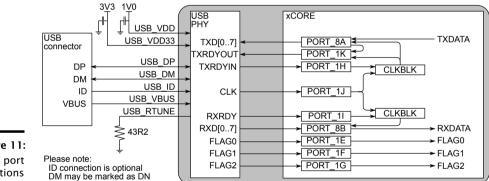

The USB PHY provides High-Speed and Full-Speed, device, host, and on-the-go functionality. The PHY is configured through a set of peripheral registers (Appendix F), and data is communicated through ports on the digital node. A library, libxud\_s.a, is provided to implement USB device functionality.

This device has two USB PHYs. One PHY is part of Node 0 and can be connected to either Tile 0 or Tile 1; it uses pins USB\_DM, USB\_DP, USB\_VUBS, USB\_ID, and USB\_RTUNE. The other PHY is part of Node 2 and can be connected to either Tile 2 or Tile 3; it uses pins USB\_2\_DM, USB\_2\_DP, USB\_2\_VUBS, USB\_2\_ID, and USB\_2\_RTUNE. Below we present the configuration of the USB PHY connected to Node 0 (Tiles 0 and 1) an identical configuration is available for Node 2.

The USB PHY is connected to the ports on Tile 0 and Tile 1 as shown in Figure 11. When the USB PHY is enabled on Tile 0, the ports shown can on Tile 0 only be used with the USB PHY. When the USB PHY is enabled on Tile 1, then the ports shown can on Tile 1 only be used with the USB PHY. All other IO pins and ports are unaffected. The USB PHY should not be enabled on both tiles.

An external resistor of 43.2 ohm (1% tolerance) should connect USB\_RTUNE to ground, as close as possible to the device.

Figure 11: USB port functions

Figure 11 shows how two clock blocks can be used to clock the USB ports. One clock block for the TXDATA path, and one clock block for the RXDATA path. Details on how to connect those ports are documented in an application note on USB for xCORE-200.

## 10.1 Logical Core Requirements

The XMOS XUD software component runs in a single logical core with endpoint and application cores communicating with it via a combination of channel communication and shared memory variables.

Each IN (host requests data from device) or OUT (data transferred from host to device) endpoint requires one logical core.

## 13 DC and Switching Characteristics

| Symbol     | Parameter                                     | MIN   | ТҮР  | MAX   | UNITS | Notes |

|------------|-----------------------------------------------|-------|------|-------|-------|-------|

| VDD        | Tile DC supply voltage                        | 0.95  | 1.00 | 1.05  | V     |       |

| VDDIO      | I/O supply voltage                            | 2.30  | 3.30 | 3.60  | V     |       |

| VDDIOT 3v3 | I/O supply voltage                            | 3.135 | 3.30 | 3.465 | V     |       |

| VDDIOT 2v5 | I/O supply voltage                            | 2.375 | 2.50 | 2.625 | V     |       |

| USB_VDD    | USB tile DC supply voltage                    | 0.95  | 1.00 | 1.05  | V     |       |

| VDD33      | Peripheral supply                             | 3.135 | 3.30 | 3.465 | V     |       |

| PLL_AVDD   | PLL analog supply                             | 0.95  | 1.00 | 1.05  | V     |       |

| Cl         | xCORE Tile I/O load                           |       |      | 25    | pF    |       |

|            | capacitance                                   |       |      |       |       |       |

| Та         | Ambient operating<br>temperature (Commercial) | 0     |      | 70    | °C    |       |

|            | Ambient operating<br>temperature (Industrial) | -40   |      | 85    | °C    |       |

| Тј         | Junction temperature                          |       |      | 125   | °C    |       |

| Tstg       | Storage temperature                           | -65   |      | 150   | °C    |       |

### 13.1 Operating Conditions

Figure 17: Operating conditions

## 13.2 DC Characteristics, VDDIO=3V3

| Symbol | Parameter                                | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|------------------------------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage                       | 2.00  |     | 3.60 | V     | A     |

| V(IL)  | Input low voltage                        | -0.30 |     | 0.70 | V     | A     |

| V(OH)  | Output high voltage                      | 2.20  |     |      | V     | B, C  |

| V(OL)  | Output low voltage                       |       |     | 0.40 | V     | B, C  |

| I(PU)  | Internal pull-up current (Vin=0V)        | -100  |     |      | μA    | D     |

| I(PD)  | Internal pull-down current<br>(Vin=3.3V) |       |     | 100  | μA    | D     |

| I(LC)  | Input leakage current                    | -10   |     | 10   | μA    |       |

Figure 18: DC characteristics

A All pins except power supply pins.

B Pins X1D40, X1D41, X1D42, X1D43, X1D26, X1D27, X3D40, X3D41, X3D42, X3D43, X3D26, and X3D27 are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry. In order to pull the pin to the opposite state, a 4K7 resistor is recommended to overome the internal pull current.

#### 13.5 Power Consumption

| Symbol     | Parameter              | MIN | TYP  | MAX  | UNITS   | Notes      |

|------------|------------------------|-----|------|------|---------|------------|

| I(DDCQ)    | Quiescent VDD current  |     | 90   |      | mA      | A, B, C    |

| PD         | Tile power dissipation |     | 325  |      | µW/MIPS | A, D, E, F |

| IDD        | Active VDD current     |     | 1140 | 1400 | mA      | A, G       |

| I(ADDPLL)  | PLL_AVDD current       |     | 5    | 7    | mA      | Н          |

| I(VDD33)   | VDD33 current          |     | 53.4 |      | mA      | I          |

| I(USB_VDD) | USB_VDD current        |     | 16.6 |      | mA      | J          |

Figure 22: xCORE Tile currents

A Use for budgetary purposes only.

- B Assumes typical tile and I/O voltages with no switching activity.

- C Includes PLL current.

- D Assumes typical tile and I/O voltages with nominal switching activity.

- E Assumes 1 MHz = 1 MIPS.

- F PD(TYP) value is the usage power consumption under typical operating conditions.

- G Measurement conditions: VDD = 1.0 V, VDDIO = 3.3 V, 25 °C, 500 MHz, average device resource usage.

- H PLL\_AVDD = 1.0 V

- I HS mode transmitting while driving all 0's data (constant JKJK on DP/DM). Loading of 10 pF. Transfers do not include any interpacket delay.

- J HS receive mode; no traffic.

The tile power consumption of the device is highly application dependent and should be used for budgetary purposes only.

More detailed power analysis can be found in the XS1-UF Power Consumption document,

| 1 | 3.6 | Clock |

|---|-----|-------|

|   |     |       |

Figure 23: Clock

| Symbol | Parameter                 | MIN  | TYP | MAX | UNITS | Notes |

|--------|---------------------------|------|-----|-----|-------|-------|

| f      | Frequency                 | 3.25 | 24  | 100 | MHz   |       |

| SR     | Slew rate                 | 0.10 |     |     | V/ns  |       |

| TJ(LT) | Long term jitter (pk-pk)  |      |     | 2   | %     | А     |

| f(MAX) | Processor clock frequency |      |     | 500 | MHz   | В     |

A Percentage of CLK period.

B Assumes typical tile and I/O voltages with nominal activity.

Further details can be found in the XS1-UF Clock Frequency Control document,

## Appendices

## A Configuration of the XUF224-512-FB374

The device is configured through banks of registers, as shown in Figure 29.

#### Figure 29: Registers

The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

## A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0B. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

## **B** Processor Status Configuration

The processor status control registers can be accessed directly by the processor using processor status reads and writes (use getps(reg) and setps(reg,value) for reads and writes).

| Number    | Perm | Description                           |

|-----------|------|---------------------------------------|

| 0x00      | RW   | RAM base address                      |

| 0x01      | RW   | Vector base address                   |

| 0x02      | RW   | xCORE Tile control                    |

| 0x03      | RO   | xCORE Tile boot status                |

| 0x05      | RW   | Security configuration                |

| 0x06      | RW   | Ring Oscillator Control               |

| 0x07      | RO   | Ring Oscillator Value                 |

| 0x08      | RO   | Ring Oscillator Value                 |

| 0x09      | RO   | Ring Oscillator Value                 |

| 0x0A      | RO   | Ring Oscillator Value                 |

| 0x0C      | RO   | RAM size                              |

| 0x10      | DRW  | Debug SSR                             |

| 0x11      | DRW  | Debug SPC                             |

| 0x12      | DRW  | Debug SSP                             |

| 0x13      | DRW  | DGETREG operand 1                     |

| 0x14      | DRW  | DGETREG operand 2                     |

| 0x15      | DRW  | Debug interrupt type                  |

| 0x16      | DRW  | Debug interrupt data                  |

| 0x18      | DRW  | Debug core control                    |

| 0x20 0x27 | DRW  | Debug scratch                         |

| 0x30 0x33 | DRW  | Instruction breakpoint address        |

| 0x40 0x43 | DRW  | Instruction breakpoint control        |

| 0x50 0x53 | DRW  | Data watchpoint address 1             |

| 0x60 0x63 | DRW  | Data watchpoint address 2             |

| 0x70 0x73 | DRW  | Data breakpoint control register      |

| 0x80 0x83 | DRW  | Resources breakpoint mask             |

| 0x90 0x93 | DRW  | Resources breakpoint value            |

| 0x9C 0x9F | DRW  | Resources breakpoint control register |

-XMOS

Figure 30: Summary

XS2-UF24A-512-FB374

| Bits  | Perm | Init | Description                                                                                                                                                                                                                           |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 25:18 | RW   | 0    | RGMII TX data delay value (in PLL output cycle increments)                                                                                                                                                                            |

| 17:9  | RW   | 0    | RGMII TX clock divider value. TX clk rises when counter (clocked<br>by PLL output) reaches this value and falls when counter reaches<br>(value»1). Value programmed into this field should be actual<br>divide value required minus 1 |

| 8     | RW   | 0    | Enable RGMII interface periph ports                                                                                                                                                                                                   |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 5     | RW   | 0    | Select the dynamic mode (1) for the clock divider when the clock divider is enabled. In dynamic mode the clock divider is only activated when all active threads are paused. In static mode the clock divider is always enabled.      |

| 4     | RW   | 0    | Enable the clock divider. This divides the output of the PLL to facilitate one of the low power modes.                                                                                                                                |

| 3     | RO   | -    | Reserved                                                                                                                                                                                                                              |

| 2     | RW   |      | Select between UTMI (1) and ULPI (0) mode.                                                                                                                                                                                            |

| 1     | RW   |      | Enable the ULPI Hardware support module                                                                                                                                                                                               |

| 0     | RO   | -    | Reserved                                                                                                                                                                                                                              |

0x02: xCORE Tile control

## B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

-XMOS<sup>®</sup>

| Bits  | Perm | Init | Description                                               |

|-------|------|------|-----------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                  |

| 23:16 | RO   |      | Processor number.                                         |

| 15:9  | RO   | -    | Reserved                                                  |

| 8     | RO   |      | Overwrite BOOT_MODE.                                      |

| 7:6   | RO   | -    | Reserved                                                  |

| 5     | RO   |      | Indicates if core1 has been powered off                   |

| 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |

| 3     | RO   |      | Boot ROM boots from RAM                                   |

| 2     | RO   |      | Boot ROM boots from JTAG                                  |

| 1:0   | RO   |      | The boot PLL mode pin value.                              |

0x03: xCORE Tile boot status

| 0x07:<br>Ring | Bits  | Perm | Init | Description                   |

|---------------|-------|------|------|-------------------------------|

| Oscillator    | 31:16 | RO   | -    | Reserved                      |

| Value         | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.8 Ring Oscillator Value: 0x08

This register contains the current count of the xCORE Tile Wire ring oscillator. This value is not reset on a system reset.

**0x08** Ring Oscillator Value

| 08:<br>ing | Bits  | Perm | Init | Description                   |

|------------|-------|------|------|-------------------------------|

| tor        | 31:16 | RO   | -    | Reserved                      |

| lue        | 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.9 Ring Oscillator Value: 0x09

This register contains the current count of the Peripheral Cell ring oscillator. This value is not reset on a system reset.

**0x09:** Ring Oscillator Value

| Bits  | Perm | Init | Description                   |

|-------|------|------|-------------------------------|

| 31:16 | RO   | -    | Reserved                      |

| 15:0  | RO   | 0    | Ring oscillator Counter data. |

#### B.10 Ring Oscillator Value: 0x0A

This register contains the current count of the Peripheral Wire ring oscillator. This value is not reset on a system reset.

**0x0A:** Ring Oscillator Value

| A:<br>ng | Bits  | Perm | Init | Description                   |

|----------|-------|------|------|-------------------------------|

| or       | 31:16 | RO   | -    | Reserved                      |

| Je       | 15:0  | RO   | 0    | Ring oscillator Counter data. |

XMOS

#### B.11 RAM size: 0x0C

The size of the RAM in bytes

40

Bits

31:0

#### C.15 PC of logical core 6: 0x46

Value of the PC of logical core 6.

**0x46:** PC of logical core 6

Perm

Init

Description

CRO

Value.

#### C.16 PC of logical core 7: 0x47

Value of the PC of logical core 7.

0x47 PC of logical core 7

| <b>)x47:</b><br>gical | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| ore 7                 | 31:0 | CRO  |      | Value.      |

## C.17 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| <b>0x60:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 0                  | 31:0 | CRO  |      | Value.      |

## C.18 SR of logical core 1: 0x61

Value of the SR of logical core 1

**0x61** SR of logical core 1

| 51:<br>al | Bits | Perm | Init | Description |

|-----------|------|------|------|-------------|

| 21        | 31:0 | CRO  |      | Value.      |

## C.19 SR of logical core 2: 0x62

Value of the SR of logical core 2

**0x62:** SR of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## C.20 SR of logical core 3: 0x63

Value of the SR of logical core 3

0x63: SR of logical core 3

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## C.21 SR of logical core 4: 0x64

Value of the SR of logical core 4

Ox64:<br/>SR of logical<br/>core 4BitsPermInitDescription31:0CROValue.

#### C.22 SR of logical core 5: 0x65

Value of the SR of logical core 5

**0x65** SR of logical core 5

| 0x65:<br>ogical | Bits | Perm | Init | Description |  |

|-----------------|------|------|------|-------------|--|

| ore 5           | 31:0 | CRO  |      | Value.      |  |

## C.23 SR of logical core 6: 0x66

Value of the SR of logical core 6

**0x66:** SR of logical core 6

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

| Bits | Perm | Init | Description                                                    |

|------|------|------|----------------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                       |

| 4    | RW   |      | If set, external pin, is the source of last GlobalDebug event. |

| 3:2  | RO   | -    | Reserved                                                       |

| 1    | RW   |      | If set, XCore1 is the source of last GlobalDebug event.        |

| 0    | RW   |      | If set, XCore0 is the source of last GlobalDebug event.        |

**0x1F:** Debug source

## D.15 Link status, direction, and network: 0x20 .. 0x28

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links 0..7.

| Bits  | Perm | Init | Description                                                                                 |

|-------|------|------|---------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                    |

| 25:24 | RO   |      | Identify the SRC_TARGET type 0 - SLink, 1 - PLink, 2 - SSCTL, 3 - Undefine.                 |

| 23:16 | RO   |      | When the link is in use, this is the destination link number to which all packets are sent. |

| 15:12 | RO   | -    | Reserved                                                                                    |

| 11:8  | RW   | 0    | The direction that this link operates in.                                                   |

| 7:6   | RO   | -    | Reserved                                                                                    |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, reset as 0.                              |

| 3     | RO   | -    | Reserved                                                                                    |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                       |

| 1     | RO   |      | 1 when the dest side of the link is in use.                                                 |

| 0     | RO   |      | 1 when the source side of the link is in use.                                               |

0x20 .. 0x28: Link status, direction, and network

## D.16 PLink status and network: 0x40 .. 0x47

These registers contain status information and the network number that each processor-link belongs to.

## **E** USB Node Configuration

The USB node control registers can be accessed using configuration reads and writes (use write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device,  $\rightarrow$  ...) for reads and writes).

| Number | Perm | Description                       |  |

|--------|------|-----------------------------------|--|

| 0x00   | RO   | RO Device identification register |  |

| 0x04   | RW   | Node configuration register       |  |

| 0x05   | RW   | Node identifier                   |  |

| 0x51   | RW   | System clock frequency            |  |

| 0x80   | RW   | Link Control and Status           |  |

Figure 33: Summary

#### E.1 Device identification register: 0x00

This register contains version information, and information on power-on behavior.

0x00: Device identification register

| Bits  | Perm | Init | Description                      |

|-------|------|------|----------------------------------|

| 31:24 | RO   | 0x0F | Chip identifier                  |

| 23:16 | RO   | -    | Reserved                         |

| 15:8  | RO   | 0x02 | Revision number of the USB block |

| 7:0   | RO   | 0x00 | Version number of the USB block  |

#### E.2 Node configuration register: 0x04

This register is used to set the communication model to use (1 or 3 byte headers), and to prevent any further updates.

|                      | Bits | Perm | Init | Description                                                                                          |

|----------------------|------|------|------|------------------------------------------------------------------------------------------------------|

| <b>0x04:</b><br>Node | 31   | RW   | 0    | Set to 1 to disable further updates to the node configuration and link control and status registers. |

| iguration            | 30:1 | RO   | -    | Reserved                                                                                             |

| register             | 0    | RW   | 0    | Header mode. 0: 3-byte headers; 1: 1-byte headers.                                                   |

| 0x2C:    |  |

|----------|--|

| UIFM PID |  |

| Bits | Perm | Init | Description                     |

|------|------|------|---------------------------------|

| 31:4 | RO   | -    | Reserved                        |

| 3:0  | RO   | 0    | Value of the last received PID. |

#### F.13 UIFM Endpoint: 0x30

The last endpoint seen

**0x30** UIFM Endpoint

|         | Bits | Perm | Init | Description                           |

|---------|------|------|------|---------------------------------------|

| 0:      | 31:5 | RO   | -    | Reserved                              |

| и.<br>И | 4    | RO   | 0    | 1 if endpoint contains a valid value. |

| t       | 3:0  | RO   | 0    | A copy of the last received endpoint. |

#### F.14 UIFM Endpoint match: 0x34

This register can be used to mark UIFM endpoints as special.

**0x34:** UIFM Endpoint match

| Bits  | Perm | Init | Description                                                                                                                          |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | -    | Reserved                                                                                                                             |

| 15:0  | RW   | 0    | This register contains a bit for each endpoint. If its bit is set, the endpoint will be supplied on the RX port when ORed with 0x10. |

## F.15 OTG Flags mask: 0x38

**0x38** OTG Flags mask

| 8:<br>s | Bits | Perm | Init | Description |

|---------|------|------|------|-------------|

| k       | 31:0 | RW   | 0    | Data        |

## F.16 UIFM power signalling: 0x3C

|                   | Bits | Perm | Init | Description |

|-------------------|------|------|------|-------------|

| 0x3C:             | 31:9 | RO   | -    | Reserved    |

| <b>UIFM</b> power | 8    | RW   | 0    | Valid       |

| signalling        | 7:0  | RW   | 0    | Data        |

## L Revision History

| Date       | Description                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------|

| 2015-03-20 | Preliminary release                                                                                 |

| 2015-04-14 | Added RST to pins to be pulled hard, and removed reference to TCK from Errata                       |

|            | Removed TRST_N references in packages that have no TRST_N                                           |

|            | New diagram for boot from embedded flash showing ports                                              |

|            | Pull up requirements for shared clock and external resistor for QSPI                                |

| 2015-05-06 | Removed references to DEBUG_N                                                                       |

| 2015-07-09 | Updated electrical characteristics - Section 13                                                     |

| 2015-08-19 | Added I(USB_VDD) - Section 13                                                                       |

|            | Added USB layout guidelines - Section 12                                                            |

| 2015-08-27 | Updated part marking and product code - Section 15                                                  |

| 2015-11-23 | Updated status of X2D04, X2D05, X2D06, X2D07 during boot - Section 8                                |

|            | Updated Schematics Design Checklist: GPIO for X2D04, X2D05, X2D06, X2D07<br>during boot - Section H |

| 2015-12-18 | Clarified connectivity of internal and external xCONNECT links - Sections 3 and 4                   |

|            | Made pin names canonical - Sections 3 and 4                                                         |

|            | Updated JTAG diagram - Section 11                                                                   |

|            | Removed references to 400MHz parts - Section 13                                                     |

| 2016-01-05 | Updated signal tables to use VDDIO - Section 4                                                      |

|            | Updated IDD value - Section 13                                                                      |

|            | Updated land pattern description - Section 12.3                                                     |

| 2016-04-20 | Typical internal pull-up and pull down current diagrams added - Section 13                          |

# XMOS®

Copyright © 2016, All Rights Reserved.

Xmos Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. Xmos Ltd. makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.