### STMicroelectronics - <u>SPC56EL70L5CBFR Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                 |

| Core Size                  | 32-Bit Dual-Core                                                        |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, LINbus, SCI, SPI, UART/USART                                    |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                 |

| Number of I/O              | 96                                                                      |

| Program Memory Size        | 2MB (2M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 192К х 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.63V                                                              |

| Data Converters            | A/D 32x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc56el70l5cbfr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| F                  | Feature                                                                           | SPC56EL64 SPC56EL70 SPC564L64 SPC564                                                                       |                                    |        |  |  |  |  |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------|--------|--|--|--|--|--|--|--|--|--|

|                    | Deserial Serial<br>Peripheral<br>Interface (DSPI)                                 |                                                                                                            | 3 × DSPI as many as 8 chip selects |        |  |  |  |  |  |  |  |  |  |

| Modules<br>(cont.) | Cyclic<br>Redundancy<br>Checker (CRC)<br>unit                                     | Yes                                                                                                        |                                    |        |  |  |  |  |  |  |  |  |  |

|                    | Junction<br>temperature<br>sensor<br>(TSENS)                                      | Yes, replicated module                                                                                     |                                    |        |  |  |  |  |  |  |  |  |  |

|                    | Digital I/Os                                                                      |                                                                                                            |                                    | t 16   |  |  |  |  |  |  |  |  |  |

|                    | Device power<br>supply                                                            | 3.3 V with integrated bypassable ballast transistor<br>External ballast transistor not needed for bare die |                                    |        |  |  |  |  |  |  |  |  |  |

| Supply             | Analog<br>reference<br>voltage                                                    | 3.0 V – 3.6 V and 4.5 V – 5.5 V                                                                            |                                    |        |  |  |  |  |  |  |  |  |  |

|                    | Frequency-<br>modulated<br>phase-locked<br>loop (FMPLL)                           | 2                                                                                                          |                                    |        |  |  |  |  |  |  |  |  |  |

| Clocking           | Internal RC<br>oscillator                                                         | 16 MHz                                                                                                     |                                    |        |  |  |  |  |  |  |  |  |  |

|                    | External crystal oscillator                                                       | 4 – 40 MHz                                                                                                 |                                    |        |  |  |  |  |  |  |  |  |  |

| Debug              | Nexus                                                                             |                                                                                                            | Le                                 | vel 3+ |  |  |  |  |  |  |  |  |  |

| Package<br>s       | LQFP                                                                              | 100 pins<br>144 pins                                                                                       |                                    |        |  |  |  |  |  |  |  |  |  |

|                    | Temperature<br>range (junction)                                                   | –40 to 150 °C                                                                                              |                                    |        |  |  |  |  |  |  |  |  |  |

| Temperat<br>ure    | Ambient<br>temperature<br>range using<br>external ballast<br>transistor<br>(LQFP) | –40 to 125 °C                                                                                              |                                    |        |  |  |  |  |  |  |  |  |  |

Table 1. SPC56XL70/SPC56X64 device summary (continued)

1. The third eTimer is not connected to any pins on the package. Its usage is confined internally to the device.

2. The second FlexPWM is not connected to any pins on the package. Its usage is confined internally to the device.

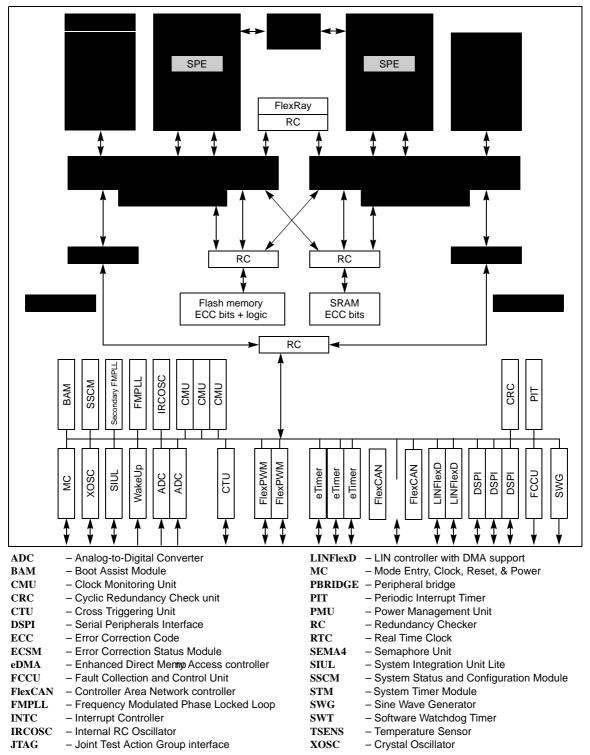

## 1.4 Block diagram

*Figure 1* shows a top-level block diagram of the SPC56EL70x/SPC564L70x device.

DocID023953 Rev 5

## **1.5** Feature details

### 1.5.1 High-performance e200z4d core

The e200z4d Power Architecture<sup>®</sup> core provides the following features:

- x 2 independent execution units, both supporting fixed-point and floating-point operations

- x Dual issue 32-bit Power Architecture technology compliant

- 5-stage pipeline (IF, DEC, EX1, EX2, WB)

- In-order execution and instruction retirement

- x Full support for Power Architecture instruction set and Variable Length Encoding (VLE)

- Mix of classic 32-bit and 16-bit instruction allowed

- Optimization of code size possible

- x Thirty-two 64-bit general purpose registers (GPRs)

- x Harvard bus (32-bit address, 64-bit data)

- I-Bus interface capable of one outstanding transaction plus one piped with no waiton-data return

- D-Bus interface capable of two transactions outstanding to fill AHB pipe

- x I-cache and I-cache controller

- 4 KB, 256-bit cache line (programmable for 2- or 4-way)

- x No data cache

- x 16-entry MMU

- x 8-entry branch table buffer

- x Branch look-ahead instruction buffer to accelerate branching

- x Dedicated branch address calculator

- x 3 cycles worst case for missed branch

- x Load/store unit

- Fully pipelined

- Single-cycle load latency

- Big- and little-endian modes supported

- Misaligned access support

- Single stall cycle on load to use

- x Single-cycle throughput (2-cycle latency) integer 32 × 32 multiplication

- x 4 14 cycles integer 32 × 32 division (average division on various benchmark of nine cycles)

- x Single precision floating-point unit

- 1 cycle throughput (2-cycle latency) floating-point 32 × 32 multiplication

- Target 9 cycles (worst case acceptable is 12 cycles) throughput floating-point 32 x 32 division

- Special square root and min/max function implemented

- x Signal processing support: APU-SPE 1.1

- Support for vectorized mode: as many as two floating-point instructions per clock

- x Vectored interrupt support

- x Reservation instruction to support read-modify-write constructs

### 1.5.19 System timer module (STM)

The STM implements the following features:

- x Up-counter with 4 output compare registers

- x OS task protection and hardware tick implementation per AUTOSAR<sup>(a)</sup> requirement

The STM is replicated for each processor.

#### 1.5.20 Software watchdog timer (SWT)

This module implements the following features:

- x Fault tolerant output

- x Safe internal RC oscillator as reference clock

- x Windowed watchdog

- x Program flow control monitor with 16-bit pseudorandom key generation

- x Allows a high level of safety (SIL3 monitor)

The SWT module is replicated for each processor.

### **1.5.21** Fault collection and control unit (FCCU)

The FCCU module has the following features:

- x Redundant collection of hardware checker results

- x Redundant collection of error information and latch of faults from critical modules on the device

- x Collection of self-test results

- x Configurable and graded fault control

- Internal reactions (no internal reaction, IRQ, Functional Reset, Destructive Reset, or Safe mode entered)

- External reaction (failure is reported to the external/surrounding system via configurable output pins)

## 1.5.22 System Integration Unit Lite (SIUL)

The SIUL controls MCU reset configuration, pad configuration, external interrupt, general purpose I/O (GPIO), internal peripheral multiplexing, and system reset operation. The reset configuration block contains the external pin boot configuration logic. The pad configuration block controls the static electrical characteristics of I/O pins. The GPIO block provides uniform and discrete input/output control of the I/O pins of the MCU.

a. Automotive Open System Architecture

The FlexCAN module provides the following features:

- x Full implementation of the CAN protocol specification, version 2.0B

- Standard data and remote frames

- Extended data and remote frames

- 0 to 8 bytes data length

- Programmable bit rate as fast as 1Mbit/s

- x 32 message buffers of 0 to 8 bytes data length

- x Each message buffer configurable as receive or transmit buffer, all supporting standard and extended messages

- x Programmable loop-back mode supporting self-test operation

- x 3 programmable mask registers

- x Programmable transmit-first scheme: lowest ID or lowest buffer number

- x Time stamp based on 16-bit free-running timer

- x Global network time, synchronized by a specific message

- x Maskable interrupts

- x Independent of the transmission medium (an external transceiver is assumed)

- x High immunity to EMI

- x Short latency time due to an arbitration scheme for high-priority messages

- x Transmit features

- Supports configuration of multiple mailboxes to form message queues of scalable depth

- Arbitration scheme according to message ID or message buffer number

- Internal arbitration to guarantee no inner or outer priority inversion

- Transmit abort procedure and notification

- x Receive features

- Individual programmable filters for each mailbox

- 8 mailboxes configurable as a 6-entry receive FIFO

- 8 programmable acceptance filters for receive FIFO

- x Programmable clock source

- System clock

- Direct oscillator clock to avoid FMPLL jitter

### 1.5.28 Serial communication interface module (LINFlexD)

The LINFlexD module (LINFlex with DMA support) on this device features the following:

- x Supports LIN Master mode, LIN Slave mode and UART mode

- x LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- x Manages LIN frame transmission and reception without CPU intervention

- x LIN features

- Autonomous LIN frame handling

- Message buffer to store as many as 8 data bytes

- Supports messages as long as 64 bytes

- Detection and flagging of LIN errors (Sync field, delimiter, ID parity, bit framing, checksum and Time-out errors)

- Classic or extended checksum calculation

- Configurable break duration of up to 50-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features (Loop back, LIN bus stuck dominant detection)

- Interrupt driven operation with 16 interrupt sources

- x LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- x UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

## 3.17 SWG electrical characteristics

| Querra la cl | Desemptor                             | Value   |         |         |  |  |  |  |  |

|--------------|---------------------------------------|---------|---------|---------|--|--|--|--|--|

| Symbol       | Parameter                             | Minimum | Typical | Maximum |  |  |  |  |  |

| Т            | Input clock                           | 12 MHz  | 16 MHz  | 20 MHz  |  |  |  |  |  |

| Т            | Frequency Range                       | 1KHz    | —       | 50 KHz  |  |  |  |  |  |

| т            | Peak to Peak <sup>(1)</sup>           | 0.4 V   | —       | 2.0V    |  |  |  |  |  |

| Т            | Peak to Peak variation <sup>(2)</sup> | -6%     | —       | 6%      |  |  |  |  |  |

| Т            | Common Mode <sup>(3)</sup>            | —       | 1.3 V   | —       |  |  |  |  |  |

| Т            | Common Mode variation                 | -6%     | —       | 6%      |  |  |  |  |  |

| Т            | SiNAD <sup>(4)</sup>                  | 45 dB   | —       | —       |  |  |  |  |  |

| Т            | Load C                                | 25 pF   | —       | 100 pF  |  |  |  |  |  |

| Т            | Load I                                | 0 μΑ    | —       | 100 µA  |  |  |  |  |  |

| Т            | ESD Pad Resistance <sup>(5)</sup>     | 230 :   | —       | 360 :   |  |  |  |  |  |

Table 29. SPC56XL70 SWG Specifications

1. Peak to Peak value is measured with no R or I load.

2. Peak to Peak excludes noise, SiNAD must be considered.

3. Common mode value is measured with no R or I load.

4. SiNAD is measured at Max Peak to Peak voltage.

5. Internal device routing resistance. ESD pad resistance is in series and must be considered for max Peak to Peak voltages, depending on application I load and/or R load.

# 3.18 AC specifications

### 3.18.1 Pad AC specifications

Table 30. Pad AC specificati ons  $(3.3 \text{ V}, \text{IPP}_\text{HVE} = 0)^{(1)}$

| No | No Pad   |          | Tswitchon <sup>1</sup><br>(ns) |        | Rise/Fall <sup>(2)</sup><br>(ns) |          |     | Frequency<br>(MHz) |     |     | Current slew <sup>(3)</sup><br>(mA/ns) |                  |       | Load<br>drive |      |      |     |   |

|----|----------|----------|--------------------------------|--------|----------------------------------|----------|-----|--------------------|-----|-----|----------------------------------------|------------------|-------|---------------|------|------|-----|---|

|    |          |          | Min                            | Тур    | Max                              | Min      | Тур | Max                | Min | Тур | Мах                                    | Min <sup>-</sup> | Typ N | lax           | (pF) |      |     |   |

|    | 1 Slow   | Slow     |                                | 3      | —                                | 40       | —   | —                  | 40  | —   | —                                      | 4                | 0.01  | —             | 2    | 25   |     |   |

| 1  |          |          | Slow T                         | Slow T | Slow                             | <b>–</b> | 3   | —                  | 40  | —   | —                                      | 50               | —     | —             | 2    | 0.01 | —   | 2 |

| 1  |          |          | '                              | 3      | —                                | 40       | —   | —                  | 75  | —   | —                                      | 2                | 0.01  | —             | 2    | 100  |     |   |

|    |          |          | 3                              | —      | 40                               | —        | —   | 100                | —   | —   | 2                                      | 0.01             | —     | 2             | 200  |      |     |   |

|    | 2 Medium | Medium T |                                | 1      | _                                | 15       | —   | —                  | 12  | _   | —                                      | 40               | 2.5   | —             | 7    | 25   |     |   |

| 2  |          |          | Medium T                       | т      | 1                                |          | 15  | —                  | —   | 25  | —                                      | —                | 20    | 2.5           | —    | 7    | 50  |   |

|    |          |          |                                |        | 1                                | _        | 15  | —                  | —   | 40  |                                        | _                | 13    | 2.5           | _    | 7    | 100 |   |

|    |          |          |                                | 1      | —                                | 15       | —   | —                  | 70  |     | —                                      | 7                | 2.5   | —             | 7    | 200  |     |   |

| No | Pad       |        | Tswitchon <sup>1</sup><br>(ns) |     |     | Rise/Fall <sup>(2)</sup><br>(ns) |     |     | Frequency<br>(MHz) |     |     | Current slew <sup>(3)</sup><br>(mA/ns) |     |     | Load<br>drive |

|----|-----------|--------|--------------------------------|-----|-----|----------------------------------|-----|-----|--------------------|-----|-----|----------------------------------------|-----|-----|---------------|

|    |           |        |                                | Тур | Max | Min                              | Тур | Max | Min                | Тур | Max | Min                                    | Тур | Max | (pF)          |

|    | 3 Fast T  |        | 1                              | —   | 6   | —                                | _   | 4   | —                  | —   | 72  | 3                                      |     | 40  | 25            |

| 2  |           | Fact T | 1                              | _   | 6   | _                                | _   | 7   | —                  | —   | 55  | 7                                      | —   | 40  | 50            |

| 3  |           | 1      | 1                              | _   | 6   | _                                | _   | 12  | —                  | —   | 40  | 7                                      | —   | 40  | 100           |

|    |           |        | 1                              | _   | 6   | _                                | _   | 18  | —                  | —   | 25  | 7                                      | —   | 40  | 200           |

| 4  | Symmetric | Т      | 1                              | _   | 8   | _                                | _   | 5   | _                  |     | 50  | 3                                      |     | 25  | 25            |

#### Table 30. Pad AC specifications (3.3 V, IPP\_HVE = 0)<sup>(1)</sup> (continued)

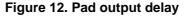

Propagation delay from V<sub>DD\_HV\_IOx</sub>/2 of internal signal to Pchannel/Nchannel switch-on condition (i.e. t\_PHL and t\_PLH in Figure 12: Pad output delay).

2. Slope at rising/falling edge(i.e. t\_F and t\_R in *Figure 12: Pad output delay*).

3. Data based on characterization results, not tested in production.

[1]  $t_F$  and  $t_R$  are transient times at the FAR END.

[2]  $t_{PHL}$  and  $t_{PLH}$  are measured at the pad.

[3] Core input slew = 1ns (0 to vdd).

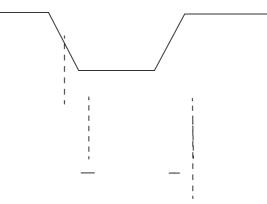

## 3.19 Reset sequence

This section shows the duration for different reset sequences. It describes the different reset sequences and it specifies the start conditions and the end indication for the reset sequences.

### 3.19.1 Reset sequence duration

*Table 31* specifies the minimum and the maximum reset sequence duration for the five different reset sequences described in *Section 3.19.2: Reset sequence description*.

#### Figure 17. Functional Reset Sequence Short

The reset sequences shown in *Figure 16* and *Figure 17* are triggered by functional reset events. RESET is driven low during these two reset sequences **only if** the corresponding functional reset source (which triggered the reset sequence) was enabled to drive RESET low for the duration of the internal reset sequence<sup>(c)</sup>.

#### 3.19.3 Reset sequence trigger mapping

The following table shows the possible trigger events for the different reset sequences. It specifies the reset sequence start conditions as well as the reset sequence end indications that are the basis for the timing data provided in *Table 31*.

#### Table 32. Reset sequence trigger — Reset sequence

|                              |                                         | Reset Sequence                         |                                                                     |                                                          |                                                                   |  |  |  |  |

|------------------------------|-----------------------------------------|----------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| Reset<br>Sequence<br>Trigger | Reset<br>Sequence<br>Start<br>Condition | Reset<br>Sequence<br>End<br>Indication | Destructive<br>reset<br>sequence,<br>bist<br>enabled <sup>(1)</sup> | Destructive<br>reset<br>sequence,<br>bisT<br>disabled(1) | External<br>reset<br>sequence drure23 re23 re23 re23d(S114.sere23 |  |  |  |  |

sss q67Tc.1

c. See RGM\_FBRE register for more details.

3. The system clock frequency needs to be four times faster than the TCK frequency.

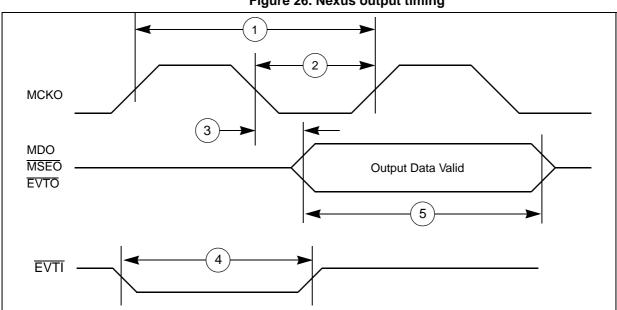

Figure 26. Nexus output timing

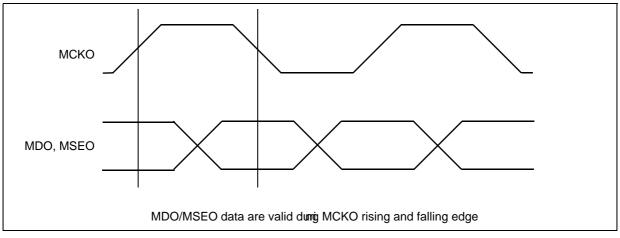

Figure 27. Nexus DDR Mode output timing

Figure 33. DSPI classic SP I timing — slave, CPHA = 1

Figure 34. DSPI modified transfer format timing — master, CPHA = 0