Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1934-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                               | Function            | Input<br>Type | Output<br>Type | Description                                                   |

|--------------------------------------------------------------------|---------------------|---------------|----------------|---------------------------------------------------------------|

| RA0/AN0/C12IN0-/C2OUT <sup>(1)</sup> /                             | RA0                 | TTL           | CMOS           | General purpose I/O.                                          |

| SRNQ <sup>(1)</sup> /SS <sup>(1)</sup> /VCAP <sup>(2)</sup> /SEG12 | AN0                 | AN            | —              | A/D Channel 0 input.                                          |

|                                                                    | C12IN0-             | AN            | _              | Comparator C1 or C2 negative input.                           |

|                                                                    | C2OUT               | _             | CMOS           | Comparator C2 output.                                         |

|                                                                    | SRNQ                | _             | CMOS           | SR Latch inverting output.                                    |

|                                                                    | SS                  | ST            | _              | Slave Select input.                                           |

|                                                                    | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1934/6/7 only). |

|                                                                    | SEG12               |               | AN             | LCD Analog output.                                            |

| RA1/AN1/C12IN1-/SEG7                                               | RA1                 | TTL           | CMOS           | General purpose I/O.                                          |

|                                                                    | AN1                 | AN            |                | A/D Channel 1 input.                                          |

|                                                                    | C12IN1-             | AN            | _              | Comparator C1 or C2 negative input.                           |

|                                                                    | SEG7                | _             | AN             | LCD Analog output.                                            |

| RA2/AN2/C2IN+/VREF-/                                               | RA2                 | TTL           | CMOS           | General purpose I/O.                                          |

| DACOUT/COM2                                                        | AN2                 | AN            | _              | A/D Channel 2 input.                                          |

|                                                                    | C2IN+               | AN            |                | Comparator C2 positive input.                                 |

|                                                                    | VREF-               | AN            | _              | A/D Negative Voltage Reference input.                         |

|                                                                    | DACOUT              | _             | AN             | Voltage Reference output.                                     |

|                                                                    | COM2                | _             | AN             | LCD Analog output.                                            |

| RA3/AN3/C1IN+/VREF+/                                               | RA3                 | TTL           | CMOS           | General purpose I/O.                                          |

| COM3 <sup>(3)</sup> /SEG15                                         | AN3                 | AN            |                | A/D Channel 3 input.                                          |

|                                                                    | C1IN+               | AN            | —              | Comparator C1 positive input.                                 |

|                                                                    | VREF+               | AN            |                | A/D Voltage Reference input.                                  |

|                                                                    | COM3 <sup>(3)</sup> | _             | AN             | LCD Analog output.                                            |

|                                                                    | SEG15               | _             | AN             | LCD Analog output.                                            |

| RA4/C1OUT/CPS6/T0CKI/SRQ/                                          | RA4                 | TTL           | CMOS           | General purpose I/O.                                          |

| CCP5/SEG4                                                          | C10UT               | _             | CMOS           | Comparator C1 output.                                         |

|                                                                    | CPS6                | AN            |                | Capacitive sensing input 6.                                   |

|                                                                    | TOCKI               | ST            |                | Timer0 clock input.                                           |

|                                                                    | SRQ                 |               | CMOS           | SR Latch non-inverting output.                                |

|                                                                    | CCP5                | ST            | CMOS           | Capture/Compare/PWM5.                                         |

|                                                                    | SEG4                |               | AN             | LCD Analog output.                                            |

| RA5/AN4/C2OUT <sup>(1)</sup> /CPS7/                                | RA5                 | TTL           | CMOS           | General purpose I/O.                                          |

| SRNQ <sup>(1)</sup> /SS <sup>(1)</sup> /VCAP <sup>(2)</sup> /SEG5  | AN4                 | AN            | _              | A/D Channel 4 input.                                          |

|                                                                    | C2OUT               |               | CMOS           | Comparator C2 output.                                         |

|                                                                    | CPS7                | AN            | —              | Capacitive sensing input 7.                                   |

|                                                                    | SRNQ                | _             | CMOS           | SR Latch inverting output.                                    |

|                                                                    | SS                  | ST            | _              | Slave Select input.                                           |

|                                                                    | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1934/6/7 only). |

|                                                                    | SEG5                | _             | AN             | LCD Analog output.                                            |

TABLE 1-2: PIC16(L)F1934/6/7 PINOUT DESCRIPTION

Legend:AN= Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $l^2C^{TM}$ = Schmitt Trigger input with l<sup>2</sup>C

HV = High Voltage XTAL = Crystal

levels

**Note 1:** Pin function is selectable via the APFCON register.

2: PIC16F1934/6/7 devices only.

3: PIC16(L)F1936 devices only.

4: PORTD is available on PIC16(L)F1934/7 devices only.

5: RE<2:0> are available on PIC16(L)F1934/7 devices only.

© 2008-2011 Microchip Technology Inc.

## TABLE 3-7: PIC16(L)F1934/6/7 MEMORY MAP, BANKS 16-23

| IADL  | -E 3-7. FI                   |       | L)F1934/0//                  |      | UNI WAF, D                   | MIN   | 3 10-23                      |      |                              |      |                              |      |                              |        |                              |

|-------|------------------------------|-------|------------------------------|------|------------------------------|-------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|--------|------------------------------|

|       | BANK 16                      |       | BANK 17                      |      | BANK 18                      |       | BANK 19                      |      | BANK 20                      |      | BANK 21                      |      | BANK 22                      |        | BANK 23                      |

| 800h  | INDF0                        | 880h  | INDF0                        | 900h | INDF0                        | 980h  | INDF0                        | A00h | INDF0                        | A80h | INDF0                        | B00h | INDF0                        | B80h   | INDF0                        |

| 801h  | INDF1                        | 881h  | INDF1                        | 901h | INDF1                        | 981h  | INDF1                        | A01h | INDF1                        | A81h | INDF1                        | B01h | INDF1                        | B81h   | INDF1                        |

| 802h  | PCL                          | 882h  | PCL                          | 902h | PCL                          | 982h  | PCL                          | A02h | PCL                          | A82h | PCL                          | B02h | PCL                          | B82h   | PCL                          |

| 803h  | STATUS                       | 883h  | STATUS                       | 903h | STATUS                       | 983h  | STATUS                       | A03h | STATUS                       | A83h | STATUS                       | B03h | STATUS                       | B83h   | STATUS                       |

| 804h  | FSR0L                        | 884h  | FSR0L                        | 904h | FSR0L                        | 984h  | FSR0L                        | A04h | FSR0L                        | A84h | FSR0L                        | B04h | FSR0L                        | B84h   | FSR0L                        |

| 805h  | FSR0H                        | 885h  | FSR0H                        | 905h | FSR0H                        | 985h  | FSR0H                        | A05h | FSR0H                        | A85h | FSR0H                        | B05h | FSR0H                        | B85h   | FSR0H                        |

| 806h  | FSR1L                        | 886h  | FSR1L                        | 906h | FSR1L                        | 986h  | FSR1L                        | A06h | FSR1L                        | A86h | FSR1L                        | B06h | FSR1L                        | B86h   | FSR1L                        |

| 807h  | FSR1H                        | 887h  | FSR1H                        | 907h | FSR1H                        | 987h  | FSR1H                        | A07h | FSR1H                        | A87h | FSR1H                        | B07h | FSR1H                        | B87h   | FSR1H                        |

| 808h  | BSR                          | 888h  | BSR                          | 908h | BSR                          | 988h  | BSR                          | A08h | BSR                          | A88h | BSR                          | B08h | BSR                          | B88h   | BSR                          |

| 809h  | WREG                         | 889h  | WREG                         | 909h | WREG                         | 989h  | WREG                         | A09h | WREG                         | A89h | WREG                         | B09h | WREG                         | B89h   | WREG                         |

| 80Ah  | PCLATH                       | 88Ah  | PCLATH                       | 90Ah | PCLATH                       | 98Ah  | PCLATH                       | A0Ah | PCLATH                       | A8Ah | PCLATH                       | B0Ah | PCLATH                       | B8Ah   | PCLATH                       |

| 80Bh  | INTCON                       | 88Bh  | INTCON                       | 90Bh | INTCON                       | 98Bh  | INTCON                       | A0Bh | INTCON                       | A8Bh | INTCON                       | B0Bh | INTCON                       | B8Bh   | INTCON                       |

| 80Ch  | —                            | 88Ch  | —                            | 90Ch | —                            | 98Ch  | —                            | A0Ch | —                            | A8Ch | —                            | B0Ch | —                            | B8Ch   | —                            |

| 80Dh  | —                            | 88Dh  | _                            | 90Dh | —                            | 98Dh  | _                            | A0Dh | _                            | A8Dh | _                            | B0Dh | —                            | B8Dh   | —                            |

| 80Eh  | -                            | 88Eh  |                              | 90Eh | _                            | 98Eh  |                              | A0Eh |                              | A8Eh |                              | B0Eh | _                            | B8Eh   | —                            |

| 80Fh  | —                            | 88Fh  | _                            | 90Fh | _                            | 98Fh  | _                            | A0Fh | _                            | A8Fh | _                            | B0Fh | —                            | B8Fh   | —                            |

| 810h  | _                            | 890h  | _                            | 910h | _                            | 990h  |                              | A10h |                              | A90h |                              | B10h | _                            | B90h   | _                            |

| 811h  |                              | 891h  |                              | 911h | _                            | 991h  |                              | A11h |                              | A91h |                              | B11h | _                            | B91h   | —                            |

| 812h  | -                            | 892h  |                              | 912h | _                            | 992h  |                              | A12h |                              | A92h |                              | B12h | _                            | B92h   | —                            |

| 813h  | -                            | 893h  |                              | 913h | _                            | 993h  |                              | A13h |                              | A93h |                              | B13h | _                            | B93h   | —                            |

| 814h  |                              | 894h  |                              | 914h | _                            | 994h  |                              | A14h |                              | A94h |                              | B14h | _                            | B94h   | —                            |

| 815h  | -                            | 895h  |                              | 915h | _                            | 995h  |                              | A15h |                              | A95h |                              | B15h | _                            | B95h   | —                            |

| 816h  | —                            | 896h  | _                            | 916h | —                            | 996h  | _                            | A16h | _                            | A96h | _                            | B16h | —                            | B96h   | —                            |

| 817h  | _                            | 897h  | _                            | 917h | _                            | 997h  | _                            | A17h | _                            | A97h | _                            | B17h | —                            | B97h   | _                            |

| 818h  | _                            | 898h  | _                            | 918h | _                            | 998h  | _                            | A18h | _                            | A98h | _                            | B18h | —                            | B98h   | _                            |

| 819h  | —                            | 899h  | —                            | 919h | —                            | 999h  | —                            | A19h | —                            | A99h | —                            | B19h | —                            | B99h   | —                            |

| 81Ah  | —                            | 89Ah  | —                            | 91Ah | —                            | 99Ah  | —                            | A1Ah | —                            | A9Ah | —                            | B1Ah | —                            | B9Ah   | —                            |

| 81Bh  | _                            | 89Bh  | _                            | 91Bh | _                            | 99Bh  | _                            | A1Bh | _                            | A9Bh | _                            | B1Bh | —                            | B9Bh   | _                            |

| 81Ch  | _                            | 89Ch  | _                            | 91Ch | _                            | 99Ch  |                              | A1Ch |                              | A9Ch |                              | B1Ch | _                            | B9Ch   | _                            |

| 81Dh  | _                            | 89Dh  | _                            | 91Dh | _                            | 99Dh  | _                            | A1Dh | _                            | A9Dh | _                            | B1Dh | —                            | B9Dh   | _                            |

| 81Eh  | _                            | 89Eh  | _                            | 91Eh | _                            | 99Eh  | _                            | A1Eh | _                            | A9Eh | _                            | B1Eh | —                            | B9Eh   | _                            |

| 81Fh  | _                            | 89Fh  | _                            | 91Fh | _                            | 99Fh  |                              | A1Fh |                              | A9Fh |                              | B1Fh | _                            | B9Fh   | —                            |

| 820h  |                              | 8A0h  |                              | 920h |                              | 9A0h  |                              | A20h |                              | AA0h |                              | B20h |                              | BA0h   |                              |

|       | Unimplemented<br>Read as '0' |       | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |       | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |      | Unimplemented<br>Read as '0' |        | Unimplemented<br>Read as '0' |

| 86Fh  |                              | 8EFh  |                              | 96Fh |                              | 9EFh  |                              | A6Fh |                              | AEFh |                              | B6Fh |                              | BEFh   |                              |

| 870h  |                              | 8F0h  |                              | 970h |                              | 9F0h  |                              | A70h |                              | AF0h |                              | B70h |                              | BF0h   |                              |

| 57011 | Accesses<br>70h – 7Fh        | 0.011 | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        | 0.011 | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        | 2.01 | Accesses<br>70h – 7Fh        | 2. 011 | Accesses<br>70h – 7Fh        |

| 87Fh  |                              | 8FFh  |                              | 97Fh |                              | 9FFh  |                              | A7Fh |                              | AFFh |                              | B7Fh |                              | BFFh   |                              |

|       |                              |       |                              |      |                              |       |                              |      |                              |      |                              |      |                              |        |                              |

Legend: = Unimplemented data memory locations, read as '0'.

| Address                | Name    | Bit 7         | Bit 6                                                                                                   | Bit 5          | Bit 4           | Bit 3          | Bit 2      | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|---------------|---------------------------------------------------------------------------------------------------------|----------------|-----------------|----------------|------------|-------|-------|----------------------|---------------------------------|

| Bank 4                 |         |               |                                                                                                         |                |                 |                |            |       |       |                      | _                               |

| 200h <sup>(2)</sup>    | INDF0   |               | this location u cal register)                                                                           | ses contents c | of FSR0H/FSF    | ROL to address | data memor | ý     |       | XXXX XXXX            | XXXX XXXX                       |

| 201h <sup>(2)</sup>    | INDF1   |               | ddressing this location uses contents of FSR1H/FSR1L to address data memory<br>not a physical register) |                |                 |                |            |       |       |                      | XXXX XXXX                       |

| 202h <sup>(2)</sup>    | PCL     | Program Co    | Program Counter (PC) Least Significant Byte                                                             |                |                 |                |            |       |       |                      | 0000 0000                       |

| 203h <sup>(2)</sup>    | STATUS  | _             | <u>TO</u> <u>PD</u> Z <u>DC</u> C                                                                       |                |                 |                |            |       |       |                      | q quuu                          |

| 204h <sup>(2)</sup>    | FSR0L   | Indirect Data | a Memory Add                                                                                            | Iress 0 Low Po | ointer          |                |            |       |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(2)</sup>    | FSR0H   | Indirect Data | a Memory Add                                                                                            | lress 0 High P | ointer          |                |            |       |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(2)</sup>    | FSR1L   | Indirect Data | a Memory Add                                                                                            | Iress 1 Low Po | pinter          |                |            |       |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(2)</sup>    | FSR1H   | Indirect Data | a Memory Add                                                                                            | lress 1 High P | ointer          |                |            |       |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(2)</sup>    | BSR     | _             | _                                                                                                       | _              |                 | E              | BSR<4:0>   |       |       | 0 0000               | 0 0000                          |

| 209h <sup>(2)</sup>    | WREG    | Working Re    | gister                                                                                                  |                |                 |                |            |       |       | 0000 0000            | uuuu uuuu                       |

| 20Ah <sup>(1, 2)</sup> | PCLATH  | _             | Write Buffer f                                                                                          | or the upper 7 | bits of the Pro | ogram Counter  | r          |       |       | -000 0000            | -000 0000                       |

| 20Bh <sup>(2)</sup>    | INTCON  | GIE           | PEIE                                                                                                    | TMR0IE         | INTE            | IOCIE          | TMR0IF     | INTF  | IOCIF | 0000 0000            | 0000 0000                       |

| 20Ch                   | —       | Unimpleme     | nted                                                                                                    |                |                 |                | •          | •     |       | _                    | —                               |

| 20Dh                   | WPUB    | WPUB7         | WPUB6                                                                                                   | WPUB5          | WPUB4           | WPUB3          | WPUB2      | WPUB1 | WPUB0 | 1111 1111            | 1111 1111                       |

| 20Eh                   |         | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | _                    | —                               |

| 20Fh                   | _       | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | _                    | _                               |

| 210h                   | WPUE    |               | _                                                                                                       | _              | _               | WPUE3          | _          | _     | _     | 1                    | 1                               |

| 211h                   | SSPBUF  | Synchronou    | us Serial Port F                                                                                        | Receive Buffer | /Transmit Reg   | jister         |            |       |       | xxxx xxxx            | uuuu uuuu                       |

| 212h                   | SSPADD  |               |                                                                                                         |                | ADD<            | 7:0>           |            |       |       | 0000 0000            | 0000 0000                       |

| 213h                   | SSPMSK  |               |                                                                                                         |                | MSK<            | 7:0>           |            |       |       | 1111 1111            | 1111 1111                       |

| 214h                   | SSPSTAT | SMP           | CKE                                                                                                     | D/A            | Р               | S              | R/W        | UA    | BF    | 0000 0000            | 0000 0000                       |

| 215h                   | SSPCON1 | WCOL          | SSPOV                                                                                                   | SSPEN          | CKP             |                | SSPM<      | :3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                   | SSPCON2 | GCEN          | ACKSTAT                                                                                                 | ACKDT          | ACKEN           | RCEN           | PEN        | RSEN  | SEN   | 0000 0000            | 0000 0000                       |

| 217h                   | SSPCON3 | ACKTIM        | PCIE                                                                                                    | SCIE           | BOEN            | SDAHT          | SBCDE      | AHEN  | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                   | _       | Unimpleme     | nted                                                                                                    |                |                 |                | 1          |       |       | _                    | _                               |

| 219h                   | _       | Unimpleme     | Unimplemented                                                                                           |                |                 |                |            |       |       | _                    | _                               |

| 21Ah                   | _       | Unimpleme     | Unimplemented                                                                                           |                |                 |                |            |       |       | _                    | _                               |

| 21Bh                   | _       | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | _                    | _                               |

| 21Ch                   | —       | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | -                    | _                               |

| 21Dh                   | —       | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | _                    | _                               |

| 21Eh                   | _       | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | _                    | _                               |

| 21Fh                   | _       | Unimpleme     | nted                                                                                                    |                |                 |                |            |       |       | _                    | _                               |

### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$Legend: \qquad x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.$

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

4: Unimplemented, read as '1'.

## 7.6.4 PIE3 REGISTER

The PIE3 register contains the interrupt enable bits, as shown in Register 7-4.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | U-0   |

|-------|---------|---------|---------|---------|-----|---------|-------|

| —     | CCP5IE  | CCP4IE  | CCP3IE  | TMR6IE  | —   | TMR4IE  | —     |

| bit 7 |         |         |         |         |     |         | bit 0 |

| Legend:          |                                                                                                                       |                                                    |                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|

| R = Readable b   | oit                                                                                                                   | W = Writable bit                                   | U = Unimplemented bit, read as '0'                    |  |  |  |  |  |

| u = Bit is uncha | anged                                                                                                                 | x = Bit is unknown                                 | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |  |

| '1' = Bit is set |                                                                                                                       | '0' = Bit is cleared                               |                                                       |  |  |  |  |  |

|                  |                                                                                                                       |                                                    |                                                       |  |  |  |  |  |

| bit 7            | Unimplemented: Read as '0'                                                                                            |                                                    |                                                       |  |  |  |  |  |

| bit 6            | CCP5IE: CCP5 Interrupt Enable bit                                                                                     |                                                    |                                                       |  |  |  |  |  |

|                  | <ul> <li>1 = Enables the CCP5 interrupt</li> <li>0 = Disables the CCP5 interrupt</li> </ul>                           |                                                    |                                                       |  |  |  |  |  |

| bit 5            | CCP4IE: CCF                                                                                                           | P4 Interrupt Enable bit                            |                                                       |  |  |  |  |  |

|                  | <ul> <li>1 = Enables the CCP4 interrupt</li> <li>0 = Disables the CCP4 interrupt</li> </ul>                           |                                                    |                                                       |  |  |  |  |  |

| bit 4            | CCP3IE: CCF                                                                                                           | P3 Interrupt Enable bit                            |                                                       |  |  |  |  |  |

|                  | <ul> <li>1 = Enables the CCP3 interrupt</li> <li>0 = Disables the CCP3 interrupt</li> </ul>                           |                                                    |                                                       |  |  |  |  |  |

| bit 3            | TMR6IE: TMF                                                                                                           | R6 to PR6 Match Interrupt E                        | Enable bit                                            |  |  |  |  |  |

|                  | <ul> <li>1 = Enables the TMR6 to PR6 Match interrupt</li> <li>0 = Disables the TMR6 to PR6 Match interrupt</li> </ul> |                                                    |                                                       |  |  |  |  |  |

| bit 2            | Unimplemen                                                                                                            | ted: Read as '0'                                   |                                                       |  |  |  |  |  |

| bit 1            | TMR4IE: TMF                                                                                                           | R4 to PR4 Match Interrupt E                        | Enable bit                                            |  |  |  |  |  |

|                  |                                                                                                                       | the TMR4 to PR4 Match int the TMR4 to PR4 Match in | •                                                     |  |  |  |  |  |

| bit 0            | Unimplemen                                                                                                            | ted: Read as '0'                                   |                                                       |  |  |  |  |  |

## 12.2 PORTA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.2.1 ANSELA REGISTER

The ANSELA register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 12.2.2 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-2.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, comparator and CapSense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 12-2.

| TABLE 12-2: PORTA OUTPUT PRIORITY |

|-----------------------------------|

|-----------------------------------|

| Pin Name | Function Priority <sup>(1)</sup>                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| RA0      | VCAP<br>SEG12 (LCD)<br>SRNQ (SR Latch)<br>C2OUT (Comparator)<br>RA0                                                       |

| RA1      | SEG7 (LCD)<br>RA1                                                                                                         |

| RA2      | COM2 (LCD)<br>AN2 (DAC)<br>RA2                                                                                            |

| RA3      | COM3 (LCD) 28-pin only<br>SEG15<br>RA3                                                                                    |

| RA4      | SEG4 (LCD)<br>SRQ (SR Latch)<br>C1OUT (Comparator)<br>CCP5, 28-pin only<br>RA4                                            |

| RA5      | VCAP (enabled by Config. Word)<br>SEG5 (LCD)<br>SRNQ (SR Latch)<br>C2OUT (Comparator)<br>RA5                              |

| RA6      | VCAP (enabled by Config. Word)<br>OSC2 (enabled by Config. Word)<br>CLKOUT (enabled by Config. Word)<br>SEG1 (LCD)<br>RA6 |

| RA7      | OSC1/CLKIN (enabled by Config. Word)<br>SEG2 (LCD)<br>RA7                                                                 |

Note 1: Priority listed from highest to lowest.

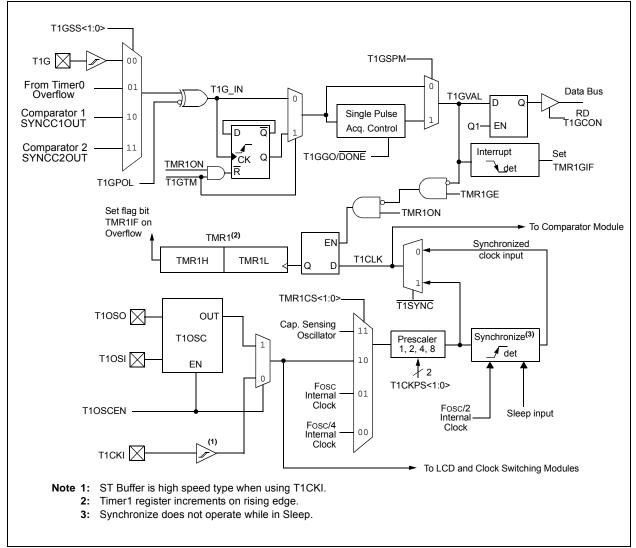

## 21.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- Programmable internal or external clock source

- · 2-bit prescaler

- · Dedicated 32 kHz oscillator circuit

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- · Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Time base for the Capture/Compare function

- Special Event Trigger (with CCP/ECCP)

- · Selectable Gate Source Polarity

- Gate Toggle Mode

- Gate Single-pulse Mode

- Gate Value Status

- Gate Event Interrupt

- Figure 21-1 is a block diagram of the Timer1 module.

## FIGURE 21-1: TIMER1 BLOCK DIAGRAM

NOTES:

## 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

| Name                 | Bit 7       | Bit 6           | Bit 5        | Bit 4         | Bit 3             | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|-------------|-----------------|--------------|---------------|-------------------|-----------------------|-----------------------|-----------------------|---------------------|

| APFCON               | _           | CCP3SEL         | T1GSEL       | P2BSEL        | SRNQSEL           | C2OUTSEL              | SSSEL                 | CCP2SEL               | 131                 |

| CCPxCON              | PxM<        | 1:0> <b>(1)</b> | DCxB         | <1:0>         |                   | CCPxM<                | :3:0>                 |                       | 234                 |

| CCPRxL               | Capture/Co  | mpare/PWM       | Register x l | Low Byte (LS  | SB)               |                       |                       |                       | 212                 |

| CCPRxH               | Capture/Co  | mpare/PWM       | Register x I | High Byte (M  | ISB)              |                       |                       |                       | 212                 |

| INTCON               | GIE         | PEIE            | TMR0IE       | INTE          | IOCIE             | TMR0IF                | INTF                  | IOCIF                 | 98                  |

| PIE1                 | TMR1GIE     | ADIE            | RCIE         | TXIE          | SSPIE             | CCP1IE                | TMR2IE                | TMR1IE                | 99                  |

| PIE2                 | OSFIE       | C2IE            | C1IE         | EEIE          | BCLIE             | LCDIE                 | _                     | CCP2IE                | 100                 |

| PIE3                 | —           | CCP5IE          | CCP4IE       | CCP3IE        | TMR6IE            | _                     | TMR4IE                | _                     | 101                 |

| PIR1                 | TMR1GIF     | ADIF            | RCIF         | TXIF          | SSPIF             | CCP1IF                | TMR2IF                | TMR1IF                | 102                 |

| PIR2                 | OSFIF       | C2IF            | C1IF         | EEIF          | BCLIF             | LCDIF                 | _                     | CCP2IF                | 103                 |

| PIR3                 | —           | CCP5IF          | CCP4IF       | CCP3IF        | TMR6IF            | _                     | TMR4IF                | —                     | 104                 |

| T1CON                | TMR1C       | S<1:0>          | T1CKP        | S<1:0>        | T1OSCEN           | T1SYNC                | _                     | TMR10N                | 203                 |

| T1GCON               | TMR1GE      | T1GPOL          | T1GTM        | T1GSPM        | T1GGO/DONE        | T1GVAL                | T1GSS                 | S<1:0>                | 204                 |

| TMR1L                | Holding Reg | gister for the  | Least Signif | icant Byte of | f the 16-bit TMR1 | 1 Register            |                       |                       | 199                 |

| TMR1H                | Holding Reg | gister for the  | Most Signifi | cant Byte of  | the 16-bit TMR1   | Register              |                       |                       | 199                 |

| TRISA                | TRISA7      | TRISA6          | TRISA5       | TRISA4        | TRISA3            | TRISA2                | TRISA1                | TRISA0                | 133                 |

| TRISB                | TRISB7      | TRISB6          | TRISB5       | TRISB4        | TRISB3            | TRISB2                | TRISB1                | TRISB0                | 138                 |

| TRISC                | TRISC7      | TRISC6          | TRISC5       | TRISC4        | TRISC3            | TRISC2                | TRISC1                | TRISC0                | 142                 |

| TRISD <sup>(2)</sup> | TRISD7      | TRISD6          | TRISD5       | TRISD4        | TRISD3            | TRISD2                | TRISD1                | TRISD0                | 145                 |

| TRISE                |             |                 |              | —             | _(3)              | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 148                 |

| TABLE 23-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE |

|-------------|----------------------------------------------|

|             |                                              |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

Note 1: Applies to ECCP modules only.

2: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

3: Unimplemented, read as '1'.

### 24.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 24.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

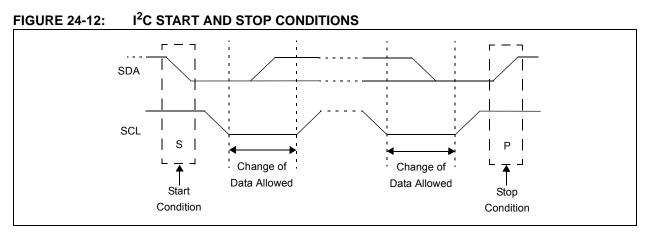

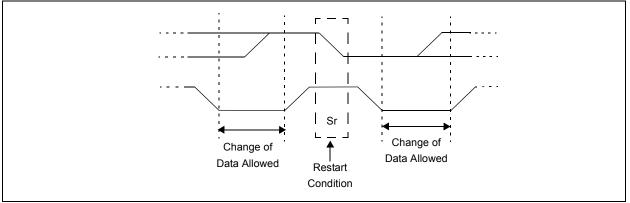

#### 24.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

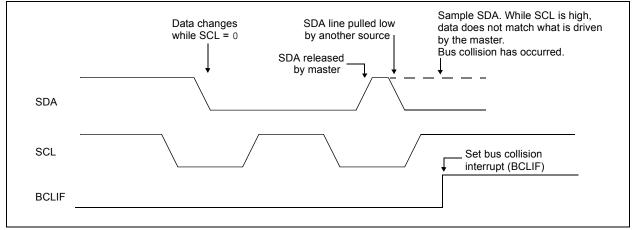

#### 24.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the I<sup>2</sup>C port to its Idle state (Figure 24-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 24-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

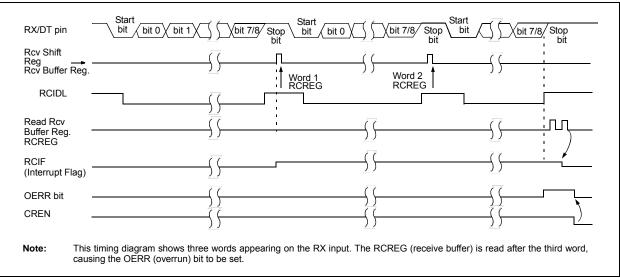

- 25.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.3 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received 8 Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### FIGURE 25-5: ASYNCHRONOUS RECEPTION

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                 | U-0  | R/W-0/0        | R/W-0/0          | R-0/0            | R/W-0/0     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|----------------|------------------|------------------|-------------|

| CPSON            | —                                                                                                                                                                                                                                                                                                                                                                                          | —                                                   | —    | CPSR           | NG<1:0>          | CPSOUT           | T0XCS       |

| bit 7            |                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |      | ·              |                  |                  | bit 0       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |      |                |                  |                  |             |

| Legend:          |                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |      |                |                  |                  |             |

| R = Readable     | bit                                                                                                                                                                                                                                                                                                                                                                                        | W = Writable                                        | bit  | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is uncha | anged                                                                                                                                                                                                                                                                                                                                                                                      | x = Bit is unkr                                     | iown | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                            | '0' = Bit is clea                                   | ared |                |                  |                  |             |

| bit 7            | 1 = CPS mod                                                                                                                                                                                                                                                                                                                                                                                | Module Enabl<br>dule is enabled<br>dule is disabled |      |                |                  |                  |             |

| bit 6-4          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                 |                                                     |      |                |                  |                  |             |

| bit 3-2          | <b>CPSRNG&lt;1:0&gt;:</b> Capacitive Sensing Current Range<br>00 = Oscillator is off<br>01 = Oscillator is in Low Range. Charge/Discharge Current is nominally 0.1 μA<br>10 = Oscillator is in Medium Range. Charge/Discharge Current is nominally 1.2 μA<br>11 = Oscillator is in High Range. Charge/Discharge Current is nominally 18 μA                                                 |                                                     |      |                |                  |                  |             |

| bit 1            | <b>CPSOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out of the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                                                         |                                                     |      |                |                  |                  |             |

| bit 0            | <b>TOXCS:</b> Timer0 External Clock Source Select bit<br><u>If TMR0CS = 1:</u><br>The TOXCS bit controls which clock external to the core/Timer0 module supplies Timer0:<br>1 = Timer0 clock source is the capacitive sensing oscillator<br>0 = Timer0 clock source is the T0CKI pin<br><u>If TMR0CS = 0:</u><br>Timer0 clock source is controlled by the core/Timer0 module and is Fosc/4 |                                                     |      |                |                  |                  |             |

## REGISTER 26-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

## 29.0 INSTRUCTION SET SUMMARY

Each PIC16 instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

## TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| n     | FSR or INDF number. (0-1)                                                                                                                                                            |

| mm    | Pre-post increment-decrement mode selection                                                                                                                                          |

#### TABLE 29-2: ABBREVIATION DESCRIPTIONS

| Field | Description     |

|-------|-----------------|

| PC    | Program Counter |

| TO    | Time-out bit    |

| С     | Carry bit       |

| DC    | Digit carry bit |

| Z     | Zero bit        |

| PD    | Power-down bit  |

## 29.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | FOR is limited to the new we oppose                                                           |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap around.

| ANDLW            | AND literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                          |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \to (W)$                                                                                                 |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |

| ADDWF            | Add W and f                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |

| Status Affected: | C, DC, Z                                                                                                                                                                        |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| ASRF             | Arithmetic Right Shift                                                                                                                                                     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                    |

| Status Affected: | C, Z                                                                                                                                                                       |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd' |

'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'.

ADD W and CARRY bit to f

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                                                                                                            |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

| ΜΟΥΙΨ            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|