Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

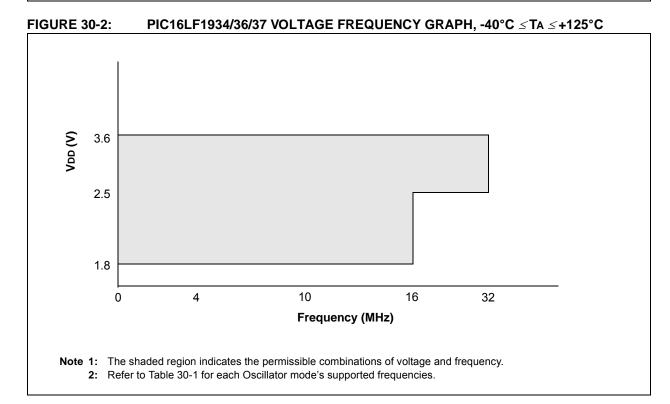

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

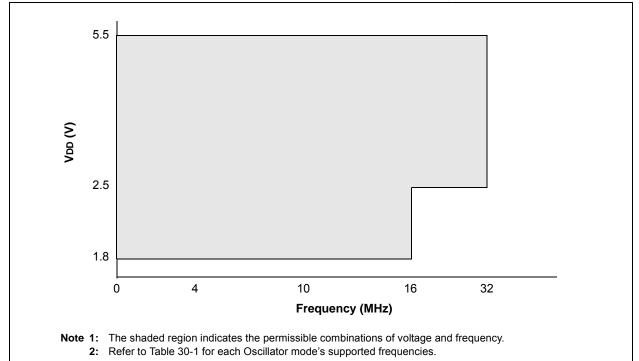

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 40-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 40-UQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1934-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE                            | 3-1Z. C | SPECIAL                    | FUNCTIC                                                  | IN REGIS        | DIER SUN     | INIART (C      |            | בט)   |       |               |      |                     |      |

|----------------------------------|---------|----------------------------|----------------------------------------------------------|-----------------|--------------|----------------|------------|-------|-------|---------------|------|---------------------|------|

| Address                          | Name    | Bit 7                      | Bit 6                                                    | Bit 5           | Bit 4        | Bit 3          | Bit 2      | Bit 1 | Bit 0 | Value<br>POR, |      | Value<br>oth<br>Res | ner  |

| Banks 1                          | 6-30    |                            |                                                          |                 |              |                |            |       |       |               |      |                     |      |

| x00h/<br>x80h <sup>(2)</sup>     | INDF0   | Addressing<br>(not a physi |                                                          | ses contents o  | of FSR0H/FSF | R0L to address | data memor | ý     |       | xxxx          | xxxx | xxxx                | xxxx |

| x00h/<br>x81h <sup>(2)</sup>     | INDF1   | Addressing<br>(not a physi |                                                          | ses contents o  | of FSR1H/FSF | R1L to address | data memor | y     |       | xxxx          | XXXX | xxxx                | xxxx |

| x02h/<br>x82h <sup>(2)</sup>     | PCL     | Program Co                 | ounter (PC) Le                                           | ast Significant | t Byte       |                |            |       |       | 0000          | 0000 | 0000                | 0000 |

| x03h/<br>x83h <sup>(2)</sup>     | STATUS  | -                          | —                                                        | _               | TO           | PD             | Z          | DC    | С     | 1             | 1000 | d                   | quuu |

| x04h/<br>x84h <sup>(2)</sup>     | FSR0L   | Indirect Dat               | a Memory Add                                             | Iress 0 Low P   | ointer       |                |            |       |       | 0000          | 0000 | uuuu                | uuuu |

| x05h/<br>x85h <b>(2)</b>         | FSR0H   | Indirect Dat               | Indirect Data Memory Address 0 High Pointer              |                 |              |                |            |       | 0000  | 0000          | 0000 | 0000                |      |

| x06h/<br>x86h <sup>(2)</sup>     | FSR1L   | Indirect Data              | Indirect Data Memory Address 1 Low Pointer               |                 |              |                |            |       | 0000  | 0000          | uuuu | uuuu                |      |

| x07h/<br>x87h <sup>(2)</sup>     | FSR1H   | Indirect Data              | Indirect Data Memory Address 1 High Pointer              |                 |              |                |            |       | 0000  | 0000          | 0000 | 0000                |      |

| x08h/<br>x88h <b>(2)</b>         | BSR     | _                          | — — — BSR<4:0>                                           |                 |              |                |            | 0     | 0000  | 0             | 0000 |                     |      |

| x09h/<br>x89h <sup>(2)</sup>     | WREG    | Working Re                 | Working Register                                         |                 |              |                |            |       | 0000  | 0000          | uuuu | uuuu                |      |

| x0Ah/<br>x8Ah <sup>(1),(2)</sup> | PCLATH  | -                          | Write Buffer for the upper 7 bits of the Program Counter |                 |              |                |            |       | -000  | 0000          | -000 | 0000                |      |

| x0Bh/<br>x8Bh <sup>(2)</sup>     | INTCON  | GIE                        | PEIE                                                     | TMR0IE          | INTE         | IOCIE          | TMR0IF     | INTF  | IOCIF | 0000          | 0000 | 0000                | 0000 |

| x0Ch/<br>x8Ch                    | —       | Unimpleme                  | nted                                                     |                 |              |                |            |       |       | -             | -    | _                   | -    |

| x1Fh/<br>x9Fh                    |         |                            |                                                          |                 |              |                |            |       |       |               |      |                     |      |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

#### 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number. A value of 0Fh will provide an adjustment to the maximum frequency. A value of 10h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

## 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator **Clock Switch Timing**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running and can be utilized.

#### 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The output of the 16 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4X PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (Default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

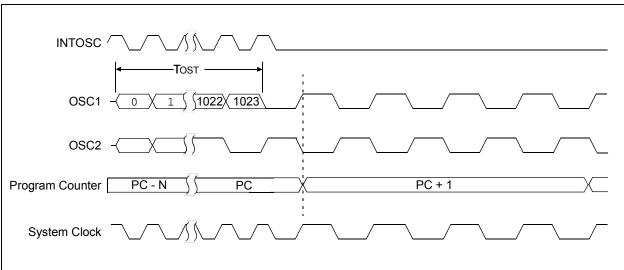

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

## 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

## 13.6 Interrupt-On-Change Registers

#### REGISTER 13-1: IOCBP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER

| '1' = Bit is set | angeu   | 0' = Bit is clear |         |                | at FOR and BO    | rv value at all t | iner Reseis |

|------------------|---------|-------------------|---------|----------------|------------------|-------------------|-------------|

| u = Bit is unch  | anged   | x = Bit is unkr   | NOWD    | _n/n = Value : | at POR and BO    | R//alue at all c  | ther Resets |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'            |             |

| Legend:          |         |                   |         |                |                  |                   |             |

|                  |         |                   |         |                |                  |                   |             |

| bit 7            | •       | •                 | •       |                |                  |                   | bit 0       |

| IOCBP7           | IOCBP6  | IOCBP5            | IOCBP4  | IOCBP3         | IOCBP2           | IOCBP1            | IOCBP0      |

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0           | R/W-0/0     |

bit 7-0

IOCBP<7:0>: Interrupt-on-Change Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 13-2: IOCBN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | IOCBN3  | IOCBN2  | IOCBN1  | IOCBN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 IOCBN<7:0>: Interrupt-on-Change Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

## REGISTER 13-3: IOCBF: INTERRUPT-ON-CHANGE FLAG REGISTER

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | IOCBF3     | IOCBF2     | IOCBF1     | IOCBF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCBF<7:0>: Interrupt-on-Change Flag bits

- 1 = An enabled change was detected on the associated pin.

Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.

- 0 = No change was detected, or the user cleared the detected change.

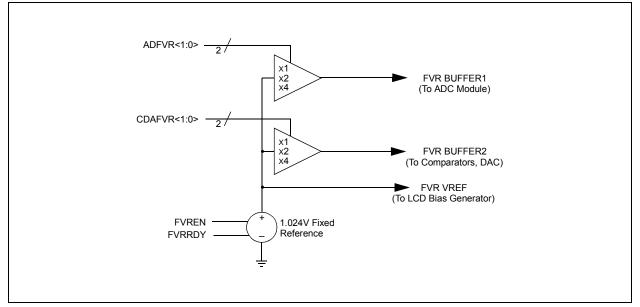

## 14.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- · ADC input channel

- · ADC positive reference

- Comparator positive input

- Digital-to-Analog Converter (DAC)

- · Capacitive Sensing (CPS) module

- LCD bias generator

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

## 14.1 Independent Gain Amplifiers

The output of the FVR supplied to the ADC, Comparators, DAC and CPS is routed through two independent programmable gain amplifiers. Each

amplifier can be configured to amplify the reference voltage by 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0** "**Analog-to-Digital Converter** (**ADC**) **Module**" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC, CPS and comparator module. Reference Section 17.0 "Digital-to-Analog Converter (DAC) Module", Section 18.0 "Comparator Module" and Section 26.0 "Capacitive Sensing (CPS) Module" for additional information.

## 14.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See in the applicable Electrical Specifications Chapter for the minimum delay requirement.

## FIGURE 14-1: VOLTAGE REFERENCE BLOCK DIAGRAM

## 18.2 Comparator Control

Each comparator has 2 control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 18-1) contain Control and Status bits for the following:

- Enable

- Output selection

- Output polarity

- Speed/Power selection

- · Hysteresis enable

- Output synchronization

The CMxCON1 registers (see Register 18-2) contain Control bits for the following:

- Interrupt enable

- Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-1 shows the output state versus input conditions, including polarity control.

#### TABLE 18-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

## 18.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

NOTES:

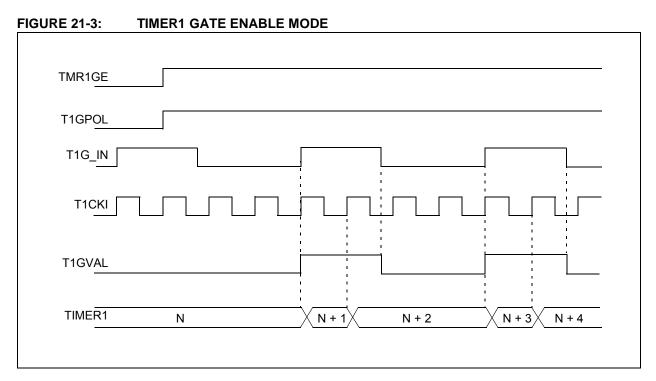

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4:TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                       |

|-------|--------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                          |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                  |

| 10    | Comparator 1 Output SYNCC1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output SYNCC2OUT<br>(optionally Timer1 synchronized output) |

## 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

## 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (SYNCC1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 18.4.1 "Comparator Output Synchronization**".

## 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (SYNCC2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 18.4.1 "Comparator Output Synchronization"**.

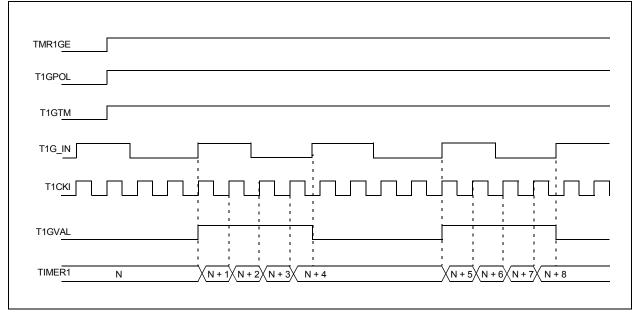

## 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

## 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

## 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## FIGURE 21-4: TIMER1 GATE TOGGLE MODE

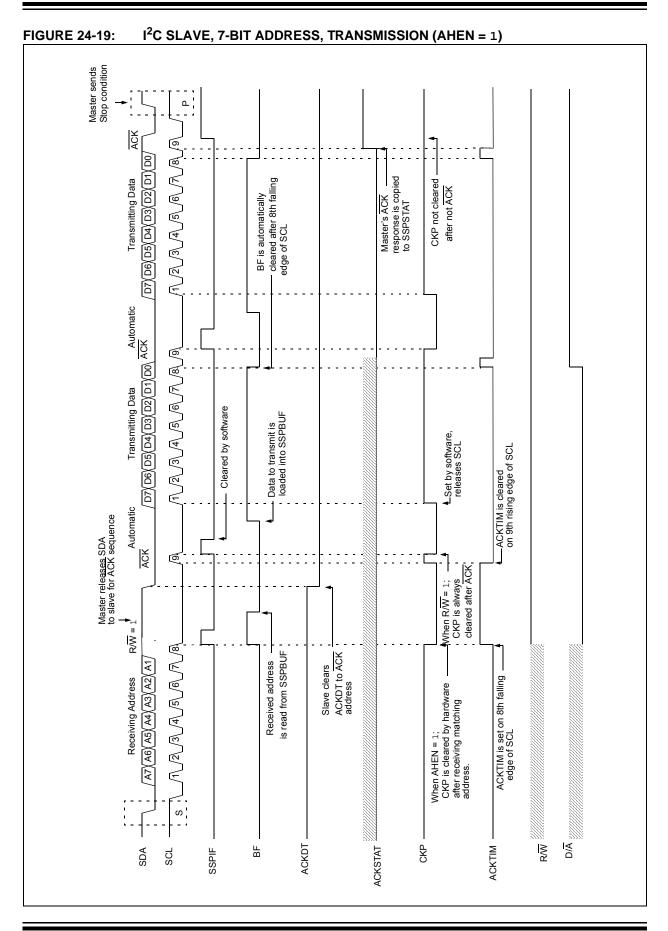

#### 24.6.6 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full (BF) flag bit, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted. SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high. When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an  $\overline{ACK}$  bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKSTAT bit on the rising edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 24-27).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will release the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT Status bit of the SSPCON2 register. Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 24.6.6.1 BF Status Flag

In Transmit mode, the BF bit of the SSPSTAT register is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

## 24.6.6.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

WCOL must be cleared by software before the next transmission.

## 24.6.6.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit of the SSPCON2 register is cleared when the slave has sent an Acknowledge ( $\overline{ACK} = 0$ ) and is set when the slave does not Acknowledge ( $\overline{ACK} = 1$ ). A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

24.6.6.4 Typical transmit sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. The MSSP module will wait the required start time before any other operation takes place.

- 5. The user loads the SSPBUF with the slave address to transmit.

- 6. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 8. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 9. The user loads the SSPBUF with eight bits of data.

- 10. Data is shifted out the SDA pin until all 8 bits are transmitted.

- 11. The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 12. Steps 8-11 are repeated for all transmitted data bytes.

- 13. The user generates a Stop or Restart condition by setting the PEN or RSEN bits of the SSPCON2 register. Interrupt is generated once the Stop/Restart condition is complete.

| Name    | Bit 7                              | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|------------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|--|

| BAUDCON | ABDOVF                             | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 302                 |  |

| INTCON  | GIE                                | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |  |

| PIE1    | TMR1GIE                            | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 99                  |  |

| PIR1    | TMR1GIF                            | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 102                 |  |

| RCREG   | EUSART Receive Data Register       |        |        |        |        |        |        |        |                     |  |

| RCSTA   | SPEN RX9 SREN CREN ADDEN FERR OERR |        |        |        |        | RX9D   | 301    |        |                     |  |

| SPBRGL  | BRG<7:0>                           |        |        |        |        |        |        |        |                     |  |

| SPBRGH  | BRG<15:8>                          |        |        |        |        |        |        |        |                     |  |

| TRISC   | TRISC7                             | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 142                 |  |

| TXSTA   | CSRC                               | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 300                 |  |

#### TABLE 25-2: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for asynchronous reception.

\* Page provides register information.

## 26.0 CAPACITIVE SENSING (CPS) MODULE

The Capacitive Sensing (CPS) module allows for an interaction with an end user without a mechanical interface. In a typical application, the CPS module is attached to a pad on a Printed Circuit Board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the CPS module. The CPS module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- Multiple power ranges

- Multiple timer resources

- Software control

- Operation during Sleep

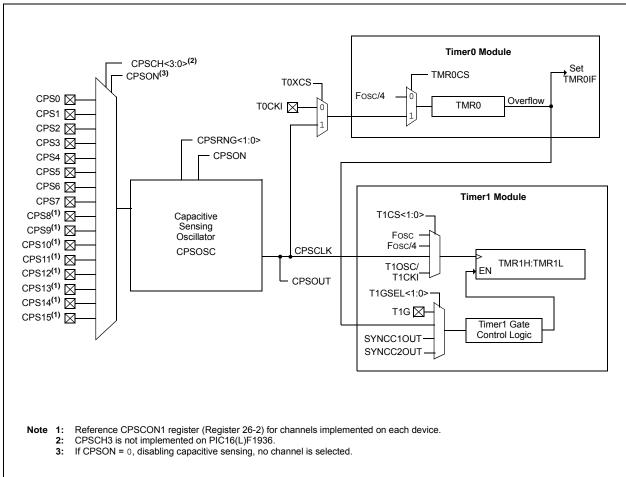

#### FIGURE 26-1: CAPACITIVE SENSING BLOCK DIAGRAM

## 26.5 Timer Resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed time base is required. For the period of the fixed time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed time base.

## 26.6 Fixed Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed time base is required. Any timer resource or software loop can be used to establish the fixed time base. It is up to the end user to determine the method in which the fixed time base is generated.

| Note: | The fixed time base can not be generated  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | by the timer resource that the capacitive |  |  |  |  |  |

|       | sensing oscillator is clocking.           |  |  |  |  |  |

#### 26.6.1 TIMER0

To select Timer0 as the timer resource for the CPS module:

- Set the T0XCS bit of the CPSCON0 register.

- Clear the TMR0CS bit of the OPTION\_REG register.

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 20.0** "**Timer0 Module**" for additional information.

## 26.6.2 TIMER1

To select Timer1 as the timer resource for the CPS module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified by using the Timer0 overflow flag.

It is recommend that the Timer0 overflow flag, in conjunction with the Toggle mode of the Timer1 gate, be used to develop the fixed time base required by the software portion of the CPS module. Refer to **Section 21.12 "Timer1 Gate Control Register"** for additional information.

TABLE 26-2: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

## 26.7 Software Control

The software portion of the CPS module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed time base to acquire counts on Timer0 or Timer1.

- Establishing the nominal frequency for the capacitive sensing oscillator.

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load.

- Set the frequency threshold.

#### 26.7.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin.

- At the start of the fixed time base, clear the timer resource.

- At the end of the fixed time base save the value in the timer resource.

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base.

#### 26.7.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin.

- Use the same fixed time base as the nominal frequency measurement.

- At the start of the fixed time base, clear the timer resource.

- At the end of the fixed time base save the value in the timer resource.

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed time base. This frequency should be less than the value obtained during the nominal frequency measurement.

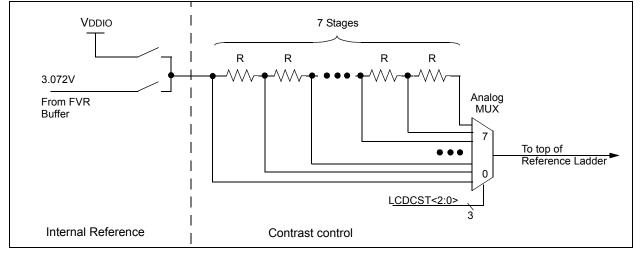

#### 27.4.4 CONTRAST CONTROL

The LCD contrast control circuit consists of a seven-tap resistor ladder, controlled by the LCDCST bits. Refer to Figure 27-7.

The contrast control circuit is used to decrease the output voltage of the signal source by a total of approximately 10%, when LCDCST = 111.

Whenever the LCD module is inactive (LCDA = 0), the contrast control ladder will be turned off (open).

## 27.4.5 INTERNAL REFERENCE

Under firmware control, an internal reference for the LCD bias voltages can be enabled. When enabled, the source of this voltage can be either VDDIO or a voltage 3 times the main fixed voltage reference (3.072V). When no internal reference is selected, the LCD contrast control circuit is disabled and LCD bias must be provided externally.

Whenever the LCD module is inactive (LCDA = 0), the internal reference will be turned off.

When the internal reference is enabled and the Fixed Voltage Reference is selected, the LCDIRI bit can be used to minimize power consumption by tieing into the LCD Reference Ladder Automatic Power mode switching. When LCDIRI = 1 and the LCD reference ladder is in Power mode 'B', the LCD internal FVR buffer is disabled.

**Note:** The LCD module automatically turns on the Fixed Voltage Reference when needed.

## 27.4.6 VLCD<3:1> PINS

The VLCD<3:1> pins provide the ability for an external LCD bias network to be used instead of the internal ladder. Use of the VLCD<3:1> pins does not prevent use of the internal ladder. Each VLCD pin has an independent control in the LCDREF register (Register 27-3), allowing access to any or all of the LCD Bias signals. This architecture allows for maximum flexibility in different applications

For example, the VLCD<3:1> pins may be used to add capacitors to the internal reference ladder, increasing the drive capacity.

For applications where the internal contrast control is insufficient, the firmware can choose to only enable the VLCD3 pin, allowing an external contrast control circuit to use the internal reference divider.

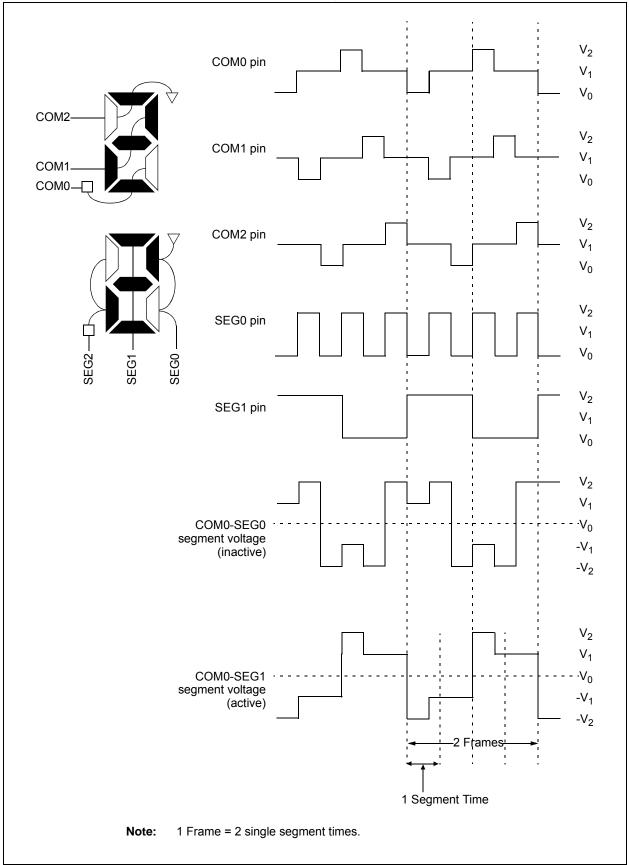

#### FIGURE 27-14: TYPE-B WAVEFORMS IN 1/3 MUX, 1/2 BIAS DRIVE

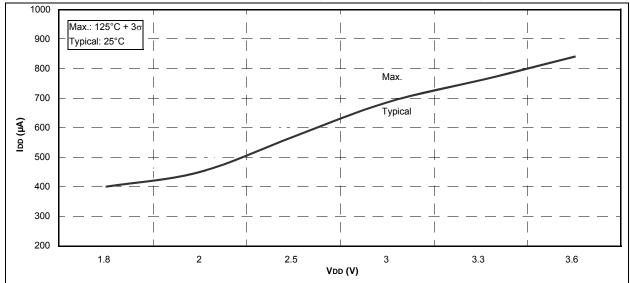

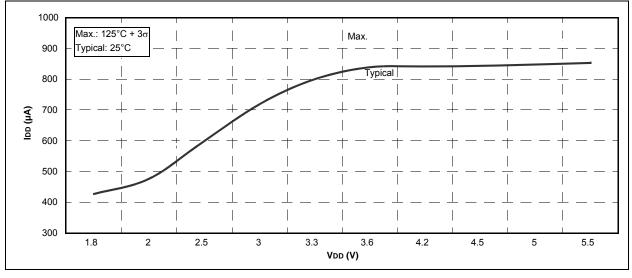

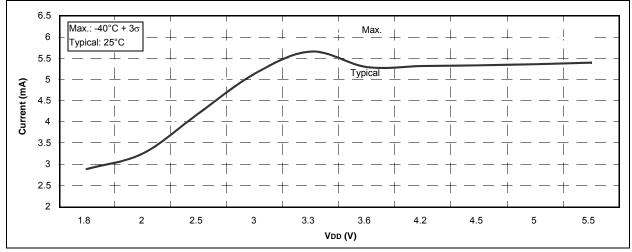

#### 30.3 DC Characteristics: PIC16(L)F1934/6/7-I/E (Power-Down)

| PIC16LF1934/36/37 |                         |                      |                                                                                                                                                                                                                                                            |       |        |       |            |                                    |  |

|-------------------|-------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|------------|------------------------------------|--|

| PIC16F1934/36/37  |                         |                      | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |       |        |       |            |                                    |  |

| Param             | Device Characteristics  | Min.                 | Typ†                                                                                                                                                                                                                                                       | Max.  | Max.   | Units | Conditions |                                    |  |

| No.               | Device onarablensites   |                      | 1961                                                                                                                                                                                                                                                       | +85°C | +125°C | onito | Vdd        | Note                               |  |

|                   | Power-down Base Current | (IPD) <sup>(2)</sup> |                                                                                                                                                                                                                                                            |       |        |       |            |                                    |  |

| D023              |                         | —                    | 0.06                                                                                                                                                                                                                                                       | 1.0   | 8.0    | μA    | 1.8        | WDT, BOR, FVR, and T1OSC           |  |

|                   |                         | _                    | 0.08                                                                                                                                                                                                                                                       | 2.0   | 9.0    | μA    | 3.0        | disabled, all Peripherals Inactive |  |

| D023              |                         | _                    | 21                                                                                                                                                                                                                                                         | 55    | 63     | μA    | 1.8        | WDT, BOR, FVR, and T1OSC           |  |

|                   |                         | _                    | 25                                                                                                                                                                                                                                                         | 58    | 78     | μA    | 3.0        | disabled, all Peripherals Inactive |  |

|                   |                         | —                    | 27                                                                                                                                                                                                                                                         | 60    | 88     | μA    | 5.0        |                                    |  |

| D024              |                         | _                    | 0.5                                                                                                                                                                                                                                                        | 4.0   | 9.0    | μA    | 1.8        | LPWDT Current (Note 1)             |  |

|                   |                         | —                    | 0.8                                                                                                                                                                                                                                                        | 5.0   | 10     | μA    | 3.0        |                                    |  |

| D024              |                         |                      | 23                                                                                                                                                                                                                                                         | 57    | 65     | μA    | 1.8        | LPWDT Current (Note 1)             |  |

|                   |                         | _                    | 26                                                                                                                                                                                                                                                         | 59    | 80     | μA    | 3.0        |                                    |  |

|                   |                         | —                    | 28                                                                                                                                                                                                                                                         | 61    | 90     | μA    | 5.0        |                                    |  |

| D025              |                         | —                    | 15                                                                                                                                                                                                                                                         | 28    | 30     | μA    | 1.8        | FVR current                        |  |

|                   |                         | —                    | 15                                                                                                                                                                                                                                                         | 30    | 33     | μA    | 3.0        |                                    |  |

| D025              |                         |                      | 38                                                                                                                                                                                                                                                         | 96    | 100    | μA    | 1.8        | FVR current (Note 4)               |  |

|                   |                         |                      | 45                                                                                                                                                                                                                                                         | 110   | 120    | μA    | 3.0        |                                    |  |

|                   |                         | —                    | 90                                                                                                                                                                                                                                                         | 140   | 155    | μA    | 5.0        |                                    |  |

| D026              |                         |                      | 13                                                                                                                                                                                                                                                         | 25    | 28     | μA    | 3.0        | BOR Current (Note 1)               |  |

| D026              |                         | _                    | 40                                                                                                                                                                                                                                                         | 110   | 120    | μA    | 3.0        | BOR Current (Note 1, Note 4)       |  |

|                   |                         | -                    | 87                                                                                                                                                                                                                                                         | 140   | 155    | μA    | 5.0        |                                    |  |

| D027              |                         | _                    | 0.6                                                                                                                                                                                                                                                        | 5.0   | 9.0    | μA    | 1.8        | T1OSC Current (Note 1)             |  |

|                   |                         | -                    | 1.8                                                                                                                                                                                                                                                        | 7.0   | 12     | μA    | 3.0        |                                    |  |

| D027              |                         | _                    | 22                                                                                                                                                                                                                                                         | 57    | 60     | μA    | 1.8        | T1OSC Current (Note 1)             |  |

|                   |                         | _                    | 29                                                                                                                                                                                                                                                         | 62    | 70     | μA    | 3.0        |                                    |  |

|                   |                         | —                    | 35                                                                                                                                                                                                                                                         | 66    | 85     | μA    | 5.0        |                                    |  |

t Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: A/D oscillator source is FRC.

4: 0.1  $\mu$ F capacitor on VCAP (RA0).

## TABLE 30-5:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET PARAMETERS

|              | -                  | ting Conditions (unless otherwise s<br>erature -40°C ≤ TA ≤ +125°C | tated)       |            |              |       |                                      |

|--------------|--------------------|--------------------------------------------------------------------|--------------|------------|--------------|-------|--------------------------------------|

| Param<br>No. | Sym Characteristic |                                                                    | Min.         | Тур†       | Max.         | Units | Conditions                           |

| 30           | TMCL               | MCLR Pulse Width (low)                                             | 2            | _          | _            | μS    |                                      |

| 31           | TWDTLP             | Low-Power Watchdog Timer<br>Time-out Period                        | 10           | 16         | 27           | ms    | VDD = 3.3V-5V<br>1:16 Prescaler used |

| 32           | Tost               | Oscillator Start-up Timer Period <sup>(1),</sup> (2)               |              | 1024       |              | Tosc  | (Note 3)                             |

| 33*          | TPWRT              | Power-up Timer Period, $\overline{PWRTE} = 0$                      | 40           | 65         | 140          | ms    |                                      |

| 34*          | Tioz               | I/O high-impedance from MCLR Low or Watchdog Timer Reset           |              | —          | 2.0          | μS    |                                      |

| 35           | VBOR               | Brown-out Reset Voltage                                            | 2.38<br>1.80 | 2.5<br>1.9 | 2.73<br>2.11 | V     | BORV=2.5V<br>BORV=1.9V               |

| 36*          | VHYST              | Brown-out Reset Hysteresis                                         | 0            | 25         | 60           | mV    | -40°C to +85°C                       |

| 37*          | TBORDC             | Brown-out Reset DC Response<br>Time                                | 1            | 3          | 35           | μS    | $V D D \leq V B O R$                 |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- **3:** Period of the slower clock.

- 4: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

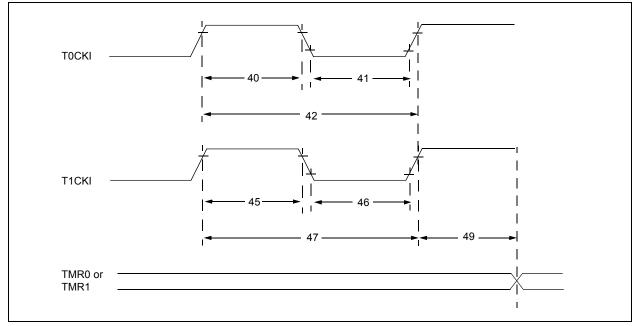

#### FIGURE 30-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

FIGURE 31-36: PIC16LF1937 EC OSCILLATOR, MEDIUM-POWER MODE, Fosc = 4 MHz