Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1934t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Peripheral Features (Continued):**

- Master Synchronous Serial Port (MSSP) with SPI and I<sup>2</sup>C<sup>™</sup> with:

- 7-bit address masking

- SMBus/PMBus<sup>™</sup> compatibility

- Auto-wake-up on start

- Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)

- RS-232, RS-485 and LIN compatible

- Auto-Baud Detect

- SR Latch (555 Timer):

- Multiple Set/Reset input options

- Emulates 555 Timer applications

- 2 Comparators:

- Rail-to-rail inputs/outputs

- Power mode control

- Software enable hysteresis

- Voltage Reference module:

- Fixed Voltage Reference (FVR) with 1.024V, 2.048V and 4.096V output levels

- 5-bit rail-to-rail resistive DAC with positive and negative reference selection

## PIC16(L)F193X Family Types

| Device                    | Program Memory<br>Flash (words) | Data EEPROM<br>(bytes) | SRAM (bytes) | s,0/I | 10-bit A/D<br>(ch) | CapSense<br>(ch) | Comparators | Timers<br>8/16-bit | EUSART | I²C™/SPI | ECCP | ССР | ГСD                  |

|---------------------------|---------------------------------|------------------------|--------------|-------|--------------------|------------------|-------------|--------------------|--------|----------|------|-----|----------------------|

| PIC16F1934<br>PIC16LF1934 | 4096                            | 256                    | 256          | 36    | 14                 | 16               | 2           | 4/1                | Yes    | Yes      | 3    | 2   | 24/4                 |

| PIC16F1936<br>PIC16LF1936 | 8192                            | 256                    | 512          | 25    | 11                 | 8                | 2           | 4/1                | Yes    | Yes      | 3    | 2   | 16 <sup>(1)</sup> /4 |

| PIC16F1937<br>PIC16LF1937 | 8192                            | 256                    | 512          | 36    | 14                 | 16               | 2           | 4/1                | Yes    | Yes      | 3    | 2   | 24/4                 |

Note 1: COM3 and SEG15 share the same physical pin on PIC16(L)F1936, therefore, SEG15 is not available when using 1/4 multiplex displays.

| Address                | Name         | Bit 7                      | Bit 6                                                    | Bit 5           | Bit 4        | Bit 3         | Bit 2       | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------------|----------------------------|----------------------------------------------------------|-----------------|--------------|---------------|-------------|---------|---------|----------------------|---------------------------------|

| Bank 5                 |              |                            |                                                          |                 |              |               |             |         |         |                      |                                 |

| 280h <sup>(2)</sup>    | INDF0        | Addressing<br>(not a physi |                                                          | ses contents o  | of FSR0H/FSR | 0L to address | data memory | /       |         | XXXX XXXX            | XXXX XXXX                       |

| 281h <sup>(2)</sup>    | INDF1        | Addressing<br>(not a physi |                                                          | ses contents o  | of FSR1H/FSR | 1L to address | data memory | /       |         | XXXX XXXX            | XXXX XXXX                       |

| 282h <sup>(2)</sup>    | PCL          | Program Co                 | ounter (PC) Le                                           | ast Significant | t Byte       |               |             |         |         | 0000 0000            | 0000 0000                       |

| 283h <sup>(2)</sup>    | STATUS       | _                          | <u> </u>                                                 |                 |              |               |             |         |         |                      | q quuu                          |

| 284h <sup>(2)</sup>    | FSR0L        | Indirect Data              | Indirect Data Memory Address 0 Low Pointer               |                 |              |               |             |         |         |                      | uuuu uuuu                       |

| 285h <sup>(2)</sup>    | FSR0H        | Indirect Data              | a Memory Add                                             | dress 0 High P  | ointer       |               |             |         |         | 0000 0000            | 0000 0000                       |

| 286h <sup>(2)</sup>    | FSR1L        | Indirect Data              | a Memory Ado                                             | dress 1 Low Po  | ointer       |               |             |         |         | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(2)</sup>    | FSR1H        | Indirect Data              | a Memory Add                                             | dress 1 High P  | ointer       |               |             |         |         | 0000 0000            | 0000 0000                       |

| 288h <sup>(2)</sup>    | BSR          | _                          | — — — BSR<4:0>                                           |                 |              |               |             |         |         | 0 0000               | 0 0000                          |

| 289h <sup>(2)</sup>    | WREG         | Working Re                 | Vorking Register                                         |                 |              |               |             |         |         |                      | uuuu uuuu                       |

| 28Ah <sup>(1, 2)</sup> | PCLATH       | _                          | Write Buffer for the upper 7 bits of the Program Counter |                 |              |               |             |         |         | -000 0000            | -000 0000                       |

| 28Bh <sup>(2)</sup>    | INTCON       | GIE                        | PEIE                                                     | TMR0IE          | INTE         | IOCIE         | TMR0IF      | INTF    | IOCIF   | 0000 0000            | 0000 0000                       |

| 28Ch                   | —            | Unimplemer                 | nted                                                     |                 |              |               |             |         |         | —                    | —                               |

| 28Dh                   | _            | Unimpleme                  | Unimplemented                                            |                 |              |               |             |         |         |                      | _                               |

| 28Eh                   | _            | Unimplemer                 | nted                                                     |                 |              |               |             |         |         | _                    | _                               |

| 28Fh                   | —            | Unimplemer                 | nted                                                     |                 |              |               |             |         |         | _                    | _                               |

| 290h                   | —            | Unimplemer                 | nted                                                     |                 |              |               |             |         |         | _                    | _                               |

| 291h                   | CCPR1L       | Capture/Co                 | mpare/PWM F                                              | Register 1 (LSE | 3)           |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 292h                   | CCPR1H       | Capture/Col                | mpare/PWM F                                              | Register 1 (MS  | B)           |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 293h                   | CCP1CON      | P1M                        | <1:0>                                                    | DC1B            | 8<1:0>       |               | CCP1M       | <3:0>   |         | 0000 0000            | 0000 0000                       |

| 294h                   | PWM1CON      | P1RSEN                     |                                                          |                 | Р            | 1DC<6:0>      |             |         |         | 0000 0000            | 0000 0000                       |

| 295h                   | CCP1AS       | CCP1ASE                    |                                                          | CCP1AS<2:0>     | >            | PSS1A         | C<1:0>      | PSS1E   | D<1:0>  | 0000 0000            | 0000 0000                       |

| 296h                   | PSTR1CON     | _                          | —                                                        | —               | STR1SYNC     | STR1D         | STR1C       | STR1B   | STR1A   | 0 0001               | 0 0001                          |

| 297h                   | _            | Unimpleme                  | nted                                                     |                 |              |               |             |         |         | _                    | _                               |

| 298h                   | CCPR2L       | Capture/Co                 | mpare/PWM F                                              | Register 2 (LSI | 3)           |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 299h                   | CCPR2H       | Capture/Col                | mpare/PWM F                                              | Register 2 (MS  | iB)          |               |             |         |         | xxxx xxxx            | uuuu uuuu                       |

| 29Ah                   | CCP2CON      | P2M                        | <1:0>                                                    | DC2E            | 3<1:0>       |               | CCP2M       | <3:0>   |         | 0000 0000            | 0000 0000                       |

| 29Bh                   | PWM2CON      | P2RSEN                     |                                                          | 1               | Р            | 2DC<6:0>      |             |         |         | 0000 0000            | 0000 0000                       |

| 29Ch                   | CCP2AS       | CCP2ASE                    |                                                          | CCP2AS<2:0>     | >            | PSS2A         | C<1:0>      | PSS2E   | D<1:0>  | 0000 0000            | 0000 0000                       |

| 29Dh                   | PSTR2CON     | _                          | —                                                        |                 | STR2SYNC     | STR2D         | STR2C       | STR2B   | STR2A   | 0 0001               | 0 0001                          |

| 29Eh                   | CCPTMRS<br>0 | C4TSEL1                    | C4TSEL0                                                  | C3TSEL1         | C3TSEL0      | C2TSEL1       | C2TSEL0     | C1TSEL1 | C1TSEL0 | 0000 0000            | 0000 0000                       |

| 29Fh                   | CCPTMRS<br>1 | —                          | —                                                        | —               | —            | —             | —           | C5TSE   | L<1:0>  | 00                   | 00                              |

#### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

4: Unimplemented, read as '1'.

| FIGURE 7  | 7-2: I       | NTERRUPT      | LATENCY           |                  |       |             |             |             |

|-----------|--------------|---------------|-------------------|------------------|-------|-------------|-------------|-------------|

|           |              |               |                   |                  |       |             |             |             |

| OSC1      |              |               |                   |                  |       |             |             |             |

| CLKOUT    |              |               | Interru<br>during | pt Sampled<br>Q1 |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | PC            | PC                | +1               | 0004h | 0005h       |             |             |

| Execute   | 1 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP   | Inst(0004h) | L           |             |

|           |              |               |                   |                  |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | PC            | PC+1/FSR<br>ADDR  | New PC/<br>PC+1  | 0004h | 0005h       |             |             |

| Execute-  | 2 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP   | Inst(0004h) |             |             |

|           |              |               |                   | 1                |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             | (           |

| PC        | PC-1         | PC            | FSR ADDR          | PC+1             | PC+2  | 0004h       | 0005h       | )           |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP   | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt |              |               |                   |                  | -     |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | РС            | FSR ADDR          | PC+1             | PC    | +2          | 0004h       | 0005h       |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP   | NOP         | NOP         | Inst(0004h) |

|           |              |               |                   |                  |       |             |             |             |

| U-0              | U-0                                     | R/W-1/1           | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|------------------|-----------------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| —                | —                                       | ANSA5             | ANSA4   | ANSA3                                                 | ANSA2   | ANSA1   | ANSA0   |  |  |

| bit 7            |                                         |                   |         |                                                       |         |         | bit 0   |  |  |

|                  |                                         |                   |         |                                                       |         |         |         |  |  |

| Legend:          |                                         |                   |         |                                                       |         |         |         |  |  |

| R = Readable     | bit                                     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

### REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 12-20: LATE: PORTE DATA LATCH REGISTER

| U-0              | U-0                                   | U-0               | U-0                                                   | U-0                                | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|------------------|---------------------------------------|-------------------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

|                  | _                                     |                   |                                                       | _                                  | LATE2   | LATE1   | LATE0   |  |  |

| bit 7            | •                                     |                   | •                                                     |                                    |         |         | bit 0   |  |  |

|                  |                                       |                   |                                                       |                                    |         |         |         |  |  |

| Legend:          |                                       |                   |                                                       |                                    |         |         |         |  |  |

| R = Readable I   | bit                                   | W = Writable      | bit                                                   | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is uncha | = Bit is unchanged x = Bit is unknown |                   | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

| '1' = Bit is set |                                       | '0' = Bit is clea | ared                                                  |                                    |         |         |         |  |  |

| 1.1.7.0 |                            |

|---------|----------------------------|

| bit 7-3 | Unimplemented: Read as '0' |

bit 2-0 LATE<2:0>: PORTE Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTE are actually written to corresponding LATE register. Reads from PORTE register is return of actual I/O pin values.

#### REGISTER 12-21: ANSELE: PORTE ANALOG SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1                  | R/W-1<br>ANSE1 <sup>(2)</sup> | R/W-1                |

|-------|-----|-----|-----|-----|------------------------|-------------------------------|----------------------|

| —     |     |     | _   | _   | — ANSE2 <sup>(2)</sup> |                               | ANSE0 <sup>(2)</sup> |

| bit 7 |     |     |     |     |                        |                               | bit 0                |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 ANSE<2:0>: Analog Select between Analog or Digital Function on Pins RE<2:0>, respectively

- 0 = Digital I/O. Pin is assigned to port or digital special function.

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- **Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: ANSELE register is not implemented on the PIC16(L)F1936. Read as '0'

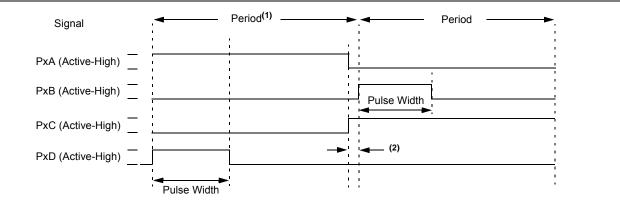

#### 23.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the PxM1 bit in the CCPxCON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the PxM1 bit of the CCPxCON register. The following sequence occurs four Timer cycles prior to the end of the current PWM period:

- The modulated outputs (PxB and PxD) are placed in their inactive state.

- The associated unmodulated outputs (PxA and PxC) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 23-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 23-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output PxA and PxD become inactive, while output PxC becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 23-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### FIGURE 23-12: EXAMPLE OF PWM DIRECTION CHANGE

**Note 1:** The direction bit PxM1 of the CCPxCON register is written any time during the PWM cycle.

2: When changing directions, the PxA and PxC signals switch before the end of the current PWM cycle. The modulated PxB and PxD signals are inactive at this time. The length of this time is four Timer counts.

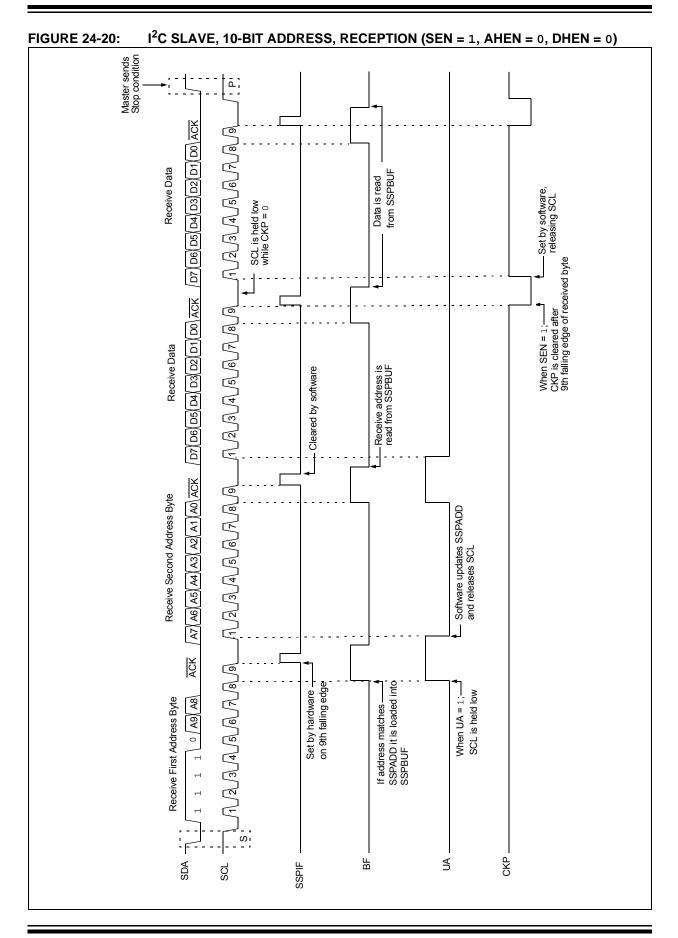

## 24.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPCON2 register.

| Note: | The MSSP module must be in an Idle      |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|

|       | state before the RCEN bit is set or the |  |  |  |  |  |  |  |  |

|       | RCEN bit will be disregarded.           |  |  |  |  |  |  |  |  |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPCON2 register.

#### 24.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 24.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 24.6.7.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 24.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. User writes SSPBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- 7. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 8. User sets the RCEN bit of the SSPCON2 register and the Master clocks in a byte from the slave.

- 9. After the 8th falling edge of SCL, SSPIF and BF are set.

- 10. Master clears SSPIF and reads the received byte from SSPBUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSPIF is set.

- 13. User clears SSPIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

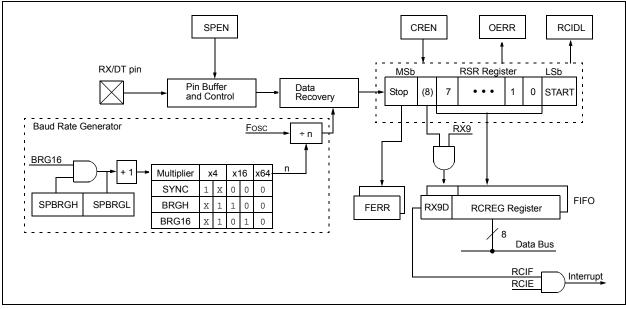

### FIGURE 25-2: EUSART RECEIVE BLOCK DIAGRAM

The operation of the EUSART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These registers are detailed in Register 25-1, Register 25-2 and Register 25-3, respectively.

When the receiver or transmitter section is not enabled then the corresponding RX or TX pin may be used for general purpose input and output.

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | —      | WUE    | ABDEN  | 302                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 99                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 102                 |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 301                 |

| SPBRGL  |                               |        |        | BRG    | <7:0>  |        |        |        | 303*                |

| SPBRGH  |                               |        |        | BRG<   | :15:8> |        |        |        | 303*                |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 142                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        |        | 293*                |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 300                 |

#### TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Asynchronous Transmission.

\* Page provides register information.

#### 25.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 25-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all 8 or 9 bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 25.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

## 25.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 25.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additiona<br>characters will be received until the overrur<br>condition is cleared. See <b>Section 25.1.2.5</b> | ۱ |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|---|

|       | "Receive Overrun Error" for more                                                                                                                   | ÷ |

|       | information on overrun errors.                                                                                                                     |   |

#### 25.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- · RCIE interrupt enable bit of the PIE1 register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

| LCD<br>Function | СОМО                |                | COM1                |                | COM2                |                | COM3                |                |

|-----------------|---------------------|----------------|---------------------|----------------|---------------------|----------------|---------------------|----------------|

|                 | LCDDATAx<br>Address | LCD<br>Segment | LCDDATAx<br>Address | LCD<br>Segment | LCDDATAx<br>Address | LCD<br>Segment | LCDDATAx<br>Address | LCD<br>Segment |

| SEG0            | LCDDATA0, 0         |                | LCDDATA3, 0         |                | LCDDATA6, 0         |                | LCDDATA9, 0         |                |

| SEG1            | LCDDATA0, 1         |                | LCDDATA3, 1         |                | LCDDATA6, 1         |                | LCDDATA9, 1         |                |

| SEG2            | LCDDATA0, 2         |                | LCDDATA3, 2         |                | LCDDATA6, 2         |                | LCDDATA9, 2         |                |

| SEG3            | LCDDATA0, 3         |                | LCDDATA3, 3         |                | LCDDATA6, 3         |                | LCDDATA9, 3         |                |

| SEG4            | LCDDATA0, 4         |                | LCDDATA3, 4         |                | LCDDATA6, 4         |                | LCDDATA9, 4         |                |

| SEG5            | LCDDATA0, 5         |                | LCDDATA3, 5         |                | LCDDATA6, 5         |                | LCDDATA9, 5         |                |

| SEG6            | LCDDATA0, 6         |                | LCDDATA3, 6         |                | LCDDATA6, 6         |                | LCDDATA9, 6         |                |

| SEG7            | LCDDATA0, 7         |                | LCDDATA3, 7         |                | LCDDATA6, 7         |                | LCDDATA9, 7         |                |

| SEG8            | LCDDATA1, 0         |                | LCDDATA4, 0         |                | LCDDATA7, 0         |                | LCDDATA10, 0        |                |

| SEG9            | LCDDATA1, 1         |                | LCDDATA4, 1         |                | LCDDATA7, 1         |                | LCDDATA10, 1        |                |

| SEG10           | LCDDATA1, 2         |                | LCDDATA4, 2         |                | LCDDATA7, 2         |                | LCDDATA10, 2        |                |

| SEG11           | LCDDATA1, 3         |                | LCDDATA4, 3         |                | LCDDATA7, 3         |                | LCDDATA10, 3        |                |

| SEG12           | LCDDATA1, 4         |                | LCDDATA4, 4         |                | LCDDATA7, 4         |                | LCDDATA10, 4        |                |

| SEG13           | LCDDATA1, 5         |                | LCDDATA4, 5         |                | LCDDATA7, 5         |                | LCDDATA10, 5        |                |

| SEG14           | LCDDATA1, 6         |                | LCDDATA4, 6         |                | LCDDATA7, 6         |                | LCDDATA10, 6        |                |

| SEG15           | LCDDATA1, 7         |                | LCDDATA4, 7         |                | LCDDATA7, 7         |                | LCDDATA10, 7        |                |

| SEG16           | LCDDATA2, 0         |                | LCDDATA5, 0         |                | LCDDATA8, 0         |                | LCDDATA11, 0        |                |

| SEG17           | LCDDATA2, 1         |                | LCDDATA5, 1         |                | LCDDATA8, 1         |                | LCDDATA11, 1        |                |

| SEG18           | LCDDATA2, 2         |                | LCDDATA5, 2         |                | LCDDATA8, 2         |                | LCDDATA11, 2        |                |

| SEG19           | LCDDATA2, 3         |                | LCDDATA5, 3         |                | LCDDATA8, 3         |                | LCDDATA11, 3        |                |

| SEG20           | LCDDATA2, 4         |                | LCDDATA5, 4         |                | LCDDATA8, 4         |                | LCDDATA11, 4        |                |

| SEG21           | LCDDATA2, 5         |                | LCDDATA5, 5         |                | LCDDATA8, 5         |                | LCDDATA11, 5        |                |

| SEG22           | LCDDATA2, 6         |                | LCDDATA5, 6         |                | LCDDATA8, 6         |                | LCDDATA11, 6        |                |

| SEG23           | LCDDATA2, 7         |                | LCDDATA5, 7         |                | LCDDATA8, 7         |                | LCDDATA11, 7        |                |

| TABLE 27-7: LCD SEGMENT MAPPING WORKSHEET |

|-------------------------------------------|

|-------------------------------------------|

## 27.12 Configuring the LCD Module

The following is the sequence of steps to configure the LCD module.

- 1. Select the frame clock prescale using bits LP<3:0> of the LCDPS register.

- 2. Configure the appropriate pins to function as segment drivers using the LCDSEn registers.

- 3. Configure the LCD module for the following using the LCDCON register:

- Multiplex and Bias mode, bits LMUX<1:0>

- Timing source, bits CS<1:0>

- Sleep mode, bit SLPEN

- 4. Write initial values to pixel data registers, LCDDATA0 through LCDDATA11.

- 5. Clear LCD Interrupt Flag, LCDIF bit of the PIR2 register and if desired, enable the interrupt by setting bit LCDIE of the PIE2 register.

- Configure bias voltages by setting the LCDRL, LCDREF and the associated ANSELx registers as needed.

- 7. Enable the LCD module by setting bit LCDEN of the LCDCON register.

## 27.13 Disabling the LCD Module

To disable the LCD module, write all '0's to the LCDCON register.

## 27.14 LCD Current Consumption

When using the LCD module the current consumption consists of the following three factors:

- Oscillator Selection

- · LCD Bias Source

- Capacitance of the LCD segments

The current consumption of just the LCD module can be considered negligible compared to these other factors.

#### 27.14.1 OSCILLATOR SELECTION

The current consumed by the clock source selected must be considered when using the LCD module. See the applicable Electrical Specifications Chapter for oscillator current consumption information.

#### 27.14.2 LCD BIAS SOURCE

The LCD bias source, internal or external, can contribute significantly to the current consumption. Use the highest possible resistor values while maintaining contrast to minimize current.

## 27.14.3 CAPACITANCE OF THE LCD SEGMENTS

The LCD segments which can be modeled as capacitors which must be both charged and discharged every frame. The size of the LCD segment and its technology determines the segment's capacitance. For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

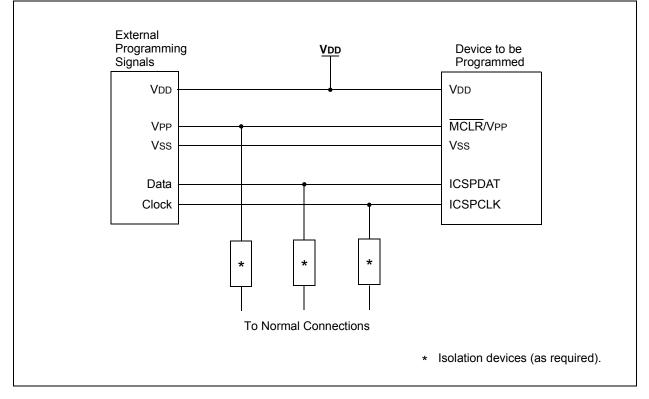

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

## 30.3 DC Characteristics: PIC16(L)F1934/6/7-I/E (Power-Down) (Continued)

| PIC16LF1         | 1 0 1                   |                      |                                                  |               | (unless otherwise stated)<br>≤ Ta ≤ +85°C for industrial<br>≤ Ta ≤ +125°C for extended |                                                                                                                                |            |                                  |  |

|------------------|-------------------------|----------------------|--------------------------------------------------|---------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|--|

| PIC16F1934/36/37 |                         |                      | Standard Operating Cond<br>Operating temperature |               |                                                                                        | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |            |                                  |  |

| Param            | Device Characteristics  | Min.                 | Тур†                                             | Max.<br>+85°C | Max.<br>+125°C                                                                         | Units                                                                                                                          | Conditions |                                  |  |

| No.              | Device Characteristics  |                      |                                                  |               |                                                                                        |                                                                                                                                | Vdd        | Note                             |  |

|                  | Power-down Base Current | (IPD) <sup>(2)</sup> |                                                  |               |                                                                                        |                                                                                                                                |            |                                  |  |

| D028             |                         | —                    | 0.1                                              | 4.0           | 8.0                                                                                    | μA                                                                                                                             | 1.8        | A/D Current (Note 1, Note 3), no |  |

|                  |                         | —                    | 0.1                                              | 5.0           | 9.0                                                                                    | μA                                                                                                                             | 3.0        | conversion in progress           |  |

| D028             |                         | _                    | 22                                               | 56            | 63                                                                                     | μA                                                                                                                             | 1.8        | A/D Current (Note 1, Note 3), no |  |

|                  |                         | _                    | 26                                               | 58            | 78                                                                                     | μA                                                                                                                             | 3.0        | conversion in progress           |  |

|                  |                         | —                    | 27                                               | 61            | 88                                                                                     | μΑ                                                                                                                             | 5.0        | ]                                |  |

| D029             |                         | —                    | 250                                              | _             | _                                                                                      | μA                                                                                                                             | 1.8        | A/D Current (Note 1, Note 3),    |  |

|                  |                         | —                    | 250                                              | —             | —                                                                                      | μA                                                                                                                             | 3.0        | conversion in progress           |  |

| D029             |                         | —                    | 280                                              |               | _                                                                                      | μΑ                                                                                                                             | 1.8        | A/D Current (Note 1, Note 3,     |  |

|                  |                         | —                    | 280                                              | _             | _                                                                                      | μA                                                                                                                             | 3.0        | Note 4), conversion in progress  |  |

|                  |                         | —                    | 280                                              |               |                                                                                        | μA                                                                                                                             | 5.0        | ]                                |  |

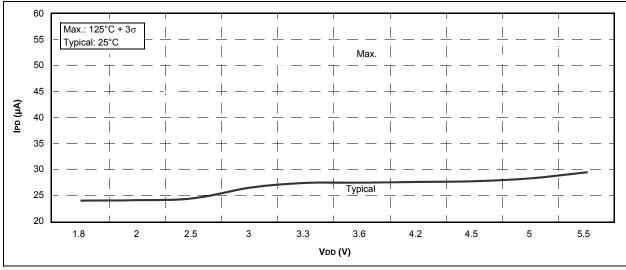

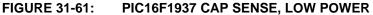

| D030             |                         | —                    | 2                                                | 7             | 11                                                                                     | μA                                                                                                                             | 1.8        | Cap Sense, Low-Power mode        |  |

|                  |                         | —                    | 3                                                | 9             | 13                                                                                     | μA                                                                                                                             | 3.0        |                                  |  |

| D030             |                         | —                    | 21                                               | 61            | 63                                                                                     | μA                                                                                                                             | 1.8        | Cap Sense, Low-Power mode        |  |

|                  |                         | —                    | 27                                               | 63            | 78                                                                                     | μA                                                                                                                             | 3.0        |                                  |  |

|                  |                         | —                    | 28                                               | 66            | 88                                                                                     | μA                                                                                                                             | 5.0        |                                  |  |

| D031             |                         | —                    | 1                                                | —             | —                                                                                      | μA                                                                                                                             | 3.0        | LCD Bias Ladder, Low-power       |  |

|                  |                         | —                    | 10                                               | _             | _                                                                                      | μA                                                                                                                             | 3.0        | LCD Bias Ladder, Medium-power    |  |

|                  |                         | —                    | 75                                               | _             | —                                                                                      | μA                                                                                                                             | 3.0        | LCD Bias Ladder, High-power      |  |

| D031             |                         | _                    | 1                                                |               |                                                                                        | μA                                                                                                                             | 5.0        | LCD Bias Ladder, Low-power       |  |

|                  |                         | _                    | 10                                               | —             | —                                                                                      | μA                                                                                                                             | 5.0        | LCD Bias Ladder, Medium-power    |  |

|                  |                         | _                    | 75                                               |               | —                                                                                      | μA                                                                                                                             | 5.0        | LCD Bias Ladder, High-power      |  |

| D032             |                         | _                    | 7.6                                              | 22            | 25                                                                                     | μA                                                                                                                             | 1.8        | Comparator, Low-Power mode       |  |

|                  |                         | _                    | 8.0                                              | 23            | 27                                                                                     | μA                                                                                                                             | 3.0        |                                  |  |

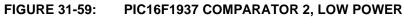

| D032             |                         | _                    | 24                                               | 65            | 75                                                                                     | μA                                                                                                                             | 1.8        | Comparator, Low-Power mode       |  |

|                  |                         | _                    | 26                                               | 75            | 88                                                                                     | μA                                                                                                                             | 3.0        |                                  |  |

|                  |                         | _                    | 28                                               | 77            | 97                                                                                     | μA                                                                                                                             | 5.0        |                                  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: A/D oscillator source is FRC.

4: 0.1 μF capacitor on VCAP (RA0).

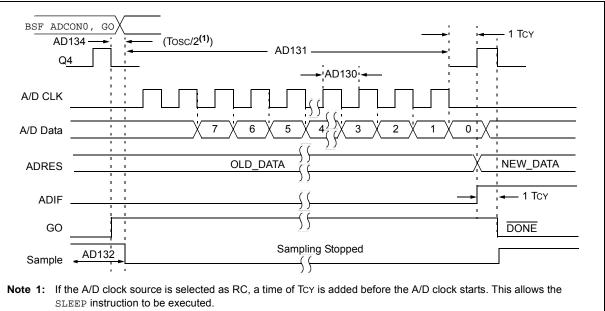

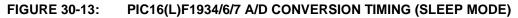

**Note 1:** If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

© 2008-2011 Microchip Technology Inc.

## 32.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 32.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 32.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## APPENDIX A: DATA SHEET REVISION HISTORY

## Revision A (12/2008)

Original release

## Revision B (04/2009)

Revised data sheet title; Revised Features section.

## Revision C (10/2009)

Added PIC16L/LF1933/34. General updates.

## Revision D (12/2009)

General updates.

## Revision E (5/2011)

Separated 193X data sheet into three separate data sheets. Added Characterization Data.

## APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{0}}$  devices to the PIC16(L)F1934/6/7 family of devices.

## B.1 PIC16F917 to PIC16F1937

## TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F917         | PIC16F1937          |

|---------------------------------------|-------------------|---------------------|

| Max. Operating Speed                  | 20 MHz            | 32 MHz              |

| Max. Program<br>Memory (Words)        | 8K                | 8K                  |

| Max. SRAM (Bytes)                     | 368               | 512                 |

| A/D Resolution                        | 10-bit            | 10-bit              |

| Timers (8/16-bit)                     | 2/1               | 4/1                 |

| Oscillator Modes                      | 4                 | 8                   |

| Brown-out Reset                       | Y                 | Y                   |

| Internal Pull-ups                     | RB<7:0>           | RB<7:0>             |

| Interrupt-on-change                   | RB<7:4>           | RB<7:0>             |

| Comparator                            | 2                 | 2                   |

| AUSART/EUSART                         | 1/0               | 0/1                 |

| Extended WDT                          | Y                 | Y                   |

| Software Control<br>Option of WDT/BOR | N                 | Y                   |

| INTOSC Frequencies                    | 30 kHz -<br>8 MHz | 500 kHz -<br>32 MHz |

| Clock Switching                       | Y                 | Y                   |

| Capacitive Sensing                    | N                 | Y                   |

| CCP/ECCP                              | 2/0               | 2/3                 |

| Enhanced PIC16 CPU                    | Ν                 | Y                   |

| MSSP/SSP                              | 0/1               | 1/0                 |

| LCD                                   | Y                 | Y                   |