Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1936-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

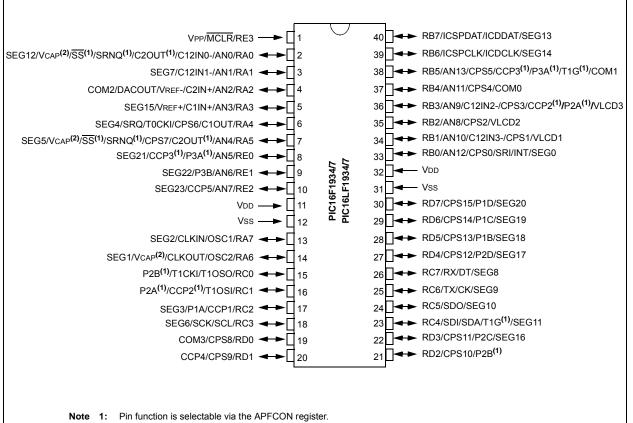

### Pin Diagram - 40-Pin PDIP (PIC16(L)F1934/7)

2: PIC16F1934/7 devices only.

| Name                                                               | Function            | Input<br>Type | Output<br>Type | Description                                                   |

|--------------------------------------------------------------------|---------------------|---------------|----------------|---------------------------------------------------------------|

| RA0/AN0/C12IN0-/C2OUT <sup>(1)</sup> /                             | RA0                 | TTL           | CMOS           | General purpose I/O.                                          |

| SRNQ <sup>(1)</sup> /SS <sup>(1)</sup> /VCAP <sup>(2)</sup> /SEG12 | AN0                 | AN            | —              | A/D Channel 0 input.                                          |

|                                                                    | C12IN0-             | AN            | _              | Comparator C1 or C2 negative input.                           |

|                                                                    | C2OUT               | _             | CMOS           | Comparator C2 output.                                         |

|                                                                    | SRNQ                | _             | CMOS           | SR Latch inverting output.                                    |

|                                                                    | SS                  | ST            | —              | Slave Select input.                                           |

|                                                                    | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1934/6/7 only). |

|                                                                    | SEG12               |               | AN             | LCD Analog output.                                            |

| RA1/AN1/C12IN1-/SEG7                                               | RA1                 | TTL           | CMOS           | General purpose I/O.                                          |

|                                                                    | AN1                 | AN            |                | A/D Channel 1 input.                                          |

|                                                                    | C12IN1-             | AN            | _              | Comparator C1 or C2 negative input.                           |

|                                                                    | SEG7                | _             | AN             | LCD Analog output.                                            |

| RA2/AN2/C2IN+/VREF-/                                               | RA2                 | TTL           | CMOS           | General purpose I/O.                                          |

| DACOUT/COM2                                                        | AN2                 | AN            | _              | A/D Channel 2 input.                                          |

|                                                                    | C2IN+               | AN            |                | Comparator C2 positive input.                                 |

|                                                                    | VREF-               | AN            | _              | A/D Negative Voltage Reference input.                         |

|                                                                    | DACOUT              | _             | AN             | Voltage Reference output.                                     |

|                                                                    | COM2                | _             | AN             | LCD Analog output.                                            |

| RA3/AN3/C1IN+/VREF+/                                               | RA3                 | TTL           | CMOS           | General purpose I/O.                                          |

| COM3 <sup>(3)</sup> /SEG15                                         | AN3                 | AN            |                | A/D Channel 3 input.                                          |

|                                                                    | C1IN+               | AN            | —              | Comparator C1 positive input.                                 |

|                                                                    | VREF+               | AN            |                | A/D Voltage Reference input.                                  |

|                                                                    | COM3 <sup>(3)</sup> | _             | AN             | LCD Analog output.                                            |

|                                                                    | SEG15               | _             | AN             | LCD Analog output.                                            |

| RA4/C1OUT/CPS6/T0CKI/SRQ/                                          | RA4                 | TTL           | CMOS           | General purpose I/O.                                          |

| CCP5/SEG4                                                          | C10UT               | _             | CMOS           | Comparator C1 output.                                         |

|                                                                    | CPS6                | AN            |                | Capacitive sensing input 6.                                   |

|                                                                    | TOCKI               | ST            |                | Timer0 clock input.                                           |

|                                                                    | SRQ                 |               | CMOS           | SR Latch non-inverting output.                                |

|                                                                    | CCP5                | ST            | CMOS           | Capture/Compare/PWM5.                                         |

|                                                                    | SEG4                | _             | AN             | LCD Analog output.                                            |

| RA5/AN4/C2OUT <sup>(1)</sup> /CPS7/                                | RA5                 | TTL           | CMOS           | General purpose I/O.                                          |

| SRNQ <sup>(1)</sup> /SS <sup>(1)</sup> /VCAP <sup>(2)</sup> /SEG5  | AN4                 | AN            | _              | A/D Channel 4 input.                                          |

|                                                                    | C2OUT               | —             | CMOS           | Comparator C2 output.                                         |

|                                                                    | CPS7                | AN            | —              | Capacitive sensing input 7.                                   |

|                                                                    | SRNQ                | _             | CMOS           | SR Latch inverting output.                                    |

|                                                                    | SS                  | ST            | _              | Slave Select input.                                           |

|                                                                    | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1934/6/7 only). |

|                                                                    | SEG5                | _             | AN             | LCD Analog output.                                            |

TABLE 1-2: PIC16(L)F1934/6/7 PINOUT DESCRIPTION

Legend:AN= Analog input or outputCMOS = CMOS compatible input or outputOD= Open DrainTTL = TTL compatible inputST= Schmitt Trigger input with CMOS levels $l^2C^{TM}$ = Schmitt Trigger input with l<sup>2</sup>C

HV = High Voltage XTAL = Crystal

levels

**Note 1:** Pin function is selectable via the APFCON register.

2: PIC16F1934/6/7 devices only.

3: PIC16(L)F1936 devices only.

4: PORTD is available on PIC16(L)F1934/7 devices only.

5: RE<2:0> are available on PIC16(L)F1934/7 devices only.

© 2008-2011 Microchip Technology Inc.

| Address                | Name     | Bit 7                      | Bit 6                                | Bit 5            | Bit 4           | Bit 3         | Bit 2         | Bit 1      | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|----------|----------------------------|--------------------------------------|------------------|-----------------|---------------|---------------|------------|-----------|----------------------|---------------------------------|

| Bank 6                 |          |                            |                                      | •                |                 |               |               |            | -         |                      |                                 |

| 300h <sup>(2)</sup>    | INDF0    | Addressing<br>(not a physi |                                      | ises contents o  | of FSR0H/FSR    | 0L to address | data memory   | /          |           | XXXX XXXX            | xxxx xxxx                       |

| 301h <sup>(2)</sup>    | INDF1    | Addressing<br>(not a physi |                                      | ises contents o  | of FSR1H/FSR    | 1L to address | data memory   | /          |           | XXXX XXXX            | xxxx xxxx                       |

| 302h <sup>(2)</sup>    | PCL      | Program Co                 | ounter (PC) Le                       | east Significant | t Byte          |               |               |            |           | 0000 0000            | 0000 0000                       |

| 303h <sup>(2)</sup>    | STATUS   | _                          | _                                    | _                | TO              | PD            | Z             | DC         | С         | 1 1000               | q quuu                          |

| 304h <sup>(2)</sup>    | FSR0L    | Indirect Data              | a Memory Ad                          | dress 0 Low P    | ointer          |               |               |            |           | 0000 0000            | uuuu uuuu                       |

| 305h <sup>(2)</sup>    | FSR0H    | Indirect Data              | a Memory Ad                          | dress 0 High P   | ointer          |               |               |            |           | 0000 0000            | 0000 0000                       |

| 306h <sup>(2)</sup>    | FSR1L    | Indirect Data              | a Memory Ad                          | dress 1 Low P    | ointer          |               |               |            |           | 0000 0000            | uuuu uuuu                       |

| 307h <sup>(2)</sup>    | FSR1H    | Indirect Data              | a Memory Ad                          | dress 1 High P   | ointer          |               |               |            |           | 0000 0000            | 0000 0000                       |

| 308h <sup>(2)</sup>    | BSR      | —                          | —                                    | _                |                 | I             | BSR<4:0>      |            |           | 0 0000               | 0 0000                          |

| 309h <sup>(2)</sup>    | WREG     | Working Re                 | gister                               |                  |                 |               |               |            |           | 0000 0000            | uuuu uuuu                       |

| 30Ah <sup>(1, 2)</sup> | PCLATH   | —                          | Write Buffer                         | for the upper 7  | bits of the Pro | gram Counte   | r             |            |           | -000 0000            | -000 0000                       |

| 30Bh <sup>(2)</sup>    | INTCON   | GIE                        | PEIE                                 | TMR0IE           | INTE            | IOCIE         | TMR0IF        | INTF       | IOCIF     | 0000 0000            | 0000 0000                       |

| 30Ch                   | —        | Unimpleme                  | nted                                 |                  |                 |               | •             | •          | •         | _                    | _                               |

| 30Dh                   | —        | Unimpleme                  | nted                                 |                  |                 |               |               |            |           | _                    | _                               |

| 30Eh                   | —        | Unimpleme                  | Unimplemented                        |                  |                 |               |               |            |           | _                    | _                               |

| 30Fh                   | —        | Unimpleme                  | nted                                 |                  |                 |               |               |            |           | _                    | _                               |

| 310h                   | —        | Unimpleme                  | nted                                 |                  |                 |               |               |            |           | _                    | _                               |

| 311h                   | CCPR3L   | Capture/Co                 | mpare/PWM I                          | Register 3 (LSI  | З)              |               |               |            |           | xxxx xxxx            | uuuu uuuu                       |

| 312h                   | CCPR3H   | Capture/Co                 | mpare/PWM I                          | Register 3 (MS   | B)              |               |               |            |           | xxxx xxxx            | uuuu uuuu                       |

| 313h                   | CCP3CON  | P3M                        | <1:0>                                | DC3E             | 3<1:0>          |               | CCP3M-        | <1:0>      |           | 0000 0000            | 0000 0000                       |

| 314h                   | PWM3CON  | P3RSEN                     |                                      |                  | P               | 3DC<6:0>      |               |            |           | 0000 0000            | 0000 0000                       |

| 315h                   | CCP3AS   | <b>CCP3ASE</b>             |                                      | CCP3AS<2:0       | >               | PSS3A         | C<1:0>        | PSS3B      | D<1:0>    | 0000 0000            | 0000 0000                       |

| 316h                   | PSTR3CON | _                          | —                                    | _                | STR3SYNC        | STR3D         | STR3C         | STR3B      | STR3A     | 0 0001               | 0 0001                          |

| 317h                   | —        | Unimpleme                  | nted                                 |                  |                 |               |               |            |           | _                    | _                               |

| 318h                   | CCPR4L   | Capture/Co                 | mpare/PWM I                          | Register 4 (LSI  | 3)              |               |               |            |           | xxxx xxxx            | uuuu uuuu                       |

| 319h                   | CCPR4H   | Capture/Co                 | Capture/Compare/PWM Register 4 (MSB) |                  |                 |               |               |            | xxxx xxxx | uuuu uuuu            |                                 |

| 31Ah                   | CCP4CON  | _                          | — — DC4B<1:0> ССР4М<3:0>             |                  |                 |               |               |            | 00 0000   | 00 0000              |                                 |

| 31Bh                   | _        | Unimpleme                  | nted                                 |                  |                 |               |               |            |           | —                    | —                               |

| 31Ch                   | CCPR5L   | Capture/Co                 | mpare/PWM F                          | Register 5 (LSI  | 3)              |               |               |            |           | xxxx xxxx            | uuuu uuuu                       |

| 31Dh                   | CCPR5H   | Capture/Co                 | mpare/PWM F                          | Register 5 (MS   | B)              |               |               |            |           | xxxx xxxx            | uuuu uuuu                       |

| 31Eh                   | CCP5CON  | —                          | —                                    | DC5E             | 8<1:0>          |               | CCP5M         | <3:0>      |           | 00 0000              | 00 0000                         |

| 31Fh                   | —        | Unimpleme                  | nted                                 |                  |                 |               |               |            |           | —                    | —                               |

| Leaend:                |          |                            | opgod vo                             | luo dopondo a    | n condition =   | unimplomon    | tod road as ' | o' – rocor | had       |                      |                                 |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

NOTES:

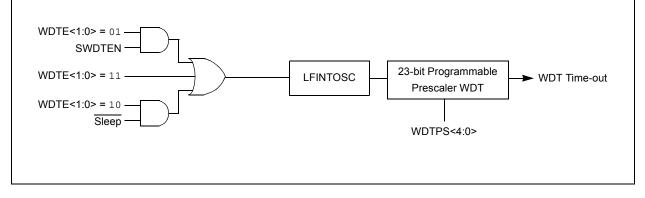

# **10.0 WATCHDOG TIMER**

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (typical)

- Multiple Reset conditions

- Operation during Sleep

#### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

## 11.0 DATA EEPROM AND FLASH PROGRAM MEMORY CONTROL

The data EEPROM and Flash program memory are readable and writable during normal operation (full VDD range). These memories are not directly mapped in the register file space. Instead, they are indirectly addressed through the Special Function Registers (SFRs). There are six SFRs used to access these memories:

- EECON1

- EECON2

- EEDATL

- EEDATH

- EEADRL

- EEADRH

When interfacing the data memory block, EEDATL holds the 8-bit data for read/write, and EEADRL holds the address of the EEDATL location being accessed. These devices have 256 bytes of data EEPROM with an address range from 0h to 0FFh.

When accessing the program memory block, the EEDATH:EEDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the EEADRL and EEADRH registers form a 2-byte word that holds the 15-bit address of the program memory location being read.

The EEPROM data memory allows byte read and write. An EEPROM byte write automatically erases the location and writes the new data (erase before write).

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

Depending on the setting of the Flash Program Memory Self Write Enable bits WRT<1:0> of the Configuration Word 2, the device may or may not be able to write certain blocks of the program memory. However, reads from the program memory are always allowed.

When the device is code-protected, the device programmer can no longer access data or program memory. When code-protected, the CPU may continue to read and write the data EEPROM memory and Flash program memory.

### 11.1 EEADRL and EEADRH Registers

The EEADRH:EEADRL register pair can address up to a maximum of 256 bytes of data EEPROM or up to a maximum of 32K words of program memory.

When selecting a program address value, the MSB of the address is written to the EEADRH register and the LSB is written to the EEADRL register. When selecting a EEPROM address value, only the LSB of the address is written to the EEADRL register.

#### 11.1.1 EECON1 AND EECON2 REGISTERS

EECON1 is the control register for EE memory accesses.

Control bit EEPGD determines if the access will be a program or data memory access. When clear, any subsequent operations will operate on the EEPROM memory. When set, any subsequent operations will operate on the program memory. On Reset, EEPROM is selected by default.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

Interrupt flag bit EEIF of the PIR2 register is set when write is complete. It must be cleared in the software.

Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence. To enable writes, a specific pattern must be written to EECON2.

NOTES:

NOTES:

## 22.5 Timer2/4/6 Control Register

#### REGISTER 22-1: TXCON: TIMER2/TIMER4/TIMER6 CONTROL REGISTER

| U-0            | R/W-0/0                  | R/W-0/0                     | R/W-0/0      | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|----------------|--------------------------|-----------------------------|--------------|----------------|------------------|------------------|--------------|--|--|--|

|                |                          | TOUTPS<3:0>                 |              |                | TMRxON           | TxCKP            | S<1:0>       |  |  |  |

| oit 7          |                          |                             |              |                |                  |                  | bit C        |  |  |  |

|                |                          |                             |              |                |                  |                  |              |  |  |  |

| _egend:        |                          |                             |              |                |                  |                  |              |  |  |  |

|                |                          |                             |              | U = Unimpler   | mented bit, read | l as '0'         |              |  |  |  |

| u = Bit is un  | changed                  | x = Bit is unkr             | nown         | -n/n = Value   | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| 1' = Bit is se | et                       | '0' = Bit is clea           | ared         |                |                  |                  |              |  |  |  |

| oit 7          | Unimpleme                | ented: Read as '            | 0'           |                |                  |                  |              |  |  |  |

| oit 6-3        | -                        | :0>: Timer Outpu            |              | Select bits    |                  |                  |              |  |  |  |

|                | 0000 = 1:1               |                             |              |                |                  |                  |              |  |  |  |

|                | 0001 = 1:2               | Postscaler                  |              |                |                  |                  |              |  |  |  |

|                | 0010 = 1:3               |                             |              |                |                  |                  |              |  |  |  |

|                | 0011 = 1:4               |                             |              |                |                  |                  |              |  |  |  |

|                | 0100 = 1:5               |                             |              |                |                  |                  |              |  |  |  |

|                | 0101 = 1:6<br>0110 = 1:7 |                             |              |                |                  |                  |              |  |  |  |

|                | 0111 = <b>1</b> :8       |                             |              |                |                  |                  |              |  |  |  |

|                | 1000 = 1:9               |                             |              |                |                  |                  |              |  |  |  |

|                | 1001 = 1:10              |                             |              |                |                  |                  |              |  |  |  |

|                | 1010 <b>= 1:11</b>       |                             |              |                |                  |                  |              |  |  |  |

|                | 1011 <b>= 1:12</b>       | 1011 = 1:12 Postscaler      |              |                |                  |                  |              |  |  |  |

|                | 1100 = 1:13              |                             |              |                |                  |                  |              |  |  |  |

|                | 1101 = 1:14              |                             |              |                |                  |                  |              |  |  |  |

|                | 1110 = 1:15              |                             |              |                |                  |                  |              |  |  |  |

| pit 2          | 1111 = 1:16              | imerx On bit                |              |                |                  |                  |              |  |  |  |

| <i>J</i> IL 2  | 1 = Timerx               |                             |              |                |                  |                  |              |  |  |  |

|                | 1 = Timerx<br>0 = Timerx |                             |              |                |                  |                  |              |  |  |  |

| oit 1-0        | TxCKPS<1:                | : <b>0&gt;:</b> Timer2-type | Clock Presca | le Select bits |                  |                  |              |  |  |  |

|                | 00 = Presca              | ler is 1                    |              |                |                  |                  |              |  |  |  |

|                | 01 = Presca              | aler is 4                   |              |                |                  |                  |              |  |  |  |

|                | 10 = Presca              |                             |              |                |                  |                  |              |  |  |  |

|                | 11 = Presca              | ler is 64                   |              |                |                  |                  |              |  |  |  |

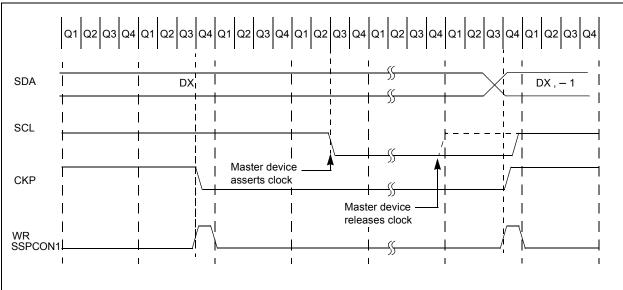

### 24.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 24.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the R/ $\overline{W}$  bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready, CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on whether the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the 9th falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPBUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 24.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

| Note: | Previous versions of the module did not      |

|-------|----------------------------------------------|

|       | stretch the clock if the second address byte |

|       | did not match.                               |

#### 24.5.6.3 Byte NACKing

When the AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCL for a received matching address byte. When the DHEN bit of SSPCON3 is set; CKP is cleared after the 8th falling edge of SCL for received data.

Stretching after the 8th falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

#### 24.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 24-22).

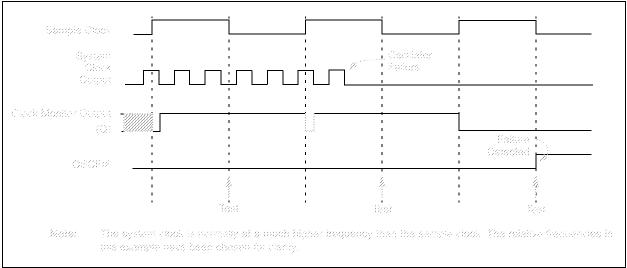

#### FIGURE 24-23: CLOCK SYNCHRONIZATION TIMING

### 25.2 Clock Accuracy with Asynchronous Operation

Г

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind. The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 5.2.2** "Internal Clock Sources" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 25.3.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

### REGISTER 25-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-/0           | R/W-0/0         | R/W-0/0                       | R/W-0/0         | R/W-0/0          | R/W-0/0              | R-1/1 | R/W-0/0 |

|------------------|-----------------|-------------------------------|-----------------|------------------|----------------------|-------|---------|

| CSRC             | TX9             | TXEN <sup>(1)</sup>           | SYNC            | SENDB            | BRGH                 | TRMT  | TX9D    |

| bit 7            |                 |                               |                 |                  |                      |       | bit (   |

| Legend:          |                 |                               |                 |                  |                      |       |         |

| R = Readable     | bit             | W = Writable bi               | t               | II = I Inimpleme | ented bit, read as ' | ٥'    |         |

| u = Bit is unch  |                 | x = Bit is unkno              |                 | •                | POR and BOR/Va       |       | Resets  |

| '1' = Bit is set | angeu           | '0' = Bit is clear            |                 |                  |                      |       | 103013  |

| 1 Dit ib bet     |                 | 0 Dit ib bicai                | cu              |                  |                      |       |         |

| bit 7            | CSRC: Clock     | Source Select bit             |                 |                  |                      |       |         |

| bit i            | Asynchronous    |                               |                 |                  |                      |       |         |

|                  | Don't care      | <u></u>                       |                 |                  |                      |       |         |

|                  | Synchronous r   | mode:                         |                 |                  |                      |       |         |

|                  | 1 = Master n    | node (clock gener             | ated internally | from BRG)        |                      |       |         |

|                  | 0 = Slave mo    | ode (clock from e             | kternal source) |                  |                      |       |         |

| bit 6            | TX9: 9-bit Trar | nsmit Enable bit              |                 |                  |                      |       |         |

|                  | 1 = Selects 9   | 9-bit transmission            |                 |                  |                      |       |         |

|                  | 0 = Selects 8   | B-bit transmission            |                 |                  |                      |       |         |

| bit 5            | TXEN: Transm    | nit Enable bit <sup>(1)</sup> |                 |                  |                      |       |         |

|                  | 1 = Transmit    | enabled                       |                 |                  |                      |       |         |

|                  | 0 = Transmit    | disabled                      |                 |                  |                      |       |         |

| bit 4            | SYNC: EUSA      | RT Mode Select b              | it              |                  |                      |       |         |

|                  | 1 = Synchron    |                               |                 |                  |                      |       |         |

|                  | 0 = Asynchro    |                               |                 |                  |                      |       |         |

| bit 3            |                 | Break Character               | bit             |                  |                      |       |         |

|                  | Asynchronous    |                               |                 |                  |                      |       |         |

|                  |                 |                               |                 | eared by hardwa  | are upon completio   | n)    |         |

|                  | Synchronous r   | ak transmission c             | ompieted        |                  |                      |       |         |

|                  | Don't care      | <u>mode</u> .                 |                 |                  |                      |       |         |

| bit 2            |                 | Baud Rate Select              | hit             |                  |                      |       |         |

| Sit 2            | Asynchronous    |                               | bit             |                  |                      |       |         |

|                  | 1 = High spece  |                               |                 |                  |                      |       |         |

|                  | 0 = Low spee    |                               |                 |                  |                      |       |         |

|                  | Synchronous r   | mode:                         |                 |                  |                      |       |         |

|                  | Unused in this  | mode                          |                 |                  |                      |       |         |

| bit 1            | TRMT: Transm    | nit Shift Register S          | Status bit      |                  |                      |       |         |

|                  | 1 = TSR emp     | oty                           |                 |                  |                      |       |         |

|                  | 0 = TSR full    |                               |                 |                  |                      |       |         |

| bit 0            | TX9D: Ninth b   | it of Transmit Dat            | а               |                  |                      |       |         |

|                  | Can be addres   |                               |                 |                  |                      |       |         |

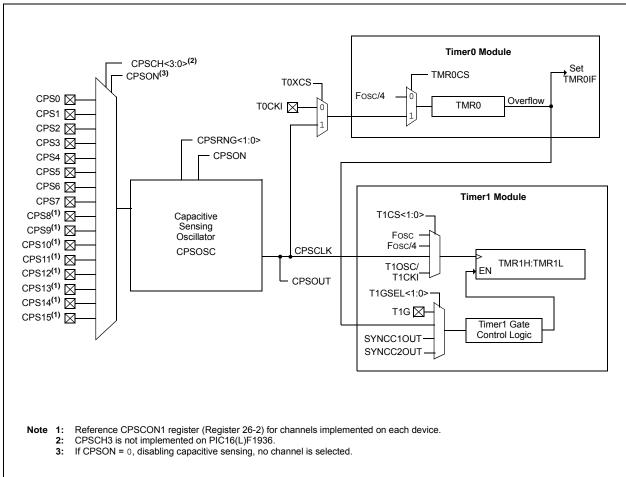

## 26.0 CAPACITIVE SENSING (CPS) MODULE

The Capacitive Sensing (CPS) module allows for an interaction with an end user without a mechanical interface. In a typical application, the CPS module is attached to a pad on a Printed Circuit Board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the CPS module. The CPS module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- Multiple power ranges

- Multiple timer resources

- Software control

- Operation during Sleep

#### FIGURE 26-1: CAPACITIVE SENSING BLOCK DIAGRAM

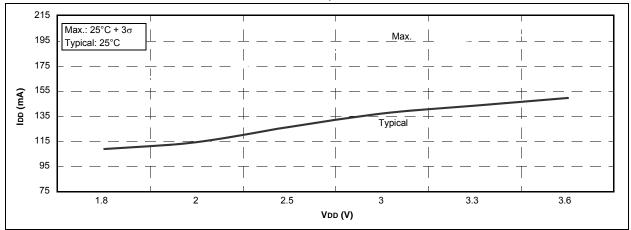

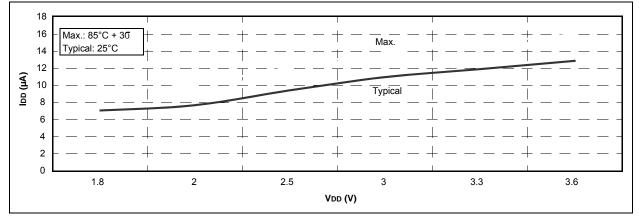

#### 30.3 DC Characteristics: PIC16(L)F1934/6/7-I/E (Power-Down)

| PIC16LF1         | 934/36/37               |                      | r <b>d Opera</b> t<br>ng temper | •                                                                                                                                                                                       | -40°C ≤ | TA ≤ +85° | nerwise stated)<br>°C for industrial<br>5°C for extended |                                    |  |  |

|------------------|-------------------------|----------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|----------------------------------------------------------|------------------------------------|--|--|

| PIC16F1934/36/37 |                         |                      |                                 | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |         |           |                                                          |                                    |  |  |

| Param            | Device Characteristics  | Min.                 | Typ†                            | Max.                                                                                                                                                                                    | Max.    | Units     |                                                          | Conditions                         |  |  |

| No.              | Device onaracteristics  |                      | וקעי                            | +85°C                                                                                                                                                                                   | +125°C  | Units     | Vdd                                                      | Note                               |  |  |

|                  | Power-down Base Current | (IPD) <sup>(2)</sup> |                                 |                                                                                                                                                                                         |         |           |                                                          |                                    |  |  |

| D023             |                         |                      | 0.06                            | 1.0                                                                                                                                                                                     | 8.0     | μA        | 1.8                                                      | WDT, BOR, FVR, and T1OSC           |  |  |

|                  |                         |                      | 0.08                            | 2.0                                                                                                                                                                                     | 9.0     | μA        | 3.0                                                      | disabled, all Peripherals Inactive |  |  |

| D023             |                         | _                    | 21                              | 55                                                                                                                                                                                      | 63      | μA        | 1.8                                                      | WDT, BOR, FVR, and T1OSC           |  |  |

|                  |                         | _                    | 25                              | 58                                                                                                                                                                                      | 78      | μA        | 3.0                                                      | disabled, all Peripherals Inactive |  |  |

|                  |                         | _                    | 27                              | 60                                                                                                                                                                                      | 88      | μA        | 5.0                                                      |                                    |  |  |

| D024             |                         |                      | 0.5                             | 4.0                                                                                                                                                                                     | 9.0     | μA        | 1.8                                                      | LPWDT Current (Note 1)             |  |  |

|                  |                         | —                    | 0.8                             | 5.0                                                                                                                                                                                     | 10      | μA        | 3.0                                                      |                                    |  |  |

| D024             |                         | _                    | 23                              | 57                                                                                                                                                                                      | 65      | μA        | 1.8                                                      | LPWDT Current (Note 1)             |  |  |

|                  |                         | _                    | 26                              | 59                                                                                                                                                                                      | 80      | μA        | 3.0                                                      |                                    |  |  |

|                  |                         | —                    | 28                              | 61                                                                                                                                                                                      | 90      | μA        | 5.0                                                      |                                    |  |  |

| D025             |                         | —                    | 15                              | 28                                                                                                                                                                                      | 30      | μA        | 1.8                                                      | FVR current                        |  |  |

|                  |                         | _                    | 15                              | 30                                                                                                                                                                                      | 33      | μA        | 3.0                                                      |                                    |  |  |

| D025             |                         |                      | 38                              | 96                                                                                                                                                                                      | 100     | μA        | 1.8                                                      | FVR current (Note 4)               |  |  |

|                  |                         |                      | 45                              | 110                                                                                                                                                                                     | 120     | μA        | 3.0                                                      |                                    |  |  |

|                  |                         | —                    | 90                              | 140                                                                                                                                                                                     | 155     | μA        | 5.0                                                      |                                    |  |  |

| D026             |                         |                      | 13                              | 25                                                                                                                                                                                      | 28      | μA        | 3.0                                                      | BOR Current (Note 1)               |  |  |

| D026             |                         | _                    | 40                              | 110                                                                                                                                                                                     | 120     | μA        | 3.0                                                      | BOR Current (Note 1, Note 4)       |  |  |

|                  |                         | —                    | 87                              | 140                                                                                                                                                                                     | 155     | μA        | 5.0                                                      |                                    |  |  |

| D027             |                         | _                    | 0.6                             | 5.0                                                                                                                                                                                     | 9.0     | μA        | 1.8                                                      | T1OSC Current (Note 1)             |  |  |

|                  |                         | —                    | 1.8                             | 7.0                                                                                                                                                                                     | 12      | μA        | 3.0                                                      |                                    |  |  |

| D027             |                         | _                    | 22                              | 57                                                                                                                                                                                      | 60      | μA        | 1.8                                                      | T1OSC Current (Note 1)             |  |  |

|                  |                         | _                    | 29                              | 62                                                                                                                                                                                      | 70      | μA        | 3.0                                                      |                                    |  |  |

|                  |                         | —                    | 35                              | 66                                                                                                                                                                                      | 85      | μA        | 5.0                                                      |                                    |  |  |

t Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: A/D oscillator source is FRC.

4: 0.1  $\mu$ F capacitor on VCAP (RA0).

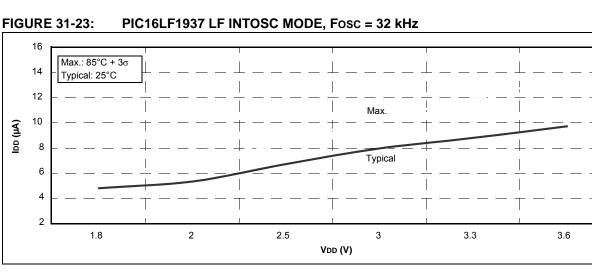

#### FIGURE 31-24: PIC16LF1937 MF INTOSC MODE, Fosc = 500 kHz

### FIGURE 31-25: PIC16LF1937 LP OSCILLATOR MODE, Fosc = 32 kHz

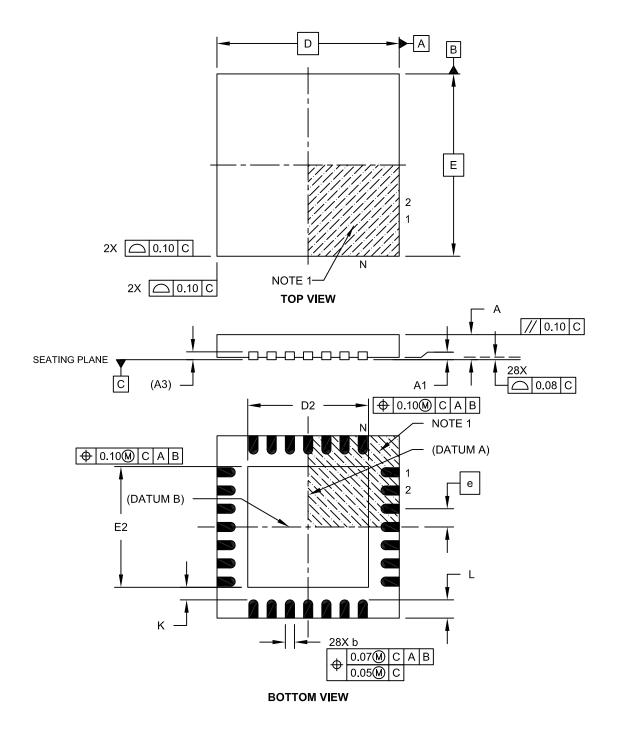

28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2

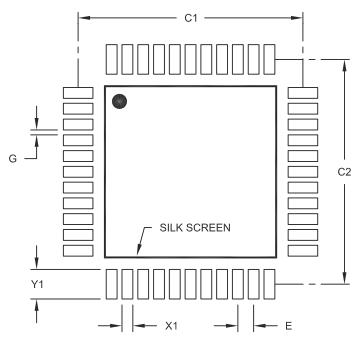

### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | N    | ILLIMETER | S    |

|------------------------|----------|------|-----------|------|

| Dimensior              | i Limits | MIN  | NOM       | MAX  |

| Number of Pins         | N        |      | 28        |      |

| Pitch                  | е        |      | 0.40 BSC  |      |

| Overall Height         | A        | 0.45 | 0.50      | 0.55 |

| Standoff               | A1       | 0.00 | 0.02      | 0.05 |

| Contact Thickness      | A3       |      | 0.127 REF |      |

| Overall Width          | E        |      | 4.00 BSC  |      |

| Exposed Pad Width      | E2       | 2.55 | 2.65      | 2.75 |

| Overall Length         | D        |      | 4.00 BSC  |      |

| Exposed Pad Length     | D2       | 2.55 | 2.65      | 2.75 |

| Contact Width          | b        | 0.15 | 0.20      | 0.25 |

| Contact Length         | L        | 0.30 | 0.40      | 0.50 |

| Contact-to-Exposed Pad | K        | 0.20 | -         | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2

### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                          | MILLIM | ETERS | _        |      |

|--------------------------|--------|-------|----------|------|

| Dimension                | Limits | MIN   | NOM      | MAX  |

| Contact Pitch            | E      |       | 0.80 BSC |      |

| Contact Pad Spacing      | C1     |       | 11.40    |      |

| Contact Pad Spacing      | C2     |       | 11.40    |      |

| Contact Pad Width (X44)  | X1     |       |          | 0.55 |

| Contact Pad Length (X44) | Y1     |       |          | 1.50 |

| Distance Between Pads    | G      | 0.25  |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A

| SPI Slave Mode (CKE = 1) 408                       |

|----------------------------------------------------|

| Synchronous Reception (Master Mode, SREN) 317      |

| Synchronous Transmission                           |

| Synchronous Transmission (Through TXEN)            |

| Timer0 and Timer1 External Clock 401               |

| Timer1 Incrementing Edge                           |

| Two Speed Start-up                                 |

| Type-A in 1/2 MUX, 1/2 Bias Drive                  |

| Type-A in 1/2 MUX, 1/3 Bias Drive                  |

| Type-A in 1/3 MUX, 1/3 Bias Drive                  |

|                                                    |

| Type-A in 1/3 MUX, 1/3 Bias Drive                  |

| Type-A in 1/4 MUX, 1/3 Bias Drive                  |

| Type-A/Type-B in Static Drive                      |

| Type-B in 1/2 MUX, 1/2 Bias Drive                  |

| Type-B in 1/2 MUX, 1/3 Bias Drive                  |

| Type-B in 1/3 MUX, 1/2 Bias Drive                  |

| Type-B in 1/3 MUX, 1/3 Bias Drive                  |

| Type-B in 1/4 MUX, 1/3 Bias Drive                  |

| USART Synchronous Receive (Master/Slave) 406       |

| USART Synchronous Transmission (Master/Slave). 405 |

| Wake-up from Interrupt                             |

| Timing Diagrams and Specifications                 |

| PLL Clock                                          |

| Timing Parameter Symbology                         |

| Timing Requirements                                |

| I <sup>2</sup> C Bus Data                          |

| I2C Bus Start/Stop Bits                            |

| SPI Mode                                           |

| TMR0 Register                                      |

|                                                    |

| TMR1H Register                                     |

| TMR1L Register                                     |

| TMR2 Register                                      |

| TRIS                                               |

| TRISA Register                                     |

| TRISB                                              |

| TRISB Register 40, 140                             |

| TRISC                                              |

| TRISC Register40, 144                              |

| TRISD 146                                          |

| TRISD Register40, 147                              |

| TRISE                                              |

| TRISE Register                                     |

| Two-Speed Clock Start-up Mode                      |

| TXCON (Timer2/4/6) Register                        |

| TXREG                                              |

| TXREG Register                                     |

| TXSTA Register                                     |

| BRGH Bit                                           |

|                                                    |

| U                                                  |

#### W

| Wake-up on Break                     | 311 |

|--------------------------------------|-----|

| Wake-up Using Interrupts             | 112 |

| Watchdog Timer (WDT)                 |     |

| Associated Registers                 |     |

| Configuration Word w/ Watchdog Timer |     |

| Modes                                | 114 |

| Specifications                       |     |

| WCOL                                 |     |

| WCOL Status Flag 273                 |     |

| WDTCON Register                      |     |

| WPUB Register                        |     |

| Write Protection                     |     |

| WWW Address                          |     |

| WWW, On-Line Support                 |     |

|                                      |     |

### ۷

USART

VREF. SEE ADC Reference Voltage

Synchronous Master Mode