#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

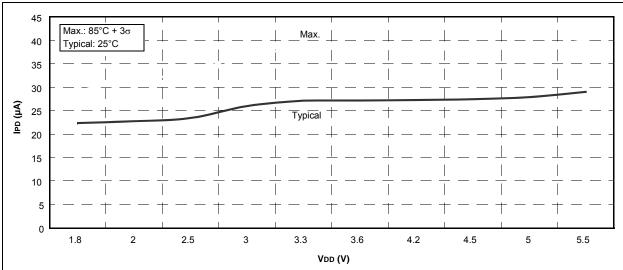

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1936-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

The PIC16(L)F1934/6/7 are described within this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1934/6/7 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral              |             | PIC16F193X | PIC16LF193X |

|-------------------------|-------------|------------|-------------|

| ADC                     | •           | •          |             |

| Capacitive Sensing Mod  | dule        | •          | •           |

| Digital-to-Analog Conve | erter (DAC) | •          | •           |

| EUSART                  |             | ٠          | •           |

| Fixed Voltage Reference | e (FVR)     | •          | •           |

| LCD                     |             | ٠          | •           |

| SR Latch                |             | •          | •           |

| Temperature Indicator   |             | •          | •           |

| Capture/Compare/PWM     |             |            |             |

|                         | ECCP1       | ٠          | •           |

|                         | ECCP2       | •          | •           |

|                         | ECCP3       | •          | •           |

|                         | CCP4        | ٠          | •           |

|                         | CCP5        | •          | •           |

| Comparators             |             |            |             |

|                         | C1          | ٠          | •           |

|                         | C2          | •          | •           |

| Operational Amplifiers  |             |            |             |

|                         | OPA1        | •          | •           |

|                         | OPA2        | •          | •           |

| Master Synchronous Se   | erial Ports |            |             |

|                         | MSSP1       | ٠          | •           |

| Timers                  |             |            |             |

|                         | Timer0      | ٠          | •           |

|                         | Timer1      | •          | •           |

|                         | Timer2      | ٠          | •           |

|                         | Timer4      | ٠          | •           |

|                         | Timer6      | •          | •           |

#### **TABLE 1-2:** PIC16(L)F1934/6/7 PINOUT DESCRIPTION (CONTINUED)

| Name                                  | Function | Input<br>Type    | Output<br>Type | Description                          |

|---------------------------------------|----------|------------------|----------------|--------------------------------------|

| RC4/SDI/SDA/T1G <sup>(1)</sup> /SEG11 | RC4      | ST               | CMOS           | General purpose I/O.                 |

|                                       | SDI      | ST               | —              | SPI data input.                      |

|                                       | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C™ data input/output. |

|                                       | T1G      | ST               | —              | Timer1 Gate input.                   |

|                                       | SEG11    | _                | AN             | LCD Analog output.                   |

| RC5/SDO/SEG10                         | RC5      | ST               | CMOS           | General purpose I/O.                 |

|                                       | SDO      |                  | CMOS           | SPI data output.                     |

|                                       | SEG10    |                  | AN             | LCD Analog output.                   |

| RC6/TX/CK/CCP3/P3A/SEG9               | RC6      | ST               | CMOS           | General purpose I/O.                 |

|                                       | TX       | _                | CMOS           | USART asynchronous transmit.         |

|                                       | СК       | ST               | CMOS           | USART synchronous clock.             |

|                                       | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.                |

|                                       | P3A      | _                | CMOS           | PWM output.                          |

|                                       | SEG9     | _                | AN             | LCD Analog output.                   |

| RC7/RX/DT/P3B/SEG8                    | RC7      | ST               | CMOS           | General purpose I/O.                 |

|                                       | RX       | ST               | —              | USART asynchronous input.            |

|                                       | DT       | ST               | CMOS           | USART synchronous data.              |

|                                       | P3B      | _                | CMOS           | PWM output.                          |

|                                       | SEG8     |                  | AN             | LCD Analog output.                   |

| RD0 <sup>(4)</sup> /CPS8/COM3         | RD0      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS8     | AN               | _              | Capacitive sensing input 8.          |

|                                       | COM3     | _                | AN             | LCD analog output.                   |

| RD1 <sup>(4)</sup> /CPS9/CCP4         | RD1      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS9     | AN               | _              | Capacitive sensing input 9.          |

|                                       | CCP4     | ST               | CMOS           | Capture/Compare/PWM4.                |

| RD2 <sup>(4)</sup> /CPS10/P2B         | RD2      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS10    | AN               | _              | Capacitive sensing input 10.         |

|                                       | P2B      |                  | CMOS           | PWM output.                          |

| RD3 <sup>(4)</sup> /CPS11/P2C/SEG16   | RD3      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS11    | AN               | _              | Capacitive sensing input 11.         |

|                                       | P2C      |                  | CMOS           | PWM output.                          |

|                                       | SEG16    |                  | AN             | LCD analog output.                   |

| RD4 <sup>(4)</sup> /CPS12/P2D/SEG17   | RD4      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS12    | AN               | —              | Capacitive sensing input 12.         |

|                                       | P2D      | _                | CMOS           | PWM output.                          |

|                                       | SEG17    | _                | AN             | LCD analog output.                   |

| RD5 <sup>(4)</sup> /CPS13/P1B/SEG18   | RD5      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS13    | AN               | —              | Capacitive sensing input 13.         |

|                                       | P1D      | _                | CMOS           | PWM output.                          |

|                                       | SEG18    | _                | AN             | LCD analog output.                   |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$

HV = High Voltage

OD = Open Drain

XTAL = Crystal

Note 1: Pin function is selectable via the APFCON register.

- 2: PIC16F1934/6/7 devices only.

- 3: PIC16(L)F1936 devices only.

- 4: PORTD is available on PIC16(L)F1934/7 devices only.

- 5: RE<2:0> are available on PIC16(L)F1934/7 devices only.

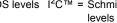

### 3.2.2 SPECIAL FUNCTION REGISTER

The Special Function Registers (SFR) are registers used by the application to control the desired operation of peripheral functions in the device. The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.2.3 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 3.2.3.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See **Section 3.5.2** "**Linear Data Memory**" for more information.

#### 3.2.4 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-3: BANKED MEMORY PARTITIONING

#### 3.2.5 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-2.

#### TABLE 3-2: MEMORY MAP TABLES

| Device      | Banks | Table No.             |

|-------------|-------|-----------------------|

| PIC16F1934  | 0-7   | Table 3-3             |

| PIC16LF1934 | 8-15  | Table 3-4, Table 3-10 |

|             | 16-23 | Table 3-7             |

|             | 23-31 | Table 3-8, Table 3-11 |

| PIC16F1936  | 0-7   | Table 3-5             |

| PIC16LF1936 | 8-15  | Table 3-6, Table 3-9  |

|             | 16-23 | Table 3-7             |

|             | 23-31 | Table 3-8, Table 3-11 |

| PIC16F1937  | 0-7   | Table 3-5             |

| PIC16LF1937 | 8-15  | Table 3-6, Table 3-10 |

|             | 16-23 | Table 3-7             |

|             | 23-31 | Table 3-8, Table 3-11 |

## TABLE 3-9:PIC16(L)F1936 MEMORY MAP,<br/>BANK 15

|            |    | Bank 15              |                            |

|------------|----|----------------------|----------------------------|

| 791        | h  | LCDCON               |                            |

| 792        |    | LCDPS                |                            |

| 793        |    | LCDREF               |                            |

| 793        |    | LCDCST               |                            |

| 794        |    | LCDRL                |                            |

| 796        |    | _                    |                            |

| 790        |    |                      |                            |

| 797        |    | LCDSE0               |                            |

| 798        |    | LCDSE1               |                            |

|            |    | LODGET               |                            |

| 79A        |    |                      |                            |

| 79B        |    |                      |                            |

| 790        |    | _                    |                            |

| 79D        |    | _                    |                            |

| 79E        |    | —                    |                            |

| 79F        |    |                      |                            |

| 7A0<br>7A1 |    | LCDDATA0<br>LCDDATA1 |                            |

| 7A1        |    | LODDAIAI             |                            |

| 7A2<br>7A3 |    | LCDDATA3             |                            |

| 7A3        |    | LCDDATA4             |                            |

| 7A5        |    | _                    |                            |

| 7A6        |    | LCDDATA6             |                            |

| 7A7        | 'n | LCDDATA7             |                            |

| 7A8        |    | —                    |                            |

| 7A9        |    | LCDDATA9             |                            |

| 744        |    | LCDDATA10            |                            |

| 7AB        |    |                      |                            |

| 7AC        |    | —                    |                            |

| 7AD        |    | —                    |                            |

| 7AE        |    | _                    |                            |

| 7AF        |    | _                    |                            |

| 7B0        |    | _                    |                            |

| 7B1        |    | —                    |                            |

| 7B2        | h  | —                    |                            |

| 7B3        |    | —                    |                            |

| 7B4        | h  | —                    |                            |

| 7B5        | h  | _                    |                            |

| 7B6        | h  | _                    |                            |

| 7B7        | 'n | —                    |                            |

| 7B8        | h  |                      |                            |

|            |    | Unimplemented        |                            |

|            |    | Read as '0'          |                            |

|            |    |                      |                            |

| 7EF        | ĥ  |                      |                            |

| Legend:    |    | = Unimplemented d    | ata memory locations, read |

| Logona.    | as | '0'.                 | ala memory locations, rea  |

|            |    |                      |                            |

## TABLE 3-10:PIC16(L)F1934/7 MEMORY<br/>MAP, BANK 15

|               | ,                            |                            |

|---------------|------------------------------|----------------------------|

|               | Bank 15                      |                            |

| 791h          | LCDCON                       |                            |

| 792h          | LCDPS                        |                            |

| 793h          | LCDREF                       |                            |

| 794h          | LCDCST                       |                            |

| 795h          | LCDRL                        |                            |

| 796h          | _                            |                            |

| 797h          |                              |                            |

| 797h<br>798h  | LCDSE0                       |                            |

|               | LCDSE1                       |                            |

| 799h          | LCDSE1                       |                            |

| 79Ah          | LCDSEZ                       |                            |

| 79Bh          | —                            |                            |

| 79Ch          | —                            |                            |

| 79Dh          | —                            |                            |

| 79Eh          | —                            |                            |

| 79Fh          | —                            |                            |

| 7A0h          | LCDDATA0                     |                            |

| 7A1h          | LCDDATA1                     |                            |

| 7A2h<br>7A3h  | LCDDATA2<br>LCDDATA3         |                            |

| 7A311<br>7A4h | LCDDATA4                     |                            |

| 7A5h          | LCDDATA5                     |                            |

| 7A6h          | LCDDATA6                     |                            |

| 7A7h          | LCDDATA7                     |                            |

| 7A8h          | LCDDATA8                     |                            |

| 7A9h<br>7AAh  | LCDDATA9<br>LCDDATA10        |                            |

| 7ABh          | LCDDATA10                    |                            |

| 7ACh          | _                            |                            |

| 7ADh          |                              |                            |

|               |                              |                            |

| 7AEh          |                              |                            |

| 7AFh          |                              |                            |

| 7B0h          |                              |                            |

| 7B1h          | _                            |                            |

| 7B2h          |                              |                            |

| 7B3h          | —                            |                            |

| 7B4h          |                              |                            |

| 7B5h          | —                            |                            |

| 7B6h          | —                            |                            |

| 7B7h          | —                            |                            |

| 7B8h          |                              |                            |

|               | Unimplemented<br>Read as '0' |                            |

| 7EFh          |                              |                            |

| Legend:<br>as | = Unimplemented d            | ata memory locations, read |

### 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Word 1 to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See **Section 5.3 "Clock Switching"**for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the state of the  $\overline{\text{CLKOUTEN}}$  bit in Configuration Word 1.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

### 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

The High-Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running and can be utilized.

The High-Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High-Frequency Internal Oscillator Status Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium-Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running and can be utilized.

### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word 1. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 oscillator and RC).

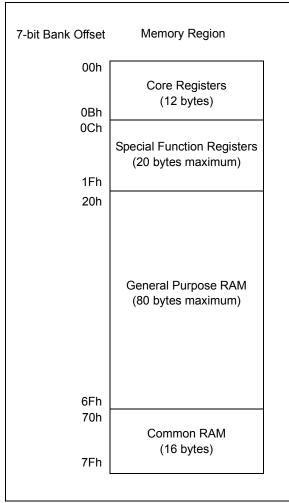

FIGURE 5-9: FSCM BLOCK DIAGRAM

#### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

#### 6.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Word 1.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Word 1. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 6-3 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Word 2.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0>                                                                                                         | SBOREN | Device Mode | BOR Mode | Device<br>Operation upon<br>release of POR | Device<br>Operation upon<br>wake- up from<br>Sleep |  |

|--------------------------------------------------------------------------------------------------------------------|--------|-------------|----------|--------------------------------------------|----------------------------------------------------|--|

| 11                                                                                                                 | х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>         |                                                    |  |

| 1.0                                                                                                                | X      | Awake       | Active   | Waits for BOR ready                        |                                                    |  |

| 10                                                                                                                 |        | Sleep       | Disabled | waits for E                                | BOR ready                                          |  |

| 01                                                                                                                 | 1      | х           | Active   | Begins immediately                         |                                                    |  |

| 01                                                                                                                 | 0      | ~           | Disabled | Begins immediately                         |                                                    |  |

| 00                                                                                                                 | х      | х           | Disabled | Begins immediately                         |                                                    |  |

| Note 1: Even though this case specifically waits for the BOR the BOR is already operating, so there is no delay in |        |             |          |                                            |                                                    |  |

#### TABLE 6-1:BOR OPERATING MODES

**Note 1:** Even though this case specifically waits for the BOR, the BOR is already operating, so there is no delay in start-up.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Word 1 are set to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Word 1 are set to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Word 1 are set to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### EXAMPLE 11-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI: PROG_ADDR_LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSEL

EEADRL

; Select Bank for EEPRO

MOVLW

PROG_ADDR_LO

;

MOVWF

EEADRL

; Store LSB of address

MOVLW

PROG_ADDR_HI

;

BANKSEL EEADRL

; Select Bank for EEPROM registers

MOVWL EEADRH

; Store MSB of address

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

BSF

EECON1,RD

; Initiate read

NOP

; Executed (Figure 11-1)

NOP

; Ignored (Figure 11-1)

BSF

INTCON, GIE

; Restore interrupts

MOVF

EEDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO ; Store in user location

EEDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in user location

MOVE

MOVWF

```

| R/W-0/0         | R/W-0/0                                                                                                                | R/W-0/0                                                            | R/W-0/0                                | U-0                                     | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------|-----------------------------------------|------------------|----------------|--------------|

| ADFM            |                                                                                                                        | ADCS<2:0>                                                          |                                        |                                         | ADNREF           | ADPRE          | F<1:0>       |

| bit 7           | ·                                                                                                                      |                                                                    |                                        |                                         |                  |                | bit (        |

|                 |                                                                                                                        |                                                                    |                                        |                                         |                  |                |              |

| Legend:         |                                                                                                                        |                                                                    |                                        |                                         |                  |                |              |

| R = Readab      | le bit                                                                                                                 | W = Writable                                                       | bit                                    | U = Unimplei                            | mented bit, read | 1 as '0'       |              |

| u = Bit is une  | changed                                                                                                                | x = Bit is unkr                                                    | nown                                   | -n/n = Value                            | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is se | et                                                                                                                     | '0' = Bit is clea                                                  | ared                                   |                                         |                  |                |              |

| bit 7           | 1 = Right ju<br>loaded.                                                                                                | Result Format S<br>stified. Six Most<br>tified. Six Least          | Significant b                          |                                         |                  |                |              |

|                 | loaded.                                                                                                                | lined. OIX Least                                                   | olgrinicarit bi                        | IS OF ADIVEOL                           |                  |                |              |

| bit 6-4         | 000 = Fosc/<br>001 = Fosc/<br>010 = Fosc/<br>011 = Frc (0<br>100 = Fosc/<br>101 = Fosc/<br>110 = Fosc/<br>111 = Frc (0 | 8<br>32<br>clock supplied fr<br>4<br>16<br>64<br>clock supplied fr | om a dedicate<br>om a dedicate         | ed RC oscillator                        |                  |                |              |

| bit 3           | Unimpleme                                                                                                              | nted: Read as '                                                    | 0'                                     |                                         |                  |                |              |

| bit 2           | 0 = VREF-                                                                                                              | /D Negative Vol<br>is connected to '<br>is connected to (          | Vss                                    |                                         | n bit            |                |              |

| bit 1-0         | <b>ADPREF&lt;1</b> :<br>00 = VREF+<br>01 = Reserv                                                                      | :0>: A/D Positive<br>is connected to<br>/ed<br>is connected to     | e Voltage Refe<br>VDD<br>external VREF | erence Configu<br>=+ pin <sup>(1)</sup> |                  | (4)            |              |

## - -

minimum voltage specification exists. See the applicable Electrical Specifications Chapter for details.

#### REGISTER 17-1: DACCON0: VOLTAGE REFERENCE CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0                                   | R/W-0/0              | U-0             | R/W-0/0         | R/W-0/0            | U-0               | R/W-0/0 |

|------------------|-------------------------------------------|----------------------|-----------------|-----------------|--------------------|-------------------|---------|

| DACEN            | DACLPS                                    | DACOE                | _               | DACP            | SS<1:0>            | —                 | DACNSS  |

| bit 7            |                                           |                      |                 |                 |                    |                   | bit 0   |

|                  |                                           |                      |                 |                 |                    |                   |         |

| Legend:          |                                           |                      |                 |                 |                    |                   |         |

| R = Readable     | bit                                       | W = Writable bit     |                 | U = Unimpleme   | ented bit, read as | ʻ0'               |         |

| u = Bit is unch  | anged                                     | x = Bit is unknow    | vn              | -n/n = Value at | POR and BOR/Va     | alue at all other | Resets  |

| '1' = Bit is set |                                           | '0' = Bit is cleare  | ed              |                 |                    |                   |         |

|                  |                                           |                      |                 |                 |                    |                   |         |

| bit 7            | DACEN: DAC Enable bit                     |                      |                 |                 |                    |                   |         |

|                  | 1 = DAC is enabled<br>0 = DAC is disabled |                      |                 |                 |                    |                   |         |

| bit 6            |                                           | C Low-Power Volta    | nao Stato Solo  | ot hit          |                    |                   |         |

| DILO             |                                           | tive reference sou   | 0               |                 |                    |                   |         |

|                  |                                           | ative reference so   |                 |                 |                    |                   |         |

| bit 5            | DACOE: DAC                                | Voltage Output Er    | nable bit       |                 |                    |                   |         |

|                  | 1 = DAC volta                             | age level is also ar | n output on the |                 |                    |                   |         |

|                  | 0 = DAC volta                             | age level is discon  | nected from th  | ne DACOUT pin   |                    |                   |         |

| bit 4            | Unimplement                               | ed: Read as '0'      |                 |                 |                    |                   |         |

| bit 3-2          |                                           | : DAC Positive S     | ource Select b  | oits            |                    |                   |         |

|                  | 00 = VDD                                  | in                   |                 |                 |                    |                   |         |

|                  | 01 = VREF+ pin<br>10 = FVR Buffer2 output |                      |                 |                 |                    |                   |         |

|                  | 11 = Reserved, do not use                 |                      |                 |                 |                    |                   |         |

| bit 1            | Unimplemented: Read as '0'                |                      |                 |                 |                    |                   |         |

| bit 0            | DACNSS: DAG                               | C Negative Source    | e Select bits   |                 |                    |                   |         |

|                  | 1 = VREF-                                 | C C                  |                 |                 |                    |                   |         |

|                  | 0 = Vss                                   |                      |                 |                 |                    |                   |         |

### REGISTER 17-2: DACCON1: VOLTAGE REFERENCE CONTROL REGISTER 1

| U-0                               | U-0 | U-0                | R/W-0/0                            | R/W-0/0                                               | R/W-0/0   | R/W-0/0 | R/W-0/0 |

|-----------------------------------|-----|--------------------|------------------------------------|-------------------------------------------------------|-----------|---------|---------|

| _                                 | _   | _                  |                                    |                                                       | DACR<4:0> |         |         |

| bit 7                             |     |                    |                                    |                                                       |           |         | bit 0   |

|                                   |     |                    |                                    |                                                       |           |         |         |

| Legend:                           |     |                    |                                    |                                                       |           |         |         |

| R = Readable bit W = Writable bit |     |                    | U = Unimplemented bit, read as '0' |                                                       |           |         |         |

| u = Bit is unchan                 | ged | x = Bit is unknown |                                    | -n/n = Value at POR and BOR/Value at all other Resets |           |         | esets   |

| '1' = Bit is set                  |     | '0' = Bit is clear | ed                                 |                                                       |           |         |         |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 DACR<4:0>: DAC Voltage Output Select bits

#### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC MODULE

| Name    | Bit 7 | Bit 6  | Bit 5 | Bit 4     | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Register<br>on page |

|---------|-------|--------|-------|-----------|-------|---------|-------|--------|---------------------|

| FVRCON  | FVREN | FVRRDY | TSEN  | TSRNG     | CDAFV | ′R<1:0> | ADFV  | R<1:0> | 156                 |

| DACCON0 | DACEN | DACLPS | DACOE | _         | DACPS | S<1:0>  | _     | DACNSS | 176                 |

| DACCON1 | _     | _      | _     | DACR<4:0> |       |         | 176   |        |                     |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC Module.

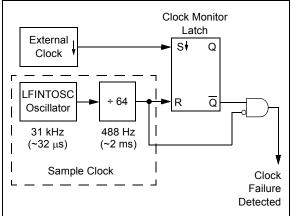

## 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is<br>used to designate Timer2, Timer4, or<br>Timer6. For example, TxCON references<br>T2CON, T4CON, or T6CON. PRx refer- |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                 |

|       | ences PR2, PR4, or PR6.                                                                                                                                         |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSP modules (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

## 24.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus  $(I^2C)$  is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

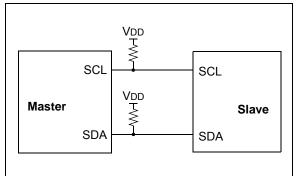

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- Serial Data (SDA)

Figure 24-11 shows the block diagram of the MSSP module when operating in  $I^2C$  Mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 24-11 shows a typical connection between two processors configured as master and slave devices.

The  $I^2C$  bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode

(master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

#### FIGURE 24-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an ACK bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last ACK bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### REGISTER 24-1: SSPSTAT: SSP STATUS REGISTER

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                        | R-0/0                                         | R-0/0                                     | R-0/0                | R-0/0                | R-0/0               | R-0/0         |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------|----------------------|----------------------|---------------------|---------------|--|--|--|

| SMP              | CKE                                                                                                                                                                                                                            | D/A                                           | Р                                         | S                    | R/W                  | UA                  | BF            |  |  |  |

| bit 7            |                                                                                                                                                                                                                                |                                               |                                           |                      | •                    |                     | bit 0         |  |  |  |

|                  |                                                                                                                                                                                                                                |                                               |                                           |                      |                      |                     |               |  |  |  |

| Legend:          |                                                                                                                                                                                                                                |                                               |                                           |                      |                      |                     |               |  |  |  |

| R = Readable b   |                                                                                                                                                                                                                                | W = Writable bi                               |                                           |                      | ented bit, read as   |                     |               |  |  |  |

| u = Bit is uncha | inged                                                                                                                                                                                                                          | x = Bit is unkno                              |                                           | -n/n = Value at      | POR and BOR/V        | alue at all other I | Resets        |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                | '0' = Bit is clear                            | ed                                        |                      |                      |                     |               |  |  |  |

| bit 7            | SMD. SDI Data                                                                                                                                                                                                                  | a Input Sample bi                             | +                                         |                      |                      |                     |               |  |  |  |

|                  | SPI Master mo                                                                                                                                                                                                                  |                                               | l l                                       |                      |                      |                     |               |  |  |  |

|                  | 1 = Input data sampled at end of data output time                                                                                                                                                                              |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | 0 = Input data sampled at middle of data output time                                                                                                                                                                           |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | <u>SPI Slave mode:</u><br>SMP must be cleared when SPI is used in Slave mode                                                                                                                                                   |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | In I <sup>2</sup> C Master or Slave mode:                                                                                                                                                                                      |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | <ul> <li>1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)</li> <li>0 = Slew rate control enabled for high speed mode (400 kHz)</li> </ul>                                                            |                                               |                                           |                      |                      |                     |               |  |  |  |

| bit 6            | CKE: SPI Cloc                                                                                                                                                                                                                  | k Edge Select bit                             | (SPI mode onl                             | y)                   |                      |                     |               |  |  |  |

|                  | CKE: SPI Clock Edge Select bit (SPI mode only) In SPI Master or Slave mode:                                                                                                                                                    |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | <ul> <li>1 = Transmit occurs on transition from active to Idle clock state</li> <li>0 = Transmit occurs on transition from Idle to active clock state</li> </ul>                                                               |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | 0 = 1 ransmit occurs on transition from idle to active clock state<br>In $I^2 C^{TM}$ mode only:                                                                                                                               |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | 1 = Enable input logic so that thresholds are compliant with SMBus specification<br>0 = Disable SMBus specific inputs                                                                                                          |                                               |                                           |                      |                      |                     |               |  |  |  |

| bit 5            | D/A: Data/Add                                                                                                                                                                                                                  | $D/A$ : Data/Address bit ( $l^2$ C mode only) |                                           |                      |                      |                     |               |  |  |  |

|                  | <ul> <li>1 = Indicates that the last byte received or transmitted was data</li> <li>0 = Indicates that the last byte received or transmitted was address</li> </ul>                                                            |                                               |                                           |                      |                      |                     |               |  |  |  |

| bit 4            | <b>P:</b> Stop bit                                                                                                                                                                                                             | lat the last byte i                           |                                           |                      | 1035                 |                     |               |  |  |  |

|                  | •                                                                                                                                                                                                                              | . This bit is clear                           | ed when the MS                            | SSP module is d      | sabled, SSPEN is     | cleared.)           |               |  |  |  |

|                  | (l <sup>2</sup> C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)<br>1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)<br>0 = Stop bit was not detected last |                                               |                                           |                      |                      |                     |               |  |  |  |

| bit 3            | S: Start bit                                                                                                                                                                                                                   |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  |                                                                                                                                                                                                                                |                                               |                                           |                      | sabled, SSPEN is     | cleared.)           |               |  |  |  |

|                  |                                                                                                                                                                                                                                | nat a Start bit has<br>is not detected la     |                                           | last (this bit is '0 | o' on Reset)         |                     |               |  |  |  |

| bit 2            |                                                                                                                                                                                                                                | ite bit information                           |                                           |                      |                      |                     |               |  |  |  |

|                  | This bit holds the to the next Star                                                                                                                                                                                            | rt bit, Stop bit, or                          | atio <u>n foll</u> owing t<br>not ACK bit | he last address r    | natch. This bit is c | nly valid from the  | address match |  |  |  |

|                  | 1 = Read                                                                                                                                                                                                                       | oue.                                          |                                           |                      |                      |                     |               |  |  |  |

|                  | 0 = Write                                                                                                                                                                                                                      |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | In I <sup>2</sup> C Master mode:<br>1 = Transmit is in progress                                                                                                                                                                |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  |                                                                                                                                                                                                                                | s in progress<br>s not in progress            |                                           |                      |                      |                     |               |  |  |  |

|                  |                                                                                                                                                                                                                                |                                               |                                           | CEN or ACKEN         | will indicate if the | MSSP is in Idle n   | node.         |  |  |  |

| bit 1            |                                                                                                                                                                                                                                | ldress bit (10-bit                            |                                           |                      |                      |                     |               |  |  |  |

|                  | <ul> <li>1 = Indicates that the user needs to update the address in the SSPADD register</li> <li>0 = Address does not need to be updated</li> </ul>                                                                            |                                               |                                           |                      |                      |                     |               |  |  |  |

| bit 0            | BF: Buffer Full                                                                                                                                                                                                                |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  |                                                                                                                                                                                                                                | ind I <sup>2</sup> C modes):                  |                                           |                      |                      |                     |               |  |  |  |

|                  |                                                                                                                                                                                                                                | mplete, SSPBUF<br>ot complete, SSP            |                                           |                      |                      |                     |               |  |  |  |

|                  | 0 = Receive not<br><u>Transmit (I<sup>2</sup>C not</u>                                                                                                                                                                         |                                               |                                           |                      |                      |                     |               |  |  |  |

|                  | 1 = Data transr                                                                                                                                                                                                                | mit in progress (d                            |                                           |                      | op bits), SSPBUF     |                     |               |  |  |  |

|                  | 0 = Data transr                                                                                                                                                                                                                | mit complete (doe                             | es not include th                         | ne ACK and Stop      | bits), SSPBUF is     | empty               |               |  |  |  |

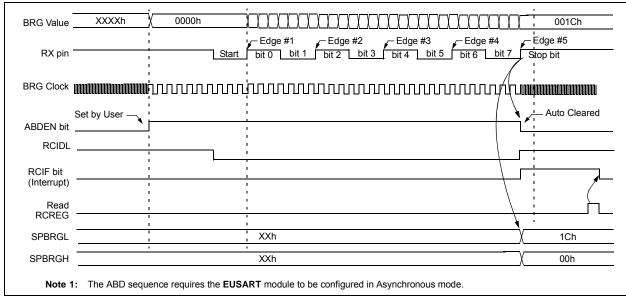

#### 25.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 25-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 25-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 25-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 25.3.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| TABLE 25-6: | BRG COUNTER CLOCK RATES |

|-------------|-------------------------|

|-------------|-------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |  |  |

|-------|------|-------------------|------------------|--|--|

| 0     | 0    | Fosc/64           | Fosc/512         |  |  |

| 0     | 1    | Fosc/16           | Fosc/128         |  |  |

| 1     | 0    | Fosc/16           | Fosc/128         |  |  |

| 1     | 1    | Fosc/4            | Fosc/32          |  |  |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

#### FIGURE 25-6: AUTOMATIC BAUD RATE CALIBRATION

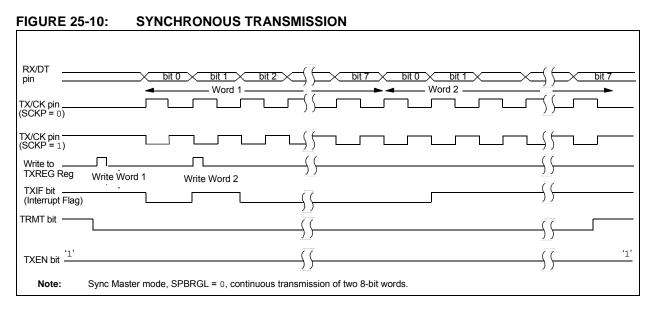

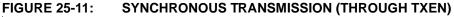

## TABLE 25-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | -      | WUE    | ABDEN  | 302                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 99                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 102                 |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 301                 |

| SPBRGL  | BRG<7:0>                      |        |        |        |        |        |        | 303*   |                     |

| SPBRGH  | BRG<15:8>                     |        |        |        |        |        | 303*   |        |                     |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 142                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        | 293*   |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 300                 |

Legend: — = unimplemented read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

## 29.0 INSTRUCTION SET SUMMARY

Each PIC16 instruction is a 14-bit word containing the operation code (opcode) and all required operands. The opcodes are broken into three broad categories.

- Byte Oriented

- · Bit Oriented

- Literal and Control

The literal and control category contains the most varied instruction word format.

Table 29-3 lists the instructions recognized by the MPASM  $^{\rm TM}$  assembler.

All instructions are executed within a single instruction cycle, with the following exceptions, which may take two or three cycles:

- Subroutine takes two cycles (CALL, CALLW)

- Returns from interrupts or subroutines take two cycles (RETURN, RETLW, RETFIE)

- Program branching takes two cycles (GOTO, BRA, BRW, BTFSS, BTFSC, DECFSZ, INCSFZ)

- One additional instruction cycle will be used when any instruction references an indirect file register and the file select register is pointing to program memory.

One instruction cycle consists of 4 oscillator cycles; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution rate of 1 MHz.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 29.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

#### TABLE 29-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                          |