Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1936-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

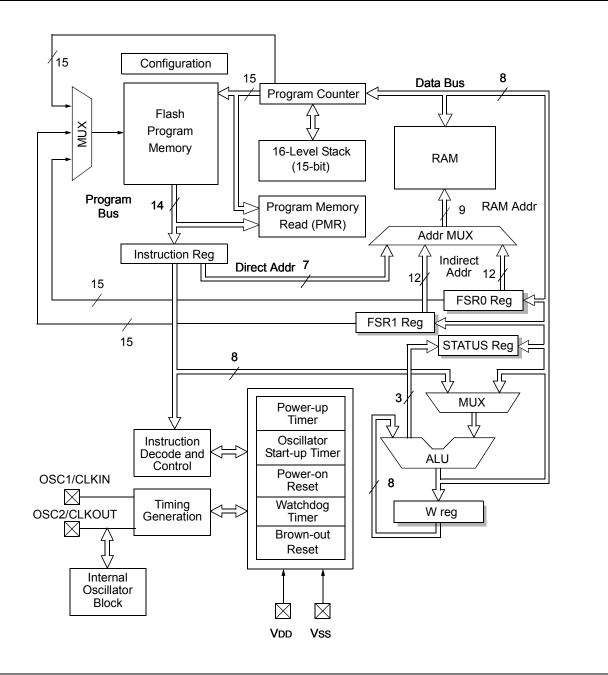

The PIC16(L)F1934/6/7 are described within this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1934/6/7 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral              |             | PIC16F193X | PIC16LF193X |

|-------------------------|-------------|------------|-------------|

| ADC                     |             | •          | •           |

| Capacitive Sensing Mod  | dule        | •          | •           |

| Digital-to-Analog Conve | erter (DAC) | ٠          | •           |

| EUSART                  |             | ٠          | •           |

| Fixed Voltage Reference | e (FVR)     | •          | •           |

| LCD                     |             | ٠          | •           |

| SR Latch                |             | •          | •           |

| Temperature Indicator   |             | •          | •           |

| Capture/Compare/PWM     |             |            |             |

|                         | ECCP1       | ٠          | •           |

|                         | ECCP2       | •          | •           |

|                         | ECCP3       | ٠          | •           |

|                         | CCP4        | ٠          | •           |

|                         | CCP5        | •          | •           |

| Comparators             |             |            |             |

|                         | C1          | ٠          | •           |

|                         | C2          | •          | •           |

| Operational Amplifiers  |             |            |             |

|                         | OPA1        | •          | •           |

|                         | OPA2        | •          | •           |

| Master Synchronous Se   | erial Ports |            |             |

|                         | MSSP1       | •          | •           |

| Timers                  |             |            |             |

|                         | Timer0      | ٠          | •           |

|                         | Timer1      | •          | •           |

|                         | Timer2      | ٠          | •           |

|                         | Timer4      | ٠          | •           |

|                         | Timer6      | •          | •           |

# PIC16(L)F1934/6/7

## 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |             |         |      |

|-----------|-------------|---------|------|

| RETLW     | DATA0       | ;Index0 | data |

| RETLW     | DATA1       | ;Index1 | data |

| RETLW     | DATA2       |         |      |

| RETLW     | DATA3       |         |      |

| my_functi | on          |         |      |

| ; LO      | IS OF CODE. |         |      |

| MOVLW     | LOW cons    | tants   |      |

| MOVWF     | FSR1L       |         |      |

| MOVLW     | HIGH con    | stants  |      |

| MOVWF     | FSR1H       |         |      |

| MOVIW     | 0[FSR1]     |         |      |

| ;THE PROG | RAM MEMORY  | IS IN W |      |

|           |             |         |      |

## 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

## 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation of the PIC16(L)F1934/6/7. These registers are listed below:

- INDF0

- INDF1

- PCL

- STATUS

- FSR0 Low

- FSR0 High

- FSR1 Low

- FSR1 High

- BSR

- WREG

- PCLATH

- INTCON

Note: The core registers are the first 12 addresses of every data memory bank.

# 4.0 DEVICE CONFIGURATION

Device Configuration consists of Configuration Word 1 and Configuration Word 2, Code Protection and Device ID.

## 4.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 at 8007h and Configuration Word 2 at 8008h.

| Note: | The DEBUG bit in Configuration Word 2 is    |

|-------|---------------------------------------------|

|       | managed automatically by device             |

|       | development tools including debuggers       |

|       | and programmers. For normal device          |

|       | operation, this bit should be maintained as |

|       | a '1'.                                      |

## 5.2.1.5 TIMER1 Oscillator

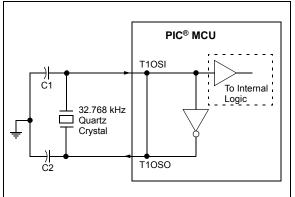

The Timer1 Oscillator is a separate crystal oscillator that is associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 Oscillator can be used as an alternate system clock source and can be selected during run-time using clock switching. Refer to **Section 5.3 "Clock Switching"** for more information.

### FIGURE 5-5: QUARTZ CRYSTAL OPERATION (TIMER1 OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

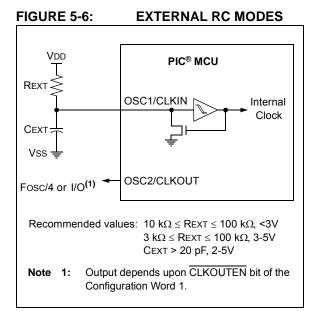

## 5.2.1.6 External RC Mode

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required.

The RC circuit connects to OSC1. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. The function of the OSC2/CLKOUT pin is determined by the state of the CLKOUTEN bit in Configuration Word 1.

Figure 5-6 shows the external RC mode connections.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- · packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

# PIC16(L)F1934/6/7

NOTES:

| U-0              | U-0   | R/W-1/1            | R/W-1/1 | R/W-1/1                                             | R/W-1/1 | R/W-1/1 | R/W-1/1      |  |

|------------------|-------|--------------------|---------|-----------------------------------------------------|---------|---------|--------------|--|

| —                | —     | ANSB5              | ANSB4   | ANSB3                                               | ANSB2   | ANSB1   | ANSB0        |  |

| bit 7            |       |                    |         |                                                     |         |         | bit 0        |  |

|                  |       |                    |         |                                                     |         |         |              |  |

| Legend:          |       |                    |         |                                                     |         |         |              |  |

| R = Readable I   | bit   | W = Writable       | bit     | U = Unimplemented bit, read as '0'                  |         |         |              |  |

| u = Bit is uncha | anged | x = Bit is unknown |         | -n/n = Value at POR and BOR/Value at all other Rese |         |         | other Resets |  |

| '1' = Bit is set |       | '0' = Bit is clea  | ared    |                                                     |         |         |              |  |

## REGISTER 12-9: ANSELB: PORTB ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSB<5:0>**: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## REGISTER 12-10: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

## 14.3 FVR Control Registers

## REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 R-q/q                          | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0/0        | R/W-0/0                     | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|------------------|------------------|--------------|--|

| FVREN FVRRDY <sup>(1)</sup>            | TSEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TSRNG          | CDAF                        | /R<1:0>          | ADFVI            | R<1:0>       |  |

| bit 7                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | ·                           |                  |                  | bit (        |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                             |                  |                  |              |  |

| Legend:                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                             |                  |                  |              |  |

| R = Readable bit                       | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit            | U = Unimplen                | nented bit, read | as '0'           |              |  |

| u = Bit is unchanged                   | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nown           | -n/n = Value a              | at POR and BOI   | R/Value at all c | other Resets |  |

| 1' = Bit is set                        | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ared           | q = Value dep               | ends on condit   | on               |              |  |

| 0 = Fixed V                            | ed Voltage Refe<br>oltage Referenc<br>oltage Referenc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e is disabled  | bit                         |                  |                  |              |  |

| 0 = Fixed V                            | ixed Voltage Ref<br>oltage Referenc<br>oltage Referenc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e output is no | t ready or not e            | nabled           |                  |              |  |

| 0 = Temper                             | perature Indicato<br>ature Indicator is<br>ature Indicator is                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | s disabled     | i)                          |                  |                  |              |  |

| 0 = VOUT =                             | mperature Indica<br>VDD - 2VT (Low<br>VDD - 4VT (High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Range)         | election bit <sup>(3)</sup> |                  |                  |              |  |

| 00 = Compa<br>01 = Compa<br>10 = Compa | <ul> <li>1 = VOUT = VDD - 4VT (High Range)</li> <li>CDAFVR&lt;1:0&gt;: Comparator and DAC Fixed Voltage Reference Selection bit</li> <li>00 = Comparator and DAC Fixed Voltage Reference Peripheral output is off.</li> <li>01 = Comparator and DAC Fixed Voltage Reference Peripheral output is 1x (1.024V)</li> <li>10 = Comparator and DAC Fixed Voltage Reference Peripheral output is 2x (2.048V)<sup>(2)</sup></li> <li>11 = Comparator and DAC Fixed Voltage Reference Peripheral output is 4x (4.096V)<sup>(2)</sup></li> </ul> |                |                             |                  |                  |              |  |

| 00 = ADC F<br>01 = ADC F<br>10 = ADC F | ADFVR<1:0>: ADC Fixed Voltage Reference Selection bit<br>00 = ADC Fixed Voltage Reference Peripheral output is off.<br>01 = ADC Fixed Voltage Reference Peripheral output is 1x (1.024V)<br>10 = ADC Fixed Voltage Reference Peripheral output is 2x (2.048V) <sup>(2)</sup><br>11 = ADC Fixed Voltage Reference Peripheral output is 4x (4.096V) <sup>(2)</sup>                                                                                                                                                                        |                |                             |                  |                  |              |  |

|                                        | VRRDY is always '1' on devices with LDO (PIC16F1934/6/7).<br>Fixed Voltage Reference output cannot exceed VDD.                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                             |                  |                  |              |  |

3: See Section 16.0 "Temperature Indicator Module" for additional information.

### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0> | ADFV  | R<1:0> | 156                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

## REGISTER 15-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| —                | —       | —                 | _       | —                                                     | _       | ADRE    | S<9:8>  |  |

| bit 7            |         |                   |         |                                                       |         |         | bit 0   |  |

|                  |         |                   |         |                                                       |         |         |         |  |

| Legend:          |         |                   |         |                                                       |         |         |         |  |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

## **REGISTER 15-6:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u     | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------------|------------|---------|---------|---------|---------|---------|---------|--|

|             | ADRES<7:0> |         |         |         |         |         |         |  |

| bit 7 bit 0 |            |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4:TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                       |

|-------|--------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                          |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                  |

| 10    | Comparator 1 Output SYNCC1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output SYNCC2OUT<br>(optionally Timer1 synchronized output) |

## 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

## 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (SYNCC1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 18.4.1 "Comparator Output Synchronization**".

## 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (SYNCC2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 18.4.1 "Comparator Output Synchronization"**.

## 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |

|-------|---------------------------------------------|

|       | as changing the gate polarity may result in |

|       | indeterminate operation.                    |

### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

## 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

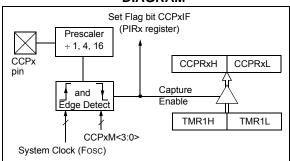

## 23.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 23-1 shows a simplified diagram of the Capture operation.

## 23.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON register. Refer to **Section 12.1 "Alternate Pin Function"** for more details.

Note: If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 23-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

## 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

## 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

## 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 23-1 demonstrates the code to perform this function.

## EXAMPLE 23-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ;Set Bank bits to point |

|-------------------------|

| ;to CCPxCON             |

| ;Turn CCP module off    |

| ;Load the W reg with    |

| ;the new prescaler      |

| ;move value and CCP ON  |

| ;Load CCPxCON with this |

| ;value                  |

|                         |

## 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

## 23.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

### 23.2.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function"** for more information.

| Name                 | Bit 7                                         | Bit 6                                      | Bit 5        | Bit 4         | Bit 3            | Bit 2                          | Bit 1                 | Bit 0                 | Register<br>on Page |  |

|----------------------|-----------------------------------------------|--------------------------------------------|--------------|---------------|------------------|--------------------------------|-----------------------|-----------------------|---------------------|--|

| APFCON               | _                                             | CCP3SEL                                    | T1GSEL       | P2BSEL        | SRNQSEL          | C2OUTSEL                       | SSSEL                 | CCP2SEL               | 131                 |  |

| CCPxCON              | PxM<                                          | 1:0> <b>(1)</b>                            | DCxB         | <1:0>         |                  | 234                            |                       |                       |                     |  |

| CCPRxL               | Capture/Compare/PWM Register x Low Byte (LSB) |                                            |              |               |                  |                                | 212                   |                       |                     |  |

| CCPRxH               | Capture/Co                                    | mpare/PWM                                  | Register x I | High Byte (M  | ISB)             |                                |                       |                       | 212                 |  |

| INTCON               | GIE                                           | PEIE                                       | TMR0IE       | INTE          | IOCIE            | IOCIF                          | 98                    |                       |                     |  |

| PIE1                 | TMR1GIE                                       | ADIE                                       | RCIE         | TXIE          | SSPIE            | CCP1IE                         | TMR2IE                | TMR1IE                | 99                  |  |

| PIE2                 | OSFIE                                         | C2IE                                       | C1IE         | EEIE          | BCLIE            | LCDIE                          | —                     | CCP2IE                | 100                 |  |

| PIE3                 | —                                             | CCP5IE                                     | CCP4IE       | CCP3IE        | TMR6IE           | _                              | TMR4IE                | _                     | 101                 |  |

| PIR1                 | TMR1GIF                                       | ADIF                                       | RCIF         | TXIF          | SSPIF            | CCP1IF                         | TMR2IF                | TMR1IF                | 102                 |  |

| PIR2                 | OSFIF                                         | C2IF                                       | C1IF         | EEIF          | BCLIF            | LCDIF                          | —                     | CCP2IF                | 103                 |  |

| PIR3                 | —                                             | CCP5IF                                     | CCP4IF       | CCP3IF        | TMR6IF           | _                              | TMR4IF                | —                     | 104                 |  |

| T1CON                | TMR1C                                         | TMR1CS<1:0>T1CKPS<1:0>T1OSCENT1SYNC—TMR1ON |              |               |                  |                                |                       | 203                   |                     |  |

| T1GCON               | TMR1GE                                        | T1GPOL                                     | T1GTM        | T1GSPM        | T1GGO/DONE       | 1GGO/DONE T1GVAL T1GSS<1:0> 20 |                       |                       |                     |  |

| TMR1L                | Holding Reg                                   | gister for the                             | Least Signif | icant Byte of | f the 16-bit TMR | 1 Register                     |                       |                       | 199                 |  |

| TMR1H                | Holding Reg                                   | gister for the                             | Most Signifi | cant Byte of  | the 16-bit TMR1  | Register                       |                       |                       | 199                 |  |

| TRISA                | TRISA7                                        | TRISA6                                     | TRISA5       | TRISA4        | TRISA3           | TRISA2                         | TRISA1                | TRISA0                | 133                 |  |

| TRISB                | TRISB7                                        | TRISB6                                     | TRISB5       | TRISB4        | TRISB3           | TRISB2                         | TRISB1                | TRISB0                | 138                 |  |

| TRISC                | TRISC7                                        | TRISC6                                     | TRISC5       | TRISC4        | TRISC3           | TRISC2                         | TRISC1                | TRISC0                | 142                 |  |

| TRISD <sup>(2)</sup> | TRISD7                                        | TRISD6                                     | TRISD5       | TRISD4        | TRISD3           | TRISD2                         | TRISD1                | TRISD0                | 145                 |  |

| TRISE                | _                                             | —                                          | _            | _             | _(3)             | TRISE2 <sup>(2)</sup>          | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 148                 |  |

## TABLE 23-4: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Compare mode.

**Note 1:** Applies to ECCP modules only.

2: These bits are not implemented on PIC16(L)F1936 devices, read as '0'.

**3:** Unimplemented, read as '1'.

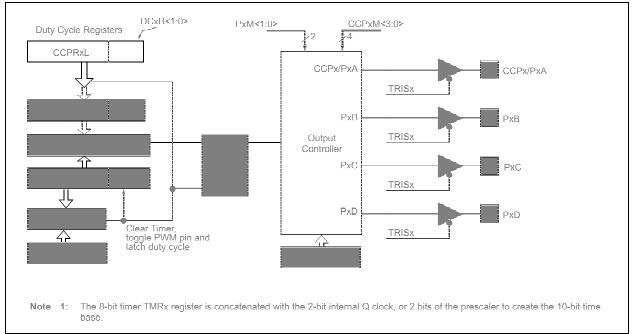

## 23.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1, ECCP2 and ECCP3, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- · CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- · CCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward Mode

- Full-Bridge PWM, Reverse Mode

- · Single PWM with PWM Steering Mode

To select an Enhanced PWM Output mode, the PxM bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 23-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Table 23-9 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

## FIGURE 23-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

# PIC16(L)F1934/6/7

© 2008-2011 Microchip Technology Inc.

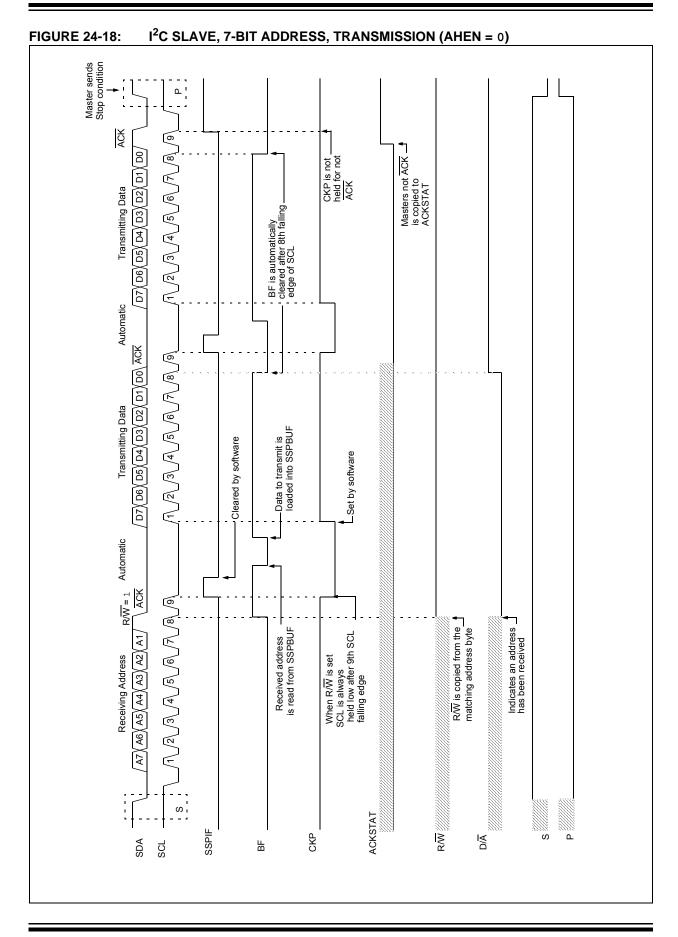

## 24.6.7 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN bit of the SSPCON2 register.

| Note: | The MSSP module must be in an Idle      |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable, ACKEN bit of the SSPCON2 register.

## 24.6.7.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

## 24.6.7.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

## 24.6.7.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

#### 24.6.7.4 Typical Receive Sequence:

- 1. The user generates a Start condition by setting the SEN bit of the SSPCON2 register.

- 2. SSPIF is set by hardware on completion of the Start.

- 3. SSPIF is cleared by software.

- 4. User writes SSPBUF with the slave address to transmit and the R/W bit set.

- 5. Address is shifted out the SDA pin until all 8 bits are transmitted. Transmission begins as soon as SSPBUF is written to.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the ACKSTAT bit of the SSPCON2 register.

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 8. User sets the RCEN bit of the SSPCON2 register and the Master clocks in a byte from the slave.

- 9. After the 8th falling edge of SCL, SSPIF and BF are set.

- 10. Master clears SSPIF and reads the received byte from SSPBUF, clears BF.

- 11. Master sets ACK value sent to slave in ACKDT bit of the SSPCON2 register and initiates the ACK by setting the ACKEN bit.

- 12. Masters ACK is clocked out to the Slave and SSPIF is set.

- 13. User clears SSPIF.

- 14. Steps 8-13 are repeated for each received byte from the slave.

- 15. Master sends a not ACK or Stop to end communication.

## 25.3.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPBRGH:SPBRGL register pair. After the ABDOVF has been set, the counter continues to count until the fifth rising edge is detected on the RX pin. Upon detecting the fifth RX edge, the hardware will set the RCIF interrupt flag and clear the ABDEN bit of the BAUDCON register. The RCIF flag can be subsequently cleared by reading the RCREG register. The ABDOVF flag of the BAUDCON register can be cleared by software directly.

To terminate the auto-baud process before the RCIF flag is set, clear the ABDEN bit then clear the ABDOVF bit of the BAUDCON register. The ABDOVF bit will remain set if the ABDEN bit is not cleared first.

## 25.3.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RX/DT line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDCON register. Once set, the normal receive sequence on RX/DT is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 25-7), and asynchronously if the device is in Sleep mode (Figure 25-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RX line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

#### 25.3.3.1 Special Considerations

Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Start-up Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

#### <u>WUE Bit</u>

The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared in hardware by a rising edge on RX/DT. The interrupt condition is then cleared in software by reading the RCREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

# 25.5 EUSART Operation During Sleep

The EUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore cannot generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 25.5.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (see Section 25.4.2.4 "Synchronous Slave Reception Set-up:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set. Thereby, waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 004h will be called.

## 25.5.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (see Section 25.4.2.2 "Synchronous Slave Transmission Set-up:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- Interrupt enable bits TXIE of the PIE1 register and PEIE of the INTCON register must set.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set. Thereby, waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

| LCD      | COM                 | D              | COM                 | 1              | СОМ                 | 2              | COM3                |                |

|----------|---------------------|----------------|---------------------|----------------|---------------------|----------------|---------------------|----------------|

| Function | LCDDATAx<br>Address | LCD<br>Segment | LCDDATAx<br>Address | LCD<br>Segment | LCDDATAx<br>Address | LCD<br>Segment | LCDDATAx<br>Address | LCD<br>Segment |

| SEG0     | LCDDATA0, 0         |                | LCDDATA3, 0         |                | LCDDATA6, 0         |                | LCDDATA9, 0         |                |

| SEG1     | LCDDATA0, 1         |                | LCDDATA3, 1         |                | LCDDATA6, 1         |                | LCDDATA9, 1         |                |

| SEG2     | LCDDATA0, 2         |                | LCDDATA3, 2         |                | LCDDATA6, 2         |                | LCDDATA9, 2         |                |

| SEG3     | LCDDATA0, 3         |                | LCDDATA3, 3         |                | LCDDATA6, 3         |                | LCDDATA9, 3         |                |

| SEG4     | LCDDATA0, 4         |                | LCDDATA3, 4         |                | LCDDATA6, 4         |                | LCDDATA9, 4         |                |

| SEG5     | LCDDATA0, 5         |                | LCDDATA3, 5         |                | LCDDATA6, 5         |                | LCDDATA9, 5         |                |

| SEG6     | LCDDATA0, 6         |                | LCDDATA3, 6         |                | LCDDATA6, 6         |                | LCDDATA9, 6         |                |

| SEG7     | LCDDATA0, 7         |                | LCDDATA3, 7         |                | LCDDATA6, 7         |                | LCDDATA9, 7         |                |

| SEG8     | LCDDATA1, 0         |                | LCDDATA4, 0         |                | LCDDATA7, 0         |                | LCDDATA10, 0        |                |

| SEG9     | LCDDATA1, 1         |                | LCDDATA4, 1         |                | LCDDATA7, 1         |                | LCDDATA10, 1        |                |

| SEG10    | LCDDATA1, 2         |                | LCDDATA4, 2         |                | LCDDATA7, 2         |                | LCDDATA10, 2        |                |

| SEG11    | LCDDATA1, 3         |                | LCDDATA4, 3         |                | LCDDATA7, 3         |                | LCDDATA10, 3        |                |

| SEG12    | LCDDATA1, 4         |                | LCDDATA4, 4         |                | LCDDATA7, 4         |                | LCDDATA10, 4        |                |

| SEG13    | LCDDATA1, 5         |                | LCDDATA4, 5         |                | LCDDATA7, 5         |                | LCDDATA10, 5        |                |

| SEG14    | LCDDATA1, 6         |                | LCDDATA4, 6         |                | LCDDATA7, 6         |                | LCDDATA10, 6        |                |

| SEG15    | LCDDATA1, 7         |                | LCDDATA4, 7         |                | LCDDATA7, 7         |                | LCDDATA10, 7        |                |

| SEG16    | LCDDATA2, 0         |                | LCDDATA5, 0         |                | LCDDATA8, 0         |                | LCDDATA11, 0        |                |

| SEG17    | LCDDATA2, 1         |                | LCDDATA5, 1         |                | LCDDATA8, 1         |                | LCDDATA11, 1        |                |

| SEG18    | LCDDATA2, 2         |                | LCDDATA5, 2         |                | LCDDATA8, 2         |                | LCDDATA11, 2        |                |

| SEG19    | LCDDATA2, 3         |                | LCDDATA5, 3         |                | LCDDATA8, 3         |                | LCDDATA11, 3        |                |

| SEG20    | LCDDATA2, 4         |                | LCDDATA5, 4         |                | LCDDATA8, 4         |                | LCDDATA11, 4        |                |

| SEG21    | LCDDATA2, 5         |                | LCDDATA5, 5         |                | LCDDATA8, 5         |                | LCDDATA11, 5        |                |

| SEG22    | LCDDATA2, 6         |                | LCDDATA5, 6         |                | LCDDATA8, 6         |                | LCDDATA11, 6        |                |

| SEG23    | LCDDATA2, 7         |                | LCDDATA5, 7         |                | LCDDATA8, 7         |                | LCDDATA11, 7        |                |

| TABLE 27-7: LCD SEGMENT MAPPING WORKSHEET |

|-------------------------------------------|

|-------------------------------------------|

# 32.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 32.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.