Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1936t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                    | Function | Input<br>Type    | Output<br>Type | Description                                                                                        |  |  |

|-----------------------------------------------------------------------------------------|----------|------------------|----------------|----------------------------------------------------------------------------------------------------|--|--|

| RB4/AN11/CPS4/P1D/COM0                                                                  | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |

|                                                                                         | AN11     | AN               | —              | A/D Channel 11 input.                                                                              |  |  |

|                                                                                         | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                        |  |  |

|                                                                                         | P1D      | _                | CMOS           | PWM output.                                                                                        |  |  |

|                                                                                         | COM0     | _                | AN             | LCD Analog output.                                                                                 |  |  |

| RB5/AN13/CPS5/P2B/CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> /T1G <sup>(1)</sup> /COM1 | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |

|                                                                                         | AN13     | AN               |                | A/D Channel 13 input.                                                                              |  |  |

|                                                                                         | CPS5     | AN               |                | Capacitive sensing input 5.                                                                        |  |  |

|                                                                                         | P2B      | _                | CMOS           | PWM output.                                                                                        |  |  |

|                                                                                         | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.                                                                              |  |  |

|                                                                                         | P3A      | _                | CMOS           | PWM output.                                                                                        |  |  |

|                                                                                         | T1G      | ST               |                | Timer1 Gate input.                                                                                 |  |  |

|                                                                                         | COM1     | _                | AN             | LCD Analog output.                                                                                 |  |  |

| RB6/ICSPCLK/ICDCLK/SEG14                                                                | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |

|                                                                                         | ICSPCLK  | ST               |                | Serial Programming Clock.                                                                          |  |  |

|                                                                                         | ICDCLK   | ST               |                | In-Circuit Debug Clock.                                                                            |  |  |

|                                                                                         | SEG14    | _                | AN             | LCD Analog output.                                                                                 |  |  |

| RB7/ICSPDAT/ICDDAT/SEG13                                                                | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |  |  |

|                                                                                         | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                    |  |  |

|                                                                                         | ICDDAT   | ST               | CMOS           | In-Circuit Data I/O.                                                                               |  |  |

|                                                                                         | SEG13    |                  | AN             | LCD Analog output.                                                                                 |  |  |

| RC0/T1OSO/T1CKI/P2B <sup>(1)</sup>                                                      | RC0      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |

|                                                                                         | T10S0    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                      |  |  |

|                                                                                         | T1CKI    | ST               |                | Timer1 clock input.                                                                                |  |  |

|                                                                                         | P2B      | _                | CMOS           | PWM output.                                                                                        |  |  |

| RC1/T1OSI/CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup>                                       | RC1      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |

|                                                                                         | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                      |  |  |

|                                                                                         | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                              |  |  |

|                                                                                         | P2A      | _                | CMOS           | PWM output.                                                                                        |  |  |

| RC2/CCP1/P1A/SEG3                                                                       | RC2      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |

|                                                                                         | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                              |  |  |

|                                                                                         | P1A      | _                | CMOS           | PWM output.                                                                                        |  |  |

|                                                                                         | SEG3     | _                | AN             | LCD Analog output.                                                                                 |  |  |

| RC3/SCK/SCL/SEG6                                                                        | RC3      | ST               | CMOS           | General purpose I/O.                                                                               |  |  |

|                                                                                         | SCK      | ST               | CMOS           | SPI clock.                                                                                         |  |  |

|                                                                                         | SCL      | I <sup>2</sup> C | OD             | I <sup>2</sup> C™ clock.                                                                           |  |  |

|                                                                                         | SEG6     | _                | AN             | LCD Analog output.                                                                                 |  |  |

#### TABLE 1-2: PIC16(L)F1934/6/7 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage XTAL = Crystal levels

Note 1: Pin function is selectable via the APFCON register.

- 2: PIC16F1934/6/7 devices only.

- **3:** PIC16(L)F1936 devices only.

- 4: PORTD is available on PIC16(L)F1934/7 devices only.

- 5: RE<2:0> are available on PIC16(L)F1934/7 devices only.

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_INI    | DEX                 |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

|                   |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

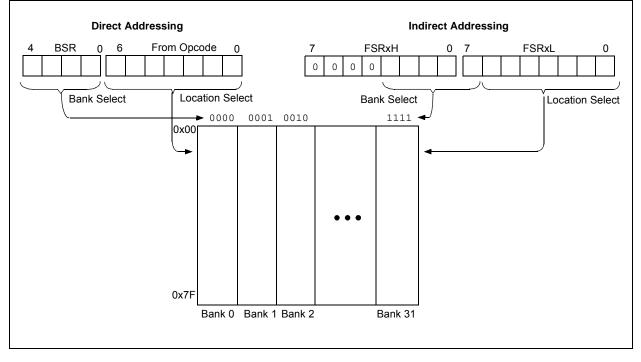

### 3.5.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

## 4.2 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.2.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Word 1. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.3** "Write **Protection**" for more information.

## 4.2.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

## 4.3 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Word 2 define the size of the program memory block that is protected.

## 4.4 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 4.5 "Device ID and Revision ID"** for more information on accessing these memory locations. For more information on checksum calculation, see the *"PIC16F193X/LF193X/PIC16F194X/LF194X/PIC16LF 190X Memory Programming Specification"* (DS41397).

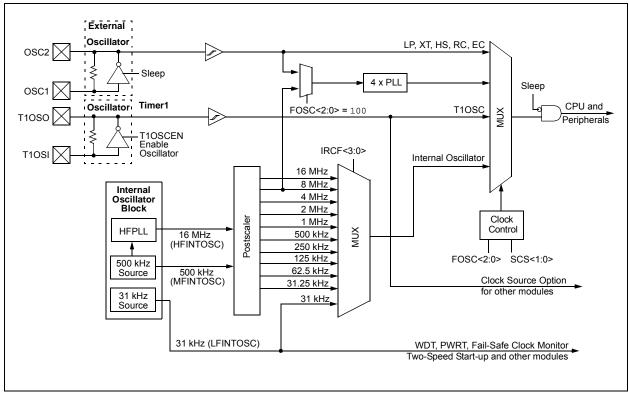

### FIGURE 5-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

| Name    | Bit 7  | Bit 6   | Bit 5       | Bit 4  | Bit 3   | Bit 2    | Bit 1  | Bit 0   | Register<br>on Page |

|---------|--------|---------|-------------|--------|---------|----------|--------|---------|---------------------|

| APFCON  | _      | CCP3SEL | T1GSEL      | P2BSEL | SRNQSEL | C2OUTSEL | SSSEL  | CCP2SEL | 131                 |

| CCPxCON | PxM    | <1:0>   | DCxB<1:0>   |        |         | CCPxN    | /<3:0> |         | 234                 |

| LATC    | LATC7  | LATC6   | LATC5       | LATC4  | LATC3   | LATC2    | LATC1  | LATC0   | 142                 |

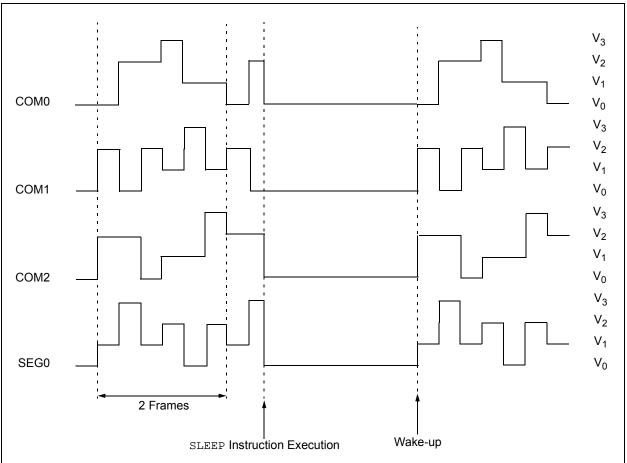

| LCDCON  | LCDEN  | SLPEN   | WERR        | —      | CS<     | :1:0>    | LMUX   | <1:0>   | 329                 |

| LCDSE0  | SE7    | SE6     | SE5         | SE4    | SE3     | SE2      | SE1    | SE0     | 333                 |

| LCDSE1  | SE15   | SE14    | SE13        | SE12   | SE11    | SE10     | SE9    | SE8     | 333                 |

| PORTC   | RC7    | RC6     | RC5         | RC4    | RC3     | RC2      | RC1    | RC0     | 142                 |

| RCSTA   | SPEN   | RX9     | SREN        | CREN   | ADDEN   | FERR     | OERR   | RX9D    | 301                 |

| SSPCON1 | WCOL   | SSPOV   | SSPEN       | CKP    |         | SSPM     | <3:0>  |         | 287                 |

| SSPSTAT | SMP    | CKE     | D/A         | Р      | S       | R/W      | UA     | BF      | 286                 |

| T1CON   | TMR1C  | S<1:0>  | T1CKPS<1:0> |        | T1OSCEN | T1SYNC   | _      | TMR10N  | 203                 |

| TXSTA   | CSRC   | TX9     | TXEN        | SYNC   | —       | BRGH     | TRMT   | TX9D    | 300                 |

| TRISC   | TRISC7 | TRISC6  | TRISC5      | TRISC4 | TRISC3  | TRISC2   | TRISC1 | TRISC0  | 142                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

NOTES:

| R/W-0/0          | R/W-0/0       | R/W-0/0                                                                                                       | R/W-0/0                                                                | R/W-0/0                | R/W-0/0                 | R/W-0/0 | R/W-0/0 |  |  |  |

|------------------|---------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------|-------------------------|---------|---------|--|--|--|

| SRSPE            | SRSCKE        | SRSC2E                                                                                                        | SRSC1E                                                                 | SRRPE                  | SRRCKE                  | SRRC2E  | SRRC1E  |  |  |  |

| bit 7            |               |                                                                                                               |                                                                        |                        |                         |         | bit 0   |  |  |  |

|                  |               |                                                                                                               |                                                                        |                        |                         |         |         |  |  |  |

| Legend:          |               |                                                                                                               |                                                                        |                        |                         |         |         |  |  |  |

| R = Readable     | bit           | W = Writable                                                                                                  | bit                                                                    |                        | nented bit, read        |         |         |  |  |  |

| u = Bit is unch  | anged         |                                                                                                               | r = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese |                        |                         |         |         |  |  |  |

| '1' = Bit is set |               | '0' = Bit is cle                                                                                              | ared                                                                   |                        |                         |         |         |  |  |  |

| 1. 1. 7          |               |                                                                                                               |                                                                        |                        |                         |         |         |  |  |  |

| bit 7            |               | •                                                                                                             | al Set Enable b                                                        |                        |                         |         |         |  |  |  |

|                  |               |                                                                                                               | ne SRI pin is hi<br>n the set input                                    | gn.<br>of the SR Latcł | า                       |         |         |  |  |  |

| bit 6            | SRSCKE: SF    | R Latch Set Clo                                                                                               | ock Enable bit                                                         |                        |                         |         |         |  |  |  |

|                  |               |                                                                                                               | s pulsed with S                                                        |                        |                         |         |         |  |  |  |

|                  | 0 = SRCLK h   | has no effect o                                                                                               | n the set input                                                        | of the SR Latcl        | า                       |         |         |  |  |  |

| bit 5            |               | Latch C2 Set Enable bit                                                                                       |                                                                        |                        |                         |         |         |  |  |  |

|                  |               | is set when the C2 Comparator output is high<br>parator output has no effect on the set input of the SR Latch |                                                                        |                        |                         |         |         |  |  |  |

| bit 4            | •             | R Latch C1 Set                                                                                                |                                                                        | in the set input       | of the SK Lato          | 1       |         |  |  |  |

| DIL 4            |               |                                                                                                               |                                                                        | ator output is hi      | ab                      |         |         |  |  |  |

|                  |               |                                                                                                               |                                                                        |                        | of the SR Latch         | า       |         |  |  |  |

| bit 3            | •             |                                                                                                               | al Reset Enabl                                                         | •                      |                         |         |         |  |  |  |

|                  |               | •                                                                                                             | the SRI pin is                                                         |                        |                         |         |         |  |  |  |

|                  | 0 = SRI pin h | nas no effect or                                                                                              | n the reset inpu                                                       | ut of the SR Lat       | tch                     |         |         |  |  |  |

| bit 2            | SRRCKE: SF    | R Latch Reset                                                                                                 | Clock Enable b                                                         | oit                    |                         |         |         |  |  |  |

|                  |               |                                                                                                               | n is pulsed with                                                       |                        |                         |         |         |  |  |  |

|                  |               |                                                                                                               | •                                                                      | ut of the SR La        | tch                     |         |         |  |  |  |

| bit 1            |               | R Latch C2 Res                                                                                                |                                                                        |                        |                         |         |         |  |  |  |

|                  |               |                                                                                                               |                                                                        | arator output is       | high<br>ut of the SR La | tch     |         |  |  |  |

| bit 0            | •             | R Latch C1 Res                                                                                                |                                                                        |                        |                         |         |         |  |  |  |

| Dit U            |               |                                                                                                               |                                                                        | arator output is       | hiah                    |         |         |  |  |  |

|                  |               |                                                                                                               |                                                                        |                        | ut of the SR La         | tch     |         |  |  |  |

|                  |               | -                                                                                                             |                                                                        |                        |                         |         |         |  |  |  |

### REGISTER 19-2: SRCON1: SR LATCH CONTROL 1 REGISTER

| Name   | Bit 7  | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|------------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA | —      | _          | ANSA5  | ANSA4  | ANSA3  | ANSA2  | ANSA1  | ANSA0  | 134                 |

| SRCON0 | SRLEN  | SRCLK<2:0> |        |        | SRQEN  | SRNQEN | SRPS   | SRPR   | 189                 |

| SRCON1 | SRSPE  | SRSCKE     | SRSC2E | SRSC1E | SRRPE  | SRRCKE | SRRC2E | SRRC1E | 190                 |

| TRISA  | TRISA7 | TRISA6     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 133                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the SR Latch module.

## 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

## 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

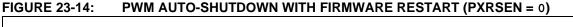

#### 23.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the CCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- A logic '1' on a Comparator (Cx) output

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the CCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 23.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the CCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

- Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or INT pin event, a software shutdown can be triggered in firmware by setting the CCPxASE bit of the CCPxAS register to '1'. The Auto-Restart feature tracks the active status of a shutdown caused by a comparator output or INT pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

## 24.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- · Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

## 24.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See **Section 24.7** "**Baud Rate Generator**" for more detail.

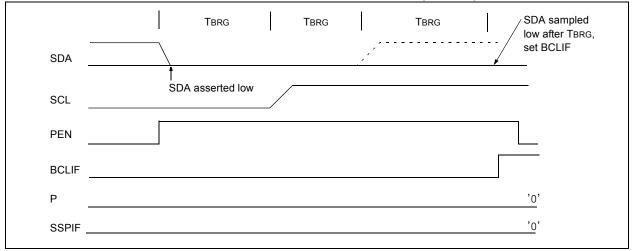

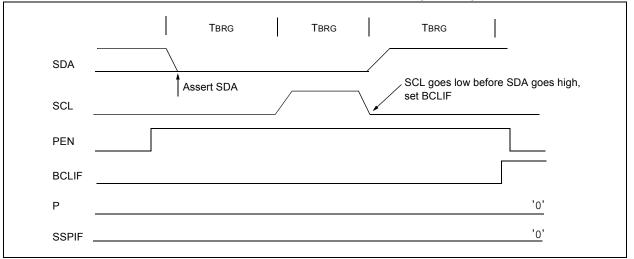

#### 24.6.13.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 24-37). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 24-38).

#### FIGURE 24-38: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 24-39: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH I CTM OPERATION |           |                |               |        |        |        |        |                       |                             |  |

|------------------------------------------------------------------|-----------|----------------|---------------|--------|--------|--------|--------|-----------------------|-----------------------------|--|

| Name                                                             | Bit 7     | Bit 6          | Bit 5         | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Reset<br>Values on<br>Page: |  |

| INTCON                                                           | GIE       | PEIE           | TMR0IE        | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF                 | 98                          |  |

| PIE1                                                             | TMR1GIE   | ADIE           | RCIE          | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE                | 99                          |  |

| PIE2                                                             | OSFIE     | C2IE           | C1IE          | EEIE   | BCLIE  | —      | _      | CCP2IE <sup>(1)</sup> | 100                         |  |

| PIR1                                                             | TMR1GIF   | ADIF           | RCIF          | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF                | 102                         |  |

| PIR2                                                             | OSFIF     | C2IF           | C1IF          | EEIF   | BCLIF  | _      | _      | CCP2IF <sup>(1)</sup> | 103                         |  |

| TRISC                                                            | TRISC7    | TRISC6         | TRISC5        | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0                | 142                         |  |

| SSPADD                                                           |           |                |               | ADD<   | :7:0>  |        |        |                       | 290                         |  |

| SSPBUF                                                           | MSSP Rece | ive Buffer/Tra | nsmit Registe | r      |        |        |        |                       | 243*                        |  |

| SSPCON1                                                          | WCOL      | SSPOV          | SSPEN         | CKP    |        | SSPM   | <3:0>  |                       | 287                         |  |

| SSPCON2                                                          | GCEN      | ACKSTAT        | ACKDT         | ACKEN  | RCEN   | PEN    | RSEN   | SEN                   | 288                         |  |

| SSPCON3                                                          | ACKTIM    | PCIE           | SCIE          | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN                  | 289                         |  |

| SSPMSK                                                           | MSK<7:0>  |                |               |        |        |        |        |                       |                             |  |

| SSPSTAT                                                          | SMP       | CKE            | D/A           | Р      | S      | R/W    | UA     | BF                    | 286                         |  |

## TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>™</sup> OPERATION

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

\* Page provides register information.

Note 1: PIC16F1934 only.

### 25.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is 8 bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 25-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 25.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 25-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 25.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 25.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 25.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit ldle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true ldle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 25.4.1.2 "Clock Polarity"**.

#### 25.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

| U-0                                  | U-0                                             | U-0                  | U-0                                | R/W-0/0 <sup>(1)</sup>                            | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|--------------------------------------|-------------------------------------------------|----------------------|------------------------------------|---------------------------------------------------|---------|-----------|---------|

|                                      | _                                               | _                    | _                                  |                                                   | CPSCI   | H<3:0>    |         |

| bit 7                                |                                                 |                      |                                    |                                                   |         |           | bit 0   |

|                                      |                                                 |                      |                                    |                                                   |         |           |         |

| Legend:                              |                                                 |                      |                                    |                                                   |         |           |         |

| R = Readable bit W = Writable bit    |                                                 | bit                  | U = Unimplemented bit, read as '0' |                                                   |         |           |         |

|                                      |                                                 | x = Bit is unkn      | own                                | -n/n = Value at POR and BOR/Value at all other Re |         | er Resets |         |

| '1' = Bit is set                     | 0                                               | '0' = Bit is cleared |                                    |                                                   |         |           |         |

|                                      |                                                 |                      |                                    |                                                   |         |           |         |

| bit 7-4                              | Unimplement                                     | ted: Read as '0'     |                                    |                                                   |         |           |         |

| bit 3-0                              | •                                               | : Capacitive Ser     |                                    | Select bits                                       |         |           |         |

|                                      | If CPSON = $0$ :                                |                      | loing chamier                      |                                                   |         |           |         |

|                                      | These bits are ignored. No channel is selected. |                      |                                    |                                                   |         |           |         |

|                                      | If CPSON = 1:                                   |                      |                                    |                                                   |         |           |         |

|                                      |                                                 | channel 0, (CP       | S0)                                |                                                   |         |           |         |

| 0001 =<br>0010 =<br>0011 =<br>0100 = |                                                 | channel 1, (CP       | ,                                  |                                                   |         |           |         |

|                                      |                                                 | channel 2, (CP       | S2)                                |                                                   |         |           |         |

|                                      |                                                 | channel 3, (CP       | S3)                                |                                                   |         |           |         |

|                                      |                                                 | channel 4, (CP       | S4)                                |                                                   |         |           |         |

|                                      |                                                 | channel 5, (CP       | S5)                                |                                                   |         |           |         |

|                                      | 0110 =                                          | channel 6, (CP       | S6)                                |                                                   |         |           |         |

|                                      | 0111 =                                          | channel 7, (CP       | S7)                                |                                                   |         |           |         |

|                                      | 1000 =                                          | channel 8, (CP       | S8 <sup>(1)</sup> )                |                                                   |         |           |         |

|                                      |                                                 | channel 9, (CP       |                                    |                                                   |         |           |         |

|                                      |                                                 | channel 10, (CI      |                                    |                                                   |         |           |         |

|                                      | 1011 =                                          | channel 11, (CF      | PS11 <sup>(1)</sup> )              |                                                   |         |           |         |

|                                      |                                                 | channel 12, (CF      |                                    |                                                   |         |           |         |

|                                      |                                                 | channel 13, (CF      |                                    |                                                   |         |           |         |

|                                      |                                                 | channel 14, (CI      |                                    |                                                   |         |           |         |

|                                      |                                                 | channel 15, (Cl      |                                    |                                                   |         |           |         |

|                                      |                                                 |                      |                                    |                                                   |         |           |         |

- Note 1: These channels are not implemented on the PIC16(L)F1936.

2: This bit is not implemented on PIC16(L)F1936, read as '0'

| ΜΟΥΙΨ            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                   |  |  |  |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{FSR + 1 (preincrement)} \\ &\text{FSR - 1 (predecrement)} \\ &\text{FSR + k (relative offset)} \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{FSR + 1 (all increments)} \\ &\text{FSR - 1 (all decrements)} \\ &\text{Unchanged} \end{split}$ |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap around.

#### MOVLB Move literal to BSR

| Syntax:          | [ <i>label</i> ]MOVLB k                                                 |  |  |

|------------------|-------------------------------------------------------------------------|--|--|

| Operands:        | $0 \leq k \leq 15$                                                      |  |  |

| Operation:       | $k \rightarrow BSR$                                                     |  |  |

| Status Affected: | None                                                                    |  |  |

| Description:     | The five-bit literal 'k' is loaded into the Bank Select Register (BSR). |  |  |

| MOVLP            | Move literal to PCLATH                                        |  |  |  |

|------------------|---------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ]MOVLP k                                       |  |  |  |

| Operands:        | $0 \le k \le 127$                                             |  |  |  |

| Operation:       | $k \rightarrow PCLATH$                                        |  |  |  |

| Status Affected: | None                                                          |  |  |  |

| Description:     | The seven-bit literal 'k' is loaded into the PCLATH register. |  |  |  |

| MOVLW            | Move literal to W                                             |  |  |  |

| Syntax:          | [ <i>label</i> ] MOVLW k                                      |  |  |  |

| Operands:        | $0 \le k \le 255$                                             |  |  |  |

| Operation:       | $k \rightarrow (W)$                                           |  |  |  |

| Status Affected: | None                                                          |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into W                    |  |  |  |

ble as '0's.

MOVLW

1

1

Words:

Cycles:

Example:

register. The "don't cares" will assem-

0x5A

|                  | After Instruction<br>W = 0x5A                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------|

| MOVWF            | Move W to f                                                                                               |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                                  |

| Operands:        | $0 \leq f \leq 127$                                                                                       |

| Operation:       | $(W) \to (f)$                                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to register 'f'.                                                                |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | MOVWF OPTION_REG                                                                                          |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

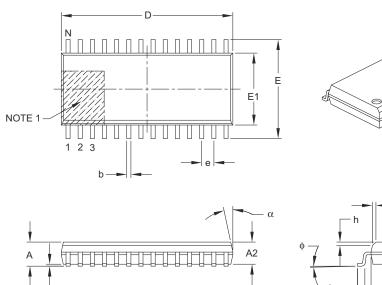

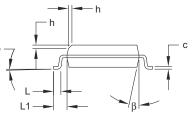

## 28-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

ALALA

|                          | Units            | MILLIMETERS |     | 3    |

|--------------------------|------------------|-------------|-----|------|

|                          | Dimension Limits | MIN         | NOM | MAX  |

| Number of Pins           | N                | 28          |     |      |

| Pitch                    | е                | 1.27 BSC    |     |      |

| Overall Height           | А                | _           | -   | 2.65 |

| Molded Package Thickness | A2               | 2.05        | -   | -    |

| Standoff §               | A1               | 0.10        | _   | 0.30 |

| Overall Width            | E                | 10.30 BSC   |     |      |

| Molded Package Width     | E1               | 7.50 BSC    |     |      |

| Overall Length           | D                | 17.90 BSC   |     |      |

| Chamfer (optional)       | h                | 0.25        | _   | 0.75 |

| Foot Length              | L                | 0.40        | -   | 1.27 |

| Footprint                | L1               | 1.40 REF    |     |      |

| Foot Angle Top           | φ                | 0°          | -   | 8°   |

| Lead Thickness           | С                | 0.18        | -   | 0.33 |

| Lead Width               | b                | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α                | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β                | 5°          | -   | 15°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

A1

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-052B