#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1936t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1934/6/7

# PIC16(L)F1934/6/7

| Address                | Name                                                                                                            | Bit 7                                                            | Bit 6        | Bit 5          | Bit 4        | Bit 3          | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------|----------------|--------------|----------------|----------------------|----------------------|----------------------|----------------------|---------------------------------|

| Bank 2                 |                                                                                                                 |                                                                  |              |                |              |                |                      |                      |                      |                      |                                 |

| 100h <sup>(2)</sup>    | INDF0                                                                                                           | Addressing<br>(not a physi                                       |              | ses contents o | of FSR0H/FSF | R0L to address | data memory          | /                    |                      | XXXX XXXX            | XXXX XXXX                       |

| 101h <sup>(2)</sup>    | INDF1 Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                                                                  |              |                |              |                |                      |                      |                      | XXXX XXXX            | XXXX XXXX                       |

| 102h <sup>(2)</sup>    | PCL                                                                                                             | Program Counter (PC) Least Significant Byte                      |              |                |              |                |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 103h <sup>(2)</sup>    | STATUS                                                                                                          | _                                                                | _            | _              | TO           | PD             | Z                    | DC                   | С                    | 1 1000               | q quuu                          |

| 104h <sup>(2)</sup>    | FSR0L                                                                                                           | Indirect Data                                                    | a Memory Add | Iress 0 Low Po | ointer       |                | •                    |                      | •                    | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(2)</sup>    | FSR0H                                                                                                           | Indirect Data                                                    | a Memory Add | lress 0 High P | ointer       |                |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 106h <sup>(2)</sup>    | FSR1L                                                                                                           | Indirect Dat                                                     | a Memory Add | Iress 1 Low Po | ointer       |                |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(2)</sup>    | FSR1H                                                                                                           | Indirect Dat                                                     | a Memory Add | lress 1 High P | ointer       |                |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 108h <sup>(2)</sup>    | BSR                                                                                                             | _                                                                | —            | —              |              | E              | BSR<4:0>             |                      |                      | 0 0000               | 0 0000                          |

| 109h <sup>(2)</sup>    | WREG                                                                                                            |                                                                  |              |                |              |                |                      |                      |                      |                      | uuuu uuuu                       |

| 10Ah <sup>(1, 2)</sup> | PCLATH                                                                                                          | CLATH — Write Buffer for the upper 7 bits of the Program Counter |              |                |              |                |                      |                      |                      |                      | -000 0000                       |

| 10Bh <sup>(2)</sup>    | INTCON                                                                                                          | GIE                                                              | PEIE         | TMR0IE         | INTE         | IOCIE          | TMR0IF               | INTF                 | IOCIF                | 0000 0000            | 0000 0000                       |

| 10Ch                   | LATA                                                                                                            | PORTA Data Latch                                                 |              |                |              |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 10Dh                   | LATB PORTB Data Latch                                                                                           |                                                                  |              |                |              |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 10Eh                   | LATC                                                                                                            | ATC PORTC Data Latch                                             |              |                |              |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 10Fh <sup>(3)</sup>    | LATD                                                                                                            | PORTD Dat                                                        | ta Latch     |                |              |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 110h                   | LATE                                                                                                            | _                                                                | —            | —              |              | _              | LATE2 <sup>(3)</sup> | LATE1 <sup>(3)</sup> | LATE0 <sup>(3)</sup> | xxx                  | uuu                             |

| 111h                   | CM1CON0                                                                                                         | C10N                                                             | C10UT        | C10E           | C1POL        | _              | C1SP                 | C1HYS                | C1SYNC               | 0000 -100            | 0000 -100                       |

| 112h                   | CM1CON1                                                                                                         | C1INTP                                                           | C1INTN       | C1PCH1         | C1PCH0       | _              | _                    | C1NCI                | H<1:0>               | 000000               | 000000                          |

| 113h                   | CM2CON0                                                                                                         | C2ON                                                             | C2OUT        | C2OE           | C2POL        | _              | C2SP                 | C2HYS                | C2SYNC               | 0000 -100            | 0000 -100                       |

| 114h                   | CM2CON1                                                                                                         | C2INTP                                                           | C2INTN       | C2PCH1         | C2PCH0       | _              | _                    | C2NCI                | H<1:0>               | 000000               | 000000                          |

| 115h                   | CMOUT                                                                                                           | _                                                                | _            | _              |              | _              | _                    | MC2OUT               | MC10UT               | 00                   | 00                              |

| 116h                   | BORCON                                                                                                          | SBOREN                                                           | _            | _              | _            | _              | _                    | —                    | BORRDY               | 1 q                  | uu                              |

| 117h                   | FVRCON                                                                                                          | FVREN                                                            | FVRRDY       | TSEN           | TSRNG        | CDAFVR1        | CDAFVR0              | ADFVI                | R<1:0>               | 0q00 0000            | 0q00 0000                       |

| 118h                   | DACCON0                                                                                                         | DACEN                                                            | DACLPS       | DACOE          |              | DACPS          | S<1:0>               |                      | DACNSS               | 000- 00-0            | 000- 00-0                       |

| 119h                   | DACCON1                                                                                                         |                                                                  |              |                |              | D              | ACR<4:0>             |                      | -                    | 0 0000               | 0 0000                          |

| 11Ah                   | SRCON0                                                                                                          | SRLEN                                                            | SRCLK2       | SRCLK1         | SRCLK0       | SRQEN          | SRNQEN               | SRPS                 | SRPR                 | 0000 0000            | 0000 0000                       |

| 11Bh                   | SRCON1                                                                                                          | SRSPE                                                            | SRSCKE       | SRSC2E         | SRSC1E       | SRRPE          | SRRCKE               | SRRC2E               | SRRC1E               | 0000 0000            | 0000 0000                       |

| 11Ch                   | —                                                                                                               | Unimpleme                                                        | nted         |                |              |                |                      |                      |                      | —                    | _                               |

| 11Dh                   | APFCON                                                                                                          | _                                                                | CCP3SEL      | T1GSEL         | P2BSEL       | SRNQSEL        | C2OUTSEL             | SSSEL                | CCP2SEL              | -000 0000            | -000 0000                       |

| 11Eh                   | —                                                                                                               | Unimpleme                                                        | nted         |                | •            |                |                      | •                    |                      | _                    | _                               |

| 11Fh                   | Unimplemented                                                                                                   |                                                                  |              |                |              |                |                      |                      |                      | _                    | _                               |

#### **TABLE 3-12:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 98                  |

| OPTION_REG | WPUEN   | INTEDG | TMROCS | TMROSE | PSA    |        | PS<2:0> |        | 193                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | 99                  |

| PIE2       | OSFIE   | C2IE   | C1IE   | EEIE   | BCLIE  | LCDIE  | _       | CCP2IE | 100                 |

| PIE3       | _       | CCP5IE | CCP4IE | CCP3IE | TMR6IE | _      | TMR4IE  | —      | 101                 |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | 102                 |

| PIR2       | OSFIF   | C2IF   | C1IF   | EEIF   | BCLIF  | LCDIF  |         | CCP2IF | 103                 |

| PIR3       |         | CCP5IF | CCP4IF | CCP3IF | TMR6IF |        | TMR4IF  | _      | 104                 |

TABLE 7-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupts.

#### 9.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- 9. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

#### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.10 "Determining the Cause of a Reset"**.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 11.4 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

- 8. Repeat steps 6 and 7 as many times as required to reprogram the erased row.

#### 11.5 User ID, Device ID and Configuration Word Access

Instead of accessing program memory or EEPROM data memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the EECON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 11-2.

When read access is initiated on an address outside the parameters listed in Table 11-2, the EEDATH:EEDATL register pair is cleared.

| _ |             |                             |             | (0) 00 = =)  |

|---|-------------|-----------------------------|-------------|--------------|

|   | Address     | Function                    | Read Access | Write Access |

|   | 8000h-8003h | User IDs                    | Yes         | Yes          |

| Γ | 8006h       | Device ID/Revision ID       | Yes         | No           |

| Γ | 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

## TABLE 11-2: USER ID, DEVICE ID AND CONFIGURATION WORD ACCESS (CFGS = 1)

#### EXAMPLE 11-3: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

- \* PROG\_ADDR\_LO (must be 00h-08h) data will be returned in the variables;

- \* PROG\_DATA\_HI, PROG\_DATA\_LO

| M                | ANKSEL<br>OVLW<br>OVWF<br>LRF    | PROG_ADDR_LO<br>EEADRL   | ;<br>;      | Select correct Bank<br>Store LSB of address<br>Clear MSB of address                                                                                |

|------------------|----------------------------------|--------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| B<br>B<br>N<br>N | SF<br>CF<br>SF<br>OP<br>OP<br>SF | INTCON,GIE<br>EECON1,RD  | ;<br>;<br>; | Select Configuration Space<br>Disable interrupts<br>Initiate read<br>Executed (See Figure 11-1)<br>Ignored (See Figure 11-1)<br>Restore interrupts |

| M<br>M           | OVF<br>OVWF<br>OVF<br>OVWF       | PROG_DATA_LO<br>EEDATH,W | ;<br>;      | Get LSB of word<br>Store in user location<br>Get MSB of word<br>Store in user location                                                             |

| R/W-0/0                            | R/W-0/0            | R/W-0/0                                                                                                                                                   | R/W/HC-0/0                 | R/W-x/q           | R/W-0/0           | R/S/HC-0/0             | R/S/HC-0/0      |  |  |

|------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|-------------------|------------------------|-----------------|--|--|

| EEPGD                              | CFGS               | LWLO                                                                                                                                                      | FREE                       | WRERR             | WREN              | WR                     | RD              |  |  |

| bit 7                              |                    |                                                                                                                                                           |                            |                   |                   |                        | bit C           |  |  |

| Logondi                            |                    |                                                                                                                                                           |                            |                   |                   |                        |                 |  |  |

| Legend:<br>R = Readable            | hit                | W = Writable                                                                                                                                              | hit                        | II – Unimplo      | monted hit read   | d oo 'O'               |                 |  |  |

|                                    |                    | x = Bit is unk                                                                                                                                            |                            | •                 | mented bit, read  | R/Value at all c       | than Basata     |  |  |

| S = Bit can or<br>'1' = Bit is set | •                  |                                                                                                                                                           |                            |                   |                   |                        | Inel Resels     |  |  |

| I = DILIS SEL                      |                    | '0' = Bit is cle                                                                                                                                          | areu                       |                   | eared by hardw    | Vale                   |                 |  |  |

| bit 7                              | EEPGD: Flas        | sh Program/Da                                                                                                                                             | ta EEPROM M                | emory Select      | bit               |                        |                 |  |  |

|                                    |                    | s program spa<br>s data EEPRO                                                                                                                             | ce Flash memo<br>M memory  | ory               |                   |                        |                 |  |  |

| bit 6                              |                    |                                                                                                                                                           | EEPROM or C                | Configuration     | Select bit        |                        |                 |  |  |

|                                    | 1 = Accesse        | s Configuration                                                                                                                                           | n, User ID and             | Device ID Reg     | gisters           |                        |                 |  |  |

|                                    |                    | -                                                                                                                                                         | m or data EEP              | ROM Memory        | /                 |                        |                 |  |  |

| bit 5                              |                    | Write Latches                                                                                                                                             | •                          |                   |                   |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   | EPGD = 1 (prog    |                        |                 |  |  |

|                                    |                    | next WR con ated.                                                                                                                                         | nmand does no              | ot initiate a w   | rite; only the p  | program memo           | y latches are   |  |  |

|                                    |                    |                                                                                                                                                           | mand writes a v            | alue from EEI     | DATH:EEDATL       | into program m         | emory latche    |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   | program memo      |                        | 2               |  |  |

|                                    | If CFGS = 0 a      | and EEPGD =                                                                                                                                               | 0: (Accessing of           | data EEPRON       | 1)                |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   | e to the data El  | EPROM.                 |                 |  |  |

| bit 4                              | FREE: Progr        | am Flash Eras                                                                                                                                             | e Enable bit               |                   |                   |                        |                 |  |  |

|                                    | <u>If CFGS = 1</u> | (Configuration                                                                                                                                            | <u>space)</u> OR <u>CF</u> | GS = 0 and E      | EPGD = 1 (prog    | gram Flash):           |                 |  |  |

|                                    |                    |                                                                                                                                                           | operation on t             | he next WR c      | ommand (clear     | ed by hardware         | after comple    |  |  |

|                                    |                    | of erase).<br>forms a write o                                                                                                                             | peration on the            | next WR con       | nmand.            |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   |                   |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           | <u>0:</u> (Accessing       |                   |                   | and a write av         |                 |  |  |

| hit 0                              | -                  |                                                                                                                                                           |                            | will initiate boi | n a erase cycle   | and a write cyo        | le.             |  |  |

| bit 3                              |                    | PROM Error F                                                                                                                                              | •                          | ram or oraco      | soquence atte     | mot or tormina         | tion (hit is so |  |  |

|                                    |                    | Condition indicates an improper program or erase sequence attempt or termination (bit is set automatically on any set attempt (write '1') of the WR bit). |                            |                   |                   |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           | operation comp             |                   |                   |                        |                 |  |  |

| bit 2                              | WREN: Prog         | ram/Erase Ena                                                                                                                                             | able bit                   |                   |                   |                        |                 |  |  |

|                                    |                    | rogram/erase o                                                                                                                                            |                            |                   |                   |                        |                 |  |  |

|                                    | -                  |                                                                                                                                                           | rasing of progra           | am Flash and      | data EEPROM       |                        |                 |  |  |

| bit 1                              | WR: Write Co       |                                                                                                                                                           |                            |                   | , .               |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   | n/erase operation | on.<br>operation is co | mnlete          |  |  |

|                                    |                    |                                                                                                                                                           | e set (not cleare          |                   |                   |                        | inpiete.        |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   | OM is complete    | e and inactive.        |                 |  |  |

| bit 0                              | RD: Read Co        | ontrol bit                                                                                                                                                |                            |                   |                   |                        |                 |  |  |

|                                    |                    |                                                                                                                                                           |                            |                   |                   | one cycle. RD          | is cleared in   |  |  |

|                                    |                    |                                                                                                                                                           | an only be set             |                   |                   |                        |                 |  |  |

|                                    |                    | i miliale a prog                                                                                                                                          | ram Flash or d             | αια ΕΕΓΚΟΙΝ       | udia iedu.        |                        |                 |  |  |

#### REGISTER 11-5: EECON1: EEPROM CONTROL 1 REGISTER

| W-0/0            | W-0/0    | W-0/0             | W-0/0     | W-0/0             | W-0/0            | W-0/0            | W-0/0       |

|------------------|----------|-------------------|-----------|-------------------|------------------|------------------|-------------|

|                  |          |                   | EEPROM Co | ontrol Register 2 |                  |                  |             |

| bit 7            |          |                   |           | -                 |                  |                  | bit 0       |

|                  |          |                   |           |                   |                  |                  |             |

| Legend:          |          |                   |           |                   |                  |                  |             |

| R = Readable     | bit      | W = Writable      | bit       | U = Unimplen      | nented bit, read | as '0'           |             |

| S = Bit can onl  | y be set | x = Bit is unkr   | nown      | -n/n = Value a    | t POR and BO     | R/Value at all c | ther Resets |

| '1' = Bit is set |          | '0' = Bit is clea | ared      |                   |                  |                  |             |

#### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 11.2.2** "Writing to the Data EEPROM Memory" for more information.

#### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7                                                   | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register on<br>Page |

|--------|---------------------------------------------------------|-------|--------|-------|-------|--------|-------|--------|---------------------|

| EECON1 | EEPGD                                                   | CFGS  | LWLO   | FREE  | WRERR | WREN   | WR    | RD     | 127                 |

| EECON2 | ON2 EEPROM Control Register 2 (not a physical register) |       |        |       |       |        |       |        |                     |

| EEADRL | EEADRL<7:0>                                             |       |        |       |       |        |       |        | 126                 |

| EEADRH | EEADRH<6:0                                              |       |        |       |       |        |       |        | 126                 |

| EEDATL | EEDATL<7:0>                                             |       |        |       |       |        |       |        | 126                 |

| EEDATH | _                                                       | _     |        |       | EEDAT | H<5:0> |       |        | 126                 |

| INTCON | GIE                                                     | PEIE  | TMR0IE | INTE  | IOCIE | TMR0IF | INTF  | IOCIF  | 98                  |

| PIE2   | OSFIE                                                   | C2IE  | C1IE   | EEIE  | BCLIE | LCDIE  | _     | CCP2IE | 100                 |

| PIR2   | OSFIF                                                   | C2IF  | C1IF   | EEIF  | BCLIF | LCDIF  | —     | CCP2IF | 103                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the data EEPROM module.

\* Page provides register information.

#### REGISTER 12-22: WPUE: WEAK PULL-UP PORTE REGISTER

| U-0                               | U-0        | U-0              | U-0                                | R/W-1/1        | U-0            | U-0              | U-0         |  |

|-----------------------------------|------------|------------------|------------------------------------|----------------|----------------|------------------|-------------|--|

|                                   |            |                  | _                                  | WPUE3          |                | —                | _           |  |

| bit 7                             | ÷          |                  |                                    |                |                |                  | bit 0       |  |

|                                   |            |                  |                                    |                |                |                  |             |  |

| Legend:                           |            |                  |                                    |                |                |                  |             |  |

| R = Readable bit W = Writable bit |            | bit              | U = Unimplemented bit, read as '0' |                |                |                  |             |  |

| u = Bit is u                      | nchanged   | x = Bit is unkr  | nown                               | -n/n = Value a | at POR and BOF | R/Value at all c | ther Resets |  |

| '1' = Bit is s                    | set        | '0' = Bit is cle | ared                               |                |                |                  |             |  |

| bit 7-4                           | Unimplomor | ited: Read as '  | 0'                                 |                |                |                  |             |  |

| DIL 7-4                           | ommplemen  |                  | U                                  |                |                |                  |             |  |

| bit 3                             | WPUE: Weal | k Pull-up Regis  | ter bit                            |                |                |                  |             |  |

|                                   |            |                  |                                    |                |                |                  |             |  |

- 1 = Pull-up enabled

- 0 = Pull-up disabled

bit 2-0 Unimplemented: Read as '0'

**Note 1:** Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3   | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|---------|-------|-------|-------|----------|---------|-----------------------|-----------------------|-----------------------|---------------------|

| ADCON0  | —     |       |       | CHS<4:0> |         |                       | GO/DONE               | ADON                  | 163                 |

| ANSELE  | _     | _     | _     |          | _       | ANSE2 <sup>(1)</sup>  | ANSE1 <sup>(1)</sup>  | ANSE0 <sup>(1)</sup>  | 149                 |

| CCPxCON | PxM≤  | <1:0> | DCxB  | <1:0>    |         | CCPxM<3:0>            |                       |                       |                     |

| LATE    | —     | _     | _     | _        | _       | LATE2 <sup>(1)</sup>  | LATE1 <sup>(1)</sup>  | LATE0 <sup>(1)</sup>  | 149                 |

| LCDCON  | LCDEN | SLPEN | WERR  | _        | CS<1:0> |                       | LMUX<1:0>             |                       | 329                 |

| LCDSE2  | SE23  | SE22  | SE21  | SE20     | SE19    | SE18                  | SE17                  | SE16                  | 333                 |

| PORTE   | —     | _     | _     | _        | RE3     | RE2 <sup>(1)</sup>    | RE1 <sup>(1)</sup>    | RE0 <sup>(1)</sup>    | 148                 |

| TRISE   | _     | _     | _     | _        | (2)     | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> | 148                 |

| WPUE    | _     | _     | _     | _        | WPUE3   | —                     | _                     | _                     | 150                 |

#### TABLE 12-12: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE.

Note 1: These bits are not implemented on the PIC16(L)F1936 devices, read as '0'.

2: Unimplemented, read as '1'.

3: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

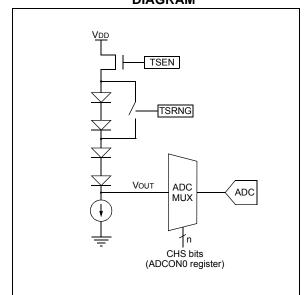

#### 16.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

#### 16.1 Circuit Operation

Figure 16-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 16-1 describes the output characteristics of the temperature indicator.

#### EQUATION 16-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 16-1: TEMPERATURE CIRCUIT DIAGRAM

#### 16.2 Minimum Operating VDD vs. Minimum Sensing Temperature

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 16-1 shows the recommended minimum VDD vs. range setting.

TABLE 16-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

#### 16.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 16.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

### 16.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

<sup>© 2008-2011</sup> Microchip Technology Inc.

#### 21.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 21-1 displays the Timer1 enable selections.

| TABLE 21-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

#### 21.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 21-2 displays the clock source selections.

#### 21.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

#### 21.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T1OSCEN | Clock Source                   |

|---------|---------|---------|--------------------------------|

| 0       | 0       | x       | Instruction Clock (Fosc/4)     |

| 0       | 1       | x       | System Clock (FOSC)            |

| 1       | 0       | 0       | External Clocking on T1CKI Pin |

| 1       | 0       | 0       | External Clocking on T1CKI Pin |

| 1       | 1       | x       | Capacitive Sensing Oscillator  |

#### TABLE 21-2: CLOCK SOURCE SELECTIONS

#### 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

#### 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

#### 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

#### 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see **Section 12.1 "Alternate Pin Function**" for more information.

| Name                 | Bit 7       | Bit 6           | Bit 5        | Bit 4         | Bit 3             | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|-------------|-----------------|--------------|---------------|-------------------|-----------------------|-----------------------|-----------------------|---------------------|

| APFCON               | _           | CCP3SEL         | T1GSEL       | P2BSEL        | SRNQSEL           | C2OUTSEL              | SSSEL                 | CCP2SEL               | 131                 |

| CCPxCON              | PxM<        | 1:0> <b>(1)</b> | DCxB         | <1:0>         |                   | CCPxM<                | :3:0>                 |                       | 234                 |

| CCPRxL               | Capture/Co  | mpare/PWM       | Register x l | Low Byte (LS  | SB)               |                       |                       |                       | 212                 |

| CCPRxH               | Capture/Co  | mpare/PWM       | Register x I | High Byte (M  | ISB)              |                       |                       |                       | 212                 |

| INTCON               | GIE         | PEIE            | TMR0IE       | INTE          | IOCIE             | TMR0IF                | INTF                  | IOCIF                 | 98                  |

| PIE1                 | TMR1GIE     | ADIE            | RCIE         | TXIE          | SSPIE             | CCP1IE                | TMR2IE                | TMR1IE                | 99                  |

| PIE2                 | OSFIE       | C2IE            | C1IE         | EEIE          | BCLIE             | LCDIE                 | _                     | CCP2IE                | 100                 |

| PIE3                 | —           | CCP5IE          | CCP4IE       | CCP3IE        | TMR6IE            | _                     | TMR4IE                | _                     | 101                 |

| PIR1                 | TMR1GIF     | ADIF            | RCIF         | TXIF          | SSPIF             | CCP1IF                | TMR2IF                | TMR1IF                | 102                 |

| PIR2                 | OSFIF       | C2IF            | C1IF         | EEIF          | BCLIF             | LCDIF                 | _                     | CCP2IF                | 103                 |

| PIR3                 | —           | CCP5IF          | CCP4IF       | CCP3IF        | TMR6IF            | _                     | TMR4IF                | —                     | 104                 |

| T1CON                | TMR1C       | S<1:0>          | T1CKP        | S<1:0>        | T1OSCEN           | T1SYNC                | _                     | TMR10N                | 203                 |

| T1GCON               | TMR1GE      | T1GPOL          | T1GTM        | T1GSPM        | T1GGO/DONE        | T1GVAL                | T1GSS                 | S<1:0>                | 204                 |

| TMR1L                | Holding Reg | gister for the  | Least Signif | icant Byte of | f the 16-bit TMR1 | 1 Register            |                       |                       | 199                 |

| TMR1H                | Holding Reg | gister for the  | Most Signifi | cant Byte of  | the 16-bit TMR1   | Register              |                       |                       | 199                 |

| TRISA                | TRISA7      | TRISA6          | TRISA5       | TRISA4        | TRISA3            | TRISA2                | TRISA1                | TRISA0                | 133                 |

| TRISB                | TRISB7      | TRISB6          | TRISB5       | TRISB4        | TRISB3            | TRISB2                | TRISB1                | TRISB0                | 138                 |

| TRISC                | TRISC7      | TRISC6          | TRISC5       | TRISC4        | TRISC3            | TRISC2                | TRISC1                | TRISC0                | 142                 |

| TRISD <sup>(2)</sup> | TRISD7      | TRISD6          | TRISD5       | TRISD4        | TRISD3            | TRISD2                | TRISD1                | TRISD0                | 145                 |

| TRISE                |             |                 |              | —             | _(3)              | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 148                 |

| TABLE 23-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE |

|-------------|----------------------------------------------|

|             |                                              |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

Note 1: Applies to ECCP modules only.

2: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

3: Unimplemented, read as '1'.

#### 25.1 EUSART Asynchronous Mode

The EUSART transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state which represents a '1' data bit, and a VOL space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is 8 bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 25-5 for examples of baud rate configurations.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 25.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 25-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TXREG register.

#### 25.1.1.1 Enabling the Transmitter

The EUSART transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the TXEN bit of the TXSTA register enables the transmitter circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note 1:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 25.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TXREG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the Stop bit of the previous character has been transmitted. The pending character in the TXREG is then transferred to the TSR in one TCY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TXREG.

#### 25.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUDCON register. The default state of this bit is '0' which selects high true transmit ldle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true ldle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 25.4.1.2 "Clock Polarity"**.

#### 25.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART transmitter is enabled and no character is being held for transmission in the TXREG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TXREG. The TXIF flag bit is not cleared immediately upon writing TXREG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TXREG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TXREG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TXREG.

|        |                |            |                             |                | SYNC       | <b>C</b> = 0, BRGH          | l = 1, BRC     | <b>616 =</b> 0 |                             |                |                  |                             |  |

|--------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|----------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fos            | c = 8.000  | ) MHz                       | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686      | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | —              | _          | —                           | _              |            | _                           |                |                | _                           | 300            | 0.16             | 207                         |  |

| 1200   | —              | —          | —                           | 1202           | 0.16       | 207                         | 1200           | 0.00           | 191                         | 1202           | 0.16             | 51                          |  |

| 2400   | 2404           | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00           | 95                          | 2404           | 0.16             | 25                          |  |

| 9600   | 9615           | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00           | 23                          | —              | _                | _                           |  |

| 10417  | 10417          | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53           | 21                          | 10417          | 0.00             | 5                           |  |

| 19.2k  | 19231          | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.2k          | 0.00           | 11                          | —              | _                | _                           |  |

| 57.6k  | 55556          | -3.55      | 8                           | —              | _          | _                           | 57.60k         | 0.00           | 3                           | —              | _                | _                           |  |

| 115.2k | —              | _          | —                           | —              | _          | —                           | 115.2k         | 0.00           | 1                           | —              | _                | —                           |  |

## TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                |            |                             |                   |            |                             |                |                    |                             |  |

|--------|----------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc           | : = 32.00                     | 0 MHz                       | Fosc           | = 20.00    | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    | 300.0          | 0.00                          | 6666                        | 300.0          | -0.01      | 4166                        | 300.0             | 0.00       | 3839                        | 300.0          | 0.00               | 2303                        |  |

| 1200   | 1200           | -0.02                         | 3332                        | 1200           | -0.03      | 1041                        | 1200              | 0.00       | 959                         | 1200           | 0.00               | 575                         |  |

| 2400   | 2401           | -0.04                         | 832                         | 2399           | -0.03      | 520                         | 2400              | 0.00       | 479                         | 2400           | 0.00               | 287                         |  |

| 9600   | 9615           | 0.16                          | 207                         | 9615           | 0.16       | 129                         | 9600              | 0.00       | 119                         | 9600           | 0.00               | 71                          |  |

| 10417  | 10417          | 0.00                          | 191                         | 10417          | 0.00       | 119                         | 10378             | -0.37      | 110                         | 10473          | 0.53               | 65                          |  |

| 19.2k  | 19.23k         | 0.16                          | 103                         | 19.23k         | 0.16       | 64                          | 19.20k            | 0.00       | 59                          | 19.20k         | 0.00               | 35                          |  |

| 57.6k  | 57.14k         | -0.79                         | 34                          | 56.818         | -1.36      | 21                          | 57.60k            | 0.00       | 19                          | 57.60k         | 0.00               | 11                          |  |

| 115.2k | 117.6k         | 2.12                          | 16                          | 113.636        | -1.36      | 10                          | 115.2k            | 0.00       | 9                           | 115.2k         | 0.00               | 5                           |  |

|        |                  | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                |                  |                             |                |            |                             |                  |            |                             |  |  |

|--------|------------------|-------------------------------|-----------------------------|----------------|------------------|-----------------------------|----------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz |                               |                             | Fos            | Fosc = 4.000 MHz |                             |                | : = 3.686  | 4 MHz                       | Fosc = 1.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate   | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 299.9            | -0.02                         | 1666                        | 300.1          | 0.04             | 832                         | 300.0          | 0.00       | 767                         | 300.5            | 0.16       | 207                         |  |  |

| 1200   | 1199             | -0.08                         | 416                         | 1202           | 0.16             | 207                         | 1200           | 0.00       | 191                         | 1202             | 0.16       | 51                          |  |  |

| 2400   | 2404             | 0.16                          | 207                         | 2404           | 0.16             | 103                         | 2400           | 0.00       | 95                          | 2404             | 0.16       | 25                          |  |  |

| 9600   | 9615             | 0.16                          | 51                          | 9615           | 0.16             | 25                          | 9600           | 0.00       | 23                          | —                | _          | _                           |  |  |

| 10417  | 10417            | 0.00                          | 47                          | 10417          | 0.00             | 23                          | 10473          | 0.53       | 21                          | 10417            | 0.00       | 5                           |  |  |

| 19.2k  | 19.23k           | 0.16                          | 25                          | 19.23k         | 0.16             | 12                          | 19.20k         | 0.00       | 11                          | —                | _          | _                           |  |  |

| 57.6k  | 55556            | -3.55                         | 8                           | —              | _                | —                           | 57.60k         | 0.00       | 3                           | —                | —          | —                           |  |  |