Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

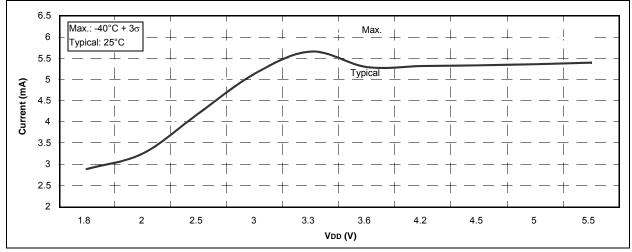

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1937-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.1.1 READING PROGRAM MEMORY AS DATA

There are two methods of accessing constants in program memory. The first method is to use tables of RETLW instructions. The second method is to set an FSR to point to the program memory.

#### 3.1.1.1 RETLW Instruction

The RETLW instruction can be used to provide access to tables of constants. The recommended way to create such a table is shown in Example 3-1.

EXAMPLE 3-1: RETLW INSTRUCTION

| constants         |                     |

|-------------------|---------------------|

| BRW               | ;Add Index in W to  |

|                   | ;program counter to |

|                   | ;select data        |

| RETLW DATA0       | ;Index0 data        |

| RETLW DATA1       | ;Index1 data        |

| RETLW DATA2       |                     |

| RETLW DATA3       |                     |

|                   |                     |

|                   |                     |

| my_function       |                     |

| ; LOTS OF CODE    |                     |

| MOVLW DATA_INI    | DEX                 |

| call constants    |                     |

| ; THE CONSTANT IS | IN W                |

|                   |                     |

The BRW instruction makes this type of table very simple to implement. If your code must remain portable with previous generations of microcontrollers, then the BRW instruction is not available so the older table read method must be used.

### TABLE 3-3: PIC16(L)F1934 MEMORY MAP, BANKS 0-7

|      | BANK 0                         | •    | BANK 1                                     |      | BANK 2                                     |      | BANK 3                       |      | BANK 4                       |      | BANK 5                       |      | BANK 6                       |      | BANK 7                       |

|------|--------------------------------|------|--------------------------------------------|------|--------------------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|

| 000h | INDF0                          | 080h | INDF0                                      | 100h | INDF0                                      | 180h | INDF0                        | 200h | INDF0                        | 280h | INDF0                        | 300h | INDF0                        | 380h | INDF0                        |

| 001h | INDF1                          | 081h | INDF1                                      | 101h | INDF1                                      | 181h | INDF1                        | 201h | INDF1                        | 281h | INDF1                        | 301h | INDF1                        | 381h | INDF1                        |

| 002h | PCL                            | 082h | PCL                                        | 102h | PCL                                        | 182h | PCL                          | 202h | PCL                          | 282h | PCL                          | 302h | PCL                          | 382h | PCL                          |

| 003h | STATUS                         | 083h | STATUS                                     | 103h | STATUS                                     | 183h | STATUS                       | 203h | STATUS                       | 283h | STATUS                       | 303h | STATUS                       | 383h | STATUS                       |

| 004h | FSR0L                          | 084h | FSR0L                                      | 104h | FSR0L                                      | 184h | FSR0L                        | 204h | FSR0L                        | 284h | FSR0L                        | 304h | FSR0L                        | 384h | FSR0L                        |

| 005h | FSR0H                          | 085h | FSR0H                                      | 105h | FSR0H                                      | 185h | FSR0H                        | 205h | FSR0H                        | 285h | FSR0H                        | 305h | FSR0H                        | 385h | FSR0H                        |

| 006h | FSR1L                          | 086h | FSR1L                                      | 106h | FSR1L                                      | 186h | FSR1L                        | 206h | FSR1L                        | 286h | FSR1L                        | 306h | FSR1L                        | 386h | FSR1L                        |

| 007h | FSR1H                          | 087h | FSR1H                                      | 107h | FSR1H                                      | 187h | FSR1H                        | 207h | FSR1H                        | 287h | FSR1H                        | 307h | FSR1H                        | 387h | FSR1H                        |

| 008h | BSR                            | 088h | BSR                                        | 108h | BSR                                        | 188h | BSR                          | 208h | BSR                          | 288h | BSR                          | 308h | BSR                          | 388h | BSR                          |

| 009h | WREG                           | 089h | WREG                                       | 109h | WREG                                       | 189h | WREG                         | 209h | WREG                         | 289h | WREG                         | 309h | WREG                         | 389h | WREG                         |

| 00Ah | PCLATH                         | 08Ah | PCLATH                                     | 10Ah | PCLATH                                     | 18Ah | PCLATH                       | 20Ah | PCLATH                       | 28Ah | PCLATH                       | 30Ah | PCLATH                       | 38Ah | PCLATH                       |

| 00Bh | INTCON                         | 08Bh | INTCON                                     | 10Bh | INTCON                                     | 18Bh | INTCON                       | 20Bh | INTCON                       | 28Bh | INTCON                       | 30Bh | INTCON                       | 38Bh | INTCON                       |

| 00Ch | PORTA                          | 08Ch | TRISA                                      | 10Ch | LATA                                       | 18Ch | ANSELA                       | 20Ch | —                            | 28Ch | —                            | 30Ch | —                            | 38Ch | _                            |

| 00Dh | PORTB                          | 08Dh | TRISB                                      | 10Dh | LATB                                       | 18Dh | ANSELB                       | 20Dh | WPUB                         | 28Dh | —                            | 30Dh | —                            | 38Dh | —                            |

| 00Eh | PORTC                          | 08Eh | TRISC                                      | 10Eh | LATC                                       | 18Eh | _                            | 20Eh |                              | 28Eh | —                            | 30Eh | —                            | 38Eh | _                            |

| 00Fh | PORTD <sup>(1)</sup>           | 08Fh | TRISD <sup>(1)</sup>                       | 10Fh | LATD <sup>(1)</sup>                        | 18Fh | ANSELD <sup>(1)</sup>        | 20Fh | _                            | 28Fh | —                            | 30Fh | —                            | 38Fh | _                            |

| 010h | PORTE                          | 090h | TRISE                                      | 110h | LATE <sup>(1)</sup>                        | 190h | ANSELE <sup>(1)</sup>        | 210h | WPUE                         | 290h | —                            | 310h | —                            | 390h |                              |

| 011h | PIR1                           | 091h | PIE1                                       | 111h | CM1CON0                                    | 191h | EEADRL                       | 211h | SSPBUF                       | 291h | CCPR1L                       | 311h | CCPR3L                       | 391h | _                            |

| 012h | PIR2                           | 092h | PIE2                                       | 112h | CM1CON1                                    | 192h | EEADRH                       | 212h | SSPADD                       | 292h | CCPR1H                       | 312h | CCPR3H                       | 392h | _                            |

| 013h | PIR3                           | 093h | PIE3                                       | 113h | CM2CON0                                    | 193h | EEDATL                       | 213h | SSPMSK                       | 293h | CCP1CON                      | 313h | CCP3CON                      | 393h | —                            |

| 014h | —                              | 094h | _                                          | 114h | CM2CON1                                    | 194h | EEDATH                       | 214h | SSPSTAT                      | 294h | PWM1CON                      | 314h | PWM3CON                      | 394h | IOCBP                        |

| 015h | TMR0                           | 095h | OPTION_REG                                 | 115h | CMOUT                                      | 195h | EECON1                       | 215h | SSPCON1                      | 295h | CCP1AS                       | 315h | CCP3AS                       | 395h | IOCBN                        |

| 016h | TMR1L                          | 096h | PCON                                       | 116h | BORCON                                     | 196h | EECON2                       | 216h | SSPCON2                      | 296h | PSTR1CON                     | 316h | PSTR3CON                     | 396h | IOCBF                        |

| 017h | TMR1H                          | 097h | WDTCON                                     | 117h | FVRCON                                     | 197h | _                            | 217h | SSPCON3                      | 297h | —                            | 317h | —                            | 397h | _                            |

| 018h | T1CON                          | 098h | OSCTUNE                                    | 118h | DACCON0                                    | 198h | —                            | 218h | _                            | 298h | CCPR2L                       | 318h | CCPR4L                       | 398h | _                            |

| 019h | T1GCON                         | 099h | OSCCON                                     | 119h | DACCON1                                    | 199h | RCREG                        | 219h | —                            | 299h | CCPR2H                       | 319h | CCPR4H                       | 399h | _                            |

| 01Ah | TMR2                           | 09Ah | OSCSTAT                                    | 11Ah | SRCON0                                     | 19Ah | TXREG                        | 21Ah | _                            | 29Ah | CCP2CON                      | 31Ah | CCP4CON                      | 39Ah |                              |

| 01Bh | PR2                            | 09Bh | ADRESL                                     | 11Bh | SRCON1                                     | 19Bh | SPBRGL                       | 21Bh | —                            | 29Bh | PWM2CON                      | 31Bh | —                            | 39Bh | _                            |

| 01Ch | T2CON                          | 09Ch | ADRESH                                     | 11Ch | —                                          | 19Ch | SPBRGH                       | 21Ch | —                            | 29Ch | CCP2AS                       | 31Ch | CCPR5L                       | 39Ch | —                            |

| 01Dh | —                              | 09Dh | ADCON0                                     | 11Dh | APFCON                                     | 19Dh | RCSTA                        | 21Dh |                              | 29Dh | PSTR2CON                     | 31Dh | CCPR5H                       | 39Dh | —                            |

| 01Eh | CPSCON0                        | 09Eh | ADCON1                                     | 11Eh | _                                          | 19Eh | TXSTA                        | 21Eh |                              | 29Eh | CCPTMRS0                     | 31Eh | CCP5CON                      | 39Eh | —                            |

| 01Fh | CPSCON1                        | 09Fh | —                                          | 11Fh | _                                          | 19Fh | BAUDCTR                      | 21Fh | —                            | 29Fh | CCPTMRS1                     | 31Fh | —                            | 39Fh |                              |

| 020h |                                | 0A0h |                                            | 120h |                                            | 1A0h |                              | 220h |                              | 2A0h |                              | 320h |                              | 3A0h |                              |

| 06Fh | General<br>Purpose<br>Register | 0EFh | General<br>Purpose<br>Register<br>80 Bytes | 16Fh | General<br>Purpose<br>Register<br>80 Bytes | 1EFh | Unimplemented<br>Read as '0' | 26Fh | Unimplemented<br>Read as '0' | 2EFh | Unimplemented<br>Read as '0' | 36Fh | Unimplemented<br>Read as '0' | 3EFh | Unimplemented<br>Read as '0' |

| 070h | 96 Bytes                       | 0F0h |                                            | 170h |                                            | 1F0h |                              | 270h |                              | 2F0h |                              | 370h |                              | 3F0h |                              |

|      |                                |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh                      |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |      | Accesses<br>70h – 7Fh        |

| 07Fh |                                | 0FFh |                                            | 17Fh |                                            | 1FFh |                              | 27Fh |                              | 2FFh |                              | 37Fh |                              | 3FFh |                              |

Legend: = Unimplemented data memory locations, read as '0'.

Note 1: Not available on PIC16(L)F1936.

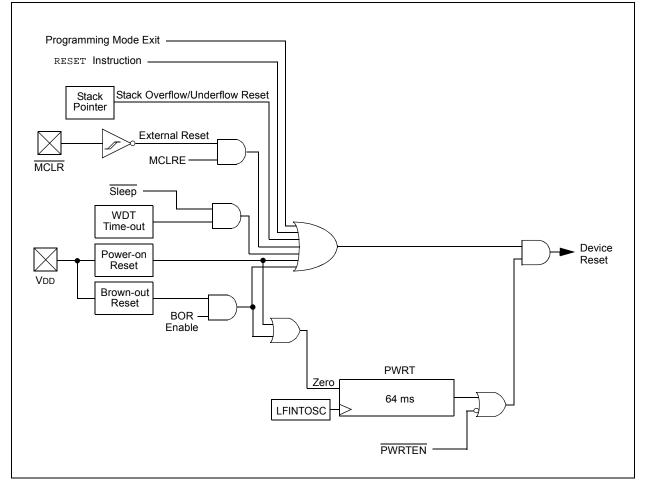

### 6.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 6-1.

#### FIGURE 6-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| FIGURE 7  | 7-2: I       | NTERRUPT      | LATENCY           |                  |       |             |             |             |

|-----------|--------------|---------------|-------------------|------------------|-------|-------------|-------------|-------------|

|           |              |               |                   |                  |       |             |             |             |

| OSC1      |              |               |                   |                  |       |             |             |             |

| CLKOUT    |              |               | Interru<br>during | pt Sampled<br>Q1 |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | PC            | PC                | +1               | 0004h | 0005h       |             |             |

| Execute   | 1 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP   | Inst(0004h) | L           |             |

|           |              |               |                   |                  |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | PC            | PC+1/FSR<br>ADDR  | New PC/<br>PC+1  | 0004h | 0005h       |             |             |

| Execute-  | 2 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP   | Inst(0004h) |             |             |

|           |              |               |                   | 1                |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             | (           |

| PC        | PC-1         | PC            | FSR ADDR          | PC+1             | PC+2  | 0004h       | 0005h       | )           |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP   | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt |              |               |                   |                  | -     |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | РС            | FSR ADDR          | PC+1             | PC    | +2          | 0004h       | 0005h       |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP   | NOP         | NOP         | Inst(0004h) |

|           |              |               |                   |                  |       |             |             |             |

| W-0/0                     | W-0/0    | W-0/0              | W-0/0 | W-0/0                                              | W-0/0            | W-0/0  | W-0/0 |  |  |  |  |

|---------------------------|----------|--------------------|-------|----------------------------------------------------|------------------|--------|-------|--|--|--|--|

| EEPROM Control Register 2 |          |                    |       |                                                    |                  |        |       |  |  |  |  |

| bit 7                     |          |                    |       | -                                                  |                  |        | bit 0 |  |  |  |  |

|                           |          |                    |       |                                                    |                  |        |       |  |  |  |  |

| Legend:                   |          |                    |       |                                                    |                  |        |       |  |  |  |  |

| R = Readable              | bit      | W = Writable       | bit   | U = Unimplen                                       | nented bit, read | as '0' |       |  |  |  |  |

| S = Bit can onl           | y be set | x = Bit is unknown |       | -n/n = Value at POR and BOR/Value at all other Res |                  |        |       |  |  |  |  |

| '1' = Bit is set          |          | '0' = Bit is clea  | ared  |                                                    |                  |        |       |  |  |  |  |

#### bit 7-0 Data EEPROM Unlock Pattern bits

To unlock writes, a 55h must be written first, followed by an AAh, before setting the WR bit of the EECON1 register. The value written to this register is used to unlock the writes. There are specific timing requirements on these writes. Refer to **Section 11.2.2** "Writing to the Data EEPROM Memory" for more information.

#### TABLE 11-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

| Name   | Bit 7                                               | Bit 6 | Bit 5  | Bit 4 | Bit 3   | Bit 2  | Bit 1 | Bit 0  | Register on<br>Page |  |

|--------|-----------------------------------------------------|-------|--------|-------|---------|--------|-------|--------|---------------------|--|

| EECON1 | EEPGD                                               | CFGS  | LWLO   | FREE  | WRERR   | WREN   | WR    | RD     | 127                 |  |

| EECON2 | EEPROM Control Register 2 (not a physical register) |       |        |       |         |        |       |        |                     |  |

| EEADRL | EEADRL<7:0>                                         |       |        |       |         |        |       |        |                     |  |

| EEADRH | EEADRH<6:0                                          |       |        |       |         |        |       |        |                     |  |

| EEDATL |                                                     |       |        | EEDAT | [L<7:0> |        |       |        | 126                 |  |

| EEDATH | _                                                   | _     |        |       | EEDAT   | H<5:0> |       |        | 126                 |  |

| INTCON | GIE                                                 | PEIE  | TMR0IE | INTE  | IOCIE   | TMR0IF | INTF  | IOCIF  | 98                  |  |

| PIE2   | OSFIE                                               | C2IE  | C1IE   | EEIE  | BCLIE   | LCDIE  | _     | CCP2IE | 100                 |  |

| PIR2   | OSFIF                                               | C2IF  | C1IF   | EEIF  | BCLIF   | LCDIF  | —     | CCP2IF | 103                 |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by the data EEPROM module.

\* Page provides register information.

| U-0              | U-0                                     | R/W-1/1           | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |

|------------------|-----------------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| —                | —                                       | ANSB5             | ANSB4   | ANSB3                                                 | ANSB2   | ANSB1   | ANSB0   |  |  |

| bit 7            |                                         |                   |         |                                                       |         |         | bit 0   |  |  |

|                  |                                         |                   |         |                                                       |         |         |         |  |  |

| Legend:          |                                         |                   |         |                                                       |         |         |         |  |  |

| R = Readable I   | bit                                     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set |                                         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |  |

#### REGISTER 12-9: ANSELB: PORTB ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSB<5:0>**: Analog Select between Analog or Digital Function on Pins RB<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### REGISTER 12-10: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| WPUB7   | WPUB6   | WPUB5   | WPUB4   | WPUB3   | WPUB2   | WPUB1   | WPUB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull-up enabled

0 = Pull-up disabled

Note 1: Global WPUEN bit of the OPTION\_REG register must be cleared for individual pull-ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

#### REGISTER 12-11: PORTC: PORTC REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u      | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|-----------------------------------------|---------|--------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| RC7                                     | RC6     | RC5          | RC4     | RC3                                                   | RC2     | RC1     | RC0     |  |  |  |

| bit 7                                   | •       | •            |         |                                                       |         | •       | bit 0   |  |  |  |

|                                         |         |              |         |                                                       |         |         |         |  |  |  |

| Legend:                                 |         |              |         |                                                       |         |         |         |  |  |  |

| R = Readable                            | bit     | W = Writable | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |         |              | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| '1' = Bit is set '0' = Bit is cleared   |         |              |         |                                                       |         |         |         |  |  |  |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits 1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 12-12: TRISC: PORTC TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2  | TRISC1  | TRISC0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISC<7:0>:** PORTC Tri-State Control bits 1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### REGISTER 12-13: LATC: PORTC DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATC7   | LATC6   | LATC5   | LATC4   | LATC3   | LATC2   | LATC1   | LATC0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATC<7:0>: PORTC Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTC are actually written to corresponding LATC register. Reads from PORTC register is return of actual I/O pin values.

### 18.2 Comparator Control

Each comparator has 2 control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 18-1) contain Control and Status bits for the following:

- Enable

- Output selection

- Output polarity

- Speed/Power selection

- · Hysteresis enable

- Output synchronization

The CMxCON1 registers (see Register 18-2) contain Control bits for the following:

- Interrupt enable

- Interrupt edge polarity

- · Positive input channel selection

- Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 18.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- · CxON bit of the CMxCON0 register must be set

| Note 1: | The CxOE bit of the CMxCON0 register   |

|---------|----------------------------------------|

|         | overrides the PORT data latch. Setting |

|         | the CxON bit of the CMxCON0 register   |

|         | has no impact on the port override.    |

2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-1 shows the output state versus input conditions, including polarity control.

#### TABLE 18-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVN > CxVP     | 0     | 0     |

| CxVN < CxVP     | 0     | 1     |

| CxVN > CxVP     | 1     | 1     |

| CxVN < CxVP     | 1     | 0     |

#### 18.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

#### 21.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

TABLE 21-4:TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                       |

|-------|--------------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                          |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)                  |

| 10    | Comparator 1 Output SYNCC1OUT<br>(optionally Timer1 synchronized output) |

| 11    | Comparator 2 Output SYNCC2OUT<br>(optionally Timer1 synchronized output) |

#### 21.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 21.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 21.6.2.3 Comparator C1 Gate Operation

The output resulting from a Comparator 1 operation can be selected as a source for Timer1 gate control. The Comparator 1 output (SYNCC1OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 18.4.1 "Comparator Output Synchronization**".

#### 21.6.2.4 Comparator C2 Gate Operation

The output resulting from a Comparator 2 operation can be selected as a source for Timer1 gate control. The Comparator 2 output (SYNCC2OUT) can be synchronized to the Timer1 clock or left asynchronous. For more information see **Section 18.4.1 "Comparator Output Synchronization"**.

#### 21.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 21-4 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

| Note: | Enabling Toggle mode at the same time       |  |

|-------|---------------------------------------------|--|

|       | as changing the gate polarity may result in |  |

|       | indeterminate operation.                    |  |

#### 21.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software. See Figure 21-5 for timing details.

If the Single Pulse Gate mode is disabled by clearing the T1GSPM bit in the T1GCON register, the T1GGO/DONE bit should also be cleared.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 21-6 for timing details.

#### 21.6.5 TIMER1 GATE VALUE STATUS

When Timer1 Gate Value Status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

### 21.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 Gate Event Interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

NOTES:

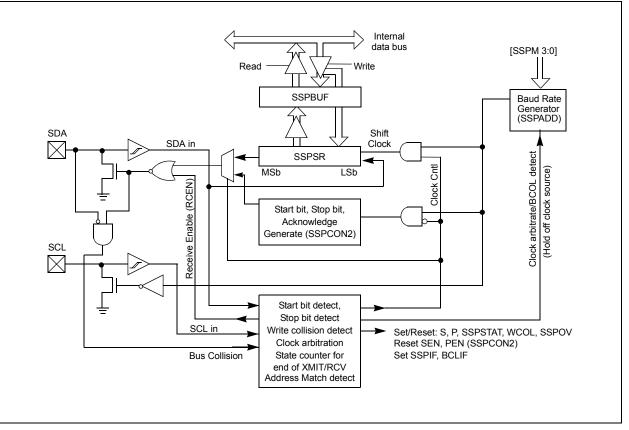

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- Clock stretching

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

Figure 24-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 24-3 is a diagram of the  $I^2C$  interface module in Slave mode.

#### FIGURE 24-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

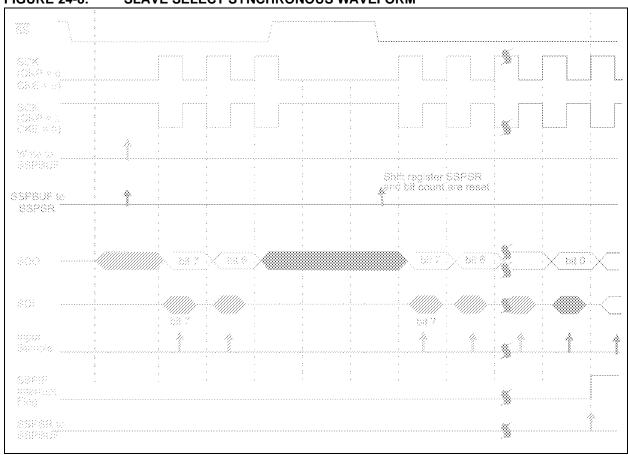

#### FIGURE 24-8: SLAVE SELECT SYNCHRONOUS WAVEFORM

| FIGURE 24-9: | SPI MODE WAVEFORM | (SLAVE MODE WITH CKE = 0) |  |

|--------------|-------------------|---------------------------|--|

|              |                   |                           |  |

|                                                                                           |                                        | ,                |

|-------------------------------------------------------------------------------------------|----------------------------------------|------------------|

|                                                                                           |                                        | (<br>(<br>(      |

|                                                                                           |                                        | (<br>(<br>       |

| - SOX<br>- CNS <sup>(2)</sup> + 1<br>- CNS <sup>(2)</sup> + 2<br>- CNS <sup>(2)</sup> + 2 |                                        |                  |

| 94/18/02<br>S-39/93/19<br>V-28/                                                           |                                        |                  |

|                                                                                           | X (68) X (60) (60)                     |                  |

|                                                                                           | all/////////////////////////////////// | :<br>;<br>;<br>; |

|                                                                                           | 4. 4.                                  |                  |

|                                                                                           |                                        |                  |

|                                                                                           |                                        |                  |

| Series Codision                                                                           | ·····                                  |                  |

#### FIGURE 24-10: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| SS<br>New Optional                 |             |                                                             |            | /        |

|------------------------------------|-------------|-------------------------------------------------------------|------------|----------|

| SCK<br>(CKP = <u>0</u><br>CKE = 1) |             | ļ                                                           |            |          |

| SCK<br>(CKP = 1<br>CKE = 1)        |             |                                                             |            |          |

| Write to<br>SSPBUF                 |             | 1 1 1<br>1 1 1<br>1 1 1<br>1 1 1<br>1 1 1<br>1 1 1<br>1 1 1 |            |          |

| SDO                                | bit 7 bit 6 | bit 5 bit 4 bit                                             |            |          |

| SDI                                | bit 7       |                                                             |            | bit 0    |

| Input<br>Sample                    | <u> </u>    | <u>↑</u> ↑ ↑                                                | <u>↑</u> ↑ | <b>↑</b> |

| SSPIF<br>Interrupt<br>Flag         |             |                                                             |            |          |

| SSPSR to<br>SSPBUF                 |             | 1 1 1<br>1 1 1<br>1 1 1<br>1 1                              |            |          |

| Wite Collision                     |             |                                                             |            |          |

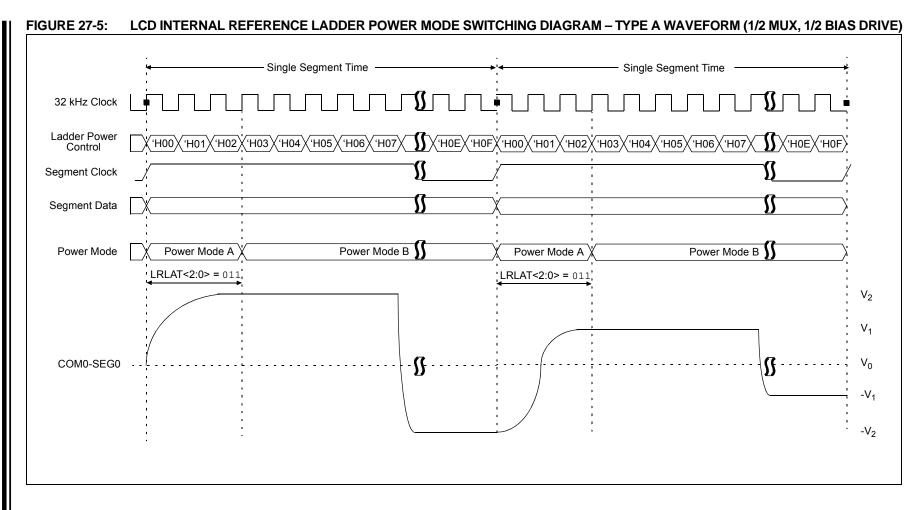

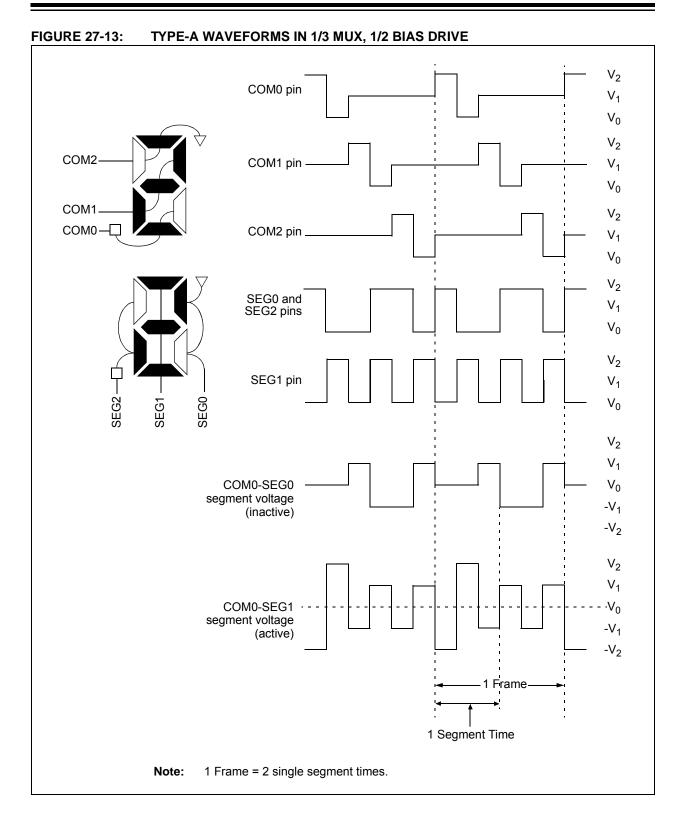

#### 27.4 LCD Bias Internal Reference Ladder

The internal reference ladder can be used to divide the LCD bias voltage two or three equally spaced voltages that will be supplied to the LCD segment pins. To create this, the reference ladder consists of three matched resistors. Refer to Figure 27-3.

#### 27.4.1 BIAS MODE INTERACTION

When in 1/2 Bias mode (BIASMD = 1), then the middle resistor of the ladder is shorted out so that only two voltages are generated. The current consumption of the ladder is higher in this mode, with the one resistor removed.

TABLE 27-3:LCD INTERNAL LADDERPOWER MODES (1/3 BIAS)

| Power<br>Mode | Nominal Resistance of<br>Entire Ladder | Nominal<br>IDD |

|---------------|----------------------------------------|----------------|

| Low           | 3 Mohm                                 | 1 µA           |

| Medium        | 300 kohm                               | 10 µA          |

| High          | 30 kohm                                | 100 µA         |

### 27.4.2 POWER MODES

The internal reference ladder may be operated in one of three power modes. This allows the user to trade off LCD contrast for power in the specific application. The larger the LCD glass, the more capacitance is present on a physical LCD segment, requiring more current to maintain the same contrast level.

Three different power modes are available, LP, MP and HP. The internal reference ladder can also be turned off for applications that wish to provide an external ladder or to minimize power consumption. Disabling the internal reference ladder results in all of the ladders being disconnected, allowing external voltages to be supplied.

Whenever the LCD module is inactive (LCDA = 0), the internal reference ladder will be turned off.

FIGURE 31-36: PIC16LF1937 EC OSCILLATOR, MEDIUM-POWER MODE, Fosc = 4 MHz

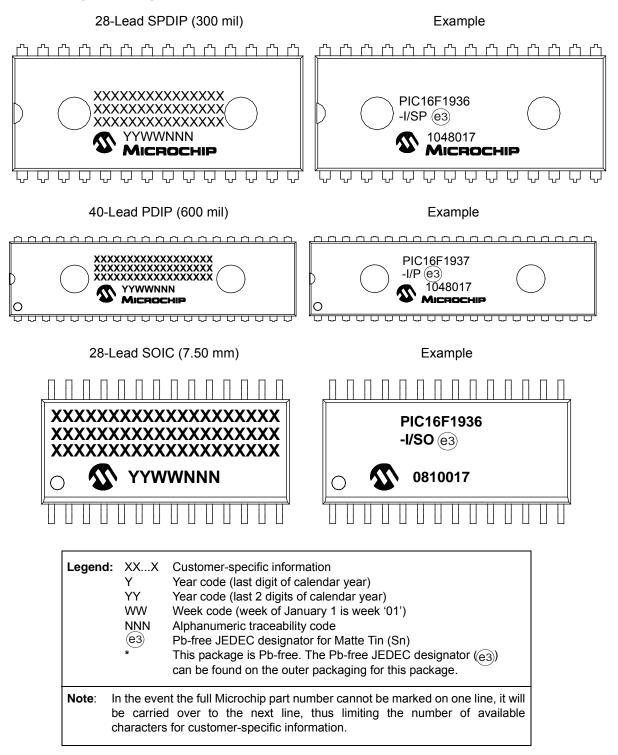

### 33.0 PACKAGING INFORMATION

#### 33.1 Package Marking Information

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

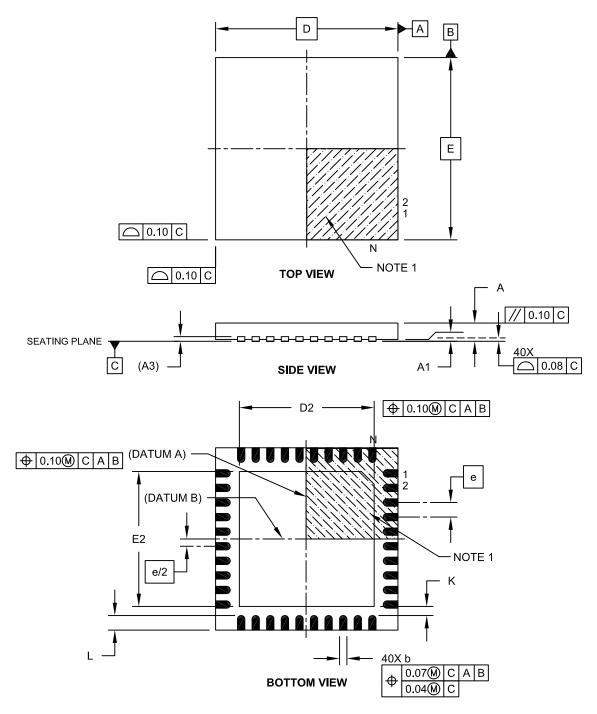

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

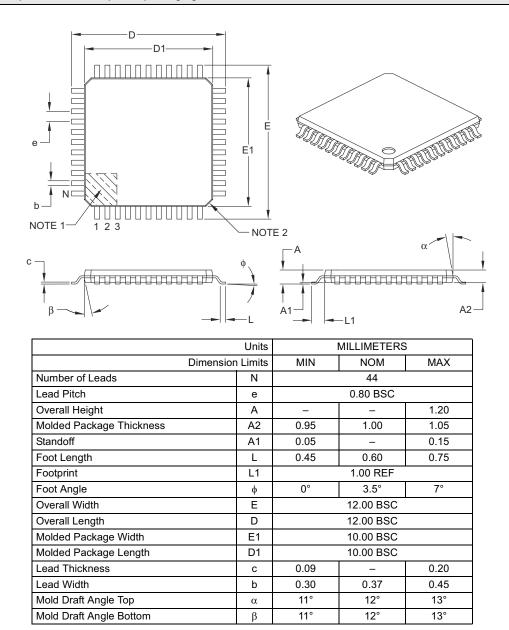

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B