#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                               |

| Number of I/O              | 36                                                                       |

| Program Memory Size        | 14KB (8K x 14)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 512 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                              |

| Data Converters            | A/D 14x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1937-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

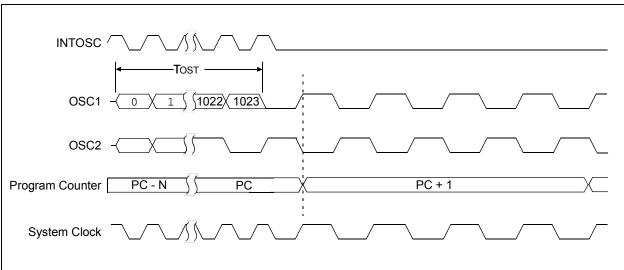

### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

# 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Word 1 configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| TABLE 5-1: OSCI | LLATOR SWITCHING DELAYS |

|-----------------|-------------------------|

|-----------------|-------------------------|

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                 |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                         |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                  |

| Sleep/POR        | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)          |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                   |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                  |

| Any clock source | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST)          |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                   |

Note 1: PLL inactive.

#### 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

| U-0              | U-0   | R/W-1/1           | R/W-1/1 | R/W-1/1        | R/W-1/1          | R/W-1/1        | R/W-1/1      |

|------------------|-------|-------------------|---------|----------------|------------------|----------------|--------------|

| —                | —     | ANSA5             | ANSA4   | ANSA3          | ANSA2            | ANSA1          | ANSA0        |

| bit 7            |       |                   |         |                |                  |                | bit 0        |

|                  |       |                   |         |                |                  |                |              |

| Legend:          |       |                   |         |                |                  |                |              |

| R = Readable     | bit   | W = Writable      | bit     | U = Unimplen   | nented bit, read | 1 as '0'       |              |

| u = Bit is uncha | anged | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared    |                |                  |                |              |

### REGISTER 12-5: ANSELA: PORTA ANALOG SELECT REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name       | Bit 7  | Bit 6   | Bit 5  | Bit 4   | Bit 3      | Bit 2    | Bit 1   | Bit 0   | Register<br>on Page |

|------------|--------|---------|--------|---------|------------|----------|---------|---------|---------------------|

| ADCON0     |        |         |        | CHS<4:0 | >          |          | GO/DONE | ADON    | 163                 |

| ANSELB     |        | —       | ANSB5  | ANSB4   | ANSB3      | ANSB2    | ANSB1   | ANSB0   | 139                 |

| APFCON     |        | CCP3SEL | T1GSEL | P2BSEL  | SRNQSEL    | C2OUTSEL | SSSEL   | CCP2SEL | 131                 |

| CCPxCON    | PxM∙   | <1:0>   | DCxB   | <1:0>   |            | CCPxM<   | 3:0>    |         | 234                 |

| CPSCON0    | CPSON  | _       | _      | —       | CPSRNG     | <1:0>    | CPSOUT  | TOXCS   | 323                 |

| CPSCON1    | _      | _       | _      | _       |            | CPSCH    | <3:>    |         | 324                 |

| INTCON     | GIE    | PEIE    | TMR0IE | INTE    | IOCIE      | TMR0IF   | INTF    | IOCIF   | 98                  |

| IOCBP      | IOCBP7 | IOCBP6  | IOCBP5 | IOCBP4  | IOCBP3     | IOCBP2   | IOCBP1  | IOCBP0  | 152                 |

| IOCBN      | IOCBN7 | IOCBN6  | IOCBN5 | IOCBN4  | IOCBN3     | IOCBN2   | IOCBN1  | IOCBN0  | 152                 |

| IOCBF      | IOCBF7 | IOCBF6  | IOCBF5 | IOCBF4  | IOCBF3     | IOCBF2   | IOCBF1  | IOCBF0  | 152                 |

| LATB       | LATB7  | LATB6   | LATB5  | LATB4   | LATB3      | LATB2    | LATB1   | LATB0   | 138                 |

| LCDCON     | LCDEN  | SLPEN   | WERR   |         | CS<1:      | 0>       | LMUX    | <1:0>   | 329                 |

| LCDSE0     | SE7    | SE6     | SE5    | SE4     | SE3        | SE2      | SE1     | SE0     | 333                 |

| LCDSE1     | SE15   | SE14    | SE13   | SE12    | SE11       | SE10     | SE9     | SE8     | 333                 |

| OPTION_REG | WPUEN  | INTEDG  | TMR0CS | TMR0SE  | PSA        |          | PS<2:0> |         | 193                 |

| PORTB      | RB7    | RB6     | RB5    | RB4     | RB3        | RB2      | RB1     | RB0     | 138                 |

| T1GCON     | TMR1GE | T1GPOL  | T1GTM  | T1GSPM  | T1GGO/DONE | T1GVAL   | T1GSS   | S<1:0>  | 204                 |

| TRISB      | TRISB7 | TRISB6  | TRISB5 | TRISB4  | TRISB3     | TRISB2   | TRISB1  | TRISB0  | 138                 |

| WPUB       | WPUB7  | WPUB6   | WPUB5  | WPUB4   | WPUB3      | WPUB2    | WPUB1   | WPUB0   | 139                 |

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

| FIGURE 21-6:           | TIMER1 GATE SINGLE                                            | -PULSE AND TOGGLE COMBINED MODE                      |

|------------------------|---------------------------------------------------------------|------------------------------------------------------|

| TMR1GE                 |                                                               |                                                      |

| T1GPOL                 |                                                               |                                                      |

| T1GSPM                 |                                                               |                                                      |

| T1GTM                  |                                                               |                                                      |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Counting enabled o<br>rising edge of T10 | Cleared by hardware on<br>falling edge of T1GVAL     |

| T1G_IN                 |                                                               |                                                      |

| Т1СКІ                  |                                                               |                                                      |

| T1GVAL                 |                                                               |                                                      |

| TIMER1                 | Ν                                                             | <u>N+1</u> <u>N+2</u> <u>N+3</u> <u>N+4</u>          |

| TMR1GIF                | - Cleared by software                                         | Set by hardware on Cleared by falling edge of T1GVAL |

|                      |          |                    |                    |                    | 520                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### **TABLE 23-9**: **EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES**

**Note 1:** PWM Steering enables outputs in Single mode.

#### EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH **FIGURE 23-6:** STATE)

| PxM<1:0>                                | Signal         | 0 Puls<br>Widt    |             | PRX+1       |

|-----------------------------------------|----------------|-------------------|-------------|-------------|

|                                         |                |                   | Period ———  | ►           |

| 00 (Single Output)                      | PxA Modulated  | Delay             | Delay       |             |

|                                         | PxA Modulated  |                   |             | ;           |

| 10 (Half-Bridge)                        | PxB Modulated  | i<br>i            | i           |             |

|                                         | PxA Active     | _ <u> </u>        |             | <br>I<br>I  |

| (Full-Bridge,<br><sup>01</sup> Forward) | PxB Inactive   | - ;               |             | 1<br>1<br>1 |

|                                         | PxC Inactive   | _ i<br>_ <u>i</u> |             |             |

|                                         | PxD Modulated  | /                 | i           |             |

|                                         | PxA Inactive   | - ;               | 1<br>1<br>1 | <br> <br>   |

| (Full-Bridge,<br>11 Reverse)            | PxB Modulated  |                   |             | <br> <br>   |

|                                         | PxC Active     |                   |             |             |

|                                         | PxD Inactive — | !                 | 1<br>1      |             |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

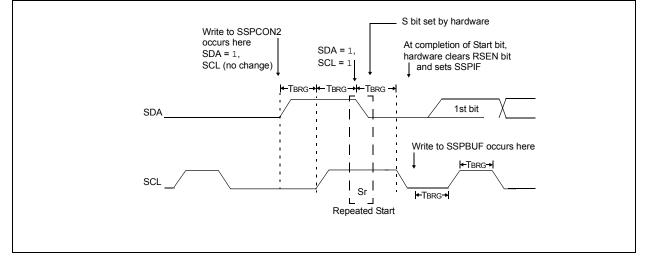

### 24.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit of the SSPCON2 register is programmed high and the Master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

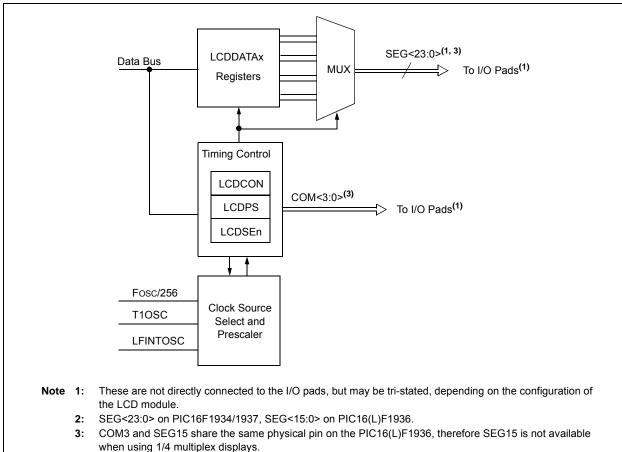

# 27.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) Driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16(L)F1934/6/7 device, the module drives the panels of up to four commons and up to 24 segments. The LCD module also provides control of the LCD pixel data.

The LCD Driver module supports:

- Direct driving of LCD panel

- Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- · Segment pins up to:

- 16 (PIC16(L)F1936)

- 24 (PIC16(L)F1934/7)

- Static, 1/2 or 1/3 LCD Bias

### FIGURE 27-1: LCD DRIVER MODULE BLOCK DIAGRAM

Note: COM3 and SEG15 share the same physical pin on the PIC16(L)F1936, therefore SEG15 is not available when using 1/4 multiplex displays.

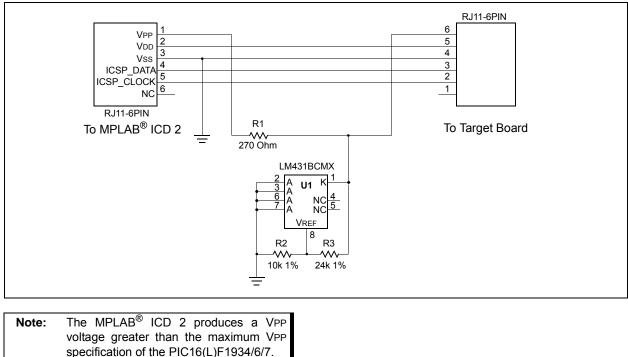

# 28.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ICSPCLK pin is the clock input. For more information on ICSP™ refer to the "*PIC16193X/PIC16LF193X Memory Programming Specification*" (DS41360).

### 28.1 High-Voltage Programming Entry Mode

The device is placed into High-Voltage Programming Entry mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP to VIHH.

Some programmers produce VPP greater than VIHH (9.0V), an external circuit is required to limit the VPP voltage. See Figure 28-1 for example circuit.

FIGURE 28-1: VPP LIMITER EXAMPLE CIRCUIT

© 2008-2011 Microchip Technology Inc.

### 29.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                           |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDFSR FSRn, k                                                                      |

| Operands:        | $-32 \le k \le 31$<br>n $\in$ [ 0, 1]                                                         |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                               |

| Status Affected: | None                                                                                          |

| Description:     | The signed 6-bit literal 'k' is added to<br>the contents of the FSRnH:FSRnL<br>register pair. |

|                  | FOR is limited to the new we oppose                                                           |

FSRn is limited to the range 0000h -FFFFh. Moving beyond these bounds will cause the FSR to wrap around.

| ANDLW            | AND literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal 'k'.<br>The result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                          |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \to (W)$                                                                                                 |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                              |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                     |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                                  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ]ASRF f{,d}                                                                                                                                                                                              |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                       |  |  |  |  |  |

| Operation:       | $(f<7>)\rightarrow dest<7>$<br>$(f<7:1>)\rightarrow dest<6:0>,$<br>$(f<0>)\rightarrow C,$                                                                                                                               |  |  |  |  |  |

| Status Affected: | C, Z                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in reg- |  |  |  |  |  |

ister 'f'.

| ► | register f | → | С |  |

|---|------------|---|---|--|

| ADDWFC           | ADD W and CARRY bit to f                                                              |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWFC f {,d}                                                        |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                     |  |  |  |  |  |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                    |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                              |  |  |  |  |  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is |  |  |  |  |  |

placed in W. If 'd' is '1', the result is placed in data memory location 'f'.

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                 |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                    |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                               |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                               |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] RETURN                                                                                                                                          |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                    |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two-cycle instruction. |  |  |  |  |  |  |

| RETLW                      | Return with literal in W                                                                                                                                                            | RLF               | Rotate Left f through Carry                                                                                                                                                                                                                                |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                    | [ <i>label</i> ] RETLW k                                                                                                                                                            | Syntax:           | [label] RLF f,d                                                                                                                                                                                                                                            |

| Operands:                  | $0 \le k \le 255$                                                                                                                                                                   | Operands:         | $0 \leq f \leq 127$                                                                                                                                                                                                                                        |

| Operation:                 | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        | Operation:        | $d \in [0,1]$<br>See description below                                                                                                                                                                                                                     |

| Status Affected:           | None                                                                                                                                                                                | Status Affected:  | С                                                                                                                                                                                                                                                          |

| Description:               | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. | Description:      | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'.                                          |

| Words:                     | 1                                                                                                                                                                                   |                   | C Register f                                                                                                                                                                                                                                               |

| Cycles:<br><u>Example:</u> | 2<br>CALL TABLE;W contains table<br>;offset value                                                                                                                                   | Words:<br>Cycles: | 1                                                                                                                                                                                                                                                          |

|                            | • ;W now has table value                                                                                                                                                            | Example:          | RLF REG1,0                                                                                                                                                                                                                                                 |

| TABLE                      | •<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>•<br>RETLW kn ; End of table                                                                          |                   | Before Instruction       REG1       =       1110       0110         C       =       0       0         After Instruction       REG1       =       1110       0110         W       =       1100       1100       0         C       =       1       1       0 |

|                            | Before Instruction<br>W = 0x07<br>After Instruction<br>W = value of k8                                                                                                              |                   |                                                                                                                                                                                                                                                            |

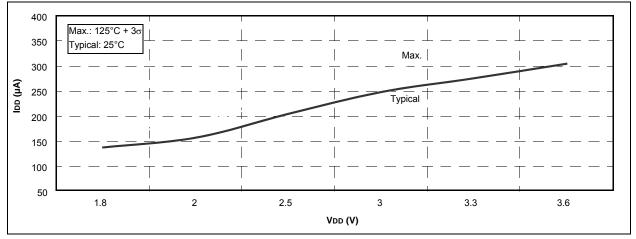

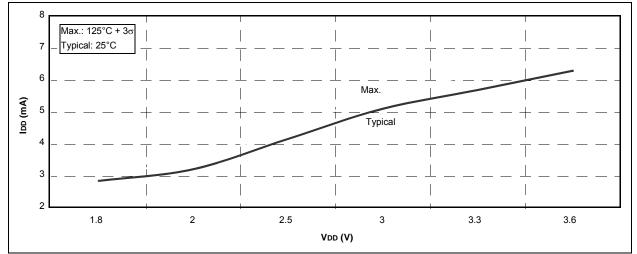

#### 30.2 DC Characteristics: PIC16(L)F1934/6/7-I/E (Industrial, Extended) (Continued)

| PIC16LF1         | 1934/36/37                          | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |      |      |       |                                                                                       |                                     |

|------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|---------------------------------------------------------------------------------------|-------------------------------------|

| PIC16F1934/36/37 |                                     |                                                                                                                                                                                                                                                              |      |      |       | l <b>ess otherwise stated)</b><br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended |                                     |

| Param            | Device                              | Min.                                                                                                                                                                                                                                                         | Тур† | Max. | Units |                                                                                       | Conditions                          |

| No.              | Characteristics                     |                                                                                                                                                                                                                                                              |      |      | •     | Vdd                                                                                   | Note                                |

| D017             | Supply Current (IDD) <sup>(1,</sup> | 2)                                                                                                                                                                                                                                                           |      |      |       |                                                                                       |                                     |

| D017             |                                     |                                                                                                                                                                                                                                                              | 110  | 180  | μA    | 1.8                                                                                   | Fosc = 500 kHz                      |

|                  |                                     | _                                                                                                                                                                                                                                                            | 140  | 250  | μA    | 3.0                                                                                   | MFINTOSC mode                       |

| D017             |                                     |                                                                                                                                                                                                                                                              | 150  | 250  | μA    | 1.8                                                                                   | Fosc = 500 kHz                      |

|                  |                                     |                                                                                                                                                                                                                                                              | 210  | 330  | μA    | 3.0                                                                                   | MFINTOSC mode (Note 5)              |

|                  |                                     | _                                                                                                                                                                                                                                                            | 270  | 430  | μΑ    | 5.0                                                                                   |                                     |

| D018             |                                     |                                                                                                                                                                                                                                                              | 1.0  | 1.4  | mA    | 1.8                                                                                   | Fosc = 8 MHz                        |

|                  |                                     | _                                                                                                                                                                                                                                                            | 1.8  | 2.3  | mA    | 3.0                                                                                   | HFINTOSC mode                       |

| D018             |                                     |                                                                                                                                                                                                                                                              | 1.0  | 1.5  | mA    | 1.8                                                                                   | Fosc = 8 MHz                        |

|                  |                                     | _                                                                                                                                                                                                                                                            | 1.8  | 2.3  | mA    | 3.0                                                                                   | HFINTOSC mode (Note 5)              |

|                  |                                     |                                                                                                                                                                                                                                                              | 2.0  | 2.8  | mA    | 5.0                                                                                   |                                     |

| D019             |                                     | _                                                                                                                                                                                                                                                            | 1.5  | 2.2  | mA    | 1.8                                                                                   | Fosc = 16 MHz                       |

|                  |                                     | —                                                                                                                                                                                                                                                            | 2.8  | 3.7  | mA    | 3.0                                                                                   | HFINTOSC mode                       |

| D019             |                                     | _                                                                                                                                                                                                                                                            | 1.7  | 2.3  | mA    | 1.8                                                                                   | Fosc = 16 MHz                       |

|                  |                                     |                                                                                                                                                                                                                                                              | 2.9  | 3.9  | mA    | 3.0                                                                                   | HFINTOSC mode (Note 5)              |

|                  |                                     | _                                                                                                                                                                                                                                                            | 3.1  | 4.1  | mA    | 5.0                                                                                   |                                     |

| D020             |                                     | _                                                                                                                                                                                                                                                            | 4.8  | 6.2  | mA    | 3.0                                                                                   | Fosc = 32 MHz<br>HFINTOSC mode      |

|                  |                                     | —                                                                                                                                                                                                                                                            | 5.0  | 7.5  | mA    | 3.6                                                                                   | HFINTOSC Mode                       |

| D020             |                                     |                                                                                                                                                                                                                                                              | 4.8  | 6.5  | mA    | 3.0                                                                                   | Fosc = 32 MHz                       |

|                  |                                     | _                                                                                                                                                                                                                                                            | 5.0  | 7.5  | mA    | 5.0                                                                                   | HFINTOSC mode                       |

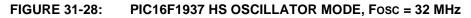

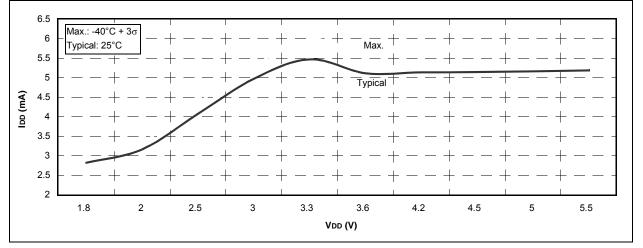

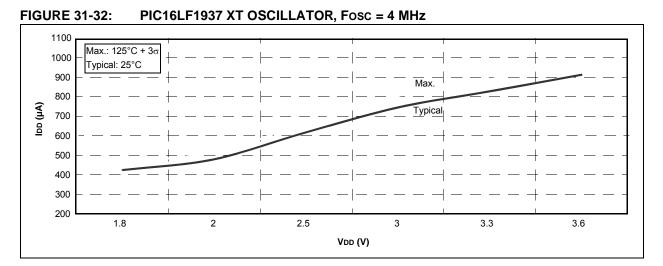

| D021             |                                     |                                                                                                                                                                                                                                                              | 410  | 550  | μA    | 1.8                                                                                   | Fosc = 4 MHz                        |

|                  |                                     |                                                                                                                                                                                                                                                              | 710  | 990  | μA    | 3.0                                                                                   | EXTRC mode (Note 3)                 |

| D021             |                                     |                                                                                                                                                                                                                                                              | 430  | 700  | μA    | 1.8                                                                                   | Fosc = 4 MHz                        |

|                  |                                     |                                                                                                                                                                                                                                                              | 730  | 1100 | μA    | 3.0                                                                                   | EXTRC mode (Note 3, Note 5)         |

|                  |                                     | _                                                                                                                                                                                                                                                            | 860  | 1400 | μA    | 5.0                                                                                   |                                     |

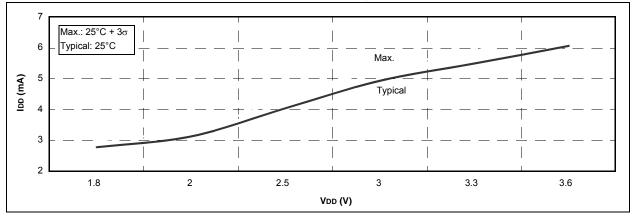

| D022             |                                     |                                                                                                                                                                                                                                                              | 5.0  | 6.2  | mA    | 3.0                                                                                   | Fosc = 32 MHz                       |

|                  |                                     | —                                                                                                                                                                                                                                                            | 6.0  | 7.5  | mA    | 3.6                                                                                   | HS Oscillator mode (Note 6)         |

| D022             |                                     |                                                                                                                                                                                                                                                              | 5.0  | 6.5  | mA    | 3.0                                                                                   | Fosc = 32 MHz                       |

|                  |                                     | —                                                                                                                                                                                                                                                            | 5.2  | 7.5  | mA    | 5.0                                                                                   | HS Oscillator mode (Note 5, Note 6) |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: FVR and BOR are disabled.

- 5: 0.1 μF capacitor on VCAP (RA0).

6: 8 MHz crystal oscillator with 4x PLL enabled.

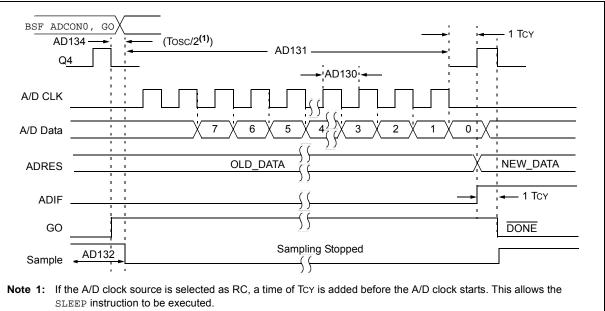

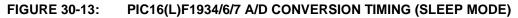

**Note 1:** If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Param.<br>No. | Symbol                              | Characte             | Min.         | Max.       | Units | Conditions |                                             |

|---------------|-------------------------------------|----------------------|--------------|------------|-------|------------|---------------------------------------------|

| SP100*        | Тнідн                               | Clock high time      | 100 kHz mode | 4.0        |       | μS         | Device must operate at a minimum of 1.5 MHz |

|               |                                     |                      | 400 kHz mode | 0.6        |       | μS         | Device must operate at a minimum of 10 MHz  |

|               |                                     |                      | SSP module   | 1.5Tcy     |       |            |                                             |

| SP101*        | TLOW                                | Clock low time       | 100 kHz mode | 4.7        |       | μS         | Device must operate at a minimum of 1.5 MHz |

|               |                                     |                      | 400 kHz mode | 1.3        |       | μS         | Device must operate at a minimum of 10 MHz  |

|               |                                     |                      | SSP module   | 1.5TCY     | _     |            |                                             |

| SP102*        | TR                                  | SDA and SCL rise     | 100 kHz mode | _          | 1000  | ns         |                                             |

|               |                                     | time                 | 400 kHz mode | 20 + 0.1Св | 300   | ns         | CB is specified to be from 10-400 pF        |

| SP103*        | TF                                  | SDA and SCL fall     | 100 kHz mode | _          | 250   | ns         |                                             |

|               |                                     | time                 | 400 kHz mode | 20 + 0.1Св | 250   | ns         | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT                             | Data input hold time | 100 kHz mode | 0          | _     | ns         |                                             |

|               |                                     |                      | 400 kHz mode | 0          | 0.9   | μS         |                                             |

| SP107*        | TSU:DAT                             | Data input setup     | 100 kHz mode | 250        | _     | ns         | (Note 2)                                    |

|               |                                     | time                 | 400 kHz mode | 100        | _     | ns         |                                             |

| SP109*        | TAA         Output valid from clock |                      | 100 kHz mode | —          | 3500  | ns         | (Note 1)                                    |

|               |                                     |                      | 400 kHz mode | —          | _     | ns         |                                             |

| SP110*        | SP110* TBUF Bus free time           |                      | 100 kHz mode | 4.7        | _     | μS         | Time the bus must be free                   |

|               |                                     |                      | 400 kHz mode | 1.3        |       | μS         | before a new transmission can start         |

| SP111         | 1 CB Bus capacitive loading         |                      |              | _          | 400   | pF         |                                             |

### TABLE 30-16: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C<sup>™</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement Tsu:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + Tsu:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.

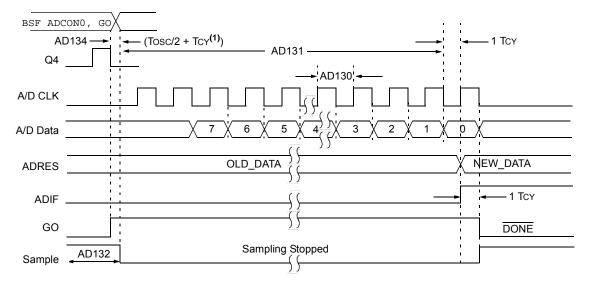

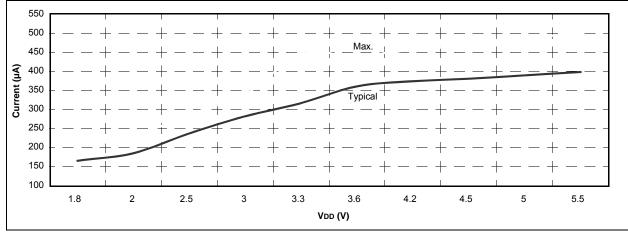

FIGURE 31-27: PIC16LF1937 HS OSCILLATOR MODE, Fosc = 32 MHz

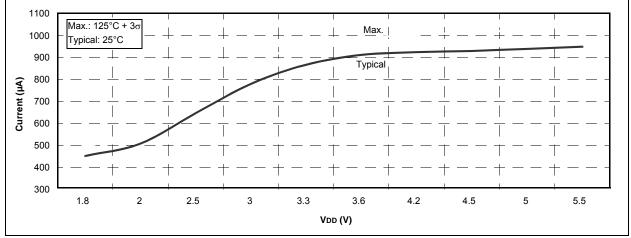

FIGURE 31-34: PIC16LF1937 EC OSCILLATOR, HIGH-POWER MODE, Fosc = 32 MHz

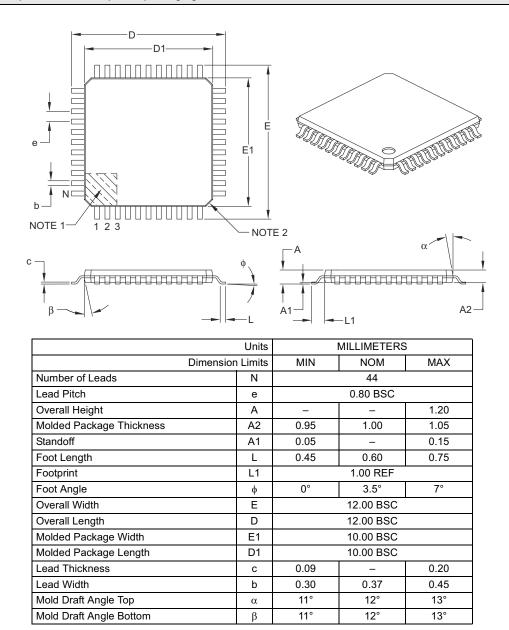

#### 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

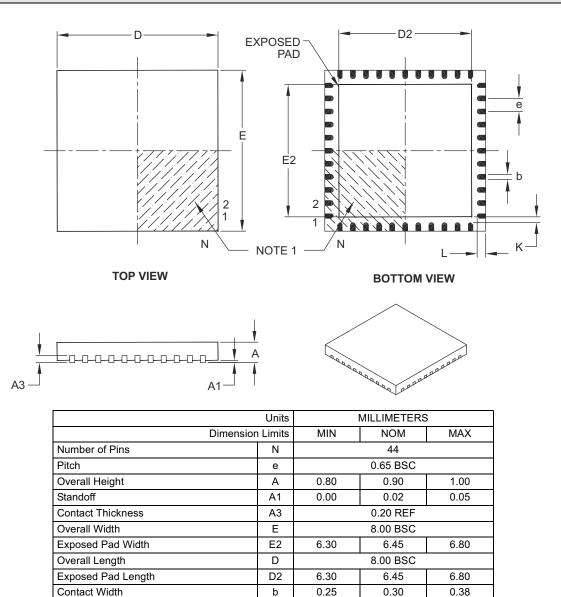

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

L

Κ

0.30

0.20

0.40

\_

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

Contact Length

Contact-to-Exposed Pad

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

0.50

\_

NOTES: