Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

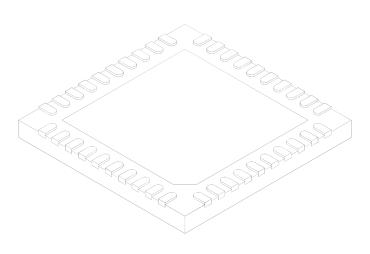

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1937-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-11:PIC16(L)F1934/6/7 MEMORYMAP, BANK 31

|      |      | Bank 31                      |                        |

|------|------|------------------------------|------------------------|

|      | F8Ch |                              |                        |

|      |      | Unimplemented<br>Read as '0' |                        |

|      | FE3h |                              |                        |

|      | FE4h | STATUS_SHAD                  |                        |

|      | FE5h | WREG_SHAD                    |                        |

|      | FE6h | BSR_SHAD                     |                        |

|      | FE7h | PCLATH_SHAD                  |                        |

|      | FE8h | FSR0L_SHAD                   |                        |

|      | FE9h | FSR0H_SHAD                   |                        |

|      | FEAh | FSR1L_SHAD                   |                        |

|      | FEBh | FSR1H_SHAD                   |                        |

|      | FECh | —                            |                        |

|      | FEDh | STKPTR                       |                        |

|      | FEEh | TOSL                         |                        |

|      | FEFh | TOSH                         |                        |

| Lege |      | = Unimplemented data<br>'0'. | memory locations, read |

## 3.2.6 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device            | Bank(s) | Page No. |

|-------------------|---------|----------|

|                   | 0       | 39       |

|                   | 1       | 40       |

|                   | 2       | 41       |

|                   | 3       | 42       |

|                   | 4       | 43       |

|                   | 5       | 44       |

| PIC16(L)F1934/6/7 | 6       | 45       |

|                   | 7       | 46       |

|                   | 8       | 47       |

|                   | 9-14    | 48       |

|                   | 15      | 49       |

|                   | 16-30   | 51       |

|                   | 31      | 52       |

# PIC16(L)F1934/6/7

| Address                | Name    | Bit 7                      | Bit 6                         | Bit 5           | Bit 4          | Bit 3          | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|----------------------------|-------------------------------|-----------------|----------------|----------------|----------------------|----------------------|----------------------|----------------------|---------------------------------|

| Bank 2                 |         |                            |                               |                 |                |                |                      |                      |                      |                      |                                 |

| 100h <sup>(2)</sup>    | INDF0   | Addressing<br>(not a physi |                               | ses contents o  | of FSR0H/FSF   | R0L to address | data memory          | /                    |                      | XXXX XXXX            | XXXX XXXX                       |

| 101h <sup>(2)</sup>    | INDF1   |                            | this location u cal register) | ses contents o  | of FSR1H/FSF   | R1L to address | data memory          | /                    |                      | XXXX XXXX            | XXXX XXXX                       |

| 102h <sup>(2)</sup>    | PCL     | Program Co                 | ounter (PC) Le                | ast Significant | t Byte         |                |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 103h <sup>(2)</sup>    | STATUS  | _                          | _                             | _               | TO             | PD             | Z                    | DC                   | С                    | 1 1000               | q quuu                          |

| 104h <sup>(2)</sup>    | FSR0L   | Indirect Data              | a Memory Add                  | Iress 0 Low Po  | ointer         |                | •                    | •                    | •                    | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(2)</sup>    | FSR0H   | Indirect Data              | a Memory Add                  | lress 0 High P  | ointer         |                |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 106h <sup>(2)</sup>    | FSR1L   | Indirect Dat               | a Memory Add                  | Iress 1 Low Po  | ointer         |                |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(2)</sup>    | FSR1H   | Indirect Data              | a Memory Add                  | lress 1 High P  | ointer         |                |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 108h <sup>(2)</sup>    | BSR     | _                          | —                             | —               |                | E              | BSR<4:0>             |                      |                      | 0 0000               | 0 0000                          |

| 109h <sup>(2)</sup>    | WREG    | Working Re                 | gister                        |                 |                |                |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 10Ah <sup>(1, 2)</sup> | PCLATH  | _                          | Write Buffer f                | or the upper 7  | bits of the Pr | ogram Counter  | r                    |                      |                      | -000 0000            | -000 0000                       |

| 10Bh <sup>(2)</sup>    | INTCON  | GIE                        | PEIE                          | TMR0IE          | INTE           | IOCIE          | TMR0IF               | INTF                 | IOCIF                | 0000 0000            | 0000 0000                       |

| 10Ch                   | LATA    | PORTA Dat                  | a Latch                       |                 |                |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 10Dh                   | LATB    | PORTB Dat                  | a Latch                       |                 |                |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 10Eh                   | LATC    | PORTC Dat                  | ta Latch                      |                 |                |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 10Fh <sup>(3)</sup>    | LATD    | PORTD Dat                  | ta Latch                      |                 |                |                |                      |                      |                      | xxxx xxxx            | uuuu uuuu                       |

| 110h                   | LATE    | _                          | —                             | —               |                | _              | LATE2 <sup>(3)</sup> | LATE1 <sup>(3)</sup> | LATE0 <sup>(3)</sup> | xxx                  | uuu                             |

| 111h                   | CM1CON0 | C10N                       | C10UT                         | C10E            | C1POL          | _              | C1SP                 | C1HYS                | C1SYNC               | 0000 -100            | 0000 -100                       |

| 112h                   | CM1CON1 | C1INTP                     | C1INTN                        | C1PCH1          | C1PCH0         | _              | _                    | C1NCI                | H<1:0>               | 000000               | 000000                          |

| 113h                   | CM2CON0 | C2ON                       | C2OUT                         | C2OE            | C2POL          | _              | C2SP                 | C2HYS                | C2SYNC               | 0000 -100            | 0000 -100                       |

| 114h                   | CM2CON1 | C2INTP                     | C2INTN                        | C2PCH1          | C2PCH0         | _              | _                    | C2NCI                | H<1:0>               | 000000               | 000000                          |

| 115h                   | CMOUT   | _                          | _                             | _               |                | _              | _                    | MC2OUT               | MC10UT               | 00                   | 00                              |

| 116h                   | BORCON  | SBOREN                     | _                             | _               | _              | _              | _                    | —                    | BORRDY               | 1 q                  | uu                              |

| 117h                   | FVRCON  | FVREN                      | FVRRDY                        | TSEN            | TSRNG          | CDAFVR1        | CDAFVR0              | ADFVI                | R<1:0>               | 0q00 0000            | 0q00 0000                       |

| 118h                   | DACCON0 | DACEN                      | DACLPS                        | DACOE           |                | DACPS          | S<1:0>               |                      | DACNSS               | 000- 00-0            | 000- 00-0                       |

| 119h                   | DACCON1 |                            |                               |                 |                | D              | ACR<4:0>             |                      | -                    | 0 0000               | 0 0000                          |

| 11Ah                   | SRCON0  | SRLEN                      | SRCLK2                        | SRCLK1          | SRCLK0         | SRQEN          | SRNQEN               | SRPS                 | SRPR                 | 0000 0000            | 0000 0000                       |

| 11Bh                   | SRCON1  | SRSPE                      | SRSCKE                        | SRSC2E          | SRSC1E         | SRRPE          | SRRCKE               | SRRC2E               | SRRC1E               | 0000 0000            | 0000 0000                       |

| 11Ch                   | —       | Unimpleme                  | nted                          |                 |                |                |                      |                      |                      | —                    | —                               |

| 11Dh                   | APFCON  | _                          | CCP3SEL                       | T1GSEL          | P2BSEL         | SRNQSEL        | C2OUTSEL             | SSSEL                | CCP2SEL              | -000 0000            | -000 0000                       |

| 11Eh                   | —       | Unimpleme                  | nted                          |                 | •              |                |                      | •                    |                      | _                    | _                               |

| 11Fh                   |         | Unimpleme                  | nted                          |                 |                |                |                      |                      |                      | _                    | _                               |

#### **TABLE 3-12:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

### 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained internally within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Word 1 to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 Oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 5.3 "Clock Switching" for more information.

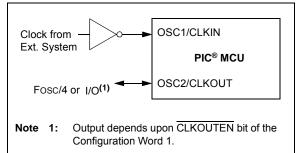

### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has 3 power modes to select from through Configuration Word 1:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

FIGURE 5-2:

### EXTERNAL CLOCK (EC) MODE OPERATION

### 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Word 1 must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Word 1 (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Word 2 must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Word 2, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

### 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables in the applicable Electrical Specifications Chapter.

# PIC16(L)F1934/6/7

| FIGURE 5-7:              | INTERNAL OSCILLATOR SWITCH TIMING                                  |

|--------------------------|--------------------------------------------------------------------|

| HEINTOSC/                | SINTOSC (SOCH and WOY (Exabled)<br><br>Otartup TimeCoycle Oycc<br> |

| IRCF <3:0>               | $\neq 0$ $\chi = 0$                                                |

| System Clock             |                                                                    |

| NENNIOSCI L<br>MENIIOSC  | FINTOSC (Either FSCM of WDT snabled)                               |

| HFINTOSC/<br>MEINTOSC    | 2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-                             |

| LFINTOSC -               |                                                                    |

| IRCF <3:0>               | $\neq 0$ $X = 0$                                                   |

| System Clock             |                                                                    |

| LEINTOSO F<br>LEINTOSO - | IFINTOSC/MFINTOSC                                                  |

| BEENTOSC/<br>MENTOSC     |                                                                    |

| \$PCF <3:0>              | • 6 X # 0                                                          |

| System Crock             |                                                                    |

| U-0              | U-0         | R/W-0/0           | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|-------------|-------------------|-----------------|------------------|------------------|----------------|--------------|

| _                | _           |                   |                 | TUN              | <5:0>            |                |              |

| bit 7            |             |                   |                 |                  |                  |                | bit 0        |

|                  |             |                   |                 |                  |                  |                |              |

| Legend:          |             |                   |                 |                  |                  |                |              |

| R = Readable     | bit         | W = Writable      | bit             | U = Unimplen     | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged       | x = Bit is unkr   | nown            | -n/n = Value a   | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |             | '0' = Bit is clea | ared            |                  |                  |                |              |

|                  |             |                   |                 |                  |                  |                |              |

| bit 7-6          | Unimpleme   | nted: Read as '   | 0'              |                  |                  |                |              |

| bit 5-0          | TUN<4:0>: F | Frequency Tunir   | ng bits         |                  |                  |                |              |

|                  |             | laximum freque    | ncy             |                  |                  |                |              |

|                  | 011110 =    |                   |                 |                  |                  |                |              |

|                  | •           |                   |                 |                  |                  |                |              |

|                  | •           |                   |                 |                  |                  |                |              |

|                  | 000001 =    |                   |                 |                  |                  |                |              |

|                  | 000000 = C  | scillator module  | e is running at | the factory-cali | brated frequen   | cy.            |              |

|                  | 111111 =    |                   |                 |                  |                  |                |              |

|                  | •           |                   |                 |                  |                  |                |              |

|                  | •           |                   |                 |                  |                  |                |              |

|                  | 100000 = N  | linimum frequer   | псу             |                  |                  |                |              |

#### **REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER**

| TABLE 5-2: | SUM | IARY OF | REGISTEI | RS ASSO | CIATED WI |  | ES |

|------------|-----|---------|----------|---------|-----------|--|----|

|            |     |         |          |         |           |  |    |

| Name    | Bit 7  | Bit 6  | Bit 5 | Bit 4    | Bit 3   | Bit 2  | Bit 1  | Bit 0                 | Register<br>on Page |

|---------|--------|--------|-------|----------|---------|--------|--------|-----------------------|---------------------|

| OSCCON  | SPLLEN |        | IRCF  | -<3:0>   |         |        | SCS    | <1:0>                 | 81                  |

| OSCSTAT | T1OSCR | PLLR   | OSTS  | HFIOFR   | HFIOFL  | MFIOFR | LFIOFR | HFIOFS                | 82                  |

| OSCTUNE | _      |        |       | TUN<5:0> |         |        |        |                       | 83                  |

| PIE2    | OSFIE  | C2IE   | C1IE  | EEIE     | BCLIE   | LCDIE  | _      | CCP2IE <sup>(1)</sup> | 100                 |

| PIR2    | OSFIF  | C2IF   | C1IF  | EEIF     | BCLIF   | LCDIF  | _      | CCP2IF <sup>(1)</sup> | 103                 |

| T1CON   | TMR1C  | S<1:0> | T1CKP | S<1:0>   | T1OSCEN | T1SYNC | _      | TMR10N                | 203                 |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F1934 only.

#### **TABLE 5-3**: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4              | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------------------|----------|----------|-----------|---------|---------------------|

|         | 13:8 | _       |         | FCMEN    | IESO                  | CLKOUTEN | BOREI    | N<1:0>    | CPD     | 00                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDTE                  | =<1:0>   |          | FOSC<2:0> |         | 62                  |

|         | 13:8 | _       | _       | LVP      | DEBUG                 | _        | BORV     | STVREN    | PLLEN   |                     |

| CONFIG2 | 7:0  | _       | _       | VCAPEN   | I<1:0> <sup>(1)</sup> | _        | _        | WRT       | <1:0>   | 64                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F1934/6/7 only.

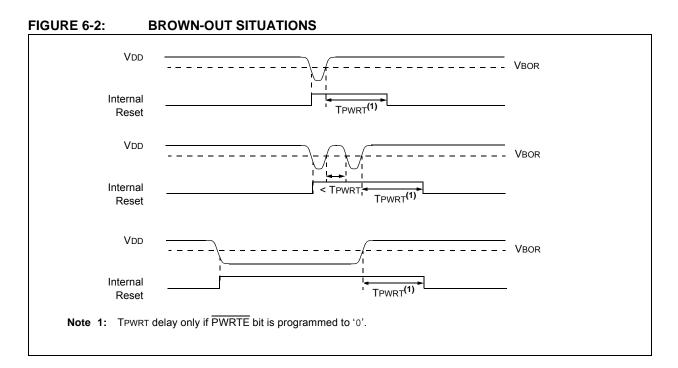

### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN  | —   | —   | _   | —   | —   | —   | BORRDY |

| bit 7   | -   |     |     |     |     |     | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | <pre>SBOREN: Software Brown-out Reset Enable bit If BOREN &lt;1:0&gt; in Configuration Word 1 ≠ 01: SBOREN is read/write, but has no effect on the BOR. If BOREN &lt;1:0&gt; in Configuration Word 1 = 01: 1 = BOR Enabled 0 = BOR Disabled</pre> |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-1 | Unimplemented: Read as '0'                                                                                                                                                                                                                        |

| bit 0   | BORRDY: Brown-out Reset Circuit Ready Status bit<br>1 = The Brown-out Reset circuit is active<br>0 = The Brown-out Reset circuit is inactive                                                                                                      |

### 9.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- 9. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to **Section 6.10** "**Determining the Cause of a Reset**".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### 11.3.2 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the EEADRH:EEADRL register pair with the address of new row to be erased.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD, FREE, and WREN bits of the EECON1 register.

- 4. Write 55h, then AAh, to EECON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the EECON1 register to begin the erase operation.

- 6. Poll the FREE bit in the EECON1 register to determine when the row erase has completed.

See Example 11-4.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

## 11.3.3 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the starting address of the word(s) to be programmed.

- 2. Load the write latches with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 11-2 (block writes to program memory with 8 write latches) for more details. The write latches are aligned to the address boundary defined by EEADRL as shown in Table 11-1. Write operations do not cross these boundaries. At the completion of a program memory write operation, the write latches are reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a block of program memory. These steps are divided into two parts. First, all write latches are loaded with data except for the last program memory location. Then, the last write latch is loaded and the programming sequence is initiated. A special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. This unlock sequence should not be interrupted.

- 1. Set the EEPGD and WREN bits of the EECON1 register.

- 2. Clear the CFGS bit of the EECON1 register.

- Set the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the EEADRH:EEADRL register pair with the address of the location to be written.

- 5. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The write latch is now loaded.

- 7. Increment the EEADRH:EEADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- 11. Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The entire latch block is now written to Flash program memory.

It is not necessary to load the entire write latch block with user program data. However, the entire write latch block will be written to program memory.

An example of the complete write sequence for eight words is shown in Example 11-5. The initial address is loaded into the EEADRH:EEADRL register pair; the eight words of data are loaded using indirect addressing.

Note: The code sequence provided in Example 11-5 must be repeated multiple times to fully program an erased program memory row.

### 11.6 Write Verify

Depending on the application, good programming practice may dictate that the value written to the data EEPROM or program memory should be verified (see Example 11-6) to the desired value to be written. Example 11-6 shows how to verify a write to EEPROM.

### EXAMPLE 11-6: EEPROM WRITE VERIFY

| BANKSEI | L EEDATL |    | ;                    |

|---------|----------|----|----------------------|

| MOVF    | EEDATL,  | W  | ;EEDATL not changed  |

|         |          |    | ;from previous write |

| BSF     | EECON1,  | RD | ;YES, Read the       |

|         |          |    | ;value written       |

| XORWF   | EEDATL,  | W  | ;                    |

| BTFSS   | STATUS,  | Ζ  | ;Is data the same    |

| GOTO    | WRITE_ER | R  | ;No, handle error    |

| :       |          |    | ;Yes, continue       |

| 1       |          |    |                      |

# PIC16(L)F1934/6/7

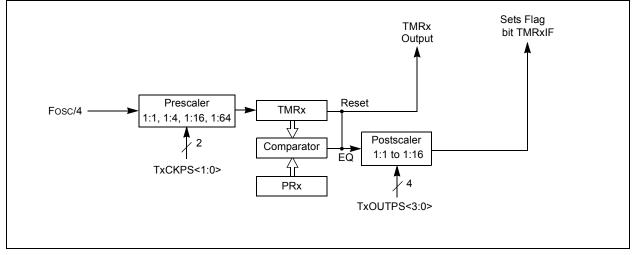

### 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is<br>used to designate Timer2, Timer4, or<br>Timer6. For example, TxCON references<br>T2CON, T4CON, or T6CON. PRx refer- |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                 |

|       | ences PR2, PR4, or PR6.                                                                                                                                         |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSP modules (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

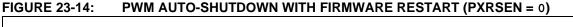

### 23.4.3 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the CCPxAS<2:0> bits of the CCPxAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- A logic '1' on a Comparator (Cx) output

A shutdown condition is indicated by the CCPxASE (Auto-Shutdown Event Status) bit of the CCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The CCPxASE bit is set to '1'. The CCPxASE will remain set until cleared in firmware or an auto-restart occurs (see Section 23.4.4 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the CCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

- Note 1: The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.

- Writing to the CCPxASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart) the PWM signal will always restart at the beginning of the next PWM period.

- 4: Prior to an auto-shutdown event caused by a comparator output or INT pin event, a software shutdown can be triggered in firmware by setting the CCPxASE bit of the CCPxAS register to '1'. The Auto-Restart feature tracks the active status of a shutdown caused by a comparator output or INT pin event only. If it is enabled at this time, it will immediately clear this bit and restart the ECCP module at the beginning of the next PWM period.

# PIC16(L)F1934/6/7

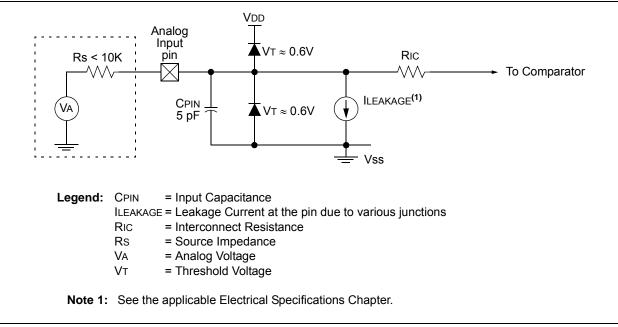

### 26.1 Analog MUX

The CPS module can monitor up to 16 inputs. The capacitive sensing inputs are defined as CPS<15:0>. To determine if a frequency change has occurred the user must:

- Select the appropriate CPS pin by setting the CPSCH<3:0> bits of the CPSCON1 register.

- Set the corresponding ANSEL bit.

- Set the corresponding TRIS bit.

- Run the software algorithm.

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

### 26.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSOUT bit of the CPSCON0 register shows the status of the capacitive sensing oscillator, whether it is a sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either Timer0 or Timer1. The oscillator has three different current settings as defined by CPSRNG<1:0> of the CPSCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed time base.

- Maximize the count differential in the timer during a change in frequency.

### 26.3 Voltage References

The capacitive sensing oscillator uses voltage references to provide two voltage thresholds for oscillation. The upper voltage threshold is referred to as Ref+ and the lower voltage threshold is referred to as Ref-.

The Vss voltage determines the lower threshold level (Ref-) and the VDD voltage determines the upper threshold level (Ref+).

### 26.4 Power Ranges

The capacitive sensing oscillator can operate in one of three different power modes.

There are three distinct power ranges; low, medium and high. Current consumption is dependent upon the range selected. See Table 26-1 for proper power range selection.

The remaining mode is a Noise Detection mode that resides within the high range. The Noise Detection mode is unique in that it disables the sinking and sourcing of current on the analog pin but leaves the rest of the oscillator circuitry active. This reduces the oscillation frequency on the analog pin to zero and also greatly reduces the current consumed by the oscillator module.

When noise is introduced onto the pin, the oscillator is driven at the frequency determined by the noise. This produces a detectable signal at the comparator output, indicating the presence of activity on the pin.

Figure 26-2 shows a more detailed drawing of the current sources and comparators associated with the oscillator.

TABLE 26-1: POWER RANGE SELECTION

| CPSRNG<1:0> | Mode   | Nominal Current <sup>(1)</sup> |

|-------------|--------|--------------------------------|

| 00          | Off    | 0.0 μA                         |

| 01          | Low    | 0.1 μA                         |

| 10          | Medium | 1.2 μA                         |

| 11          | High   | 18 μA                          |

**Note 1:** See the applicable Electrical Specifications Chapter for more information.

| R/W-0/0                                                            | R/W-0/0                       | R/W-0/0                               | U-0            | R/W-0/0                           | R/W-0/0           | R/W-0/0           | U-0        |

|--------------------------------------------------------------------|-------------------------------|---------------------------------------|----------------|-----------------------------------|-------------------|-------------------|------------|

| LCDIRE                                                             | LCDIRS                        | LCDIRI                                | _              | VLCD3PE                           | VLCD2PE           | VLCD1PE           | _          |

| bit 7                                                              |                               |                                       |                |                                   |                   |                   | bit 0      |

|                                                                    |                               |                                       |                |                                   |                   |                   |            |

| Legend:                                                            |                               |                                       |                |                                   |                   |                   |            |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                               |                                       |                |                                   |                   |                   |            |

| u = Bit is und                                                     | •                             | x = Bit is unkr                       |                |                                   |                   | R/Value at all ot | her Resets |

| '1' = Bit is se                                                    | et                            | '0' = Bit is clea                     | ared           | C = Only clea                     | rable bit         |                   |            |

| bit 7                                                              | I CDIRE:   C                  | D Internal Refer                      | ence Enable    | • hit                             |                   |                   |            |

|                                                                    |                               |                                       |                | and connected to                  | the Internal Co   | ontrast Control o | circuit    |

|                                                                    | 0 = Internal                  | LCD Reference                         | is disabled    |                                   |                   |                   |            |

| bit 6                                                              |                               | D Internal Refer                      | ence Source    | e bit                             |                   |                   |            |

|                                                                    | If LCDIRE =                   |                                       |                |                                   | _                 |                   |            |

|                                                                    |                               |                                       |                | powered by VD<br>powered by a 3   |                   | f the FVR         |            |

|                                                                    | If LCDIRE =                   |                                       |                | , ponoloù sy a e                  |                   |                   |            |

|                                                                    | Internal LCD                  | Contrast Contro                       | ol is unconne  | ected. LCD band                   | lgap buffer is di | sabled.           |            |

| bit 5                                                              |                               | Internal Refere                       |                |                                   |                   |                   |            |

|                                                                    |                               |                                       |                | wn when the LC                    |                   |                   |            |

|                                                                    |                               |                                       |                | s in power mode<br>s the LCD Refe |                   |                   |            |

| bit 4                                                              |                               | nted: Read as '                       | •              |                                   |                   |                   |            |

| bit 3                                                              | VLCD3PE: V                    | LCD3 Pin Enab                         | ole bit        |                                   |                   |                   |            |

|                                                                    | 1 = The VLC                   | D3 pin is conne                       | ected to the i | nternal bias volt                 | age LCDBIAS3      | (1)               |            |

|                                                                    |                               | CD3 pin is not co                     |                |                                   |                   |                   |            |

| bit 2                                                              | VLCD2PE: VLCD2 Pin Enable bit |                                       |                |                                   |                   |                   |            |

|                                                                    |                               | CD2 pin is conne<br>CD2 pin is not co |                | nternal bias volt                 | age LCDBIAS2      | (1)               |            |

| bit 1                                                              | VLCD1PE: VLCD1 Pin Enable bit |                                       |                |                                   |                   |                   |            |

|                                                                    |                               |                                       |                | nternal bias volt                 | age LCDBIAS1      | (1)               |            |

|                                                                    |                               | D1 pin is not co                      |                |                                   | 0                 |                   |            |

| bit 0                                                              | Unimplemer                    | nted: Read as '                       | )'             |                                   |                   |                   |            |

|                                                                    | la una al usia, a a ustua     |                                       |                |                                   |                   |                   |            |

### REGISTER 27-3: LCDREF: LCD REFERENCE VOLTAGE CONTROL REGISTER

Note 1: Normal pin controls of TRISx and ANSELx are unaffected.

### REGISTER 27-4: LCDCST: LCD CONTRAST CONTROL REGISTER

| U-0         U-0         U-0         U-0         R/W-0/0         R/W-0/0           -         -         -         -         LCDCST<2:0>         bit 7         bit 0 | P = Poodoblo bi | +   | M = M/ritabla | hit | II – Unimplor | monted bit read | 0,          |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|---------------|-----|---------------|-----------------|-------------|---------|

| LCDCST<2:0>                                                                                                                                                       | Legend:         |     |               |     |               |                 |             |         |

| LCDCST<2:0>                                                                                                                                                       | DIL 7           |     |               |     |               |                 |             |         |

|                                                                                                                                                                   | h:t 7           |     |               |     |               |                 |             | h:+ 0   |

| U-0 U-0 U-0 U-0 U-0 R/W-0/0 R/W-0/0 R/W-0/0                                                                                                                       | _               | _   | _             | _   | _             |                 | LCDCST<2:0> |         |

|                                                                                                                                                                   | U-0             | U-0 | U-0           | U-0 | U-0           | R/W-0/0         | R/W-0/0     | R/W-0/0 |

| R = Readable bit     | VV = VVritable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | C = Only clearable bit                                |

### bit 7-3 Unimplemented: Read as '0'

bit 2-0 LCDCST<2:0>: LCD Contrast Control bits

Selects the resistance of the LCD contrast control resistor ladder

Bit Value = Resistor ladder

000 = Minimum Resistance (Maximum contrast). Resistor ladder is shorted.

001 = Resistor ladder is at 1/7th of maximum resistance

010 = Resistor ladder is at 2/7th of maximum resistance

011 = Resistor ladder is at 3/7th of maximum resistance

100 = Resistor ladder is at 4/7th of maximum resistance

101 = Resistor ladder is at 5/7th of maximum resistance

110 = Resistor ladder is at 6/7th of maximum resistance

111 = Resistor ladder is at maximum resistance (Minimum contrast).

### 30.3 DC Characteristics: PIC16(L)F1934/6/7-I/E (Power-Down) (Continued)

| PIC16LF1                                     | Standard Operating Cond<br>Operating temperature |      |                                                  | litions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |        |                                                                                                                                |     |                                  |  |  |

|----------------------------------------------|--------------------------------------------------|------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|--|--|

| PIC16F1934/36/37                             |                                                  |      | Standard Operating Cond<br>Operating temperature |                                                                                                                                |        | litions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |     |                                  |  |  |

| Param                                        | Device Characteristics                           | Min. | Typt Max.                                        | Max.                                                                                                                           | Units  | Conditions                                                                                                                     |     |                                  |  |  |

| No.                                          | Device onarablensitos                            |      | וקני                                             | +85°C                                                                                                                          | +125°C | Onito                                                                                                                          | VDD | Note                             |  |  |

| Power-down Base Current (IPD) <sup>(2)</sup> |                                                  |      |                                                  |                                                                                                                                |        |                                                                                                                                |     |                                  |  |  |

| D028                                         |                                                  | _    | 0.1                                              | 4.0                                                                                                                            | 8.0    | μA                                                                                                                             | 1.8 | A/D Current (Note 1, Note 3), no |  |  |

|                                              |                                                  |      | 0.1                                              | 5.0                                                                                                                            | 9.0    | μA                                                                                                                             | 3.0 | conversion in progress           |  |  |

| D028                                         |                                                  | _    | 22                                               | 56                                                                                                                             | 63     | μΑ                                                                                                                             | 1.8 | A/D Current (Note 1, Note 3), no |  |  |

|                                              |                                                  | —    | 26                                               | 58                                                                                                                             | 78     | μA                                                                                                                             | 3.0 | conversion in progress           |  |  |

|                                              |                                                  | —    | 27                                               | 61                                                                                                                             | 88     | μA                                                                                                                             | 5.0 |                                  |  |  |

| D029                                         |                                                  | _    | 250                                              | _                                                                                                                              | _      | μA                                                                                                                             | 1.8 | A/D Current (Note 1, Note 3),    |  |  |

|                                              |                                                  | _    | 250                                              | —                                                                                                                              | —      | μA                                                                                                                             | 3.0 | conversion in progress           |  |  |

| D029                                         |                                                  | _    | 280                                              | _                                                                                                                              | _      | μΑ                                                                                                                             | 1.8 | A/D Current (Note 1, Note 3,     |  |  |

|                                              |                                                  | _    | 280                                              | _                                                                                                                              | _      | μA                                                                                                                             | 3.0 | Note 4), conversion in progress  |  |  |

|                                              |                                                  |      | 280                                              | _                                                                                                                              |        | μA                                                                                                                             | 5.0 | ]                                |  |  |

| D030                                         |                                                  | _    | 2                                                | 7                                                                                                                              | 11     | μA                                                                                                                             | 1.8 | Cap Sense, Low-Power mode        |  |  |

|                                              |                                                  |      | 3                                                | 9                                                                                                                              | 13     | μA                                                                                                                             | 3.0 |                                  |  |  |

| D030                                         |                                                  | —    | 21                                               | 61                                                                                                                             | 63     | μA                                                                                                                             | 1.8 | Cap Sense, Low-Power mode        |  |  |

|                                              |                                                  | —    | 27                                               | 63                                                                                                                             | 78     | μA                                                                                                                             | 3.0 |                                  |  |  |

|                                              |                                                  | _    | 28                                               | 66                                                                                                                             | 88     | μA                                                                                                                             | 5.0 |                                  |  |  |

| D031                                         |                                                  | _    | 1                                                | —                                                                                                                              | —      | μA                                                                                                                             | 3.0 | LCD Bias Ladder, Low-power       |  |  |

|                                              |                                                  | —    | 10                                               | —                                                                                                                              | —      | μA                                                                                                                             | 3.0 | LCD Bias Ladder, Medium-power    |  |  |

|                                              |                                                  | —    | 75                                               | _                                                                                                                              | _      | μA                                                                                                                             | 3.0 | LCD Bias Ladder, High-power      |  |  |

| D031                                         |                                                  | —    | 1                                                | —                                                                                                                              | _      | μA                                                                                                                             | 5.0 | LCD Bias Ladder, Low-power       |  |  |

|                                              |                                                  | _    | 10                                               | —                                                                                                                              | _      | μA                                                                                                                             | 5.0 | LCD Bias Ladder, Medium-power    |  |  |

|                                              |                                                  | _    | 75                                               | _                                                                                                                              |        | μA                                                                                                                             | 5.0 | LCD Bias Ladder, High-power      |  |  |

| D032                                         |                                                  | —    | 7.6                                              | 22                                                                                                                             | 25     | μA                                                                                                                             | 1.8 | Comparator, Low-Power mode       |  |  |

|                                              |                                                  | —    | 8.0                                              | 23                                                                                                                             | 27     | μA                                                                                                                             | 3.0 |                                  |  |  |

| D032                                         |                                                  | _    | 24                                               | 65                                                                                                                             | 75     | μA                                                                                                                             | 1.8 | Comparator, Low-Power mode       |  |  |

|                                              |                                                  | _    | 26                                               | 75                                                                                                                             | 88     | μA                                                                                                                             | 3.0 |                                  |  |  |

|                                              |                                                  |      | 28                                               | 77                                                                                                                             | 97     | μA                                                                                                                             | 5.0 |                                  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: A/D oscillator source is FRC.

4: 0.1 μF capacitor on VCAP (RA0).

### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units        | MILLIMETERS    |          |      |  |

|------------------------|--------------|----------------|----------|------|--|

| Dime                   | nsion Limits | MIN            | NOM      | MAX  |  |

| Number of Pins         | N            |                | 40       |      |  |

| Pitch                  | е            |                | 0.40 BSC |      |  |

| Overall Height         | A            | 0.45           | 0.50     | 0.55 |  |

| Standoff               | A1           | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3           | 0.127 REF      |          |      |  |

| Overall Width          | E            | 5.00 BSC       |          |      |  |

| Exposed Pad Width      | E2           | 3.60 3.70 3.8  |          | 3.80 |  |

| Overall Length         | D            | 5.00 BSC       |          |      |  |

| Exposed Pad Length     | D2           | 3.60           | 3.70     | 3.80 |  |

| Contact Width          | b            | 0.15 0.20 0.25 |          |      |  |

| Contact Length         | L            | 0.30 0.40 0.50 |          |      |  |

| Contact-to-Exposed Pad | K            | 0.20           | -        | -    |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2

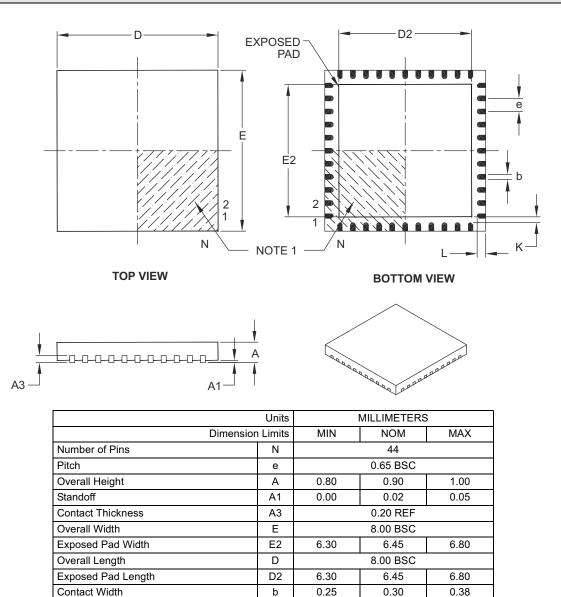

### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

L

Κ

0.30

0.20

0.40

\_

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

Contact Length

Contact-to-Exposed Pad

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

0.50

\_