Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 14KB (8K x 14)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

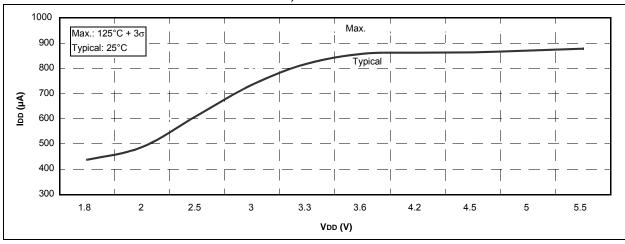

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1937-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

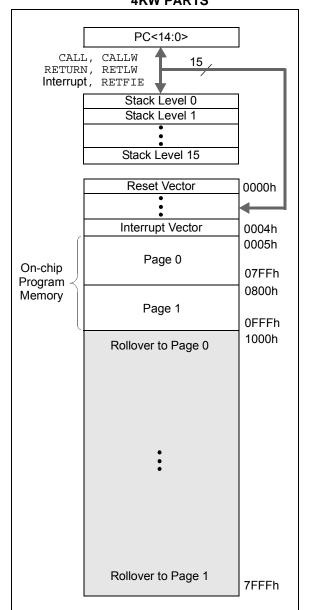

FIGURE 3-1: PROGRAM MEMORY MAP

AND STACK FOR

4KW PARTS

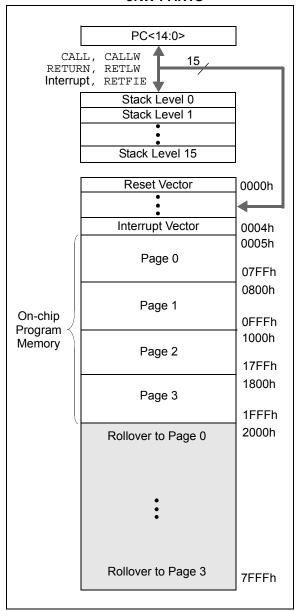

FIGURE 3-2: PROGRAM MEMORY MAP

AND STACK FOR

8KW PARTS

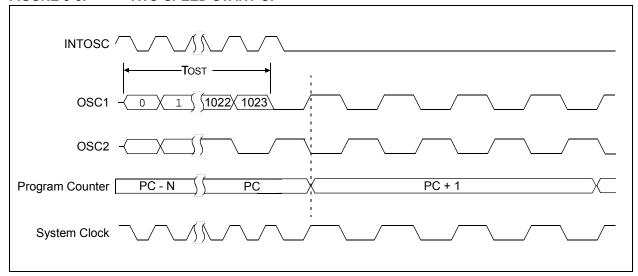

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

Note:

Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCSTAT register to remain clear.

## 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Word 1 configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- · Wake-up from Sleep.

TABLE 5-1: OSCILLATOR SWITCHING DELAYS

| ., .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | , • • •                                                                 | , , , , , , , , , , , , , , , , , , ,           |                                  |

|-----------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|

| Switch From                             | Switch To                                                               | Frequency                                       | Oscillator Delay                 |

| Sleep/POR                               | LFINTOSC <sup>(1)</sup> MFINTOSC <sup>(1)</sup> HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (TWARM) |

| Sleep/POR                               | EC, RC <sup>(1)</sup>                                                   | DC – 32 MHz                                     | 2 cycles                         |

| LFINTOSC                                | EC, RC <sup>(1)</sup>                                                   | DC – 32 MHz                                     | 1 cycle of each                  |

| Sleep/POR                               | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                          | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)          |

| Any clock source                        | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                      | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                   |

| Any clock source                        | LFINTOSC <sup>(1)</sup>                                                 | 31 kHz                                          | 1 cycle of each                  |

| Any clock source                        | Timer1 Oscillator                                                       | 32 kHz                                          | 1024 Clock Cycles (OST)          |

| PLL inactive                            | PLL active                                                              | 16-32 MHz                                       | 2 ms (approx.)                   |

Note 1: PLL inactive.

## 5.4.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- 2. Instructions begin execution by the internal oscillator at the frequency set in the IRCF<3:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- System clock is switched to external clock source.

# 5.4.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCSTAT register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or the internal oscillator.

#### FIGURE 5-8: TWO-SPEED START-UP

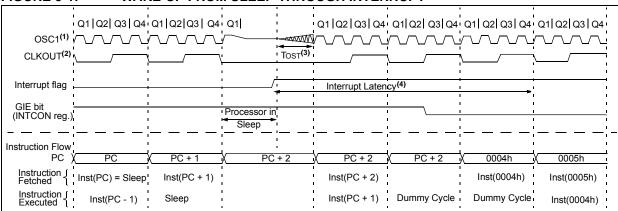

#### 9.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

Note 1: XT, HS or LP Oscillator mode assumed.

2: CLKOUT is not available in XT, HS, or LP Oscillator modes, but shown here for timing reference.

3: Tost = 1024 Tosc (drawing not to scale). This delay applies only to XT, HS or LP Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

| Name   | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3      | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|--------|--------|--------|------------|--------|--------|--------|---------------------|

| INTCON | GIE     | PEIE   | TMR0IE | INTE   | IOCIE      | TMR0IF | INTF   | IOCIF  | 98                  |

| IOCBF  | IOCBF7  | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3     | IOCBF2 | IOCBF1 | IOCBF0 | 152                 |

| IOCBN  | IOCBN7  | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3     | IOCBN2 | IOCBN1 | IOCBN0 | 152                 |

| IOCBP  | IOCBP7  | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3     | IOCBP2 | IOCBP1 | IOCBP0 | 152                 |

| PIE1   | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 99                  |

| PIE2   | OSFIE   | C2IE   | C1IE   | EEIE   | BCLIE      | LCDIE  | 1      | CCP2IE | 100                 |

| PIE3   | 1       | CCP5IE | CCP4IE | CCP3IE | TMR6IE     | -      | TMR4IE | -      | 101                 |

| PIR1   | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 102                 |

| PIR2   | OSFIF   | C2IF   | C1IF   | EEIF   | BCLIF      | LCDIF  | _      | CCP2IF | 103                 |

| PIR3   | -       | CCP5IF | CCP4IF | CCP3IF | TMR6IF     | _      | TMR4IF | _      | 104                 |

| STATUS | _       | _      | _      | TO     | PD         | Z      | DC     | С      | 29                  |

| WDTCON | _       | _      |        | \      | NDTPS<4:0> | •      |        | SWDTEN | 113                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used in Power-down mode.

#### **REGISTER 12-2: PORTA: PORTA REGISTER**

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RA7     | RA6     | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 RA<7:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is > VIH 0 = Port pin is < VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

#### **REGISTER 12-3: TRISA: PORTA TRI-STATE REGISTER**

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2  | TRISA1  | TRISA0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

#### REGISTER 12-4: LATA: PORTA DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATA7   | LATA6   | LATA5   | LATA4   | LATA3   | LATA2   | LATA1   | LATA0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 LATA<7:0>: PORTA Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register is return of actual I/O pin values.

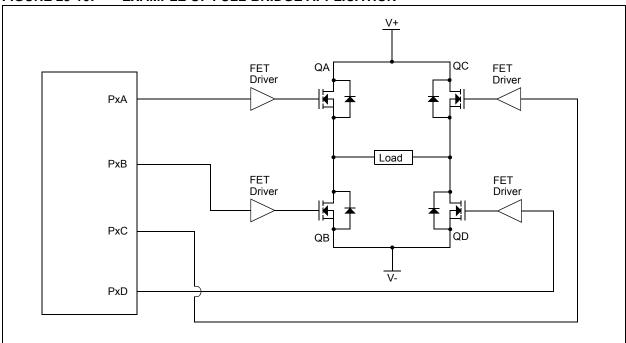

#### 23.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 23-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 23-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 23-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

FIGURE 23-10: EXAMPLE OF FULL-BRIDGE APPLICATION

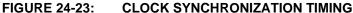

#### 24.5.6 CLOCK STRETCHING

Clock stretching occurs when a device on the bus holds the SCL line low, effectively pausing communication. The slave may stretch the clock to allow more time to handle data or prepare a response for the master device. A master device is not concerned with stretching as anytime it is active on the bus and not transferring data it is stretching. Any stretching done by a slave is invisible to the master software and handled by the hardware that generates SCL.

The CKP bit of the SSPCON1 register is used to control stretching in software. Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. Setting CKP will release SCL and allow more communication.

#### 24.5.6.1 Normal Clock Stretching

Following an  $\overline{ACK}$  if the R/W bit of SSPSTAT is set, a read request, the slave hardware will clear CKP. This allows the slave time to update SSPBUF with data to transfer to the master. If the SEN bit of SSPCON2 is set, the slave hardware will always stretch the clock after the  $\overline{ACK}$  sequence. Once the slave is ready, CKP is set by software and communication resumes.

- Note 1: The BF bit has no effect on whether the clock will be stretched or not. This is different than previous versions of the module that would not stretch the clock, clear CKP, if SSPBUF was read before the 9th falling edge of SCL.

- 2: Previous versions of the module did not stretch the clock for a transmission if SSPBUF was loaded before the 9th falling edge of SCL. It is now always cleared for read requests.

#### 24.5.6.2 10-bit Addressing Mode

In 10-bit Addressing mode, when the UA bit is set, the clock is always stretched. This is the only time the SCL is stretched without CKP being cleared. SCL is released immediately after a write to SSPADD.

**Note:** Previous versions of the module did not stretch the clock if the second address byte did not match.

#### 24.5.6.3 Byte NACKing

When the AHEN bit of SSPCON3 is set; CKP is cleared by hardware after the 8th falling edge of SCL for a received matching address byte. When the DHEN bit of SSPCON3 is set; CKP is cleared after the 8th falling edge of SCL for received data.

Stretching after the 8th falling edge of SCL allows the slave to look at the received address or data and decide if it wants to ACK the received data.

# 24.5.7 CLOCK SYNCHRONIZATION AND THE CKP BIT

Any time the CKP bit is cleared, the module will wait for the SCL line to go low and then hold it. However, clearing the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external I<sup>2</sup>C master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the I<sup>2</sup>C bus have released SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 24-22).

TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION

| Name    | Bit 7      | Bit 6           | Bit 5         | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Reset<br>Values on<br>Page: |

|---------|------------|-----------------|---------------|--------|--------|--------|--------|-----------------------|-----------------------------|

| INTCON  | GIE        | PEIE            | TMR0IE        | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF                 | 98                          |

| PIE1    | TMR1GIE    | ADIE            | RCIE          | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE                | 99                          |

| PIE2    | OSFIE      | C2IE            | C1IE          | EEIE   | BCLIE  | _      | _      | CCP2IE <sup>(1)</sup> | 100                         |

| PIR1    | TMR1GIF    | ADIF            | RCIF          | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF                | 102                         |

| PIR2    | OSFIF      | C2IF            | C1IF          | EEIF   | BCLIF  | _      | _      | CCP2IF <sup>(1)</sup> | 103                         |

| TRISC   | TRISC7     | TRISC6          | TRISC5        | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0                | 142                         |

| SSPADD  |            |                 |               | ADD<   | :7:0>  |        |        |                       | 290                         |

| SSPBUF  | MSSP Recei | ive Buffer/Trai | nsmit Registe | r      |        |        |        |                       | 243*                        |

| SSPCON1 | WCOL       | SSPOV           | SSPEN         | CKP    |        | SSPM   | <3:0>  |                       | 287                         |

| SSPCON2 | GCEN       | ACKSTAT         | ACKDT         | ACKEN  | RCEN   | PEN    | RSEN   | SEN                   | 288                         |

| SSPCON3 | ACKTIM     | PCIE            | SCIE          | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN                  | 289                         |

| SSPMSK  | MSK<7:0>   |                 |               |        |        |        |        | 290                   |                             |

| SSPSTAT | SMP        | CKE             | D/A           | Р      | S      | R/W    | UA     | BF                    | 286                         |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

\* Page provides register information.

**Note 1:** PIC16F1934 only.

# 25.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The EUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The EUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- · Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- · Input buffer overrun error detection

- Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- Programmable clock polarity in synchronous modes

- · Sleep operation

The EUSART module implements the following additional features, making it ideally suited for use in Local Interconnect Network (LIN) bus systems:

- · Automatic detection and calibration of the baud rate

- · Wake-up on Break reception

- · 13-bit Break character transmit

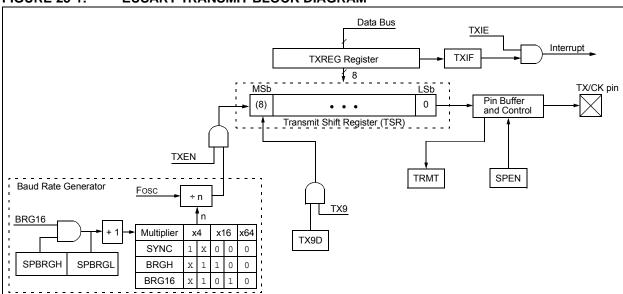

Block diagrams of the EUSART transmitter and receiver are shown in Figure 25-1 and Figure 25-2.

FIGURE 25-1: EUSART TRANSMIT BLOCK DIAGRAM

TABLE 25-3: BAUD RATE FORMULAS

| (    | Configuration Bi | ts   | DDC/EUCADT Mada     | Baud Rate Formula |

|------|------------------|------|---------------------|-------------------|

| SYNC | BRG16            | BRGH | BRG/EUSART Mode     | Baud Kale Formula |

| 0    | 0                | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |

| 0    | 0                | 1    | 8-bit/Asynchronous  | F-20//40 (- 14)1  |

| 0    | 1                | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |

| 0    | 1                | 1    | 16-bit/Asynchronous |                   |

| 1    | 0                | х    | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |

| 1    | 1                | х    | 16-bit/Synchronous  |                   |

**Legend:** x = Don't care, n = value of SPBRGH, SPBRGL register pair

TABLE 25-4: SUMMARY OF REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Name    | Bit 7     | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register on Page |

|---------|-----------|----------|-------|-------|-------|-------|-------|-------|------------------|

| BAUDCON | ABDOVF    | RCIDL    | _     | SCKP  | BRG16 |       | WUE   | ABDEN | 302              |

| RCSTA   | SPEN      | RX9      | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 301              |

| SPBRGL  |           | BRG<7:0> |       |       |       |       | 303*  |       |                  |

| SPBRGH  | BRG<15:8> |          |       |       | 303*  |       |       |       |                  |

| TXSTA   | CSRC      | TX9      | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 300              |

**Legend:** — = unimplemented read as '0'. Shaded cells are not used for the Baud Rate Generator.

<sup>\*</sup> Page provides register information.

#### REGISTER 27-7: LCDRL: LCD REFERENCE LADDER CONTROL REGISTERS

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0    | R/W-0/0 |

|---------|---------|---------|---------|-----|---------|------------|---------|

| LRLAF   | P<1:0>  | LRLBF   | P<1:0>  | _   |         | LRLAT<2:0> |         |

| bit 7   |         |         |         |     |         |            | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 LRLAP<1:0>: LCD Reference Ladder A Time Power Control bits

During Time interval A (Refer to Figure 27-4):

00 = Internal LCD Reference Ladder is powered down and unconnected

01 = Internal LCD Reference Ladder is powered in Low-Power mode

10 = Internal LCD Reference Ladder is powered in Medium-Power mode

11 = Internal LCD Reference Ladder is powered in High-Power mode

bit 5-4 LRLBP<1:0>: LCD Reference Ladder B Time Power Control bits

During Time interval B (Refer to Figure 27-4):

00 = Internal LCD Reference Ladder is powered down and unconnected

01 = Internal LCD Reference Ladder is powered in Low-Power mode

10 = Internal LCD Reference Ladder is powered in Medium-Power mode

11 = Internal LCD Reference Ladder is powered in High-Power mode

bit 3 Unimplemented: Read as '0'

bit 2-0 LRLAT<2:0>: LCD Reference Ladder A Time Interval Control bits

Sets the number of 32 kHz clocks that the A Time Interval Power mode is active

For type A waveforms (WFT = 0):

000 = Internal LCD Reference Ladder is always in 'B' Power mode

001 = Internal LCD Reference Ladder is in 'A' Power mode for 1 clock and 'B' Power mode for 15 clocks

010 = Internal LCD Reference Ladder is in 'A' Power mode for 2 clocks and 'B' Power mode for 14 clocks

011 = Internal LCD Reference Ladder is in 'A' Power mode for 3 clocks and 'B' Power mode for 13 clocks

100 = Internal LCD Reference Ladder is in 'A' Power mode for 4 clocks and 'B' Power mode for 12 clocks

101 = Internal LCD Reference Ladder is in 'A' Power mode for 5 clocks and 'B' Power mode for 11 clocks

110 = Internal LCD Reference Ladder is in 'A' Power mode for 6 clocks and 'B' Power mode for 10 clocks

111 = Internal LCD Reference Ladder is in 'A' Power mode for 7 clocks and 'B' Power mode for 9 clocks

For type B waveforms (WFT = 1):

000 = Internal LCD Reference Ladder is always in 'B' Power mode.

001 = Internal LCD Reference Ladder is in 'A' Power mode for 1 clock and 'B' Power mode for 31 clocks

010 = Internal LCD Reference Ladder is in 'A' Power mode for 2 clocks and 'B' Power mode for 30 clocks

011 = Internal LCD Reference Ladder is in 'A' Power mode for 3 clocks and 'B' Power mode for 29 clocks

100 = Internal LCD Reference Ladder is in 'A' Power mode for 4 clocks and 'B' Power mode for 28 clocks

101 = Internal LCD Reference Ladder is in 'A' Power mode for 5 clocks and 'B' Power mode for 27 clocks

110 = Internal LCD Reference Ladder is in 'A' Power mode for 6 clocks and 'B' Power mode for 26 clocks

111 = Internal LCD Reference Ladder is in 'A' Power mode for 7 clocks and 'B' Power mode for 25 clocks

| LSLF             | Logical Left Shift                                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] LSLF f {,d}                                                                                                                                                                                                   |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                      |

| Operation:       | $(f<7>) \rightarrow C$<br>$(f<6:0>) \rightarrow dest<7:1>$<br>$0 \rightarrow dest<0>$                                                                                                                                   |

| Status Affected: | C, Z                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are shifted one bit to the left through the Carry flag. A '0' is shifted into the LSb. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |

|                  | C register f ←0                                                                                                                                                                                                         |

| LSRF             | Logical Right Shift                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] LSLF f {,d}                                                                                                                                                                                                    |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                       |

| Operation:       | $0 \rightarrow \text{dest<7>}$ $(f<7:1>) \rightarrow \text{dest<6:0>},$ $(f<0>) \rightarrow C,$                                                                                                                          |

| Status Affected: | C, Z                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are shifted one bit to the right through the Carry flag. A '0' is shifted into the MSb. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is stored back in register 'f'. |

|                  | 0 → register f C                                                                                                                                                                                                         |

| MOVF             | Move f                                                                                                                                                                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                      |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                |

| Status Affected: | Z                                                                                                                                                                                                                                                       |

| Description:     | The contents of register f is moved to a destination dependent upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |

| Words:           | 1                                                                                                                                                                                                                                                       |

| Cycles:          | 1                                                                                                                                                                                                                                                       |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                             |

|                  | After Instruction  W = value in FSR register  Z = 1                                                                                                                                                                                                     |

#### TABLE 30-8: PIC16(L)F1934/6/7 A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated) Operating temperature Tested at 25°C |      |                                                   |      |      |      |       |                                                                          |

|----------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|--------------------------------------------------------------------------|

| Param<br>No.                                                                                 | Sym. | Characteristic                                    | Min. | Typ† | Max. | Units | Conditions                                                               |

| AD01                                                                                         | NR   | Resolution                                        | _    | _    | 10   | bit   |                                                                          |

| AD02                                                                                         | EIL  | Integral Error                                    | _    | _    | ±1.7 | LSb   | VREF = 3.0V                                                              |

| AD03                                                                                         | EDL  | Differential Error                                | _    | _    | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                          |

| AD04                                                                                         | Eoff | Offset Error                                      | _    | _    | ±2.5 | LSb   | VREF = 3.0V                                                              |

| AD05                                                                                         | Egn  | Gain Error                                        | _    | _    | ±2.0 | LSb   | VREF = 3.0V                                                              |

| AD06                                                                                         | VREF | Reference Voltage <sup>(3)</sup>                  | 1.8  | _    | VDD  | V     | VREF = (VREF+ minus VREF-) (Note 5)                                      |

| AD07                                                                                         | Vain | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                          |

| AD08                                                                                         | ZAIN | Recommended Impedance of<br>Analog Voltage Source | _    | _    | 10   | kΩ    | Can go higher if external $0.01\mu F$ capacitor is present on input pin. |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 3: ADC VREF is from external VREF, VDD pin or FVR, whichever is selected as reference input.

- **4:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

- 5: FVR voltage selected must be 2.048V or 4.096V.

#### TABLE 30-9: PIC16(L)F1934/6/7 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |      |                                                                 |      |      |      |       |                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------|------|------|-------|----------------------------------------|

| Param<br>No.                                                                                                                                | Sym. | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                             |

| AD130*                                                                                                                                      | TAD  | A/D Clock Period                                                | 1.0  |      | 9.0  | μS    | Tosc-based                             |

|                                                                                                                                             |      | A/D Internal RC Oscillator<br>Period                            | 1.0  | 2.5  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)             |

| AD131                                                                                                                                       | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | -    | 11   | _    | TAD   | Set GO/DONE bit to conversion complete |

| AD132*                                                                                                                                      | TACQ | Acquisition Time                                                | _    | 5.0  | _    | μS    |                                        |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TcY cycle.

FIGURE 31-38: PIC16LF1937 EC OSCILLATOR, LOW-POWER MODE, Fosc = 500 kHz

FIGURE 31-39: PIC16F1937 EC OSCILLATOR, LOW-POWER MODE, Fosc = 500 kHz

FIGURE 31-40: PIC16F1937 EXTRC MODE, Fosc = 4 MHz

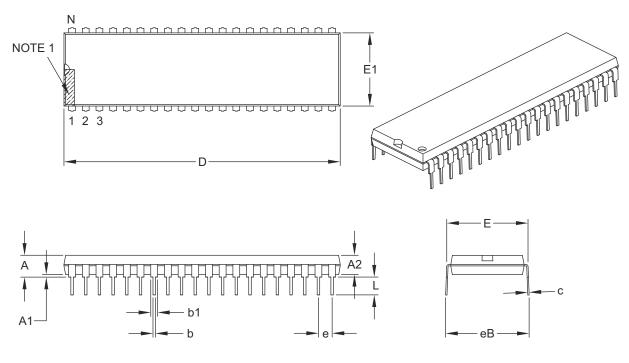

#### 40-Lead Plastic Dual In-Line (P) - 600 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |       | INCHES   |       |

|----------------------------|------------------|-------|----------|-------|

|                            | Dimension Limits | MIN   | NOM      | MAX   |

| Number of Pins             | N                |       | 40       | •     |

| Pitch                      | е                |       | .100 BSC |       |

| Top to Seating Plane       | A                | _     | -        | .250  |

| Molded Package Thickness   | A2               | .125  | -        | .195  |

| Base to Seating Plane      | A1               | .015  | _        | _     |

| Shoulder to Shoulder Width | E                | .590  | -        | .625  |

| Molded Package Width       | E1               | .485  | -        | .580  |

| Overall Length             | D                | 1.980 | -        | 2.095 |

| Tip to Seating Plane       | L                | .115  | -        | .200  |

| Lead Thickness             | С                | .008  | -        | .015  |

| Upper Lead Width           | b1               | .030  | _        | .070  |

| Lower Lead Width           | b                | .014  | _        | .023  |

| Overall Row Spacing §      | eB               | _     | _        | .700  |

#### Notes

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-016B

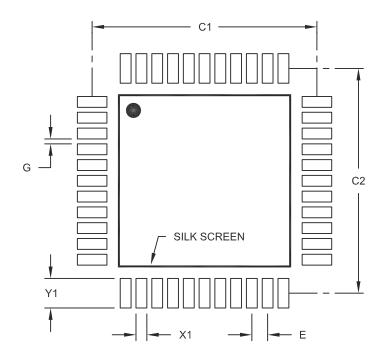

#### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIM |      |          |      |

|--------------------------|--------|------|----------|------|

| Dimension Limits         |        | MIN  | NOM      | MAX  |

| Contact Pitch            | E      |      | 0.80 BSC |      |

| Contact Pad Spacing      | C1     |      | 11.40    |      |

| Contact Pad Spacing      | C2     |      | 11.40    |      |

| Contact Pad Width (X44)  | X1     |      |          | 0.55 |

| Contact Pad Length (X44) | Y1     |      |          | 1.50 |

| Distance Between Pads    | G      | 0.25 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A

| Baud Rates, Asynchronous Modes                     |               | CALLW                                    | 373     |

|----------------------------------------------------|---------------|------------------------------------------|---------|

| Formulas                                           |               | LSLF                                     | 375     |

| High Baud Rate Select (BRGH Bit)                   | 305           | LSRF                                     | 375     |

| Synchronous Master Mode                            | 314, 318      | MOVF                                     | 375     |

| Associated Registers                               |               | MOVIW                                    | 376     |

| Receive                                            | 317           | MOVLB                                    | 376     |

| Transmit                                           | 315           | MOVWI                                    | 377     |

| Reception                                          | 316           | OPTION                                   | 377     |

| Transmission                                       |               | RESET                                    | 377     |

| Synchronous Slave Mode                             |               | SUBWFB                                   | 379     |

| Associated Registers                               |               | TRIS                                     | 380     |

| Receive                                            | 319           | BCF                                      | 372     |

| Transmit                                           |               | BSF                                      | 372     |

| Reception                                          |               | BTFSC                                    | 372     |

| Transmission                                       |               | BTFSS                                    |         |

| Extended Instruction Set                           |               | CALL                                     |         |

| ADDFSR                                             | 371           | CLRF                                     |         |

| ADDI OI                                            |               | CLRW                                     |         |

| F                                                  |               | CLRWDT                                   |         |

| Fail-Safe Clock Monitor                            | 81            | COMF                                     |         |

| Fail-Safe Condition Clearing                       |               |                                          |         |

| Fail-Safe Detection                                |               | DECF                                     |         |

| Fail-Safe Operation                                |               | DECFSZ                                   |         |

| •                                                  |               | GOTO                                     |         |

| Reset or Wake-up from Sleep                        |               | INCF                                     |         |

| Firmware Instructions(FVD)                         | 307           | INCFSZ                                   |         |

| Fixed Voltage Reference (FVR)                      | 450           | IORLW                                    |         |

| Associated Registers                               |               | IORWF                                    |         |

| Flash Program Memory                               |               | MOVLW                                    |         |

| Erasing                                            |               | MOVWF                                    | 376     |

| Modifying                                          |               | NOP                                      |         |

| Writing                                            |               | RETFIE                                   | 378     |

| FSR Register39, 40, 41, 42, 43, 44, 45, 46, 47, 48 |               | RETLW                                    | 378     |

| FVRCON (Fixed Voltage Reference Control) Reg       | ister 158     | RETURN                                   | 378     |

|                                                    |               | RLF                                      | 378     |

|                                                    |               | RRF                                      | 379     |

| <sup>2</sup> C Mode (MSSP)                         |               | SLEEP                                    | 379     |

| Acknowledge Sequence Timing                        | 280           | SUBLW                                    | 379     |

| Bus Collision                                      |               | SUBWF                                    | 379     |

| During a Repeated Start Condition                  | 284           | SWAPF                                    | 380     |

| During a Stop Condition                            | 285           | XORLW                                    |         |

| Effects of a Reset                                 | 281           | XORWF                                    |         |

| I <sup>2</sup> C Clock Rate w/BRG                  | 287           | INTCON Register                          |         |

| Master Mode                                        |               | Internal Oscillator Block                |         |

| Operation                                          | 272           | INTOSC                                   |         |

| Reception                                          |               | Specifications                           | 307     |

| Start Condition Timing                             |               | Internal Sampling Switch (Rss) Impedance |         |

| Transmission                                       |               | , .                                      |         |

| Multi-Master Communication, Bus Collision          |               | Internet Address                         |         |

| Arbitration                                        |               | Interrupt-On-Change                      |         |

| Multi-Master Mode                                  |               | Associated Registers                     |         |

| _                                                  |               | Interrupts                               |         |

| Read/Write Bit Information (R/W Bit)               | 237           | ADC                                      |         |

| Slave Mode                                         | 000           | Associated registers w/ Interrupts       |         |

| Transmission                                       |               | Configuration Word w/ Clock Sources      |         |

| Sleep Operation                                    |               | Configuration Word w/ LDO                | 109     |

| Stop Condition Timing                              |               | TMR1                                     | 201     |

| NDF Register39, 40, 41, 42, 43, 44, 45, 46, 47, 48 | 8, 49, 51, 52 | INTOSC Specifications                    | 397     |

| ndirect Addressing                                 | 56            | IOCBF Register                           | 154     |

| nstruction Format                                  | 368           | IOCBN Register                           |         |

| nstruction Set                                     | 367           | IOCBP Register                           |         |

| ADDLW                                              | 371           | •                                        |         |

| ADDWF                                              |               | L                                        |         |

| ADDWFC                                             |               | LATA Register                            | 135 144 |

| ANDLW                                              |               | LATB Register                            |         |

| ANDWF                                              |               | LATD Register                            |         |

| BRA                                                |               | <u> </u>                                 |         |

| CALL                                               |               | LATE Register                            | 131     |

| UNLL                                               |               | LCD                                      |         |

| SPI Slave Mode (CKE = 1)408                        |

|----------------------------------------------------|

| Synchronous Reception (Master Mode, SREN) 317      |

| Synchronous Transmission315                        |

| Synchronous Transmission (Through TXEN) 315        |

| Timer0 and Timer1 External Clock                   |

| Timer1 Incrementing Edge201                        |

| Two Speed Start-up80                               |

| Type-A in 1/2 MUX, 1/2 Bias Drive                  |

| Type-A in 1/2 MUX, 1/3 Bias Drive                  |

| Type-A in 1/3 MUX, 1/2 Bias Drive                  |

| Type-A in 1/3 MUX, 1/3 Bias Drive                  |

| Type-A in 1/3 MOX, 1/3 Bias Drive                  |

| Type-A/Type-B in Static Drive                      |

|                                                    |

| Type-B in 1/2 MUX, 1/2 Bias Drive                  |

| Type-B in 1/2 MUX, 1/3 Bias Drive                  |

| Type-B in 1/3 MUX, 1/2 Bias Drive                  |

| Type-B in 1/3 MUX, 1/3 Bias Drive                  |

| Type-B in 1/4 MUX, 1/3 Bias Drive                  |

| USART Synchronous Receive (Master/Slave) 406       |

| USART Synchronous Transmission (Master/Slave). 405 |

| Wake-up from Interrupt112                          |

| Timing Diagrams and Specifications                 |

| PLL Clock                                          |

| Timing Parameter Symbology                         |

| Timing Requirements                                |

| I <sup>2</sup> C Bus Data411                       |

| I2C Bus Start/Stop Bits410                         |

| SPI Mode409                                        |

| TMR0 Register39                                    |

| TMR1H Register39                                   |

| TMR1L Register                                     |

| TMR2 Register                                      |

| TRIS                                               |

| TRISA Register                                     |

| TRISB                                              |

| TRISB Register                                     |

| TRISC                                              |

| TRISC Register                                     |

| TRISD                                              |

| TRISD                                              |

|                                                    |

| TRISE                                              |

| TRISE Register                                     |

| Two-Speed Clock Start-up Mode                      |

| TXCON (Timer2/4/6) Register211                     |

| TXREG                                              |

| TXREG Register42                                   |

| TXSTA Register                                     |

| BRGH Bit                                           |

| U                                                  |

| _                                                  |

| USART                                              |

| Synchronous Master Mode                            |

| Requirements, Synchronous Receive406               |

| Requirements, Synchronous Transmission 406         |

| Timing Diagram, Synchronous Receive 406            |

| Timing Diagram, Synchronous Transmission 405       |

| ١ | ľ | V |

|---|---|---|

| 311              |

|------------------|

| 112              |

| 90               |

| 116              |

| 116              |

| 114              |

| 401              |

| 3, 276, 278, 280 |

| 3, 276, 278, 280 |

| 115              |

| 141              |

| 65               |

| 471              |

| 14               |

|                  |

VREF. SEE ADC Reference Voltage