Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1934-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F1934/6/7

| Address                | Name    | Bit 7         | Bit 6                         | Bit 5           | Bit 4           | Bit 3          | Bit 2      | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|---------------|-------------------------------|-----------------|-----------------|----------------|------------|-------|-------|----------------------|---------------------------------|

| Bank 4                 |         |               |                               |                 |                 |                |            |       |       |                      | _                               |

| 200h <sup>(2)</sup>    | INDF0   |               | this location u cal register) | ses contents c  | of FSR0H/FSF    | ROL to address | data memor | ý     |       | XXXX XXXX            | XXXX XXXX                       |

| 201h <sup>(2)</sup>    | INDF1   |               | this location u cal register) | ses contents c  | of FSR1H/FSF    | R1L to address | data memor | ý     |       | XXXX XXXX            | XXXX XXXX                       |

| 202h <sup>(2)</sup>    | PCL     | Program Co    | ounter (PC) Le                | ast Significant | Byte            |                |            |       |       | 0000 0000            | 0000 0000                       |

| 203h <sup>(2)</sup>    | STATUS  | _             | _                             | _               | TO              | PD             | Z          | DC    | С     | 1 1000               | q quuu                          |

| 204h <sup>(2)</sup>    | FSR0L   | Indirect Data | a Memory Add                  | Iress 0 Low Po  | ointer          |                |            |       |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(2)</sup>    | FSR0H   | Indirect Data | a Memory Add                  | lress 0 High P  | ointer          |                |            |       |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(2)</sup>    | FSR1L   | Indirect Data | a Memory Add                  | Iress 1 Low Po  | pinter          |                |            |       |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(2)</sup>    | FSR1H   | Indirect Data | a Memory Add                  | lress 1 High P  | ointer          |                |            |       |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(2)</sup>    | BSR     | _             | _                             | _               |                 | E              | BSR<4:0>   |       |       | 0 0000               | 0 0000                          |

| 209h <sup>(2)</sup>    | WREG    | Working Re    | gister                        |                 |                 |                |            |       |       | 0000 0000            | uuuu uuuu                       |

| 20Ah <sup>(1, 2)</sup> | PCLATH  | _             | Write Buffer f                | or the upper 7  | bits of the Pro | ogram Counter  | r          |       |       | -000 0000            | -000 0000                       |

| 20Bh <sup>(2)</sup>    | INTCON  | GIE           | PEIE                          | TMR0IE          | INTE            | IOCIE          | TMR0IF     | INTF  | IOCIF | 0000 0000            | 0000 0000                       |

| 20Ch                   | —       | Unimpleme     | nted                          |                 |                 |                | •          | •     |       | _                    | —                               |

| 20Dh                   | WPUB    | WPUB7         | WPUB6                         | WPUB5           | WPUB4           | WPUB3          | WPUB2      | WPUB1 | WPUB0 | 1111 1111            | 1111 1111                       |

| 20Eh                   |         | Unimpleme     | nted                          |                 |                 |                |            |       |       | _                    | _                               |

| 20Fh                   | _       | Unimpleme     | nted                          |                 |                 |                |            |       |       | _                    | _                               |

| 210h                   | WPUE    |               | _                             | _               | _               | WPUE3          | _          | _     | _     | 1                    | 1                               |

| 211h                   | SSPBUF  | Synchronou    | us Serial Port F              | Receive Buffer  | /Transmit Reg   | jister         |            |       |       | xxxx xxxx            | uuuu uuuu                       |

| 212h                   | SSPADD  |               |                               |                 | ADD<            | 7:0>           |            |       |       | 0000 0000            | 0000 0000                       |

| 213h                   | SSPMSK  |               |                               |                 | MSK<            | 7:0>           |            |       |       | 1111 1111            | 1111 1111                       |

| 214h                   | SSPSTAT | SMP           | CKE                           | D/A             | Р               | S              | R/W        | UA    | BF    | 0000 0000            | 0000 0000                       |

| 215h                   | SSPCON1 | WCOL          | SSPOV                         | SSPEN           | CKP             |                | SSPM<      | :3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                   | SSPCON2 | GCEN          | ACKSTAT                       | ACKDT           | ACKEN           | RCEN           | PEN        | RSEN  | SEN   | 0000 0000            | 0000 0000                       |

| 217h                   | SSPCON3 | ACKTIM        | PCIE                          | SCIE            | BOEN            | SDAHT          | SBCDE      | AHEN  | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                   | _       | Unimpleme     | nted                          |                 |                 |                | 1          | •     |       | _                    | _                               |

| 219h                   | _       | Unimpleme     | Unimplemented                 |                 |                 |                |            |       |       | _                    | _                               |

| 21Ah                   | _       | Unimpleme     | Unimplemented                 |                 |                 |                |            |       |       | _                    | _                               |

| 21Bh                   | _       | Unimpleme     | Unimplemented                 |                 |                 |                |            |       |       | _                    | _                               |

| 21Ch                   | —       | Unimpleme     | Unimplemented                 |                 |                 |                |            |       |       | -                    | _                               |

| 21Dh                   | —       | Unimpleme     | Unimplemented                 |                 |                 |                |            |       |       | _                    | _                               |

| 21Eh                   | _       | Unimpleme     | nted                          |                 |                 |                |            |       |       | _                    | _                               |

| 21Fh                   | _       | Unimpleme     | nted                          |                 |                 |                |            |       |       | _                    | _                               |

## TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

$Legend: \qquad x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.$

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

4: Unimplemented, read as '1'.

# 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

# 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word 1) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Word 1 configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| TABLE 5-1: OSCI | LLATOR SWITCHING DELAYS |

|-----------------|-------------------------|

|-----------------|-------------------------|

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay                 |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | Oscillator Warm-up Delay (Twarm) |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                         |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each                  |

| Sleep/POR        | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST)          |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)                   |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each                  |

| Any clock source | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST)          |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)                   |

Note 1: PLL inactive.

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

| EXA   | MPI                  | LE 11-5:       | WRITING TO FLA    | ASH PROGRAM MEMORY                                                                  |

|-------|----------------------|----------------|-------------------|-------------------------------------------------------------------------------------|

| ; ]   | This                 | write rout     | ine assumes the f | ollowing:                                                                           |

| ; 1   | 1. Tł                | ne 16 bytes    | of data are load  | ed, starting at the address in DATA_ADDR                                            |

|       |                      | _              |                   | en is made up of two adjacent bytes in DATA_ADDR,                                   |

| ;     |                      |                | ttle endian forma |                                                                                     |

| ; 3   | 3. A                 | valid star     | ting address (the | least significant bits = 000) is loaded in ADDRH:ADDRL                              |

|       |                      |                |                   | n shared data memory $0x70 - 0x7F$ (common RAM)                                     |

| ;     |                      |                |                   |                                                                                     |

|       |                      | BCF            | INTCON, GIE       | ; Disable ints so required sequences will execute properly                          |

|       |                      | BANKSEL        |                   | <i>i</i> Bank 3                                                                     |

|       |                      | MOVF           |                   | ; Load initial address                                                              |

|       |                      | MOVWF          |                   | i                                                                                   |

|       |                      | MOVF           |                   | ·<br>/                                                                              |

|       |                      | MOVWF          | EEADRL            | ·<br>/                                                                              |

|       |                      | MOVLW          |                   | ; Load initial data address                                                         |

|       |                      | MOVWF          |                   | i                                                                                   |

|       |                      | MOVLW          |                   | ; Load initial data address                                                         |

|       |                      | MOVWF          |                   | i                                                                                   |

|       |                      | BSF            |                   | ; Point to program memory                                                           |

|       |                      | BCF            |                   | ; Not configuration space                                                           |

|       |                      | BSF            |                   | ; Enable writes                                                                     |

|       |                      | BSF            |                   | ; Only Load Write Latches                                                           |

| LOC   | OP                   |                | ,                 | -                                                                                   |

|       |                      | MOVIW          | FSR0++            | ; Load first data byte into lower                                                   |

|       |                      | MOVWF          | EEDATL            | -<br>;                                                                              |

|       |                      | MOVIW          |                   | ; Load second data byte into upper                                                  |

|       |                      | MOVWF          |                   | <br>;                                                                               |

|       |                      |                |                   |                                                                                     |

|       |                      | MOVF           | EEADRL,W          | ; Check if lower bits of address are '000'                                          |

| 1     |                      | XORLW          | 0x07              | ; Check if we're on the last of 8 addresses                                         |

|       |                      | ANDLW          | 0x07              | ;                                                                                   |

|       |                      | BTFSC          | STATUS, Z         | ; Exit if last of eight words,                                                      |

|       |                      | GOTO           | START_WRITE       | ;                                                                                   |

| _     |                      |                |                   |                                                                                     |

|       |                      | MOVLW          | 55h               | ; Start of required write sequence:                                                 |

|       |                      | MOVWF          | EECON2            | ; Write 55h                                                                         |

|       | л ü                  | MOVLW          | 0AAh              | ;                                                                                   |

|       | enc.                 | MOVWF          | EECON2            | ; Write AAh                                                                         |

|       | Required<br>Sequence | BSF            | EECON1,WR         | ; Set WR bit to begin write                                                         |

| 1     | S, R                 | NOP            |                   | ; Any instructions here are ignored as processor                                    |

|       |                      |                |                   | ; halts to begin write sequence                                                     |

|       |                      | NOP            |                   | ; Processor will stop here and wait for write to complete.                          |

| L     |                      |                |                   |                                                                                     |

|       |                      |                |                   | ; After write processor continues with 3rd instruction.                             |

|       |                      |                |                   |                                                                                     |

|       |                      | INCF           |                   | ; Still loading latches Increment address                                           |

|       |                      | GOTO           | LOOP              | ; Write next latches                                                                |

| ~ ~ ~ |                      |                |                   |                                                                                     |

| S17   | 4K.I. <sup>_</sup> N | VRITE          | BEGON1 INTO       | · No would look a lot show . Notice like a tout Black we we we                      |

|       |                      | BCF            |                   | ; No more loading latches - Actually start Flash program                            |

|       |                      |                |                   | ; memory write                                                                      |

| Γ     |                      | MOLITIN        | Г Г h             | · Chart of manufactured and the semiconset                                          |

|       |                      | MOVLW          |                   | ; Start of required write sequence:                                                 |

|       | <u>س</u>             | MOVWF          |                   | ; Write 55h                                                                         |

|       | no.                  | MOVLW<br>MOVWF |                   | ;<br>; Write AAh                                                                    |

|       | Required<br>Sequence | BSF            |                   | , write AAN<br>; Set WR bit to begin write                                          |

|       | Sec                  | NOP            |                   | -                                                                                   |

|       |                      | NOF            |                   | ; Any instructions here are ignored as processor<br>; halts to begin write sequence |

|       |                      | NOP            |                   | ; Processor will stop here and wait for write complete.                             |

|       |                      | NOF            |                   | , ridessor will stop here and wait for write compile.                               |

|       |                      |                |                   | ; after write processor continues with 3rd instruction                              |

| ı.    |                      | BCF            |                   | ; Disable writes                                                                    |

| ı.    |                      | BSF            | •                 | ; Enable interrupts                                                                 |

|       |                      |                |                   |                                                                                     |

|       |                      |                |                   |                                                                                     |

| U-0             | R/W-0/0                                                                                                                          | R/W-0/0                                                                                                                              | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|--------------|--|--|--|--|

| _               | CCP3SEL                                                                                                                          | T1GSEL                                                                                                                               | P2BSEL         | SRNQSEL        | C2OUTSEL         | SSSEL            | CCP2SEL      |  |  |  |  |

| bit 7           |                                                                                                                                  |                                                                                                                                      |                |                |                  |                  | bit 0        |  |  |  |  |

|                 |                                                                                                                                  |                                                                                                                                      |                |                |                  |                  |              |  |  |  |  |

| Legend:         |                                                                                                                                  |                                                                                                                                      |                |                |                  |                  |              |  |  |  |  |

| R = Readabl     |                                                                                                                                  | W = Writable                                                                                                                         |                | -              | mented bit, read |                  |              |  |  |  |  |

| u = bit is unc  | -                                                                                                                                | x = Bit is unk                                                                                                                       |                | -n/n = Value a | at POR and BOF   | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is se | t                                                                                                                                | '0' = Bit is cle                                                                                                                     | ared           |                |                  |                  |              |  |  |  |  |

| bit 7           | Unimplement                                                                                                                      | ed: Read as '0                                                                                                                       | ,              |                |                  |                  |              |  |  |  |  |

| bit 6           | •                                                                                                                                | CP3 Input/Out                                                                                                                        |                | ion bit        |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | vices (PIC16F                                                                                                                        |                |                |                  |                  |              |  |  |  |  |

|                 | 0 = CCP3/P3                                                                                                                      | BA function is c                                                                                                                     | on RC6/TX/CK   | C/CCP3/P3A/SE  | EG9              |                  |              |  |  |  |  |

|                 |                                                                                                                                  |                                                                                                                                      |                | CPS5/CCP3/P    | 3A/T1G/COM1      |                  |              |  |  |  |  |

|                 | -                                                                                                                                | evices (PIC16F                                                                                                                       |                |                | ~ /              |                  |              |  |  |  |  |

|                 |                                                                                                                                  |                                                                                                                                      |                | CP3/P3A/SEG    |                  |                  |              |  |  |  |  |

| bit 5           |                                                                                                                                  | <ul> <li>1 = CCP3/P3A function is on RB5/AN13/CPS5/CCP3/P3A/T1G/COM1</li> <li>T1GSEL: Timer1 Gate Input Pin Selection bit</li> </ul> |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | tion is on RB5/AN13/CPS5/CCP3/P3A/T1G/COM1                                                                                           |                |                |                  |                  |              |  |  |  |  |

|                 | 1 = T1G fund                                                                                                                     | ction is on RC4                                                                                                                      | /SDI/SDA/T10   | G/SEG11        |                  |                  |              |  |  |  |  |

| bit 4           | P2BSEL: CC                                                                                                                       | P2 PWM B Ou                                                                                                                          | tput Pin Selec | ction bit      |                  |                  |              |  |  |  |  |

|                 | For 28-Pin De                                                                                                                    | evices (PIC16F                                                                                                                       | <u>1936)</u> : |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | tion is on RC0/T1OSO/T1CKI/P2B                                                                                                       |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | tion is on RB5/AN13/P2B/CPS5/T1G/COM1<br>vices (PIC16F1934/7):                                                                       |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | -                                                                                                                                    | -              | KI/P2B         |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | 0 = P2B function is on RC0/T1OSO/T1CKI/P2B<br>1 = P2B function is on RD2/CPS10/P2B                                                   |                |                |                  |                  |              |  |  |  |  |

| bit 3           | SRNQSEL: S                                                                                                                       | R Latch nQ O                                                                                                                         | utput Pin Sele | ction bit      |                  |                  |              |  |  |  |  |

|                 | 0 = SRnQ function is on RA5/AN4/C2OUT/SRnQ/SS/CPS7/SEG5/Vcap<br>1 = SRnQ function is on RA0/AN0/C12IN0-/C2OUT/SRnQ/SS/SEG12/Vcap |                                                                                                                                      |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  |                                                                                                                                      |                |                | nQ/SS/SEG12/V    | CAP              |              |  |  |  |  |

| bit 2           |                                                                                                                                  | C2OUTSEL: Comparator C2 Output Pin Selection bit                                                                                     |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                                                  | 0 = C2OUT function is on RA5/AN4/C2OUT/SRnQ/SS/CPS7/SEG5/Vcap<br>1 = C2OUT function is on RA0/AN0/C12IN0-/C2OUT/SRnQ/SS/SEG12/Vcap   |                |                |                  |                  |              |  |  |  |  |

| bit 1           |                                                                                                                                  | nput Pin Select                                                                                                                      |                | N0-/C2001/Sr   | (IIQ/33/3EG12/   | VCAP             |              |  |  |  |  |

|                 |                                                                                                                                  |                                                                                                                                      |                | RNQ/SS/CPS     | 7/SEG5/VCAP      |                  |              |  |  |  |  |

|                 |                                                                                                                                  |                                                                                                                                      |                |                | /SS/SEG12/Vca    | P                |              |  |  |  |  |

| bit 0           |                                                                                                                                  | CP2 Input/Out                                                                                                                        |                |                |                  |                  |              |  |  |  |  |

|                 | 0 = CCP2/P2                                                                                                                      | 2A function is c                                                                                                                     | on RC1/T1OS    | /CCP2/P2A      |                  |                  |              |  |  |  |  |

|                 | 1 = CCP2/P2                                                                                                                      | 2A function is c                                                                                                                     | n RB3/AN9/C    | 12IN2-/CPS3/0  | CCP2/P2A/VLCI    | 03               |              |  |  |  |  |

# REGISTER 12-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| Name       | Bit 7  | Bit 6   | Bit 5      | Bit 4    | Bit 3   | Bit 2             | Bit 1      | Bit 0   | Register<br>on Page |

|------------|--------|---------|------------|----------|---------|-------------------|------------|---------|---------------------|

| ADCON0     |        |         |            | CHS<4:0> |         |                   | GO/DONE    | ADON    | 163                 |

| ADCON1     | ADFM   |         | ADCS<2:0>  |          | —       | ADNREF            | ADPRE      | F<1:0>  | 164                 |

| ANSELA     | _      | _       | ANSA5      | ANSA4    | ANSA3   | ANSA2             | ANSA1      | ANSA0   | 134                 |

| APFCON     | -      | CCP3SEL | T1GSEL     | P2BSEL   | SRNQSEL | C2OUTSEL          | SSSEL      | CCP2SEL | 131                 |

| CM1CON0    | C10N   | C1OUT   | C10E       | C1POL    | —       | C1SP              | C1HYS      | C1SYNC  | 183                 |

| CM2CON0    | C2ON   | C2OUT   | C2OE       | C2POL    | —       | C2SP              | C2HYS      | C2SYNC  | 183                 |

| CM1CON1    | C1NTP  | C1INTN  | C1PCI      | H<1:0>   | —       | —                 | C1NCI      | H<1:0>  | 184                 |

| CM2CON1    | C2NTP  | C2INTN  | C2PCI      | H<1:0>   | —       | —                 | C2NCH<1:0> |         | 184                 |

| CPSCON0    | CPSON  | —       | _          | —        | CPSRN   | IG<1:0>           | CPSOUT     | TOXCS   | 323                 |

| CPSCON1    | _      | —       | _          | —        |         | CPSCI             |            | 324     |                     |

| DACCON0    | DACEN  | DACLPS  | DACOE      |          | DACPS   | SS<1:0>           |            | DACNSS  | 176                 |

| LATA       | LATA7  | LATA6   | LATA5      | LATA4    | LATA3   | LATA2             | LATA1      | LATA0   | 133                 |

| LCDCON     | LCDEN  | SLPEN   | WERR       | —        | CS<     | CS<1:0> LMUX<1:0> |            |         | 329                 |

| LCDSE0     | SE7    | SE6     | SE5        | SE4      | SE3     | SE2               | SE1        | SE0     | 333                 |

| LCDSE1     | SE15   | SE14    | SE13       | SE12     | SE11    | SE10              | SE9        | SE8     | 333                 |

| OPTION_REG | WPUEN  | INTEDG  | TMR0CS     | TMR0SE   | PSA     |                   | PS<2:0>    |         | 193                 |

| PORTA      | RA7    | RA6     | RA5        | RA4      | RA3     | RA2               | RA1        | RA0     | 133                 |

| SRCON0     | SRLEN  |         | SRCLK<2:0> | •        | SRQEN   | SRNQEN            | SRPS       | SRPR    | 189                 |

| SSPCON1    | WCOL   | SSPOV   | SSPEN      | CKP      |         | SSPM              | 1          | 287     |                     |

| TRISA      | TRISA7 | TRISA6  | TRISA5     | TRISA4   | TRISA3  | TRISA2            | TRISA1     | TRISA0  | 133                 |

# TABLE 12-3: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

## TABLE 12-4: SUMMARY OF CONFIGURATION WORD WITH PORTA

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5                   | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------------------------|-----------|----------|----------|---------|---------|---------------------|

| 0015104 | 13:8 | _       | _       | FCMEN                      | IESO      | CLKOUTEN | BORE     | N<1:0>  | CPD     |                     |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE                      | WDTE<1:0> |          |          | 62      |         |                     |

| 0015100 | 13:8 | _       | _       | LVP                        | DEBUG     | _        | BORV     | STVREN  | PLLEN   |                     |

| CONFIG2 | 7:0  | _       | _       | VCAPEN<1:0> <sup>(1)</sup> |           | _        | _        | WRT     | <1:0>   | 64                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by PORTA.

Legend: — = unimplemented lo Note 1: PIC16F1934/6/7 only.

# 12.5 PORTD Registers

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 12-14). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTD register (Register 12-14) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATD).

| Note: | PORTD is available on PIC16(L)F1934 |

|-------|-------------------------------------|

|       | and PIC16(L)F1937 only.             |

The TRISD register (Register 12-15) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 12.5.1 ANSELD REGISTER

The ANSELD register (Register 12-17) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELD bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

## 12.5.2 PORTD FUNCTIONS AND OUTPUT PRIORITIES

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-9.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-9.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RD0      | COM3 (LCD)<br>RD0                |

| RD1      | CCP4 (CCP)<br>RD1                |

| RD2      | P2B (CCP)<br>RD2                 |

| RD3      | SEG16 (LCD)<br>P2C (CCP)<br>RD3  |

| RD4      | SEG17 (LCD)<br>P2D (CCP)<br>RD4  |

| RD5      | SEG18 (LCD)<br>P1B (CCP)<br>RD5  |

| RD6      | SEG19 (LCD)<br>P1C (CCP)<br>RD6  |

| RD7      | SEG20 (LCD)<br>P1D (CCP)<br>RD7  |

TABLE 12-9: PORTD OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

| R/W-1/1                                 | R/W-1/1 | R/W-1/1           | R/W-1/1 | R/W-1/1                                               | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |  |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|--|

| ANSD7                                   | ANSD6   | ANSD5             | ANSD4   | ANSD3                                                 | ANSD2   | ANSD1   | ANSD0   |  |  |  |

| bit 7 b                                 |         |                   |         |                                                       |         |         |         |  |  |  |

|                                         |         |                   |         |                                                       |         |         |         |  |  |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |  |  |

| R = Readable                            | bit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clea |         |                                                       |         |         |         |  |  |  |

# REGISTER 12-17: ANSELD: PORTD ANALOG SELECT REGISTER<sup>(2)</sup>

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 2: ANSELD register is not implemented on the PIC16(L)F1936. Read as '0'.

- 3: PORTD implemented on PIC16(L)F1934/7 devices only.

| TABLE 12-10 | ): SUMM | ARY OF F | REGISTER | S ASSOC | IATED W | ITH PORT | 'D <sup>(1)</sup> |   |

|-------------|---------|----------|----------|---------|---------|----------|-------------------|---|

| Name        | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3   | Bit 2    | Bit 1             | E |

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3         | Bit 2  | Bit 1         | Bit 0  | Register on<br>Page |

|---------|--------|--------|--------|--------|---------------|--------|---------------|--------|---------------------|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3         | ANSD2  | ANSD1         | ANSD0  | 146                 |

| CCPxCON | PxM<   | <1:0>  | DCxB   | <1:0>  | 0> CCPxM<3:0> |        |               |        | 234                 |

| CPSCON0 | CPSON  | _      | _      |        | CPSRNG<1:0>   |        | G<1:0> CPSOUT |        | 323                 |

| CPSCON1 | _      | _      | _      |        | CPSCH<3:0>    |        |               |        | 324                 |

| LATD    | LATD7  | LATD6  | LATD5  | LATD4  | LATD3         | LATD2  | LATD1         | LATD0  | 145                 |

| LCDCON  | LCDEN  | SLPEN  | WERR   | _      | CS<           | 1:0>   | LMUX          | (<1:0> | 329                 |

| LCDSE2  | SE23   | SE22   | SE21   | SE20   | SE19          | SE18   | SE17          | SE16   | 333                 |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3           | RD2    | RD1           | RD0    | 145                 |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3        | TRISD2 | TRISD1        | TRISD0 | 145                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not implemented on the PIC16(L)F1936 devices, read as '0'.

bit 7-0 ANSD<7:0>: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function.

Note 1: When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

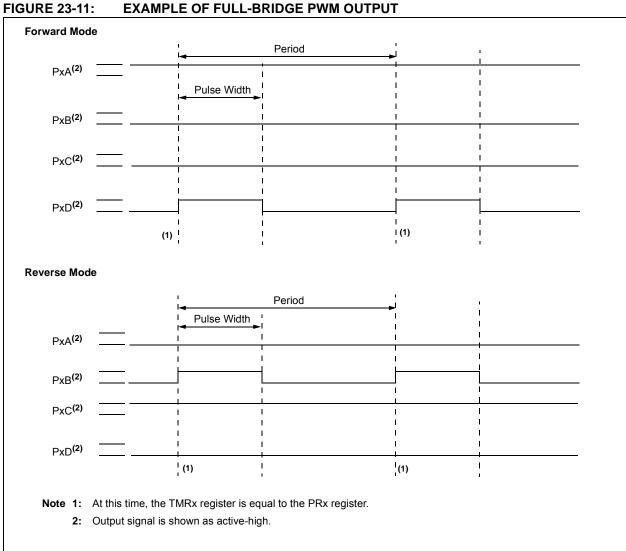

| PxM< | 1:0>                      | Signal        | 0 Pulse Width   | <b>—</b>  |          |

|------|---------------------------|---------------|-----------------|-----------|----------|

| 00   | (Single Output)           | PxA Modulated |                 | Period —  |          |

| 00   | (Single Output)           |               | -               | <br>: :   |          |

|      |                           | PxA Modulated | Delay           | <br>Delay | i        |

| 10   | (Half-Bridge)             | PxB Modulated |                 |           | <u>_</u> |

|      |                           | PxA Active    | - :<br>- :<br>: |           |          |

| 01   | (Full-Bridge,<br>Forward) | PxB Inactive  | - '<br>- '<br>' |           |          |

|      |                           | PxC Inactive  | - 1             |           |          |

|      |                           | PxD Modulated |                 | I         |          |

|      |                           | PxA Inactive  | - <u> </u>      |           | <u> </u> |

| 11   | (Full-Bridge,<br>Reverse) | PxB Modulated | -  <br>- ¦      | <u> </u>  |          |

|      |                           | PxC Active    |                 |           |          |

|      |                           | PxD Inactive  | -               |           | 1        |

| Rola | ionships:                 |               |                 |           |          |

#### **FIGURE 23-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)**

CPxCON<5:4>) \* (TMRx Prescale Value)

Pulse Width = IOSC \* (CCPRXL<7:0>:C

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

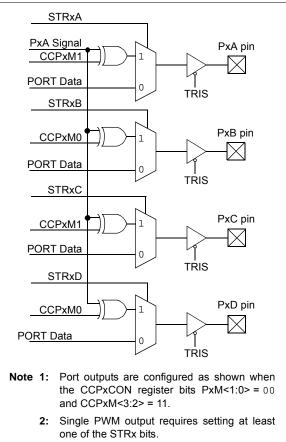

# 23.4.6 PWM STEERING MODE

In Single Output mode, PWM steering allows any of the PWM pins to be the modulated signal. Additionally, the same PWM signal can be simultaneously available on multiple pins.

Once the Single Output mode is selected (CCPxM<3:2> = 11 and PxM<1:0> = 00 of the CCPxCON register), the user firmware can bring out the same PWM signal to one, two, three or four output pins by setting the appropriate STRx<D:A> bits of the PSTRxCON register, as shown in Table 23-9.

Note: The associated TRIS bits must be set to output ('0') to enable the pin output driver in order to see the PWM signal on the pin.

While the PWM Steering mode is active, CCPxM<1:0> bits of the CCPxCON register select the PWM output polarity for the Px<D:A> pins.

The PWM auto-shutdown operation also applies to PWM Steering mode as described in **Section 23.4.3 "Enhanced PWM Auto-shutdown mode"**. An auto-shutdown event will only affect pins that have PWM outputs enabled.

FIGURE 23-18: SIMPLIFIED STEERING BLOCK DIAGRAM

| R/W-0/0          | R/W-0/0     | R/W-0/0           | R/W-0/0    | R/W-0/0                                               | R/W-0/0          | R/W-0/0      | R/W-0/0        |  |  |

|------------------|-------------|-------------------|------------|-------------------------------------------------------|------------------|--------------|----------------|--|--|

| PxRSEN           |             |                   |            | PxDC<6:0>                                             |                  |              |                |  |  |

| bit 7            |             |                   |            |                                                       |                  |              | bit 0          |  |  |

|                  |             |                   |            |                                                       |                  |              |                |  |  |

| Legend:          |             |                   |            |                                                       |                  |              |                |  |  |

| R = Readable     | e bit       | W = Writable      | bit        | U = Unimplen                                          | nented bit, read | d as '0'     |                |  |  |

| u = Bit is unc   | hanged      | x = Bit is unkr   | nown       | -n/n = Value at POR and BOR/Value at all other Resets |                  |              |                |  |  |

| '1' = Bit is set | t           | '0' = Bit is clea | ared       |                                                       |                  |              |                |  |  |

|                  |             |                   |            |                                                       |                  |              |                |  |  |

| bit 7            | PxRSEN: P   | WM Restart Ena    | ıble bit   |                                                       |                  |              |                |  |  |

|                  | the PWI     | M restarts auton  | natically  | oit clears automa                                     |                  |              | ent goes away; |  |  |

|                  | 0 = Upon au | uto-shutdown, C   | CPxASE mus | st be cleared in s                                    | software to rest | tart the PWM |                |  |  |

| bit 6-0          | PxDC<6:0>:  | : PWM Delay Co    | ount bits  |                                                       |                  |              |                |  |  |

|                  |             |                   | . ,        | cycles between<br>e <b>actual</b> time it ti          |                  |              | a PWM signal   |  |  |

# REGISTER 23-5: PWMxCON: ENHANCED PWM CONTROL REGISTER

**Note 1:** Bit resets to '0' with Two-Speed Start-up and LP, XT or HS selected as the Oscillator mode or Fail-Safe mode is enabled.

# PIC16(L)F1934/6/7

# PIC16(L)F1934/6/7

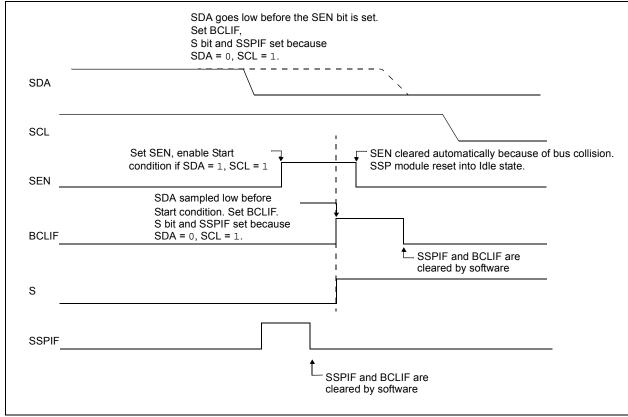

#### 24.6.13.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 24-32).

- b) SCL is sampled low before SDA is asserted low (Figure 24-33).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 24-32).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded and counts down. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 24-34). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to zero; if the SCL pin is sampled as '0' during this time, a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

# FIGURE 24-33: BUS COLLISION DURING START CONDITION (SDA ONLY)

|        |                   | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                   |            |                             |                   |      |       |                    |            |                             |

|--------|-------------------|------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------|-------|--------------------|------------|-----------------------------|

| BAUD   | Fosc = 32.000 MHz |                                                      |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |      |       | Fosc = 11.0592 MHz |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    |      |       | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | 300.0             | 0.00                                                 | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00 | 15359 | 300.0              | 0.00       | 9215                        |

| 1200   | 1200              | 0.00                                                 | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00 | 3839  | 1200               | 0.00       | 2303                        |

| 2400   | 2400              | 0.01                                                 | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00 | 1919  | 2400               | 0.00       | 1151                        |

| 9600   | 9604              | 0.04                                                 | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00 | 479   | 9600               | 0.00       | 287                         |

| 10417  | 10417             | 0.00                                                 | 767                         | 10417             | 0.00       | 479                         | 10425             | 0.08 | 441   | 10433              | 0.16       | 264                         |

| 19.2k  | 19.18k            | -0.08                                                | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00 | 239   | 19.20k             | 0.00       | 143                         |

| 57.6k  | 57.55k            | -0.08                                                | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00 | 79    | 57.60k             | 0.00       | 47                          |

| 115.2k | 115.9k            | 0.64                                                 | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00 | 39    | 115.2k             | 0.00       | 23                          |

# TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|                     | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                |            |                             |                |            |                             |                |            |                             |

|---------------------|------------------------------------------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD Fosc = 8.000 M |                                                      | ) MHz      | Fos                         | c = 4.000      | ) MHz      | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE                | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300                 | 300.0                                                | 0.00       | 6666                        | 300.0          | 0.01       | 3332                        | 300.0          | 0.00       | 3071                        | 300.1          | 0.04       | 832                         |

| 1200                | 1200                                                 | -0.02      | 1666                        | 1200           | 0.04       | 832                         | 1200           | 0.00       | 767                         | 1202           | 0.16       | 207                         |

| 2400                | 2401                                                 | 0.04       | 832                         | 2398           | 0.08       | 416                         | 2400           | 0.00       | 383                         | 2404           | 0.16       | 103                         |

| 9600                | 9615                                                 | 0.16       | 207                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 95                          | 9615           | 0.16       | 25                          |

| 10417               | 10417                                                | 0          | 191                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 87                          | 10417          | 0.00       | 23                          |

| 19.2k               | 19.23k                                               | 0.16       | 103                         | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 47                          | 19.23k         | 0.16       | 12                          |

| 57.6k               | 57.14k                                               | -0.79      | 34                          | 58.82k         | 2.12       | 16                          | 57.60k         | 0.00       | 15                          | —              | _          | _                           |

| 115.2k              | 117.6k                                               | 2.12       | 16                          | 111.1k         | -3.55      | 8                           | 115.2k         | 0.00       | 7                           | _              | —          | _                           |

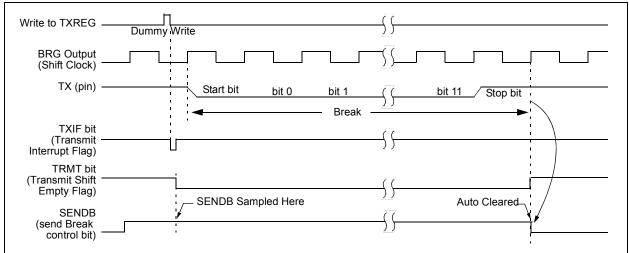

# 25.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 25-9 for the timing of the Break character sequence.

#### 25.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

### 25.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- · RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 25.3.3** "Auto-Wake-up on **Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

### FIGURE 25-9: SEND BREAK CHARACTER SEQUENCE

# 27.10 LCD Interrupts

The LCD module provides an interrupt in two cases. An interrupt when the LCD controller goes from active to inactive controller. An interrupt also provides unframed boundaries for Type B waveform. The LCD timing generation provides an interrupt that defines the LCD frame timing.

#### 27.10.1 LCD INTERRUPT ON MODULE SHUTDOWN

An LCD interrupt is generated when the module completes shutting down (LCDA goes from '1' to '0').

# 27.10.2 LCD FRAME INTERRUPTS

A new frame is defined to begin at the leading edge of the COM0 common signal. The interrupt will be set immediately after the LCD controller completes accessing all pixel data required for a frame. This will occur at a fixed interval before the frame boundary (TFINT), as shown in Figure 27-19. The LCD controller will begin to access data for the next frame within the interval from the interrupt to when the controller begins to access data after the interrupt (TFWR). New data must be written within TFWR, as this is when the LCD controller will begin to access the data for the next frame.

When the LCD driver is running with Type-B waveforms and the LMUX<1:0> bits are not equal to '00' (static drive), there are some additional issues that must be addressed. Since the DC voltage on the pixel takes two frames to maintain zero volts, the pixel data must not change between subsequent frames. If the pixel data were allowed to change, the waveform for the odd frames would not necessarily be the complement of the waveform generated in the even frames and a DC component would be introduced into the panel. Therefore, when using Type-B waveforms, the user must synchronize the LCD pixel updates to occur within a subframe after the frame interrupt.

To correctly sequence writing while in Type-B, the interrupt will only occur on complete phase intervals. If the user attempts to write when the write is disabled, the WERR bit of the LCDCON register is set and the write does not occur.

| Note: | The LCD frame interrupt is not generated |

|-------|------------------------------------------|

|       | when the Type-A waveform is selected     |

|       | and when the Type-B with no multiplex    |

|       | (static) is selected.                    |

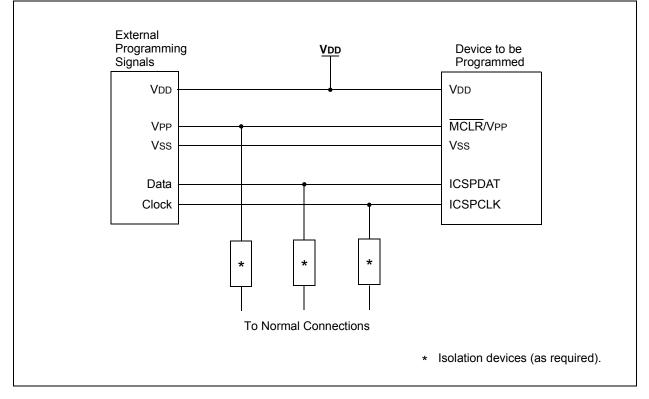

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

| TABLE 30-4: CLKOUT AND I/O TIMING PARAMETERS |

|----------------------------------------------|

|----------------------------------------------|

|              | Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                              |               |          |          |       |                              |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|--|--|--|--|

| Param<br>No. | Sym.                                                                                                                     | Characteristic                                               | Min.          | Тур†     | Max.     | Units | Conditions                   |  |  |  |  |

| OS11         | TosH2ckL                                                                                                                 | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              |               | _        | 70       | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS12         | TosH2ckH                                                                                                                 | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | —             | _        | 72       | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS13         | TckL2ioV                                                                                                                 | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | _        | 20       | ns    |                              |  |  |  |  |

| OS14         | TioV2ckH                                                                                                                 | Port input valid before CLKOUT↑ <sup>(1)</sup>               | Tosc + 200 ns | _        | _        | ns    |                              |  |  |  |  |

| OS15         | TosH2ioV                                                                                                                 | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS16         | TosH2iol                                                                                                                 | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            | _        | _        | ns    | VDD = 3.3-5.0V               |  |  |  |  |

| OS17         | TioV2osH                                                                                                                 | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | _        | _        | ns    |                              |  |  |  |  |

| OS18         | TioR                                                                                                                     | Port output rise time                                        | _             | 40<br>15 | 72<br>32 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |  |  |  |  |

| OS19         | TioF                                                                                                                     | Port output fall time                                        | _             | 28<br>15 | 55<br>30 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |  |  |  |  |

| OS20*        | Tinp                                                                                                                     | INT pin input high or low time                               | 25            | —        |          | ns    |                              |  |  |  |  |

| OS21*        | Tioc                                                                                                                     | Interrupt-on-change new input level time                     | 25            | _        | _        | ns    |                              |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

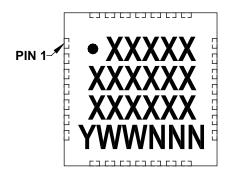

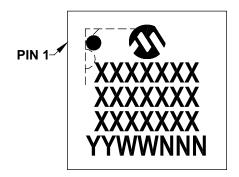

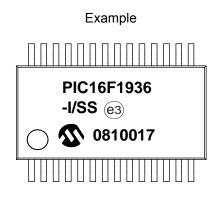

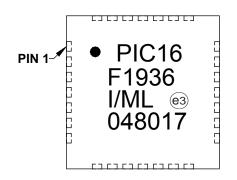

# Package Marking Information (Continued)

28-Lead SSOP (5.30 mm)

28-Lead UQFN (4x4x0.5 mm)

40-Lead UQFN (5x5x0.5 mm)

Example

Example