#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1934-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TAB        | LE 2        | 2:          | _           | 40/4        | 14-P   | IN SU         | MMA          | RY(PIC1                          | 6(L)F1              | 934/7)             |                                             |        |                   |       |             |         |                         |

|------------|-------------|-------------|-------------|-------------|--------|---------------|--------------|----------------------------------|---------------------|--------------------|---------------------------------------------|--------|-------------------|-------|-------------|---------|-------------------------|

| 0/         | 40-Pin PDIP | 40-Pin UQFN | 44-Pin TQFP | 44-Pin QFN  | ANSEL  | A/D           | Cap Sense    | Comparator                       | SR Latch            | Timers             | ссь                                         | EUSART | MSSP              | гср   | Interrupt   | dn-Iluq | Basic                   |

| RA0        | 2           | 17          | 19          | 19          | Y      | AN0           | —            | C12IN0-/<br>C2OUT <sup>(1)</sup> | SRNQ <sup>(1)</sup> |                    |                                             | —      | SS <sup>(1)</sup> | SEG12 | —           |         | VCAP                    |

| RA1        | 3           | 18          | 20          | 20          | Y      | AN1           | _            | C12IN1-                          | _                   | -                  | _                                           | _      | _                 | SEG7  | —           | _       | _                       |

| RA2        | 4           | 19          | 21          | 21          | Y      | AN2/<br>VREF- | —            | C2IN+/<br>DACOUT                 | —                   | _                  | _                                           | —      | —                 | COM2  | —           | _       | —                       |

| RA3        | 5           | 20          | 22          | 22          | Y      | AN3/<br>VREF+ | —            | C1IN+                            | —                   | _                  | _                                           | —      | —                 | SEG15 | —           | —       | —                       |

| RA4        | 6           | 21          | 23          | 23          | Y      | —             | CPS6         | C10UT                            | SRQ                 | T0CKI              |                                             | -      | —                 | SEG4  |             | I       | _                       |

| RA5        | 7           | 22          | 24          | 24          | Y      | AN4           | CPS7         | C2OUT <sup>(1)</sup>             | SRNQ <sup>(1)</sup> |                    |                                             | —      | SS <sup>(1)</sup> | SEG5  | -           | I       | VCAP                    |

| RA6        | 14          | 29          | 31          | 33          | _      | -             | _            | _                                | _                   | _                  | _                                           | _      | _                 | SEG1  |             | _       | OSC2/<br>CLKOUT<br>VCAP |

| RA7        | 13          | 28          | 30          | 32          | —      | —             | —            | -                                | —                   |                    | -                                           | —      | —                 | SEG2  | —           | -       | OSC1/<br>CLKIN          |

| RB0        | 33          | 8           | 8           | 9           | Y      | AN12          | CPS0         | _                                | SRI                 | _                  | _                                           | —      | —                 | SEG0  | INT/<br>IOC | Y       | —                       |

| RB1        | 34          | 9           | 9           | 10          | Y      | AN10          | CPS1         | C12IN3-                          | —                   |                    | _                                           | —      | —                 | VLCD1 | IOC         | Y       | —                       |

| RB2        | 35          | 10          | 10          | 11          | Y      | AN8           | CPS2         |                                  | _                   |                    |                                             | _      | _                 | VLCD2 | IOC         | Υ       | _                       |

| RB3        | 36          | 11          | 11          | 12          | Y      | AN9           | CPS3         | C12IN2-                          | —                   |                    | CCP2 <sup>(1)</sup> /<br>P2A <sup>(1)</sup> | —      | _                 | VLCD3 | IOC         | Y       | _                       |

| RB4        | 37          | 12          | 14          | 14          | Y      | AN11          | CPS4         | _                                | —                   |                    |                                             | —      | —                 | COM0  | IOC         | Y       | —                       |

| RB5        | 38          | 13          | 15          | 15          | Y      | AN13          | CPS5         |                                  | _                   | T1G <sup>(1)</sup> | CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> | —      | —                 | COM1  | IOC         | Y       | —                       |

| RB6        | 39          | 14          | 16          | 16          | —      | -             | —            |                                  | _                   | —                  |                                             | —      | —                 | SEG14 | IOC         | Y       | ICSPCLK/<br>ICDCLK      |

| RB7        | 40          | 15          | 17          | 17          | _      | _             | _            | _                                | _                   | _                  | _                                           | _      | —                 | SEG13 | IOC         | Y       | ICSPDAT/<br>ICDDAT      |

| RC0        | 15          | 30          | 32          | 34          | -      | —             | —            | -                                | _                   | T1OSO/<br>T1CKI    | P2B <sup>(1)</sup>                          | —      | —                 |       | —           | -       | —                       |

| RC1        | 16          | 31          | 35          | 35          | -      | _             |              | _                                | _                   | T10SI              | CCP2 <sup>(1)</sup> /<br>P2A <sup>(1)</sup> | _      | _                 | _     | _           | -       | _                       |

| RC2        | 17          | 32          | 36          | 36          | -      | -             |              | _                                | _                   |                    | CCP1/<br>P1A                                | —      |                   | SEG3  | _           | _       | _                       |

| RC3        | 18          | 33          | 37          | 37          | -      | —             | —            | -                                | —                   |                    | -                                           | —      | SCK/SCL           | SEG6  | _           | _       | _                       |

| RC4        | 23          | 38          | 42          | 42          | —      |               |              | —                                | _                   | T1G <sup>(1)</sup> | —                                           | -      | SDI/SDA           | SEG11 | —           | _       | —                       |

| RC5        | 24          | 39          | 43          | 43          | —      | _             | _            | _                                | _                   | _                  | _                                           | -      | SDO               | SEG10 | _           | _       | _                       |

| RC6        | 25          | 40          | 44          | 44          |        | _             |              | _                                |                     | —                  | _                                           | TX/CK  | _                 | SEG9  |             | _       |                         |

| RC7        | 26          | 1           | 1           | 1           |        |               |              |                                  | _                   | _                  |                                             | RX/DT  | —                 | SEG8  | _           | _       |                         |

| RD0<br>RD1 | 19<br>20    | 34<br>35    | 38<br>39    | 38<br>39    | Y<br>Y | _             | CPS8<br>CPS9 | _                                | _                   |                    | CCP4                                        | _      |                   | COM3  | _           | _       | _                       |

| RD2        | 21          | 36          | 40          | 40          | Y      | _             | CPS10        | _                                | _                   | _                  | P2B <sup>(1)</sup>                          | _      | _                 | _     | _           | _       | _                       |

| RD3        | 22          | 37          | 41          | 41          | Y      | _             | CPS11        | _                                | _                   | -                  | P2C                                         | _      |                   | SEG16 | _           | _       | _                       |

| RD4        | 27          | 2           | 2           | 2           | Y      | _             | CPS12        | _                                | _                   | _                  | P2D                                         |        | _                 | SEG17 | -           | _       | _                       |

| RD5        | 28          | 3           | 3           | 3           | Y      | _             | CPS13        | _                                | _                   | _                  | P1B                                         | _      | _                 | SEG18 | —           | _       | _                       |

| RD6        | 29          | 4           | 4           | 4           | Y      | _             | CPS14        | _                                | —                   | _                  | P1C                                         | —      | —                 | SEG19 | —           | _       | _                       |

| RD7        | 30          | 5           | 5           | 5           | Y      | _             | CPS15        | _                                | —                   | _                  | P1D                                         | —      | —                 | SEG20 | -           | —       | —                       |

| RE0        | 8           | 23          | 25          | 25          | Y      | AN5           | —            | _                                | _                   | _                  | CCP3 <sup>(1)</sup><br>P3A <sup>(1)</sup>   | _      | —                 | SEG21 | —           | —       | _                       |

| RE1        | 9           | 24          | 26          | 26          | Y      | AN6           | —            |                                  | —                   |                    | P3B                                         | —      | —                 | SEG22 | —           |         | —                       |

| RE2        | 10          | 25          | 27          | 27          | Y      | AN7           | —            |                                  | _                   | _                  | CCP5                                        | _      |                   | SEG23 | —           | I       |                         |

| RE3        | 1           | 16          | 18          | 18          | —      | _             | _            | _                                | _                   | _                  | _                                           | _      | _                 | _     | _           | Y       | MCLR/VPP                |

| Vdd        | 11,<br>32   | 7,<br>26    | 7,<br>28    | 7,8,<br>28  | —      | —             | —            | —                                | —                   | —                  | —                                           | —      | —                 | _     | —           | —       | VDD                     |

| Vss        | 12,<br>31   | 6,<br>27    | 6,<br>29    | 6,30,<br>31 | —      | —             | -            | _                                | -                   | _                  | _                                           | —      | _                 | _     | —           | —       | Vss                     |

| Note       | 4.          |             | un oti      |             | hom    | avad uai      |              | FCON regis                       | tor                 |                    |                                             |        |                   |       |             |         |                         |

Note 1: Pin functions can be moved using the APFCON register.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

The PIC16(L)F1934/6/7 are described within this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1934/6/7 devices. Table 1-2 shows the pinout descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral              |                             | PIC16F193X | PIC16LF193X |  |  |

|-------------------------|-----------------------------|------------|-------------|--|--|

| ADC                     |                             | •          | •           |  |  |

| Capacitive Sensing Mod  | dule                        | •          | •           |  |  |

| Digital-to-Analog Conve | erter (DAC)                 | •          | •           |  |  |

| EUSART                  |                             | ٠          | •           |  |  |

| Fixed Voltage Reference | e (FVR)                     | •          | •           |  |  |

| LCD                     |                             | ٠          | •           |  |  |

| SR Latch                |                             | •          | •           |  |  |

| Temperature Indicator   |                             | •          | •           |  |  |

| Capture/Compare/PWM     | Capture/Compare/PWM Modules |            |             |  |  |

|                         | ECCP1                       | ٠          | •           |  |  |

|                         | ECCP2                       | •          | •           |  |  |

|                         | ECCP3                       | •          | •           |  |  |

|                         | CCP4                        | ٠          | •           |  |  |

|                         | CCP5                        | •          | •           |  |  |

| Comparators             |                             |            |             |  |  |

|                         | C1                          | ٠          | •           |  |  |

|                         | C2                          | •          | •           |  |  |

| Operational Amplifiers  |                             |            |             |  |  |

|                         | OPA1                        | •          | •           |  |  |

|                         | OPA2                        | •          | •           |  |  |

| Master Synchronous Se   | erial Ports                 |            |             |  |  |

|                         | MSSP1                       | •          | •           |  |  |

| Timers                  |                             |            |             |  |  |

|                         | Timer0                      | ٠          | •           |  |  |

|                         | Timer1                      | •          | •           |  |  |

|                         | Timer2                      | ٠          | •           |  |  |

|                         | Timer4                      | ٠          | •           |  |  |

|                         | Timer6                      | •          | •           |  |  |

### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |             |         |      |

|-----------|-------------|---------|------|

| RETLW     | DATA0       | ;Index0 | data |

| RETLW     | DATA1       | ;Index1 | data |

| RETLW     | DATA2       |         |      |

| RETLW     | DATA3       |         |      |

| my_functi | on          |         |      |

| ; LO      | IS OF CODE. |         |      |

| MOVLW     | LOW cons    | tants   |      |

| MOVWF     | FSR1L       |         |      |

| MOVLW     | HIGH con    | stants  |      |

| MOVWF     | FSR1H       |         |      |

| MOVIW     | 0[FSR1]     |         |      |

| ;THE PROG | RAM MEMORY  | IS IN W |      |

|           |             |         |      |

# 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

# 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation of the PIC16(L)F1934/6/7. These registers are listed below:

- INDF0

- INDF1

- PCL

- STATUS

- FSR0 Low

- FSR0 High

- FSR1 Low

- FSR1 High

- BSR

- WREG

- PCLATH

- INTCON

Note: The core registers are the first 12 addresses of every data memory bank.

#### **TABLE 3-12:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address  | Name                         | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|----------|------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----------------------|---------------------------------|

| Bank 15  | Bank 15 (Continued)          |               |               |               |               |               |               |               |               |                      |                                 |

| 7A6h     | LCDDATA6                     | SEG7<br>COM2  | SEG6<br>COM2  | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2  | SEG2<br>COM2  | SEG1<br>COM2  | SEG0<br>COM2  | XXXX XXXX            | uuuu uuuu                       |

| 7A7h     | LCDDATA7                     | SEG15<br>COM2 | SEG14<br>COM2 | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG9<br>COM2  | SEG8<br>COM2  | XXXX XXXX            | uuuu uuuu                       |

| 7A8h     | LCDDATA8 <sup>(</sup><br>3)  | SEG23<br>COM2 | SEG22<br>COM2 | SEG21<br>COM2 | SEG20<br>COM2 | SEG19<br>COM2 | SEG18<br>COM2 | SEG17<br>COM2 | SEG16<br>COM2 | XXXX XXXX            | uuuu uuuu                       |

| 7A9h     | LCDDATA9                     | SEG7<br>COM3  | SEG6<br>COM3  | SEG5<br>COM3  | SEG4<br>COM3  | SEG3<br>COM3  | SEG2<br>COM3  | SEG1<br>COM3  | SEG0<br>COM3  | XXXX XXXX            | uuuu uuuu                       |

| 7AAh     | LCDDATA1<br>0                | SEG15<br>COM3 | SEG14<br>COM3 | SEG13<br>COM3 | SEG12<br>COM3 | SEG11<br>COM3 | SEG10<br>COM3 | SEG9<br>COM3  | SEG8<br>COM3  | XXXX XXXX            | uuuu uuuu                       |

| 7ABh     | LCDDATA11 <sup>(</sup><br>3) | SEG23<br>COM3 | SEG22<br>COM3 | SEG21<br>COM3 | SEG20<br>COM3 | SEG19<br>COM3 | SEG18<br>COM3 | SEG17<br>COM3 | SEG16<br>COM3 | XXXX XXXX            | uuuu uuuu                       |

| 7ACh     | —                            | Unimplemer    | nted          |               |               |               |               |               |               | -                    | —                               |

| <br>7EFh |                              |               |               |               |               |               |               |               |               |                      |                                 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred Note 1: to the upper byte of the program counter.

2: These registers can be addressed from any bank.

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

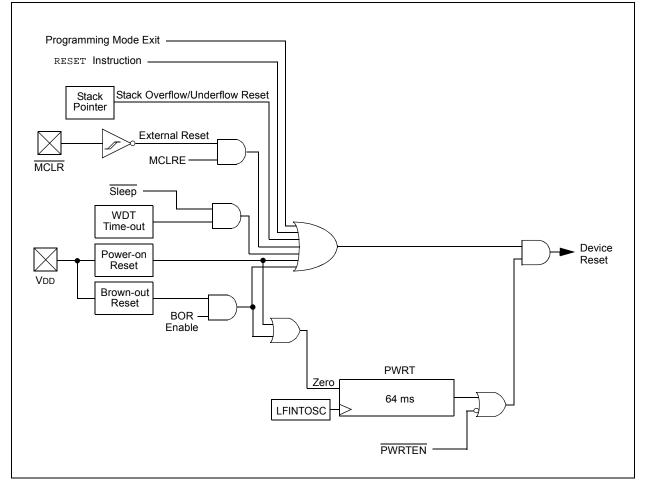

# 6.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- Stack Overflow

- Stack Underflow

- Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 6-1.

#### FIGURE 6-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 15.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- · Channel selection

- · ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

#### 15.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined  |

|-------|---------------------------------------------|

|       | as a digital input may cause the input buf- |

|       | fer to conduct excess current.              |

#### 15.1.2 CHANNEL SELECTION

There are 17 channel selections available:

- AN<13:0> pins

- · Temperature Indicator

- DAC Output

- FVR (Fixed Voltage Reference) Output

Refer to Section 16.0 "Temperature Indicator Module", Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these channel selections.

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 15.2 "ADC Operation"** for more information.

#### 15.1.3 ADC VOLTAGE REFERENCE

The ADPREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- Vdd

- FVR 2.048V

- FVR 4.096V (Not available on LF devices)

The ADNREF bits of the ADCON1 register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 14.0** "Fixed Voltage Reference (FVR)" for more details on the fixed voltage reference.

### 15.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- · Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- · FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 15-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in the applicable Electrical Specifications Chapter for more information. Table 15-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

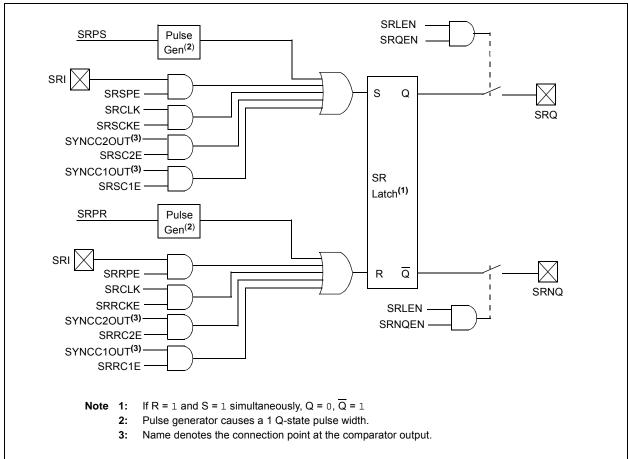

#### FIGURE 19-1: SR LATCH SIMPLIFIED BLOCK DIAGRAM

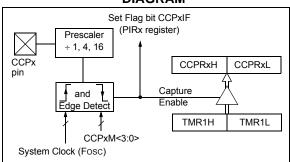

# 23.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Figure 23-1 shows a simplified diagram of the Capture operation.

#### 23.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON register. Refer to **Section 12.1 "Alternate Pin Function"** for more details.

Note: If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 23-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

### 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

# 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 23-1 demonstrates the code to perform this function.

### EXAMPLE 23-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL CCPxCON  | ;Set Bank bits to point |

|------------------|-------------------------|

|                  | ;to CCPxCON             |

| CLRF CCPxCON     | ;Turn CCP module off    |

| MOVLW NEW_CAPT_P | 5;Load the W reg with   |

|                  | ;the new prescaler      |

|                  | ;move value and CCP ON  |

| MOVWF CCPxCON    | ;Load CCPxCON with this |

|                  | ;value                  |

# 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

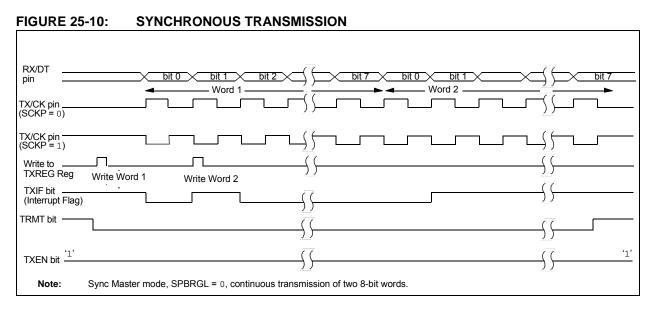

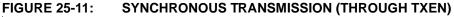

# TABLE 25-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | —      | SCKP   | BRG16  | -      | WUE    | ABDEN  | 302                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 99                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 102                 |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 301                 |

| SPBRGL  |                               |        |        | BRG    | <7:0>  |        |        |        | 303*                |

| SPBRGH  |                               |        |        | BRG<   | :15:8> |        |        |        | 303*                |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 142                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        |        | 293*   |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 300                 |

Legend: — = unimplemented read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

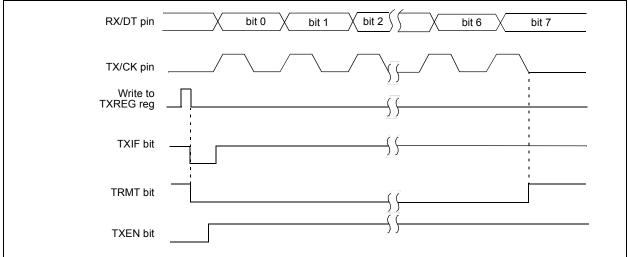

#### REGISTER 27-2: LCDPS: LCD PHASE REGISTER

| R/W-0/0         | R/W-0/0                                        | R-0/0                          | R-0/0             | R/W-0/0        | R/W-0/0          | R/W-1/1          | R/W-1/1      |  |  |  |

|-----------------|------------------------------------------------|--------------------------------|-------------------|----------------|------------------|------------------|--------------|--|--|--|

| WFT             | BIASMD                                         | LCDA                           | WA                |                | LP<              | 3:0>             |              |  |  |  |

| bit 7           |                                                |                                |                   |                |                  |                  | bit C        |  |  |  |

|                 |                                                |                                |                   |                |                  |                  |              |  |  |  |

| Legend:         |                                                |                                |                   |                |                  |                  |              |  |  |  |

| R = Readable    | e bit                                          | W = Writable                   | bit               | U = Unimpler   | mented bit, read | l as '0'         |              |  |  |  |

| u = Bit is unc  | hanged                                         | x = Bit is unk                 | nown              | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is se | t                                              | '0' = Bit is cle               | ared              | C = Only clea  | arable bit       |                  |              |  |  |  |

|                 |                                                | <b>T T T T</b>                 |                   |                |                  |                  |              |  |  |  |

| bit 7           | WFT: Wavefo                                    | • •                            | on oosh from      |                |                  |                  |              |  |  |  |

|                 |                                                | phase changes<br>phase changes |                   |                |                  |                  |              |  |  |  |

| bit 6           | BIASMD: Bia                                    | as Mode Select                 | bit               |                |                  |                  |              |  |  |  |

|                 | When LMUX                                      | <1:0> = 00:                    |                   |                |                  |                  |              |  |  |  |

|                 | 0 = Static Bia<br>When LMUX                    | as mode (do no                 | t set this bit to | oʻ1')          |                  |                  |              |  |  |  |

|                 |                                                |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1 = 1/2 Bias mode<br>0 = 1/3 Bias mode         |                                |                   |                |                  |                  |              |  |  |  |

|                 | <u>When LMUX&lt;1:0&gt; = 10:</u>              |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1 = 1/2 Bias mode                              |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0 = 1/3 Bias mode<br>When LMUX<1:0> = 11:      |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0 = 1/3 Bias mode (do not set this bit to '1') |                                |                   |                |                  |                  |              |  |  |  |

| bit 5           | LCDA: LCD Active Status bit                    |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1 = LCD Driv                                   | iver module is active          |                   |                |                  |                  |              |  |  |  |

|                 | 0 = LCD Driv                                   | er module is in                | active            |                |                  |                  |              |  |  |  |

| bit 4           | WA: LCD Wr                                     | ite Allow Status               | s bit             |                |                  |                  |              |  |  |  |

|                 |                                                | o the LCDDATA                  |                   |                |                  |                  |              |  |  |  |

| bit 3-0         | <b>LP&lt;3:0&gt;:</b> LC                       | D Prescaler Se                 | election bits     |                |                  |                  |              |  |  |  |

|                 | 1111 = <b>1</b> : <b>1</b> 6                   |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1110 = 1:15                                    |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1101 = 1:14<br>1100 = 1:13                     |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1011 = 1:12                                    |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1010 = <b>1:11</b>                             |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1001 = 1:10<br>1000 = 1:9                      |                                |                   |                |                  |                  |              |  |  |  |

|                 | 1000 = 1.9<br>0111 = 1.8                       |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0110 = 1:7                                     |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0101 = 1:6                                     |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0100 = 1:5                                     |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0011 = 1:4<br>0010 = 1:3                       |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0001 = 1:2                                     |                                |                   |                |                  |                  |              |  |  |  |

|                 | 0000 = 1:1                                     |                                |                   |                |                  |                  |              |  |  |  |

FIGURE 27-12: TYPE-B WAVEFORMS IN 1/2 MUX, 1/3 BIAS DRIVE

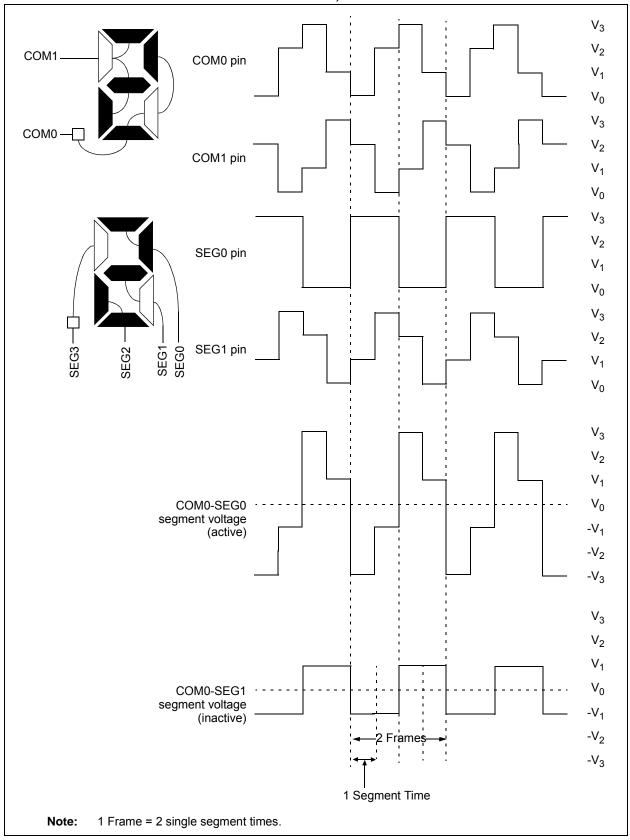

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

| ΜΟΥΨΙ            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} n \in [0,1] \\ mm \in [00,01,10,11] \\ -32 \leq k \leq 31 \end{array}$                                                                                                                                                                                                                                                                                                                                                 |

| Operation:       | $\label{eq:W} \begin{split} W &\rightarrow INDFn \\ \text{Effective address is determined by} \\ \bullet \ FSR + 1 \ (\text{preincrement}) \\ \bullet \ FSR + 1 \ (\text{predecrement}) \\ \bullet \ FSR + k \ (\text{relative offset}) \\ \text{After the Move, the FSR value will be} \\ \text{either:} \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP     |  |

|---------|--|

| Syntax: |  |

| Syntax:          | [label] NOP   |

|------------------|---------------|

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

**No Operation**

| OPTION           | Load OPTION_REG Register with W                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] OPTION                                                                                            |

| Operands:        | None                                                                                                      |

| Operation:       | $(W) \rightarrow OPTION\_REG$                                                                             |

| Status Affected: | None                                                                                                      |

| Description:     | Move data from W register to<br>OPTION_REG register.                                                      |

| Words:           | 1                                                                                                         |

| Cycles:          | 1                                                                                                         |

| Example:         | OPTION                                                                                                    |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.             |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

# 30.1 DC Characteristics: PIC16(L)F1934/6/7-I/E (Industrial, Extended)

| PIC16LF1934/36/37 |           |                                                                                                                                                                                                                                              | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |     |            |        |                                                                                                                                    |  |

|-------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|--------|------------------------------------------------------------------------------------------------------------------------------------|--|

| PIC16F1           | 934/36/37 | Standard Operating Conditions (unless otherwise states of the conditions)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for induction of the conditions $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended of the conditions |                                                                                                                                                                                                                                                                |     |            |        |                                                                                                                                    |  |

| Param.<br>No.     | Sym.      | Characteristic                                                                                                                                                                                                                               | Min. Typ† Max. Units                                                                                                                                                                                                                                           |     |            | Units  | Conditions                                                                                                                         |  |

| D001              | Vdd       | Supply Voltage                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                |     |            |        |                                                                                                                                    |  |

|                   |           | PIC16LF1934/36/37                                                                                                                                                                                                                            | 1.8<br>2.3                                                                                                                                                                                                                                                     | _   | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                                                                  |  |

| D001              |           | PIC16F1934/36/37                                                                                                                                                                                                                             | 1.8<br>2.3                                                                                                                                                                                                                                                     | _   | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                                                                  |  |

| D002*             | Vdr       | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                |     |            |        |                                                                                                                                    |  |

|                   |           | PIC16LF1934/36/37                                                                                                                                                                                                                            | 1.5                                                                                                                                                                                                                                                            | _   | _          | V      | Device in Sleep mode                                                                                                               |  |

| D002*             |           | PIC16F1934/36/37                                                                                                                                                                                                                             | 1.7                                                                                                                                                                                                                                                            | _   | _          | V      | Device in Sleep mode                                                                                                               |  |

|                   | VPOR*     | Power-on Reset Release Voltage                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                | 1.6 | _          | V      |                                                                                                                                    |  |

|                   | VPORR*    | Power-on Reset Rearm Voltage                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                |     |            |        |                                                                                                                                    |  |

|                   |           | PIC16LF1934/36/37                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                              | 0.8 | —          | V      | Device in Sleep mode                                                                                                               |  |

|                   |           | PIC16F1934/36/37                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                              | 1.7 | —          | V      | Device in Sleep mode                                                                                                               |  |

| D003              | VADFVR    | Fixed Voltage Reference Voltage<br>for ADC                                                                                                                                                                                                   | -8                                                                                                                                                                                                                                                             |     | 6          | %      | $\begin{array}{l} 1.024V, \ V\text{DD} \geq 2.5V \\ 2.048V, \ V\text{DD} \geq 2.5V \\ 4.096V, \ V\text{DD} \geq 4.75V \end{array}$ |  |

| D003A             | VCDAFVR   | Fixed Voltage Reference Voltage<br>for Comparator and DAC                                                                                                                                                                                    | -11                                                                                                                                                                                                                                                            |     | 7          | %      | $\begin{array}{l} 1.024V, \ VDD \geq 2.5V\\ 2.048V, \ VDD \geq 2.5V\\ 4.096V, \ VDD \geq 4.75V \end{array}$                        |  |

| D003B             | VLCDFVR   | Fixed Voltage Reference Voltage<br>for LCD Bias                                                                                                                                                                                              | -11                                                                                                                                                                                                                                                            | —   | 10         | %      | $3.072V, \text{VDD} \geq 3.6V$                                                                                                     |  |

| D004*             | SVDD      | VDD Rise Rate to ensure internal<br>Power-on Reset signal                                                                                                                                                                                    | 0.05                                                                                                                                                                                                                                                           | _   | _          | V/ms   | See Section 6.1 "Power-on Reset (POR)" for details.                                                                                |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

**2:** PLL required for 32 MHz operation.

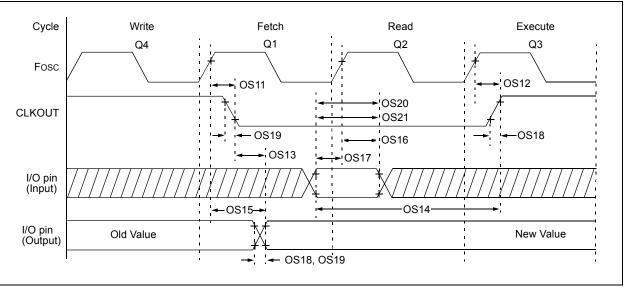

# 30.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| <u>z. 1ppo</u> |                                      |     |                |

|----------------|--------------------------------------|-----|----------------|

| т              |                                      |     |                |

| F              | Frequency                            | Т   | Time           |

| Lowerc         | ase letters (pp) and their meanings: |     |                |

| рр             |                                      |     |                |

| сс             | CCP1                                 | OSC | OSC1           |

| ck             | CLKOUT                               | rd  | RD             |

| CS             | CS                                   | rw  | RD or WR       |

| di             | SDI                                  | sc  | SCK            |

| do             | SDO                                  | SS  | SS             |

| dt             | Data in                              | t0  | TOCKI          |

| io             | I/O PORT                             | t1  | T1CKI          |

| mc             | MCLR                                 | wr  | WR             |

| Upperc         | ase letters and their meanings:      |     |                |

| S              |                                      |     |                |

| F              | Fall                                 | Р   | Period         |

| Н              | High                                 | R   | Rise           |

| 1              | Invalid (High-impedance)             | V   | Valid          |

| L              | Low                                  | Z   | High-impedance |

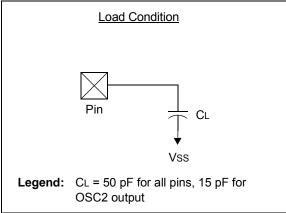

#### FIGURE 30-5: LOAD CONDITIONS

| Param.<br>No. | Symbol | Characteristic |               | Min.       | Тур†       | Max.       | Units    | Conditions |

|---------------|--------|----------------|---------------|------------|------------|------------|----------|------------|

| CS01          | ISRC   | Current Source | High          | -3         | -8         | -15        | μA       |            |

|               |        |                | Medium        | -0.8       | -1.5       | -3         | μA       |            |

|               |        |                | Low           | -0.1       | -0.3       | -0.4       | μA       |            |

| CS02          | Isnk   | Current Sink   | High          | 2.5        | 7.5        | 14         | μA       |            |

|               |        |                | Medium        | 0.6        | 1.5        | 2.9        | μA       |            |

|               |        |                | Low           | 0.1        | 0.25       | 0.6        | μA       |            |

| CS03          | VСтн   | Cap Threshold  |               | _          | 0.8        | —          | mV       |            |

| CS04          | VCTL   | Cap Threshold  |               |            | 0.4        | —          | mV       |            |

| CS05          | VCHYST | Cap Hysteresis | High          | 350        | 525        | 725        | mV       |            |

|               |        | (VCTH-VCTL)    | Medium<br>Low | 250<br>175 | 375<br>300 | 500<br>425 | mV<br>mV |            |

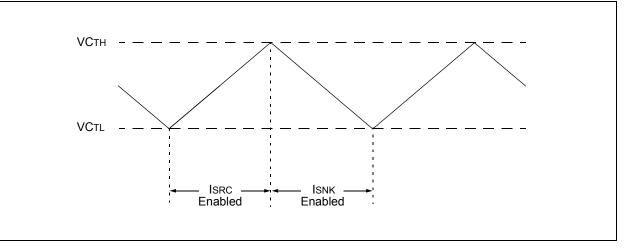

# TABLE 30-17: CAP SENSE OSCILLATOR SPECIFICATIONS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### FIGURE 30-22: CAP SENSE OSCILLATOR

# Package Marking Information (Continued)

44-Lead TQFP (10x10x1 mm)

44-Lead QFN (8x8x0.9 mm)

Example

For the most current package drawings, please see the Microchip Packaging Specification located at

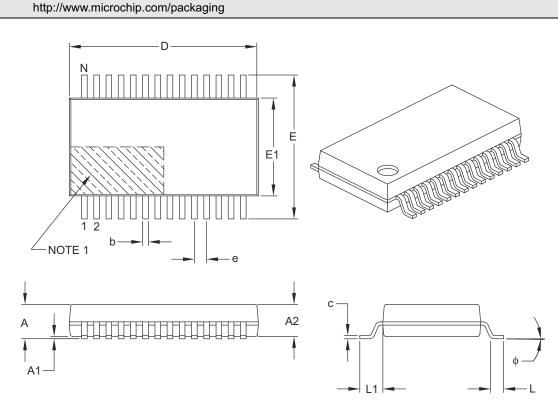

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units            |          |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|----------|-------------|--|--|--|

|                          | Dimension Limits | MIN      | NOM      | MAX         |  |  |  |

| Number of Pins           | N                |          | 28       |             |  |  |  |

| Pitch                    | е                |          | 0.65 BSC |             |  |  |  |

| Overall Height           | А                | -        | -        | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05     | -        | -           |  |  |  |

| Overall Width            | E                | 7.40     | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30     | 5.60        |  |  |  |

| Overall Length           | D                | 9.90     | 10.20    | 10.50       |  |  |  |

| Foot Length              | L                | 0.55     | 0.75     | 0.95        |  |  |  |

| Footprint                | L1               | 1.25 REF |          |             |  |  |  |

| Lead Thickness           | С                | 0.09     | -        | 0.25        |  |  |  |

| Foot Angle               | ф                | 0°       | 4°       | 8°          |  |  |  |

| Lead Width               | b                | 0.22     | -        | 0.38        |  |  |  |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B