Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

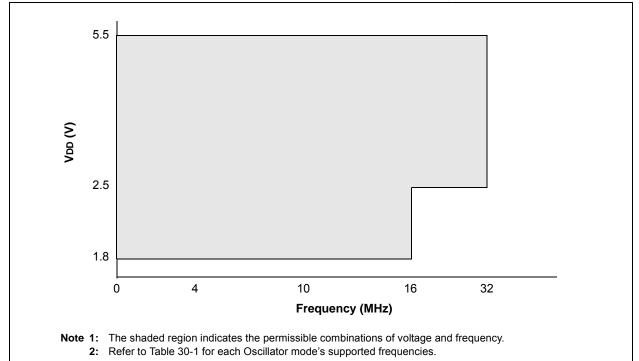

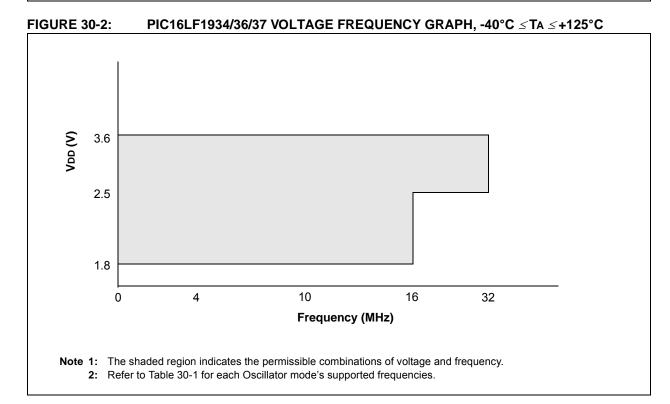

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1934-e-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE                            | 3-1Z. C | SPECIAL                    | FUNCTIC          | IN REGIS        | DIER SUN        | INIART (C      |            | בט)   |       |               |      |                     |      |

|----------------------------------|---------|----------------------------|------------------|-----------------|-----------------|----------------|------------|-------|-------|---------------|------|---------------------|------|

| Address                          | Name    | Bit 7                      | Bit 6            | Bit 5           | Bit 4           | Bit 3          | Bit 2      | Bit 1 | Bit 0 | Value<br>POR, |      | Value<br>oth<br>Res | ner  |

| Banks 1                          | 6-30    |                            |                  |                 |                 |                |            |       |       |               |      |                     |      |

| x00h/<br>x80h <sup>(2)</sup>     | INDF0   | Addressing<br>(not a physi |                  | ses contents o  | of FSR0H/FSF    | R0L to address | data memor | ý     |       | xxxx          | xxxx | xxxx                | xxxx |

| x00h/<br>x81h <sup>(2)</sup>     | INDF1   | Addressing<br>(not a physi |                  | ses contents o  | of FSR1H/FSF    | R1L to address | data memor | y     |       | xxxx          | XXXX | xxxx                | xxxx |

| x02h/<br>x82h <sup>(2)</sup>     | PCL     | Program Co                 | ounter (PC) Le   | ast Significant | t Byte          |                |            |       |       | 0000          | 0000 | 0000                | 0000 |

| x03h/<br>x83h <sup>(2)</sup>     | STATUS  | -                          | —                | _               | TO              | PD             | Z          | DC    | С     | 1             | 1000 | d                   | quuu |

| x04h/<br>x84h <sup>(2)</sup>     | FSR0L   | Indirect Dat               | a Memory Add     | Iress 0 Low P   | ointer          |                |            |       |       | 0000          | 0000 | uuuu                | uuuu |

| x05h/<br>x85h <b>(2)</b>         | FSR0H   | Indirect Dat               | a Memory Add     | lress 0 High P  | Pointer         |                |            |       |       | 0000          | 0000 | 0000                | 0000 |

| x06h/<br>x86h <sup>(2)</sup>     | FSR1L   | Indirect Data              | a Memory Ado     | Iress 1 Low P   | ointer          |                |            |       |       | 0000          | 0000 | uuuu                | uuuu |

| x07h/<br>x87h <sup>(2)</sup>     | FSR1H   | Indirect Data              | a Memory Add     | lress 1 High P  | Pointer         |                |            |       |       | 0000          | 0000 | 0000                | 0000 |

| x08h/<br>x88h <b>(2)</b>         | BSR     | _                          | —                | —               |                 |                | BSR<4:0>   |       |       | 0             | 0000 | 0                   | 0000 |

| x09h/<br>x89h <sup>(2)</sup>     | WREG    | Working Re                 | Working Register |                 |                 |                |            |       | 0000  | 0000          | uuuu | uuuu                |      |

| x0Ah/<br>x8Ah <sup>(1),(2)</sup> | PCLATH  | -                          | Write Buffer f   | or the upper 7  | bits of the Pro | ogram Counter  | r          |       |       | -000          | 0000 | -000                | 0000 |

| x0Bh/<br>x8Bh <sup>(2)</sup>     | INTCON  | GIE                        | PEIE             | TMR0IE          | INTE            | IOCIE          | TMR0IF     | INTF  | IOCIF | 0000          | 0000 | 0000                | 0000 |

| x0Ch/<br>x8Ch                    | —       | Unimpleme                  | nted             |                 |                 |                |            |       |       | -             | -    | _                   | -    |

| x1Fh/<br>x9Fh                    |         |                            |                  |                 |                 |                |            |       |       |               |      |                     |      |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

| R-1/q            | R-0/q                                                              | R-q/q                                                     | R-0/q            | R-0/q           | R-q/q            | R-0/0          | R-0/q        |

|------------------|--------------------------------------------------------------------|-----------------------------------------------------------|------------------|-----------------|------------------|----------------|--------------|

| T1OSCR           | PLLR                                                               | OSTS                                                      | HFIOFR           | HFIOFL          | MFIOFR           | LFIOFR         | HFIOFS       |

| bit 7            |                                                                    |                                                           |                  |                 |                  |                | bit 0        |

|                  |                                                                    |                                                           |                  |                 |                  |                |              |

| Legend:          |                                                                    |                                                           |                  |                 |                  |                |              |

| R = Readable     |                                                                    | W = Writable                                              |                  | -               | mented bit, read |                |              |

| u = Bit is uncl  | •                                                                  | x = Bit is unk                                            |                  |                 | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set |                                                                    | '0' = Bit is cle                                          | ared             | q = Condition   | al               |                |              |

| bit 7            | <u>If T1OSCEN</u><br>1 = Timer1<br>0 = Timer1<br><u>If T1OSCEN</u> | oscillator is rea<br>oscillator is not                    | dy<br>ready      |                 |                  |                |              |

| bit 6            | <b>PLLR</b> 4x PL<br>1 = 4x PLL                                    | L Ready bit                                               |                  |                 |                  |                |              |

| bit 5            | 1 = Runnin                                                         | llator Start-up T<br>g from the clocl<br>g from an interr | c defined by the | e FOSC<2:0>     |                  | guration Word  | 1            |

| bit 4            | 1 = HFINTC                                                         | gh-Frequency Iı<br>DSC is ready<br>DSC is not ready       |                  | or Ready bit    |                  |                |              |

| bit 3            | 1 = HFINTC                                                         | gh-Frequency Ir<br>DSC is at least 2<br>DSC is not 2% a   | 2% accurate      | or Locked bit   |                  |                |              |

| bit 2            | 1 = MFINTO                                                         | edium-Frequen<br>DSC is ready<br>DSC is not read          | -                | illator Ready b | it               |                |              |

| bit 1            | 1 = LFINTO                                                         | w-Frequency In<br>SC is ready<br>SC is not ready          |                  | r Ready bit     |                  |                |              |

| bit 0            | 1 = HFINTC                                                         | gh-Frequency Ir<br>DSC is at least 0<br>DSC is not 0.5%   | ).5% accurate    | or Stable bit   |                  |                |              |

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

#### 12.4 PORTC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 12-12). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 12-11) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

The TRISC register (Register 12-12) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 12.4.1 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-7.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in Table 12-7.

| Pin Name | Function Priority <sup>(1)</sup>                                          |

|----------|---------------------------------------------------------------------------|

| RC0      | T1OSO (Timer1 Oscillator)<br>CCP2/P2B<br>RC0                              |

| RC1      | T1OSI (Timer1 Oscillator)<br>CCP2/P2A<br>RC1                              |

| RC2      | SEG3 (LCD)<br>CCP1/P1A<br>RC2                                             |

| RC3      | SEG6 (LCD)<br>SCL (MSSP)<br>SCK (MSSP)<br>RC3                             |

| RC4      | SEG11 (LCD)<br>SDA (MSSP)<br>RC4                                          |

| RC5      | SEG10 (LCD)<br>SDO (MSSP)<br>RC5                                          |

| RC6      | ISEG9 (LCD)<br>TX (EUSART)<br>CK (EUSART)<br>CCP3/P3A, 28-pin only<br>RC6 |

| RC7      | SEG8 (LCD)<br>DT (EUSART)<br>CCP3/P3B, 28 pin only<br>RC7                 |

TABLE 12-7: PORTC OUTPUT PRIORITY

**Note 1:** Priority listed from highest to lowest.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB | _      | —      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 139                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| IOCBF  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 152                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 152                 |

| IOCBP  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 152                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 138                 |

TABLE 13-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupt-on-Change.

#### 15.2 ADC Operation

#### 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 15.2.6 "A/D Conver-     |

|       | sion Procedure".                         |

#### 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 15.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 15-2: SPECIAL EVENT TRIGGER

| Device            | CCPx/ECCPx |

|-------------------|------------|

| PIC16(L)F1934/6/7 | CCP5       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 23.0 "Capture/Compare/PWM Modules" for more information.

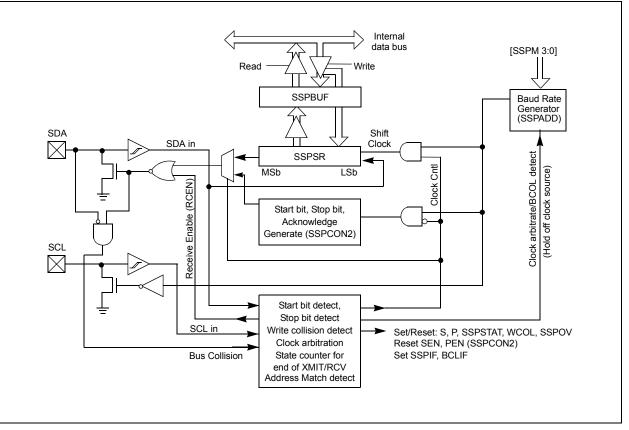

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- Slave mode

- Byte NACKing (Slave mode)

- · Limited Multi-master support

- 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- Clock stretching

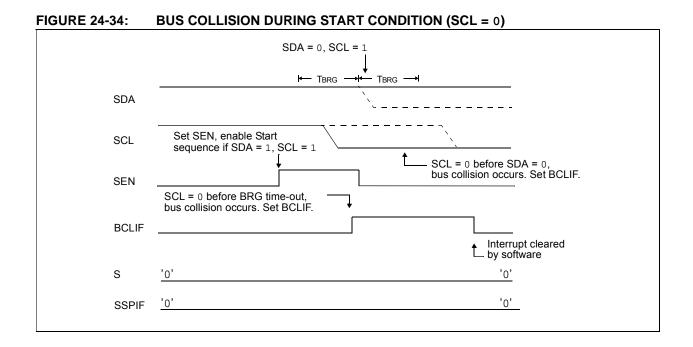

- · Bus collision detection

- · General call address matching

- Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

Figure 24-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 24-3 is a diagram of the  $I^2C$  interface module in Slave mode.

#### FIGURE 24-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

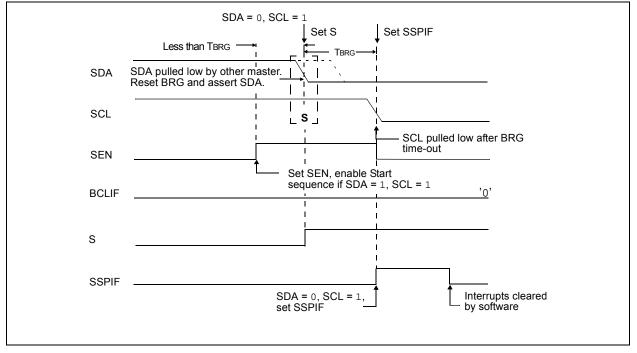

#### FIGURE 24-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

#### REGISTER 24-1: SSPSTAT: SSP STATUS REGISTER

| R/W-0/0          | R/W-0/0                                                | R-0/0                                      | R-0/0                                                            | R-0/0                | R-0/0                | R-0/0              | R-0/0         |

|------------------|--------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------|----------------------|----------------------|--------------------|---------------|

| SMP              | CKE                                                    | D/A                                        | Р                                                                | S                    | R/W                  | UA                 | BF            |

| bit 7            |                                                        |                                            |                                                                  |                      | •                    |                    | bit 0         |

|                  |                                                        |                                            |                                                                  |                      |                      |                    |               |

| Legend:          |                                                        |                                            |                                                                  |                      |                      |                    |               |

| R = Readable bit |                                                        | W = Writable bi                            |                                                                  |                      | ented bit, read as   |                    |               |

| u = Bit is uncha | inged                                                  |                                            | x = Bit is unknown -n/n = Value at POR and BOR/Value at all othe |                      |                      |                    |               |

| '1' = Bit is set |                                                        | '0' = Bit is clear                         | ed                                                               |                      |                      |                    |               |

| bit 7            | SMD. SDI Data                                          | a Input Sample bi                          | +                                                                |                      |                      |                    |               |

|                  | SPI Master mo                                          |                                            | l l                                                              |                      |                      |                    |               |

|                  |                                                        | sampled at end c                           | of data output tir                                               | ne                   |                      |                    |               |

|                  | 0 = Input data                                         | sampled at middl                           | e of data outpu                                                  | t time               |                      |                    |               |

|                  |                                                        | cleared when SP                            | is used in Slav                                                  | re mode              |                      |                    |               |

|                  | $\frac{\ln l^2 C \text{ Master c}}{1 = Slew rate}$     | or Slave mode:<br>control disabled f       | or standard so                                                   | ed mode (100 k       | Hz and 1 MHz)        |                    |               |

|                  |                                                        | control enabled f                          | •                                                                |                      |                      |                    |               |

| bit 6            | CKE: SPI Cloc                                          | k Edge Select bit                          | (SPI mode onl                                                    | y)                   |                      |                    |               |

|                  | In SPI Master of                                       |                                            | - <b>f</b>                                                       |                      |                      |                    |               |

|                  |                                                        | ccurs on transitio<br>ccurs on transitio   |                                                                  |                      |                      |                    |               |

|                  | In I <sup>2</sup> C™ mode                              |                                            |                                                                  |                      |                      |                    |               |

|                  | 1 = Enable inp                                         |                                            |                                                                  | mpliant with SM      | Bus specification    |                    |               |

| bit 5            | D/A: Data/Add                                          | ress bit (I <sup>2</sup> C mod             | e only)                                                          |                      |                      |                    |               |

|                  |                                                        | nat the last byte r<br>nat the last byte r |                                                                  |                      |                      |                    |               |

| bit 4            | <b>P:</b> Stop bit                                     | lat the last byte i                        |                                                                  |                      | 1035                 |                    |               |

|                  | •                                                      | . This bit is clear                        | ed when the MS                                                   | SSP module is d      | sabled, SSPEN is     | cleared.)          |               |

|                  | 1 = Indicates th                                       | nat a Stop bit has<br>is not detected la   | been detected                                                    |                      |                      | ,                  |               |

| bit 3            | S: Start bit                                           |                                            |                                                                  |                      |                      |                    |               |

|                  |                                                        |                                            |                                                                  |                      | sabled, SSPEN is     | cleared.)          |               |

|                  |                                                        | nat a Start bit has<br>is not detected la  |                                                                  | last (this bit is '0 | o' on Reset)         |                    |               |

| bit 2            |                                                        | ite bit information                        |                                                                  |                      |                      |                    |               |

|                  | This bit holds the to the next Star                    | rt bit, Stop bit, or                       | atio <u>n foll</u> owing t<br>not ACK bit                        | he last address r    | natch. This bit is c | nly valid from the | address match |

|                  | 1 = Read                                               | oue.                                       |                                                                  |                      |                      |                    |               |

|                  | 0 = Write                                              |                                            |                                                                  |                      |                      |                    |               |

|                  | In I <sup>2</sup> C Master n                           |                                            |                                                                  |                      |                      |                    |               |

|                  | 1 = Transmit i<br>0 = Transmit i                       | s not in progress                          |                                                                  |                      |                      |                    |               |

|                  |                                                        |                                            |                                                                  | CEN or ACKEN         | will indicate if the | MSSP is in Idle n  | node.         |

| bit 1            |                                                        | ldress bit (10-bit                         |                                                                  |                      |                      |                    |               |

|                  |                                                        | nat the user need<br>bes not need to b     | •                                                                | address in the S     | SSPADD register      |                    |               |

| bit 0            | BF: Buffer Full                                        |                                            |                                                                  |                      |                      |                    |               |

|                  |                                                        | ind I <sup>2</sup> C modes):               |                                                                  |                      |                      |                    |               |

|                  |                                                        | mplete, SSPBUF<br>ot complete, SSP         |                                                                  |                      |                      |                    |               |

|                  | 0 = Receive not<br><u>Transmit (I<sup>2</sup>C not</u> |                                            |                                                                  |                      |                      |                    |               |

|                  | 1 = Data transr                                        | mit in progress (d                         |                                                                  |                      | op bits), SSPBUF     |                    |               |

|                  | 0 = Data transr                                        | mit complete (doe                          | es not include th                                                | ne ACK and Stop      | bits), SSPBUF is     | empty              |               |

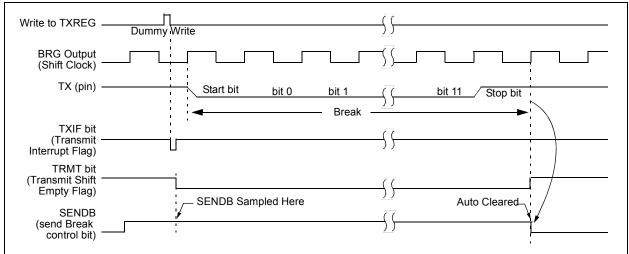

#### 25.3.4 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. A Break character consists of a Start bit, followed by 12 '0' bits and a Stop bit.

To send a Break character, set the SENDB and TXEN bits of the TXSTA register. The Break character transmission is then initiated by a write to the TXREG. The value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit of the TXSTA register indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 25-9 for the timing of the Break character sequence.

#### 25.3.4.1 Break and Sync Transmit Sequence

The following sequence will start a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to enable the Break sequence.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

5. After the Break has been sent, the SENDB bit is reset by hardware and the Sync character is then transmitted.

When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

#### 25.3.5 RECEIVING A BREAK CHARACTER

The Enhanced EUSART module can receive a Break character in two ways.

The first method to detect a Break character uses the FERR bit of the RCSTA register and the Received data as indicated by RCREG. The Baud Rate Generator is assumed to have been initialized to the expected baud rate.

A Break character has been received when;

- · RCIF bit is set

- FERR bit is set

- RCREG = 00h

The second method uses the Auto-Wake-up feature described in **Section 25.3.3** "Auto-Wake-up on **Break**". By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt, and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Detect feature. For both methods, the user can set the ABDEN bit of the BAUDCON register before placing the EUSART in Sleep mode.

#### FIGURE 25-9: SEND BREAK CHARACTER SEQUENCE

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               | U-0                                | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W-0/0          | R/W-1/1               | R/W-1/1          |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|------------------|--|

| R/W-0/0                              | R/W-0/0                                                                                                                                                           | R/C-0/0                                                                                                                                                                                                                       | 0-0                                | 11/00-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10.00 0/0        |                       |                  |  |

| LCDEN                                | SLPEN                                                                                                                                                             | WERR                                                                                                                                                                                                                          |                                    | CS<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | :1:0>            | LMUX                  | <1:0>            |  |

| bit 7                                |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       | bit (            |  |

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

| Legend:                              |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

| R = Readable                         | e bit                                                                                                                                                             | W = Writable bit                                                                                                                                                                                                              |                                    | U = Unimplen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nented bit, read | l as '0'              |                  |  |

| u = Bit is unch                      | nanged                                                                                                                                                            | x = Bit is unknow                                                                                                                                                                                                             | vn                                 | -n/n = Value a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | t POR and BO     | R/Value at all c      | other Resets     |  |

| '1' = Bit is set                     |                                                                                                                                                                   | '0' = Bit is cleare                                                                                                                                                                                                           | d                                  | C = Only clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rable bit        |                       |                  |  |

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

| bit 7                                |                                                                                                                                                                   | Driver Enable bit                                                                                                                                                                                                             |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

|                                      | -                                                                                                                                                                 | = LCD Driver module is enabled                                                                                                                                                                                                |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

| bit 6                                |                                                                                                                                                                   | er module is disat                                                                                                                                                                                                            |                                    | - hit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |                       |                  |  |

|                                      |                                                                                                                                                                   | Driver Enable in                                                                                                                                                                                                              | •                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

|                                      |                                                                                                                                                                   | <ul> <li>= LCD Driver module is disabled in Sleep mode</li> <li>= LCD Driver module is enabled in Sleep mode</li> </ul>                                                                                                       |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                       |                  |  |

|                                      |                                                                                                                                                                   |                                                                                                                                                                                                                               | led in Sleer                       | o mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                       |                  |  |

| bit 5                                | 0 = LCD Driv                                                                                                                                                      |                                                                                                                                                                                                                               | •                                  | p mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                       |                  |  |

| bit 5                                | 0 = LCD Drive<br>WERR: LCD                                                                                                                                        | er module is enab                                                                                                                                                                                                             | bit                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | E LCDPS regis    | ter = 0 (must         | be cleared in    |  |

| bit 5                                | 0 = LCD Drive<br>WERR: LCD<br>1 = LCDDAT<br>software                                                                                                              | er module is enab<br>Write Failed Error<br>An register writte<br>)                                                                                                                                                            | bit                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECDPS regis      | ter = 0 (must         | be cleared in    |  |

|                                      | 0 = LCD Drive<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v                                                                                              | er module is enab<br>Write Failed Error<br>An register writte<br>)<br>vrite error                                                                                                                                             | bit                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e LCDPS regis    | ter = 0 (must         | be cleared in    |  |

| bit 4                                | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen                                                                                 | er module is enab<br>Write Failed Error<br>An register writte<br>)<br>vrite error<br><b>ted:</b> Read as '0'                                                                                                                  | bit<br>n while the                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECDPS regis      | ter = 0 (must         | be cleared in    |  |

| bit 4                                | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo                                                                 | er module is enab<br>Write Failed Error<br>An register writte<br>)<br>vrite error<br>t <b>ed:</b> Read as '0'<br>ock Source Select                                                                                            | bit<br>n while the                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECDPS regis      | ter = 0 (must         | be cleared in    |  |

| bit 4                                | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25                                                 | er module is enab<br>Write Failed Error<br>An register writte<br>)<br>vrite error<br>ted: Read as '0'<br>ock Source Select                                                                                                    | bit<br>n while the                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECDPS regis      | ter = 0 (must         | be cleared in    |  |

| bit 4                                | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC                                   | er module is enab<br>Write Failed Error<br>An register writte<br>vrite error<br>ted: Read as '0'<br>ock Source Select<br>66<br>(Timer1)                                                                                       | bit<br>n while the                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ELCDPS regis     | ter = 0 (must         | be cleared in    |  |

| bit 5<br>bit 4<br>bit 3-2<br>bit 1-0 | 0 = LCD Drive<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO                   | er module is enab<br>Write Failed Error<br>An register writte<br>vrite error<br>ted: Read as '0'<br>ock Source Select<br>66<br>(Timer1)                                                                                       | bit<br>n while the<br>bits         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ECDPS regis      | ter = 0 (must         | be cleared ir    |  |

| bit 4<br>bit 3-2                     | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:      | er module is enab<br>Write Failed Error<br>An register writte<br>vrite error<br>ted: Read as '0'<br>ock Source Select<br>66<br>(Timer1)<br>SC (31 kHz)                                                                        | bit<br>n while the<br>bits         | e WA bit of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LCDPS regis      |                       | be cleared ir    |  |

| bit 4<br>bit 3-2                     | 0 = LCD Drive<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO                   | er module is enab<br>Write Failed Error<br>An register writte<br>vrite error<br>ted: Read as '0'<br>ock Source Select<br>66<br>(Timer1)<br>SC (31 kHz)                                                                        | bit<br>n while the<br>bits<br>bits | e WA bit of the<br>Maximum N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | lumber of Pixe   | ls                    | be cleared ir    |  |

| bit 4<br>bit 3-2                     | 0 = LCD Drivi<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>      | er module is enab<br>Write Failed Error<br>An register writte<br>write error<br>ted: Read as '0'<br>ted: Read as '0'<br>ted: Read as '0'<br>bock Source Select<br>G<br>(Timer1)<br>SC (31 kHz)<br>Commons Select<br>Multiplex | bit<br>n while the<br>bits<br>bits | e WA bit of the<br>Maximum Maximum | lumber of Pixe   | ls<br>L)F1934/7       | – Bias           |  |

| bit 4<br>bit 3-2                     | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:      | er module is enab<br>Write Failed Error<br>An register writte<br>vrite error<br>ted: Read as '0'<br>ock Source Select<br>66<br>(Timer1)<br>SC (31 kHz)<br>Commons Select<br>Multiplex<br>Static (COM0)                        | bit<br>n while the<br>bits<br>bits | Maximum M                                                                                                                                                                                                                                                          | lumber of Pixe   | ls<br>L)F1934/7<br>24 |                  |  |

| bit 4<br>bit 3-2                     | 0 = LCD Driv<br>WERR: LCD<br>1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clc<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0><br>00 | er module is enab<br>Write Failed Error<br>An register writte<br>write error<br>ted: Read as '0'<br>ted: Read as '0'<br>ted: Read as '0'<br>bock Source Select<br>G<br>(Timer1)<br>SC (31 kHz)<br>Commons Select<br>Multiplex | bit<br>n while the<br>bits<br>bits | e WA bit of the<br>Maximum Maximum | lumber of Pixe   | ls<br>L)F1934/7       | - Bias<br>Static |  |

#### REGISTER 27-1: LCDCON: LIQUID CRYSTAL DISPLAY (LCD) CONTROL REGISTER

Note 1: On these devices, COM3 and SEG15 are shared on one pin, limiting the device from driving 64 pixels.

| BCF              | Bit Clear f                          |

|------------------|--------------------------------------|

| Syntax:          | [label]BCF f,b                       |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $0 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is cleared.  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|