Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1934-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

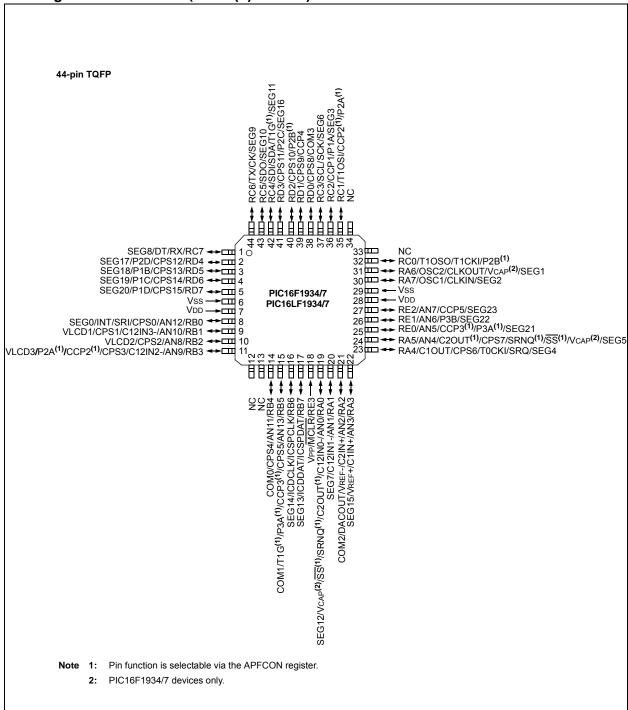

### Pin Diagram – 44-Pin TQFP (PIC16(L)F1934/7)

**NOTES:**

DS41364E-page 36

TABLE 3-8: PIC16(L)F1934/6/7 MEMORY MAP, BANKS 24-31

|      | BANK 24                      |      | BANK 25                      |      | BANK 26                      |      | BANK 27                      |      | BANK 28                      |      | BANK 29                      |      | BANK 30                      |      | BANK 31        |

|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|----------------|

| C00h | INDF0                        | C80h | INDF0                        | D00h | INDF0                        | D80h | INDF0                        | E00h | INDF0                        | E80h | INDF0                        | F00h | INDF0                        | F80h | INDF0          |

| C01h | INDF1                        | C81h | INDF1                        | D01h | INDF1                        | D81h | INDF1                        | E01h | INDF1                        | E81h | INDF1                        | F01h | INDF1                        | F81h | INDF1          |

| C02h | PCL                          | C82h | PCL                          | D02h | PCL                          | D82h | PCL                          | E02h | PCL                          | E82h | PCL                          | F02h | PCL                          | F82h | PCL            |

| C03h | STATUS                       | C83h | STATUS                       | D03h | STATUS                       | D83h | STATUS                       | E03h | STATUS                       | E83h | STATUS                       | F03h | STATUS                       | F83h | STATUS         |

| C04h | FSR0L                        | C84h | FSR0L                        | D04h | FSR0L                        | D84h | FSR0L                        | E04h | FSR0L                        | E84h | FSR0L                        | F04h | FSR0L                        | F84h | FSR0L          |

| C05h | FSR0H                        | C85h | FSR0H                        | D05h | FSR0H                        | D85h | FSR0H                        | E05h | FSR0H                        | E85h | FSR0H                        | F05h | FSR0H                        | F85h | FSR0H          |

| C06h | FSR1L                        | C86h | FSR1L                        | D06h | FSR1L                        | D86h | FSR1L                        | E06h | FSR1L                        | E86h | FSR1L                        | F06h | FSR1L                        | F86h | FSR1L          |

| C07h | FSR1H                        | C87h | FSR1H                        | D07h | FSR1H                        | D87h | FSR1H                        | E07h | FSR1H                        | E87h | FSR1H                        | F07h | FSR1H                        | F87h | FSR1H          |

| C08h | BSR                          | C88h | BSR                          | D08h | BSR                          | D88h | BSR                          | E08h | BSR                          | E88h | BSR                          | F08h | BSR                          | F88h | BSR            |

| C09h | WREG                         | C89h | WREG                         | D09h | WREG                         | D89h | WREG                         | E09h | WREG                         | E89h | WREG                         | F09h | WREG                         | F89h | WREG           |

| C0Ah | PCLATH                       | C8Ah | PCLATH                       | D0Ah | PCLATH                       | D8Ah | PCLATH                       | E0Ah | PCLATH                       | E8Ah | PCLATH                       | F0Ah | PCLATH                       | F8Ah | PCLATH         |

| C0Bh | INTCON                       | C8Bh | INTCON                       | D0Bh | INTCON                       | D8Bh | INTCON                       | E0Bh | INTCON                       | E8Bh | INTCON                       | F0Bh | INTCON                       | F8Bh | INTCON         |

| C0Ch | _                            | C8Ch | _                            | D0Ch | _                            | D8Ch | ı                            | E0Ch | -                            | E8Ch | ı                            | F0Ch | _                            | F8Ch |                |

| C0Dh | _                            | C8Dh | _                            | D0Dh | _                            | D8Dh | ı                            | E0Dh | 1                            | E8Dh | ı                            | F0Dh | _                            | F8Dh |                |

| C0Eh | _                            | C8Eh | _                            | D0Eh | _                            | D8Eh | I                            | E0Eh | 1                            | E8Eh | I                            | F0Eh | _                            | F8Eh |                |

| C0Fh | _                            | C8Fh | _                            | D0Fh | _                            | D8Fh |                              | E0Fh | 1                            | E8Fh |                              | F0Fh | _                            | F8Fh |                |

| C10h | _                            | C90h | _                            | D10h | _                            | D90h |                              | E10h | 1                            | E90h |                              | F10h | _                            | F90h |                |

| C11h | _                            | C91h | _                            | D11h | _                            | D91h |                              | E11h | 1                            | E91h |                              | F11h | _                            | F91h |                |

| C12h | _                            | C92h | _                            | D12h | _                            | D92h |                              | E12h | ı                            | E92h |                              | F12h | _                            | F92h |                |

| C13h | _                            | C93h | _                            | D13h | _                            | D93h |                              | E13h | ı                            | E93h |                              | F13h | _                            | F93h |                |

| C14h | _                            | C94h | _                            | D14h | _                            | D94h |                              | E14h | ı                            | E94h |                              | F14h | _                            | F94h |                |

| C15h | _                            | C95h | _                            | D15h | _                            | D95h | _                            | E15h | _                            | E95h | _                            | F15h | _                            | F95h |                |

| C16h | _                            | C96h | _                            | D16h | _                            | D96h | _                            | E16h | _                            | E96h | _                            | F16h | _                            | F96h |                |

| C17h | _                            | C97h | _                            | D17h | _                            | D97h | I                            | E17h | I                            | E97h | I                            | F17h | _                            | F97h |                |

| C18h | _                            | C98h | _                            | D18h | _                            | D98h | 1                            | E18h | 1                            | E98h | 1                            | F18h | _                            | F98h | See Table 3-11 |

| C19h | _                            | C99h | _                            | D19h | _                            | D99h |                              | E19h | ı                            | E99h |                              | F19h | _                            | F99h | 000 100.00 11  |

| C1Ah | _                            | C9Ah | _                            | D1Ah | _                            | D9Ah | _                            | E1Ah | _                            | E9Ah | _                            | F1Ah | _                            | F9Ah |                |

| C1Bh | _                            | C9Bh | _                            | D1Bh | _                            | D9Bh | _                            | E1Bh | _                            | E9Bh | _                            | F1Bh | _                            | F9Bh |                |

| C1Ch | _                            | C9Ch | _                            | D1Ch | _                            | D9Ch |                              | E1Ch | _                            | E9Ch |                              | F1Ch | _                            | F9Ch |                |

| C1Dh | _                            | C9Dh | _                            | D1Dh | _                            | D9Dh | 1                            | E1Dh | 1                            | E9Dh | 1                            | F1Dh | _                            | F9Dh |                |

| C1Eh | _                            | C9Eh | _                            | D1Eh | _                            | D9Eh | _                            | E1Eh | _                            | E9Eh | _                            | F1Eh | _                            | F9Eh |                |

| C1Fh | _                            | C9Fh |                              | D1Fh |                              | D9Fh | _                            | E1Fh | _                            | E9Fh | _                            | F1Fh | _                            | F9Fh |                |

| C20h |                              | CA0h |                              | D20h |                              | DA0h |                              | E20h |                              | EA0h |                              | F20h |                              | FA0h |                |

|      | Unimplemented<br>Read as '0' |      |                |

| C6Fh |                              | CEFh |                              | D6Fh |                              | DEFh |                              | E6Fh |                              | EEFh |                              | F6Fh |                              | FEFh |                |

| C70h |                              | CF0h |                              | D70h |                              | DF0h |                              | E70h |                              | EF0h |                              | F70h |                              | FF0h |                |

|      | Accesses                     |      | Accesses       |

|      | 70h – 7Fh                    |      | 70h – 7Fh      |

| CFFh |                              | CFFh |                              | D7Fh |                              | DFFh |                              | E7Fh |                              | EFFh |                              | F7Fh |                              | FFFh |                |

| L    | - I I - I I - I I - I        | L    |                              | . !  |                              | ,    |                              | i i  |                              | ,    |                              | ,    |                              | L    |                |

**Legend:** = Unimplemented data memory locations, read as '0'.

### TABLE 3-12: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address                  | Name            | Bit 7                 | Bit 6                                                    | Bit 5           | Bit 4          | Bit 3          | Bit 2        | Bit 1   | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------------|-----------------|-----------------------|----------------------------------------------------------|-----------------|----------------|----------------|--------------|---------|--------|----------------------|---------------------------------|

| Bank 31                  |                 |                       |                                                          |                 |                |                |              |         |        |                      |                                 |

| F80h <sup>(2)</sup>      | INDF0           | _                     | this location u<br>ical register)                        | ses contents o  | of FSR0H/FSR   | ROL to address | data memor   | у       |        | xxxx xxxx            | xxxx xxxx                       |

| F81h <sup>(2)</sup>      | INDF1           |                       | this location u                                          | ses contents o  | of FSR1H/FSF   | R1L to address | data memor   | у       |        | xxxx xxxx            | xxxx xxxx                       |

| F82h <sup>(2)</sup>      | PCL             | Program Co            | ounter (PC) Le                                           | ast Significan  | t Byte         |                |              |         |        | 0000 0000            | 0000 0000                       |

| F83h <sup>(2)</sup>      | STATUS          | _                     | _                                                        | _               | TO             | PD             | Z            | DC      | С      | 1 1000               | q quuu                          |

| F84h <sup>(2)</sup>      | FSR0L           | Indirect Dat          | a Memory Add                                             | ress 0 Low P    | ointer         |                |              |         |        | 0000 0000            | uuuu uuuu                       |

| F85h <sup>(2)</sup>      | FSR0H           | Indirect Dat          | a Memory Add                                             |                 | 0000 0000      | 0000 0000      |              |         |        |                      |                                 |

| F86h <sup>(2)</sup>      | FSR1L           | Indirect Dat          | a Memory Ado                                             | 0000 0000       | uuuu uuuu      |                |              |         |        |                      |                                 |

| F87h <sup>(2)</sup>      | FSR1H           | Indirect Dat          | a Memory Ado                                             | ress 1 High F   | ointer         |                |              |         |        | 0000 0000            | 0000 0000                       |

| F88h <sup>(2)</sup>      | BSR             | _                     | _                                                        | _               |                | E              | BSR<4:0>     |         |        | 0 0000               | 0 0000                          |

| F89h <sup>(2)</sup>      | WREG            | Working Re            | gister                                                   |                 | •              |                |              |         |        | 0000 0000            | uuuu uuuu                       |

| F8Ah <sup>(1),(2</sup> ) | PCLATH          | _                     | Write Buffer for the upper 7 bits of the Program Counter |                 |                |                |              |         |        |                      | -000 0000                       |

| F8Bh <sup>(2)</sup>      | INTCON          | GIE                   | GIE PEIE TMR0IE INTE IOCIE TMR0IF INTF IOCIF             |                 |                |                |              |         |        |                      | 0000 0000                       |

| F8Ch                     | _               | Unimpleme             | Unimplemented                                            |                 |                |                |              |         |        |                      |                                 |

| FE3h                     |                 |                       |                                                          | ı               | 1              | 1              | •            | _       |        |                      |                                 |

| FE4h                     | STATUS_<br>SHAD |                       |                                                          |                 |                |                | Z_SHAD       | DC_SHAD | C_SHAD | xxx                  | uuu                             |

| FE5h                     | WREG_<br>SHAD   | Working Re            | gister Normal                                            | (Non-ICD) Sh    | adow           |                |              |         |        | xxxx xxxx            | uuuu uuuu                       |

| FE6h                     | BSR_<br>SHAD    |                       |                                                          |                 | Bank Select I  | Register Norm  | al (Non-ICD) | Shadow  |        | x xxxx               | u uuuu                          |

| FE7h                     | PCLATH_         |                       | Program Cou                                              | ınter Latch Hiç | gh Register No | ormal (Non-ICE | D) Shadow    |         |        | -xxx xxxx            | uuuu uuuu                       |

|                          | SHAD            | –                     | L                                                        |                 |                |                |              |         |        |                      |                                 |

| FE8h                     | FSR0L_<br>SHAD  | Indirect Dat          | a Memory Ado                                             | iress 0 Low P   | ointer Normal  | (Non-ICD) Sha  | adow         |         |        | xxxx xxxx            | uuuu uuuu                       |

| FE9h                     | FSR0H_<br>SHAD  | Indirect Dat          | a Memory Ado                                             | lress 0 High F  | ointer Normal  | (Non-ICD) Sh   | adow         |         |        | xxxx xxxx            | uuuu uuuu                       |

| FEAh                     | FSR1L_          | Indirect Dat          | a Memory Ado                                             | dress 1 Low P   | ointer Normal  | (Non-ICD) Sha  | adow         |         |        | xxxx xxxx            | uuuu uuuu                       |

|                          | SHAD            |                       |                                                          |                 |                |                |              |         |        |                      |                                 |

| FEBh                     | FSR1H_<br>SHAD  | Indirect Dat          | a Memory Add                                             | lress 1 High P  | ointer Normal  | (Non-ICD) Sh   | adow         |         |        | xxxx xxxx            | uuuu uuuu                       |

| FECh                     | _               | Unimpleme             | nted                                                     |                 |                |                |              |         |        | _                    | _                               |

| FEDh                     | STKPTR          | Current Stack pointer |                                                          |                 |                |                |              |         |        | 1 1111               | 1 1111                          |

| FEEh                     | TOSL            | Top of Stack          | k Low byte                                               |                 | !              |                |              |         |        | xxxx xxxx            | uuuu uuuu                       |

|                          | . 002           |                       | Top of Stack                                             |                 |                |                |              |         |        |                      |                                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'.

4: Unimplemented, read as '1'.

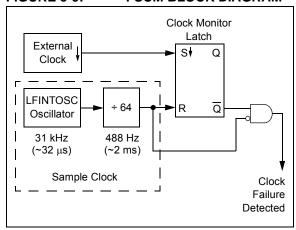

#### 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word 1. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 oscillator and RC).

FIGURE 5-9: FSCM BLOCK DIAGRAM

#### 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

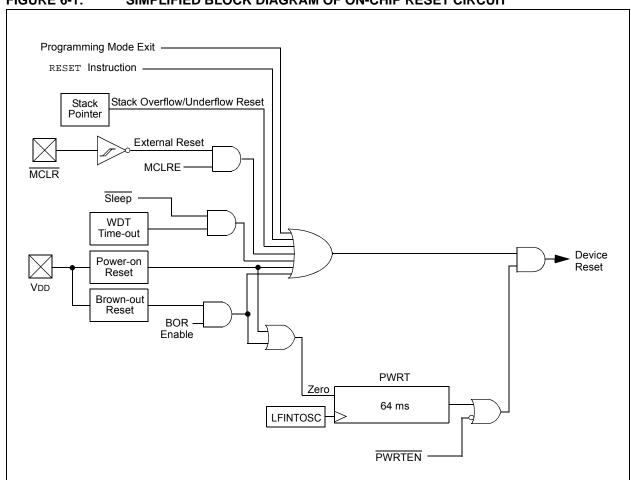

#### 6.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- · Brown-out Reset (BOR)

- MCLR Reset

- · WDT Reset

- RESET instruction

- · Stack Overflow

- · Stack Underflow

- · Programming mode exit

To allow VDD to stabilize, an optional power-up timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 6-1.

FIGURE 6-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

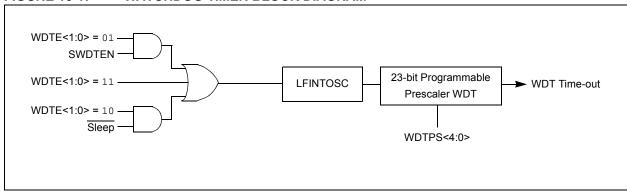

#### 10.0 WATCHDOG TIMER

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- · Independent clock source

- · Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (typical)

- · Multiple Reset conditions

- · Operation during Sleep

### FIGURE 10-1: WATCHDOG TIMER BLOCK DIAGRAM

#### 12.0 I/O PORTS

Depending on the device selected and peripherals enabled, there are up to five ports available. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- · ANSELx (analog select)

- WPUx (weak pull-up)

- · INLVLx (input level control)

TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC | PORTD | PORTE |

|---------------|-------|-------|-------|-------|-------|

| PIC16(L)F1934 | •     | •     | •     | •     | •     |

| PIC16(L)F1936 | •     | •     | •     |       | •     |

| PIC16(L)F1937 | •     | •     | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

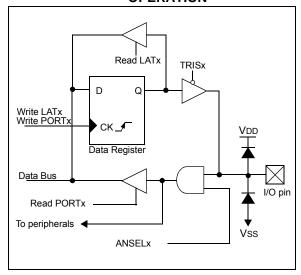

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

FIGURE 12-1: GENERIC I/O PORT OPERATION

#### **EXAMPLE 12-1: INITIALIZING PORTA**

```

; This code example illustrates

; initializing the PORTA register. The

; other ports are initialized in the same

; manner.

BANKSEL PORTA

CLRF

PORTA

;Init PORTA

BANKSEL LATA

;Data Latch

CLRF

T.ATA

BANKSEL ANSELA

;digital I/O

CLRF

ANSELA

BANKSEL TRISA

MOVLW B'00111000'

;Set RA<5:3> as inputs

MOVWE

;and set RA<2:0> as

TRISA

;outputs

```

### REGISTER 12-17: ANSELD: PORTD ANALOG SELECT REGISTER<sup>(2)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSD7   | ANSD6   | ANSD5   | ANSD4   | ANSD3   | ANSD2   | ANSD1   | ANSD0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared

bit 7-0 ANSD<7:0>: Analog Select between Analog or Digital Function on Pins RD<7:0>, respectively

0 = Digital I/O. Pin is assigned to port or digital special function.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

2: ANSELD register is not implemented on the PIC16(L)F1936. Read as '0'.

3: PORTD implemented on PIC16(L)F1934/7 devices only.

### TABLE 12-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD<sup>(1)</sup>

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                  | Bit 2      | Bit 1  | Bit 0  | Register on Page |  |  |

|---------|--------|--------|--------|--------|------------------------|------------|--------|--------|------------------|--|--|

| ANSELD  | ANSD7  | ANSD6  | ANSD5  | ANSD4  | ANSD3                  | ANSD2      | ANSD1  | ANSD0  | 146              |  |  |

| CCPxCON | PxM<   | <1:0>  | DCxB   | <1:0>  |                        | CCPxM<3:0> |        |        |                  |  |  |

| CPSCON0 | CPSON  | _      | _      | _      | CPSRNG<1:0> CPSOUT T0X |            |        | T0XCS  | 323              |  |  |

| CPSCON1 | _      | _      | _      | _      | CPSCH<3:0>             |            |        |        | 324              |  |  |

| LATD    | LATD7  | LATD6  | LATD5  | LATD4  | LATD3                  | LATD2      | LATD1  | LATD0  | 145              |  |  |

| LCDCON  | LCDEN  | SLPEN  | WERR   | _      | CS<                    | 1:0>       | LMUX   | <1:0>  | 329              |  |  |

| LCDSE2  | SE23   | SE22   | SE21   | SE20   | SE19                   | SE18       | SE17   | SE16   | 333              |  |  |

| PORTD   | RD7    | RD6    | RD5    | RD4    | RD3                    | RD2        | RD1    | RD0    | 145              |  |  |

| TRISD   | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3                 | TRISD2     | TRISD1 | TRISD0 | 145              |  |  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not implemented on the PIC16(L)F1936 devices, read as '0'.

#### 15.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- · Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 15.3 "A/D Acquisition Requirements".

#### **EXAMPLE 15-1: A/D CONVERSION**

```

; This code block configures the ADC

; for polling, Vdd and Vss references, Frc

; clock and ANO input.

;Conversion start & polling for completion

; are included.

BANKSEL ADCON1

B'11110000' ;Right justify, Frc

MOVLW

;clock

MOVWF

ADCON1

;Vdd and Vss Vref

BANKSEL TRISA

BSF

TRISA,0 ;Set RAO to input

BANKSEL ANSEL

BSF

ANSEL,0 ;Set RAO to analog

BANKSEL

ADCON0

B'00000001' ;Select channel AN0

MOVLW

MOVWE

;Turn ADC On

ADCON0

SampleTime ;Acquisiton delay

CALL

ADCON0, ADGO ; Start conversion

BSF

BTFSC

ADCON0, ADGO ; Is conversion done?

GOTO

$-1

;No, test again

ADRESH

BANKSEL

ADRESH,W ;Read upper 2 bits

MOVF

MOVWF

RESULTHI

;store in GPR space

BANKSEL

ADRESL

ADRESL,W

MOVF

;Read lower 8 bits

MOVWF

RESULTIO

;Store in GPR space

```

**NOTES:**

#### 19.0 SR LATCH

The module consists of a single SR Latch with multiple Set and Reset inputs as well as separate latch outputs. The SR Latch module includes the following features:

- · Programmable input selection

- SR Latch output is available externally

- Separate Q and Q outputs

- · Firmware Set and Reset

The SR Latch can be used in a variety of analog applications, including oscillator circuits, one-shot circuit, hysteretic controllers, and analog timing applications.

### 19.1 Latch Operation

The latch is a Set-Reset Latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. The latch can be set or reset by:

- Software control (SRPS and SRPR bits)

- Comparator C1 output (SYNCC1OUT)

- Comparator C2 output (SYNCC2OUT)

- SRI pin

- Programmable clock (SRCLK)

The SRPS and the SRPR bits of the SRCON0 register may be used to set or reset the SR Latch, respectively. The latch is Reset-dominant. Therefore, if both Set and Reset inputs are high, the latch will go to the Reset state. Both the SRPS and SRPR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

The output from Comparator C1 or C2 can be used as the Set or Reset inputs of the SR Latch. The output of either Comparator can be synchronized to the Timer1 clock source. See Section 18.0 "Comparator Module" and Section 21.0 "Timer1 Module with Gate Control" for more information.

An external source on the SRI pin can be used as the Set or Reset inputs of the SR Latch.

An internal clock source is available that can periodically set or reset the SR Latch. The SRCLK<2:0> bits in the SRCON0 register are used to select the clock source period. The SRSCKE and SRRCKE bits of the SRCON1 register enable the clock source to set or reset the SR Latch, respectively.

Note:

Enabling both the Set and Reset inputs from any one source at the same time may result in indeterminate operation, as the Reset dominance cannot be assured.

#### 19.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR Latch outputs may be directly output to an I/O pin at the same time. The  $\overline{Q}$  latch output pin function can be moved to an alternate pin using the SRNQSEL bit of the APFCON register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

#### 19.3 Effects of a Reset

Upon any device Reset, the SR Latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

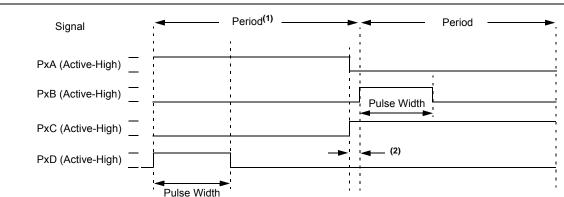

## 23.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the PxM1 bit in the CCPxCON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the PxM1 bit of the CCPxCON register. The following sequence occurs four Timer cycles prior to the end of the current PWM period:

- The modulated outputs (PxB and PxD) are placed in their inactive state.

- The associated unmodulated outputs (PxA and PxC) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 23-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 23-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output PxA and PxD become inactive, while output PxC becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 23-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

- Note 1: The direction bit PxM1 of the CCPxCON register is written any time during the PWM cycle.

- 2: When changing directions, the PxA and PxC signals switch before the end of the current PWM cycle. The modulated PxB and PxD signals are inactive at this time. The length of this time is four Timer counts.

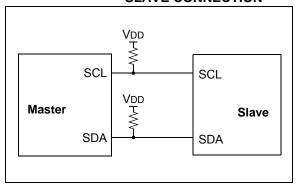

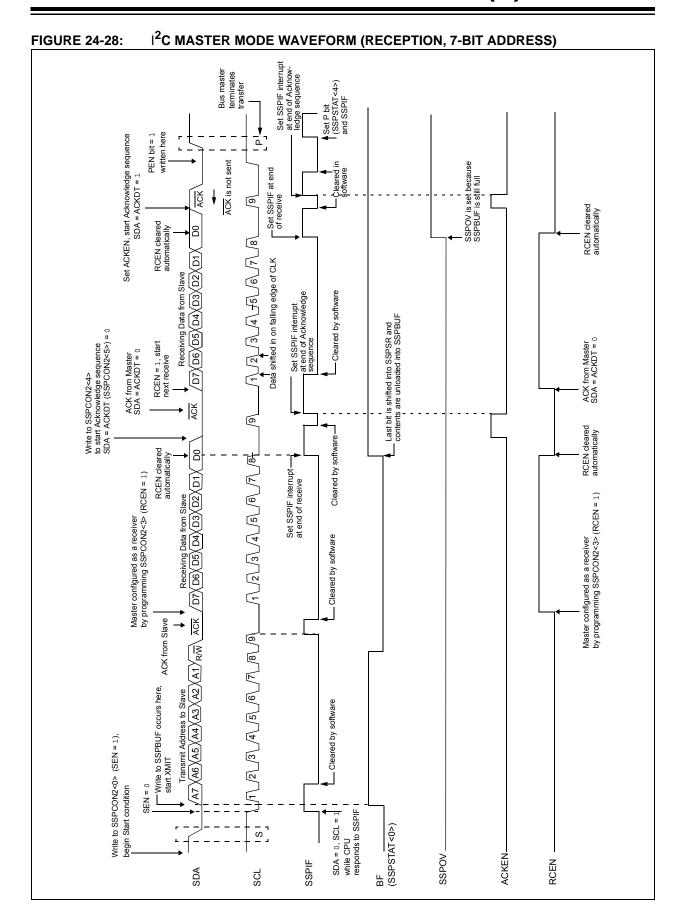

#### 24.3 I<sup>2</sup>C Mode Overview

The Inter-Integrated Circuit Bus (I<sup>2</sup>C) is a multi-master serial data communication bus. Devices communicate in a master/slave environment where the master devices initiate the communication. A Slave device is controlled through addressing.

The I<sup>2</sup>C bus specifies two signal connections:

- · Serial Clock (SCL)

- · Serial Data (SDA)

Figure 24-11 shows the block diagram of the MSSP module when operating in I<sup>2</sup>C Mode.

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors for the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one.

Figure 24-11 shows a typical connection between two processors configured as master and slave devices.

The I<sup>2</sup>C bus can operate with one or more master devices and one or more slave devices.

There are four potential modes of operation for a given device:

- Master Transmit mode (master is transmitting data to a slave)

- Master Receive mode (master is receiving data from a slave)

- Slave Transmit mode (slave is transmitting data to a master)

- Slave Receive mode (slave is receiving data from the master)

To begin communication, a master device starts out in Master Transmit mode. The master device sends out a Start bit followed by the address byte of the slave it intends to communicate with. This is followed by a single Read/Write bit, which determines whether the master intends to transmit to or receive data from the slave device.

If the requested slave exists on the bus, it will respond with an Acknowledge bit, otherwise known as an ACK. The master then continues in either Transmit mode or Receive mode and the slave continues in the complement, either in Receive mode or Transmit mode, respectively.

A Start bit is indicated by a high-to-low transition of the SDA line while the SCL line is held high. Address and data bytes are sent out, Most Significant bit (MSb) first. The Read/Write bit is sent out as a logical one when the master intends to read data from the slave, and is sent out as a logical zero when it intends to write data to the slave.

FIGURE 24-11: I<sup>2</sup>C MASTER/ SLAVE CONNECTION

The Acknowledge bit  $(\overline{ACK})$  is an active-low signal, which holds the SDA line low to indicate to the transmitter that the slave device has received the transmitted data and is ready to receive more.

The transition of a data bit is always performed while the SCL line is held low. Transitions that occur while the SCL line is held high are used to indicate Start and Stop bits.

If the master intends to write to the slave, then it repeatedly sends out a byte of data, with the slave responding after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Transmit mode and the slave is in Slave Receive mode.

If the master intends to read from the slave, then it repeatedly receives a byte of data from the slave, and responds after each byte with an  $\overline{ACK}$  bit. In this example, the master device is in Master Receive mode and the slave is Slave Transmit mode.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends the Stop bit in place of the last  $\overline{ACK}$  bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send another Start bit in place of the Stop bit or last  $\overline{ACK}$  bit when it is in receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

TABLE 25-5: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|        |                   | <b>SYNC</b> = 0, <b>BRGH</b> = 1, <b>BRG16</b> = 1 or <b>SYNC</b> = 1, <b>BRG16</b> = 1 |                             |                   |            |                             |                   |            |                             |                    |            |                             |  |  |  |

|--------|-------------------|-----------------------------------------------------------------------------------------|-----------------------------|-------------------|------------|-----------------------------|-------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--|--|--|

| BAUD   | Fosc = 32.000 MHz |                                                                                         |                             | Fosc = 20.000 MHz |            |                             | Fosc = 18.432 MHz |            |                             | Fosc = 11.0592 MHz |            |                             |  |  |  |

| RATE   | Actual<br>Rate    | %<br>Error                                                                              | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 300    | 300.0             | 0.00                                                                                    | 26666                       | 300.0             | 0.00       | 16665                       | 300.0             | 0.00       | 15359                       | 300.0              | 0.00       | 9215                        |  |  |  |

| 1200   | 1200              | 0.00                                                                                    | 6666                        | 1200              | -0.01      | 4166                        | 1200              | 0.00       | 3839                        | 1200               | 0.00       | 2303                        |  |  |  |

| 2400   | 2400              | 0.01                                                                                    | 3332                        | 2400              | 0.02       | 2082                        | 2400              | 0.00       | 1919                        | 2400               | 0.00       | 1151                        |  |  |  |

| 9600   | 9604              | 0.04                                                                                    | 832                         | 9597              | -0.03      | 520                         | 9600              | 0.00       | 479                         | 9600               | 0.00       | 287                         |  |  |  |

| 10417  | 10417             | 0.00                                                                                    | 767                         | 10417             | 0.00       | 479                         | 10425             | 80.0       | 441                         | 10433              | 0.16       | 264                         |  |  |  |

| 19.2k  | 19.18k            | -0.08                                                                                   | 416                         | 19.23k            | 0.16       | 259                         | 19.20k            | 0.00       | 239                         | 19.20k             | 0.00       | 143                         |  |  |  |

| 57.6k  | 57.55k            | -0.08                                                                                   | 138                         | 57.47k            | -0.22      | 86                          | 57.60k            | 0.00       | 79                          | 57.60k             | 0.00       | 47                          |  |  |  |

| 115.2k | 115.9k            | 0.64                                                                                    | 68                          | 116.3k            | 0.94       | 42                          | 115.2k            | 0.00       | 39                          | 115.2k             | 0.00       | 23                          |  |  |  |

|        | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |            |                             |                  |            |                             |                   |            |                             |                  |            |                             |  |  |

|--------|------------------------------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|--|--|

| BAUD   | Fosc = 8.000 MHz                                     |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |  |  |

| RATE   | Actual<br>Rate                                       | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 300    | 300.0                                                | 0.00       | 6666                        | 300.0            | 0.01       | 3332                        | 300.0             | 0.00       | 3071                        | 300.1            | 0.04       | 832                         |  |  |

| 1200   | 1200                                                 | -0.02      | 1666                        | 1200             | 0.04       | 832                         | 1200              | 0.00       | 767                         | 1202             | 0.16       | 207                         |  |  |

| 2400   | 2401                                                 | 0.04       | 832                         | 2398             | 0.08       | 416                         | 2400              | 0.00       | 383                         | 2404             | 0.16       | 103                         |  |  |

| 9600   | 9615                                                 | 0.16       | 207                         | 9615             | 0.16       | 103                         | 9600              | 0.00       | 95                          | 9615             | 0.16       | 25                          |  |  |

| 10417  | 10417                                                | 0          | 191                         | 10417            | 0.00       | 95                          | 10473             | 0.53       | 87                          | 10417            | 0.00       | 23                          |  |  |

| 19.2k  | 19.23k                                               | 0.16       | 103                         | 19.23k           | 0.16       | 51                          | 19.20k            | 0.00       | 47                          | 19.23k           | 0.16       | 12                          |  |  |

| 57.6k  | 57.14k                                               | -0.79      | 34                          | 58.82k           | 2.12       | 16                          | 57.60k            | 0.00       | 15                          | _                | _          | _                           |  |  |

| 115.2k | 117.6k                                               | 2.12       | 16                          | 111.1k           | -3.55      | 8                           | 115.2k            | 0.00       | 7                           | _                |            | _                           |  |  |

### 30.8 AC Characteristics: PIC16(L)F1934/6/7-I/E

#### TABLE 30-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

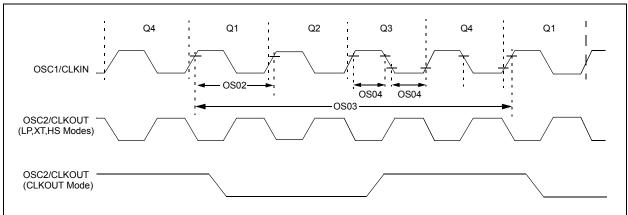

Standard Operating Conditions (unless otherwise stated) Operating temperature  $-40^{\circ}C \le TA \le +125^{\circ}C$ **Param** Sym. Characteristic Min. Typ† Max. Units Conditions No. External CLKIN Frequency<sup>(1)</sup> OS01 DC 0.5 MHz EC Oscillator mode (low) DC EC Oscillator mode (medium) 4 MHz DC 20 MHz EC Oscillator mode (high) Oscillator Frequency<sup>(1)</sup> LP Oscillator mode 32.768 kHz 0.1 4 MHz XT Oscillator mode 1 4 MHz HS Oscillator mode 20 MHz HS Oscillator mode. VDD > 2.7V 1 DC 4 MHz RC Oscillator mode,  $VDD \le 2.0V$ OS02 Tosc External CLKIN Period<sup>(1)</sup> 27 LP Oscillator mode μS 250 XT Oscillator mode HS Oscillator mode 50 00 ns 50 EC Oscillator mode ns Oscillator Period<sup>(1)</sup> LP Oscillator mode 30.5 μS 250 10,000 XT Oscillator mode ns HS Oscillator mode 1,000 50 ns 250 RC Oscillator mode ns **OS03** Instruction Cycle Time<sup>(1)</sup> DC Tcy = 4/Fosc TCY 200 TCY ns OS04<sup>3</sup> TosH. External CLKIN High. 2 μS LP oscillator TosL External CLKIN Low XT oscillator 100 ns 20 HS oscillator ns OS05\* External CLKIN Rise. TosR. 0 LP oscillator ns External CLKIN Fall TosF XT oscillator 0 00 ns ns HS oscillator

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

| PWM Setup                                       | 219     | Industrial and Extended (PIC16F/LF1934/36/37)   | 384 |

|-------------------------------------------------|---------|-------------------------------------------------|-----|

| CCP1CON Register                                | 44, 45  | Development Support                             | 441 |

| CCPR1H Register                                 | 44, 45  | Device Configuration                            | 6′  |

| CCPR1L Register                                 |         | Code Protection                                 |     |

| CCPTMRS0 Register                               |         | Configuration Word                              |     |

| CCPTMRS1 Register                               |         | User ID                                         |     |

| CCPxAS Register                                 |         | Device Overview19                               |     |

| CCPxCON (ECCPx) Register                        |         | Digital-to-Analog Converter (DAC)               |     |

| Clock Accuracy with Asynchronous Operation      |         | Associated Registers                            |     |

| Clock Sources                                   |         | Effects of a Reset                              |     |

| External Modes                                  | 71      | Specifications                                  |     |

| EC                                              |         | Specifications                                  | 400 |

|                                                 |         | E                                               |     |

| HS                                              |         | ECCD/CCD, Soo Enhanced Conture/Compare/DW/M     |     |

| LP                                              |         | ECCP/CCP. See Enhanced Capture/Compare/PWM      | 447 |

| OST                                             |         | EEADR Registers                                 |     |

| RC                                              |         | EEADRH Registers                                |     |

| XT                                              |         | EEADRL Register                                 |     |

| Internal Modes                                  |         | EEADRL Registers                                |     |

| HFINTOSC                                        |         | EECON1 Register11                               |     |

| Internal Oscillator Clock Switch Timing         |         | EECON2 Register117                              |     |

| LFINTOSC                                        | 75      | EEDATH Register                                 |     |

| MFINTOSC                                        | 74      | EEDATL Register                                 | 128 |

| Clock Switching                                 | 78      | EEPROM Data Memory                              |     |

| CMOUT Register                                  | 186     | Avoiding Spurious Write                         |     |

| CMxCON0 Register                                | 185     | Write Verify                                    | 127 |

| CMxCON1 Register                                | 186     | Effects of Reset                                |     |

| Code Examples                                   |         | PWM mode                                        | 221 |

| A/D Conversion                                  | 164     | Electrical Specifications (PIC16F/LF1934/36/37) | 381 |

| Changing Between Capture Prescalers             | 214     | Enhanced Capture/Compare/PWM (ECCP)             |     |

| Initializing PORTA                              |         | Enhanced PWM Mode                               | 222 |

| Initializing PORTE                              |         | Auto-Restart                                    | 231 |

| Write Verify                                    |         | Auto-shutdown                                   |     |

| Writing to Flash Program Memory                 |         | Direction Change in Full-Bridge Output Mode     |     |

| Comparator                                      |         | Full-Bridge Application                         |     |

| Associated Registers                            | 187 188 | Full-Bridge Mode                                |     |

| Operation                                       |         | Half-Bridge Application                         |     |

| Comparator Module                               |         | Half-Bridge Application Examples                |     |

| Cx Output State Versus Input Conditions         |         | Half-Bridge Mode                                |     |

| Comparator Specifications                       |         | Output Relationships (Active-High and           |     |

| Comparators                                     |         | Active-Low)                                     | 223 |

| C2OUT as T1 Gate                                | 100     | Output Relationships Diagram                    |     |

| Compare Module. See Enhanced Capture/Compar     |         | Programmable Dead Band Delay                    |     |

| PWM (ECCP)                                      | C/      | Shoot-through Current                           |     |

| CONFIG1 Register                                | 62      | Start-up Considerations                         |     |

|                                                 |         | Specifications                                  |     |

| CONFIG2 Register                                |         | Enhanced Mid-range CPU                          |     |

| Core Registers                                  |         | Enhanced Universal Synchronous Asynchronous     | 20  |

| CPSCON0 Register                                |         | · · · · · · · · · · · · · · · · · · ·           | 202 |

| CPSCON1 Register                                |         | Receiver Transmitter (EUSART)                   |     |

| Customer Change Notification Service            |         | Errata                                          |     |

| Customer Notification Service                   |         | EUSART                                          | 293 |

| Customer Support                                | 471     | Associated Registers                            | 000 |

| D                                               |         | Baud Rate Generator                             |     |

|                                                 |         | Asynchronous Mode                               |     |

| DACCON0 (Digital-to-Analog Converter Control 0) | 470     | 12-bit Break Transmit and Receive               | 313 |

| Register                                        | 178     | Associated Registers                            | 004 |

| DACCON1 (Digital-to-Analog Converter Control 1) | 470     | Receive                                         |     |

| Register                                        |         | Transmit                                        |     |

| Memory                                          |         | Auto-Wake-up on Break                           |     |

| Associated Registers                            |         | Baud Rate Generator (BRG)                       |     |

| Code Protection                                 |         | Clock Accuracy                                  |     |

| Reading                                         |         | Receiver                                        |     |

| Writing                                         |         | Setting up 9-bit Mode with Address Detect       |     |

| Data Memory                                     |         | Transmitter                                     | 295 |

| DC and AC Characteristics                       | 413     | Baud Rate Generator (BRG)                       |     |

| DC Characteristics                              |         | Auto Baud Rate Detect                           |     |

| Extended and Industrial (PIC16F/LF1934/36/3     | 37) 391 | Baud Rate Error, Calculating                    | 305 |

| Baud Rates, Asynchronous Modes                     |               | CALLW                                    | 373     |

|----------------------------------------------------|---------------|------------------------------------------|---------|

| Formulas                                           |               | LSLF                                     | 375     |

| High Baud Rate Select (BRGH Bit)                   | 305           | LSRF                                     | 375     |

| Synchronous Master Mode                            | 314, 318      | MOVF                                     | 375     |

| Associated Registers                               |               | MOVIW                                    | 376     |

| Receive                                            | 317           | MOVLB                                    | 376     |

| Transmit                                           | 315           | MOVWI                                    | 377     |

| Reception                                          | 316           | OPTION                                   | 377     |

| Transmission                                       |               | RESET                                    | 377     |

| Synchronous Slave Mode                             |               | SUBWFB                                   | 379     |

| Associated Registers                               |               | TRIS                                     | 380     |

| Receive                                            | 319           | BCF                                      | 372     |

| Transmit                                           |               | BSF                                      | 372     |

| Reception                                          |               | BTFSC                                    | 372     |

| Transmission                                       |               | BTFSS                                    |         |

| Extended Instruction Set                           |               | CALL                                     |         |

| ADDFSR                                             | 371           | CLRF                                     |         |

| ADDI OI                                            |               | CLRW                                     |         |

| F                                                  |               | CLRWDT                                   |         |

| Fail-Safe Clock Monitor                            | 81            | COMF                                     |         |

| Fail-Safe Condition Clearing                       |               |                                          |         |

| Fail-Safe Detection                                |               | DECF                                     |         |

| Fail-Safe Operation                                |               | DECFSZ                                   |         |

| •                                                  |               | GOTO                                     |         |

| Reset or Wake-up from Sleep                        |               | INCF                                     |         |

| Firmware Instructions                              | 307           | INCFSZ                                   |         |

| Fixed Voltage Reference (FVR)                      | 450           | IORLW                                    |         |

| Associated Registers                               |               | IORWF                                    |         |

| Flash Program Memory                               |               | MOVLW                                    |         |

| Erasing                                            |               | MOVWF                                    | 376     |

| Modifying                                          |               | NOP                                      |         |

| Writing                                            |               | RETFIE                                   | 378     |

| FSR Register39, 40, 41, 42, 43, 44, 45, 46, 47, 48 |               | RETLW                                    | 378     |

| FVRCON (Fixed Voltage Reference Control) Reg       | ister 158     | RETURN                                   | 378     |

|                                                    |               | RLF                                      | 378     |

|                                                    |               | RRF                                      | 379     |

| <sup>2</sup> C Mode (MSSP)                         |               | SLEEP                                    | 379     |

| Acknowledge Sequence Timing                        | 280           | SUBLW                                    | 379     |

| Bus Collision                                      |               | SUBWF                                    | 379     |

| During a Repeated Start Condition                  | 284           | SWAPF                                    | 380     |

| During a Stop Condition                            | 285           | XORLW                                    |         |

| Effects of a Reset                                 | 281           | XORWF                                    |         |

| I <sup>2</sup> C Clock Rate w/BRG                  | 287           | INTCON Register                          |         |

| Master Mode                                        |               | Internal Oscillator Block                |         |

| Operation                                          | 272           | INTOSC                                   |         |

| Reception                                          |               | Specifications                           | 307     |

| Start Condition Timing                             |               | Internal Sampling Switch (Rss) Impedance |         |

| Transmission                                       |               | , .                                      |         |

| Multi-Master Communication, Bus Collision          |               | Internet Address                         |         |

| Arbitration                                        |               | Interrupt-On-Change                      |         |

| Multi-Master Mode                                  |               | Associated Registers                     |         |

| _                                                  |               | Interrupts                               |         |

| Read/Write Bit Information (R/W Bit)               | 237           | ADC                                      |         |

| Slave Mode                                         | 000           | Associated registers w/ Interrupts       |         |

| Transmission                                       |               | Configuration Word w/ Clock Sources      |         |

| Sleep Operation                                    |               | Configuration Word w/ LDO                | 109     |

| Stop Condition Timing                              |               | TMR1                                     | 201     |

| NDF Register39, 40, 41, 42, 43, 44, 45, 46, 47, 48 | 8, 49, 51, 52 | INTOSC Specifications                    | 397     |

| ndirect Addressing                                 | 56            | IOCBF Register                           | 154     |

| nstruction Format                                  | 368           | IOCBN Register                           |         |

| nstruction Set                                     | 367           | IOCBP Register                           |         |

| ADDLW                                              | 371           | •                                        |         |

| ADDWF                                              |               | L                                        |         |

| ADDWFC                                             |               | LATA Register                            | 135 144 |

| ANDLW                                              |               | LATB Register                            |         |

| ANDWF                                              |               | LATD Register                            |         |

| BRA                                                |               | <u> </u>                                 |         |

| CALL                                               |               | LATE Register                            | 131     |

| UNLL                                               |               | LCD                                      |         |