Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

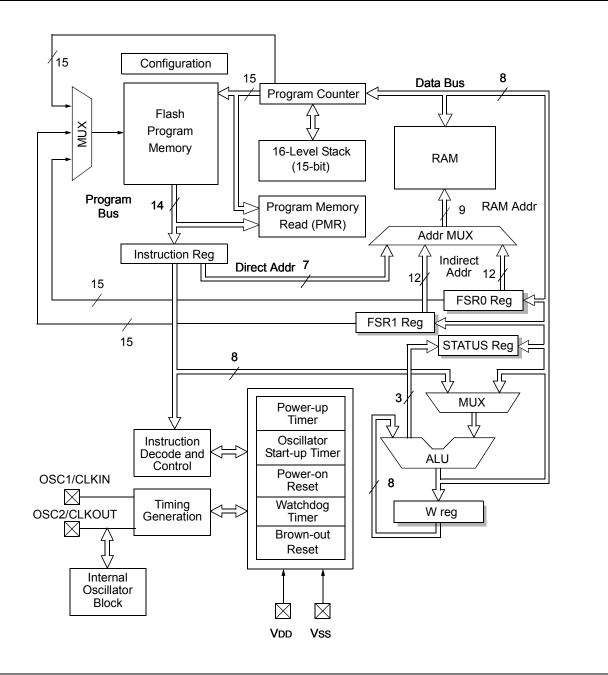

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 14x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1934t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-6:PIC16(L)F1936/1937 MEMORY MAP, BANKS 8-15

|      | BANK 8                       |      | BANK 9                       |      | BANK 10                      |      | BANK 11                      |      | BANK 12                      |      | BANK 13                      |      | BANK 14                      |      | BANK 15               |

|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|------------------------------|------|-----------------------|

| 400h | INDF0                        | 480h | INDF0                        | 500h | INDF0                        | 580h | INDF0                        | 600h | INDF0                        | 680h | INDF0                        | 700h | INDF0                        | 780h | INDF0                 |

| 401h | INDF1                        | 481h | INDF1                        | 501h | INDF1                        | 581h | INDF1                        | 601h | INDF1                        | 681h | INDF1                        | 701h | INDF1                        | 781h | INDF1                 |

| 402h | PCL                          | 482h | PCL                          | 502h | PCL                          | 582h | PCL                          | 602h | PCL                          | 682h | PCL                          | 702h | PCL                          | 782h | PCL                   |

| 403h | STATUS                       | 483h | STATUS                       | 503h | STATUS                       | 583h | STATUS                       | 603h | STATUS                       | 683h | STATUS                       | 703h | STATUS                       | 783h | STATUS                |

| 404h | FSR0L                        | 484h | FSR0L                        | 504h | FSR0L                        | 584h | FSR0L                        | 604h | FSR0L                        | 684h | FSR0L                        | 704h | FSR0L                        | 784h | FSR0L                 |

| 405h | FSR0H                        | 485h | FSR0H                        | 505h | FSR0H                        | 585h | FSR0H                        | 605h | FSR0H                        | 685h | FSR0H                        | 705h | FSR0H                        | 785h | FSR0H                 |

| 406h | FSR1L                        | 486h | FSR1L                        | 506h | FSR1L                        | 586h | FSR1L                        | 606h | FSR1L                        | 686h | FSR1L                        | 706h | FSR1L                        | 786h | FSR1L                 |

| 407h | FSR1H                        | 487h | FSR1H                        | 507h | FSR1H                        | 587h | FSR1H                        | 607h | FSR1H                        | 687h | FSR1H                        | 707h | FSR1H                        | 787h | FSR1H                 |

| 408h | BSR                          | 488h | BSR                          | 508h | BSR                          | 588h | BSR                          | 608h | BSR                          | 688h | BSR                          | 708h | BSR                          | 788h | BSR                   |

| 409h | WREG                         | 489h | WREG                         | 509h | WREG                         | 589h | WREG                         | 609h | WREG                         | 689h | WREG                         | 709h | WREG                         | 789h | WREG                  |

| 40Ah | PCLATH                       | 48Ah | PCLATH                       | 50Ah | PCLATH                       | 58Ah | PCLATH                       | 60Ah | PCLATH                       | 68Ah | PCLATH                       | 70Ah | PCLATH                       | 78Ah | PCLATH                |

| 40Bh | INTCON                       | 48Bh | INTCON                       | 50Bh | INTCON                       | 58Bh | INTCON                       | 60Bh | INTCON                       | 68Bh | INTCON                       | 70Bh | INTCON                       | 78Bh | INTCON                |

| 40Ch | _                            | 48Ch | —                            | 50Ch | _                            | 58Ch | _                            | 60Ch | _                            | 68Ch | _                            | 70Ch | —                            | 78Ch | _                     |

| 40Dh | _                            | 48Dh |                              | 50Dh | _                            | 58Dh | _                            | 60Dh | —                            | 68Dh | —                            | 70Dh | —                            | 78Dh | _                     |

| 40Eh | _                            | 48Eh |                              | 50Eh | _                            | 58Eh | _                            | 60Eh | —                            | 68Eh | —                            | 70Eh | —                            | 78Eh | _                     |

| 40Fh | _                            | 48Fh |                              | 50Fh | _                            | 58Fh | _                            | 60Fh | —                            | 68Fh | —                            | 70Fh | —                            | 78Fh |                       |

| 410h | —                            | 490h | —                            | 510h | _                            | 590h | —                            | 610h | —                            | 690h | —                            | 710h | —                            | 790h | —                     |

| 411h | —                            | 491h | —                            | 511h | _                            | 591h | —                            | 611h | —                            | 691h | —                            | 711h | —                            | 791h |                       |

| 412h | —                            | 492h | —                            | 512h | —                            | 592h | —                            | 612h | —                            | 692h | —                            | 712h | —                            | 792h |                       |

| 413h |                              | 493h |                              | 513h | —                            | 593h |                              | 613h | —                            | 693h | —                            | 713h | —                            | 793h |                       |

| 414h | _                            | 494h |                              | 514h | _                            | 594h |                              | 614h | _                            | 694h | _                            | 714h |                              | 794h |                       |

| 415h | TMR4                         | 495h | —                            | 515h | _                            | 595h | _                            | 615h | _                            | 695h | _                            | 715h | —                            | 795h |                       |

| 416h | PR4                          | 496h |                              | 516h | _                            | 596h |                              | 616h | _                            | 696h |                              | 716h |                              | 796h |                       |

| 417h | T4CON                        | 497h | _                            | 517h | _                            | 597h | _                            | 617h | _                            | 697h | _                            | 717h | _                            | 797h |                       |

| 418h | _                            | 498h | _                            | 518h | —                            | 598h | _                            | 618h | _                            | 698h | _                            | 718h | —                            | 798h |                       |

| 419h | _                            | 499h | _                            | 519h | _                            | 599h | _                            | 619h | _                            | 699h | _                            | 719h | _                            | 799h |                       |

| 41Ah | _                            | 49Ah |                              | 51Ah | _                            | 59Ah | _                            | 61Ah |                              | 69Ah | —                            | 71Ah |                              | 79Ah | See Table 3-9 or      |

| 41Bh |                              | 49Bh |                              | 51Bh | _                            | 59Bh |                              | 61Bh |                              | 69Bh | _                            | 71Bh |                              | 79Bh | Table 3-10            |

| 41Ch | TMR6                         | 49Ch | _                            | 51Ch | _                            | 59Ch |                              | 61Ch | _                            | 69Ch | _                            | 71Ch | _                            | 79Ch |                       |

| 41Dh | PR6                          | 49Dh |                              | 51Dh | —                            | 59Dh | _                            | 61Dh | _                            | 69Dh | —                            | 71Dh |                              | 79Dh |                       |

| 41Eh | T6CON                        | 49Eh |                              | 51Eh | —                            | 59Eh | —                            | 61Eh | —                            | 69Eh |                              | 71Eh |                              | 79Eh |                       |

| 41Fh | —                            | 49Fh | —                            | 51Fh | —                            | 59Fh | _                            | 61Fh | —                            | 69Fh | —                            | 71Fh | —                            | 79Fh |                       |

| 420h |                              | 4A0h |                              | 520h |                              | 5A0h |                              | 620h |                              | 6A0h |                              | 720h |                              | 7A0h |                       |

|      | Unimplemented<br>Read as '0' |      |                       |

| 46Fh |                              | 4EFh |                              | 56Fh |                              | 5EFh |                              | 66Fh |                              | 6EFh |                              | 76Fh |                              | 7EFh |                       |

| 470h | Accesses<br>70h – 7Fh        | 4F0h | Accesses<br>70h – 7Fh        | 570h | Accesses<br>70h – 7Fh        | 5F0h | Accesses<br>70h – 7Fh        | 670h | Accesses<br>70h – 7Fh        | 6F0h | Accesses<br>70h – 7Fh        | 770h | Accesses<br>70h – 7Fh        | 7F0h | Accesses<br>70h – 7Fh |

| 47Fh |                              | 4FFh |                              | 57Fh |                              | 5FFh |                              | 67Fh |                              | 6FFh |                              | 77Fh |                              | 7FFh |                       |

**Legend:** = Unimplemented data memory locations, read as '0'.

| Address                | Name   | Bit 7                                                                                                     | Bit 6                                                    | Bit 5           | Bit 4        | Bit 3          | Bit 2       | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|--------------|----------------|-------------|-------|---------|----------------------|---------------------------------|

| Bank 8                 |        |                                                                                                           |                                                          |                 |              |                |             |       |         |                      |                                 |

| 400h <sup>(2)</sup>    | INDF0  | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                                          |                 |              |                |             |       |         |                      | XXXX XXXX                       |

| 401h <sup>(2)</sup>    | INDF1  | Addressing<br>(not a physi                                                                                |                                                          | ses contents o  | of FSR1H/FSF | R1L to address | data memory | /     |         | XXXX XXXX            | XXXX XXXX                       |

| 402h <sup>(2)</sup>    | PCL    | Program Co                                                                                                | ounter (PC) Le                                           | ast Significant | t Byte       |                |             |       |         | 0000 0000            | 0000 0000                       |

| 403h <sup>(2)</sup>    | STATUS | _                                                                                                         | _                                                        | —               | TO           | PD             | Z           | DC    | С       | 1 1000               | q quuu                          |

| 404h <sup>(2)</sup>    | FSR0L  | Indirect Data                                                                                             | a Memory Add                                             | Iress 0 Low Po  | ointer       | •              | •           | •     | •       | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(2)</sup>    | FSR0H  | Indirect Data                                                                                             | a Memory Add                                             | lress 0 High P  | ointer       |                |             |       |         | 0000 0000            | 0000 0000                       |

| 406h <sup>(2)</sup>    | FSR1L  | Indirect Data                                                                                             | a Memory Add                                             | Iress 1 Low Po  | ointer       |                |             |       |         | 0000 0000            | uuuu uuuu                       |

| 407h <sup>(2)</sup>    | FSR1H  | Indirect Date                                                                                             | a Memory Add                                             | Iress 1 High P  | ointer       |                |             |       |         | 0000 0000            | 0000 0000                       |

| 408h <sup>(2)</sup>    | BSR    | _                                                                                                         | —                                                        | —               |              | E              | BSR<4:0>    |       |         | 0 0000               | 0 0000                          |

| 409h <sup>(2)</sup>    | WREG   | Working Re                                                                                                | gister                                                   |                 |              |                |             |       |         | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1, 2)</sup> | PCLATH | _                                                                                                         | Write Buffer for the upper 7 bits of the Program Counter |                 |              |                |             |       |         |                      | -000 0000                       |

| 40Bh <sup>(2)</sup>    | INTCON | GIE                                                                                                       | PEIE                                                     | TMR0IE          | INTE         | IOCIE          | TMR0IF      | INTF  | IOCIF   | 0000 0000            | 0000 0000                       |

| 40Ch                   |        | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 40Dh                   | _      | Unimpleme                                                                                                 | Jnimplemented                                            |                 |              |                |             |       |         |                      | _                               |

| 40Eh                   | _      | Unimpleme                                                                                                 | Jnimplemented                                            |                 |              |                |             |       |         |                      | _                               |

| 40Fh                   | _      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 410h                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 411h                   | _      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 412h                   | _      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 413h                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 414h                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 415h                   | TMR4   | Timer4 Mod                                                                                                | ule Register                                             |                 |              |                |             |       |         | 0000 0000            | 0000 0000                       |

| 416h                   | PR4    | Timer4 Peri                                                                                               | od Register                                              |                 |              |                |             |       |         | 1111 1111            | 1111 1111                       |

| 417h                   | T4CON  | _                                                                                                         |                                                          | T4OUT           | PS<3:0>      |                | TMR40N      | T4CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 418h                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | —                               |

| 419h                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

| 41Ah                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | —                               |

| 41Bh                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | —                               |

| 41Ch                   | TMR6   | Timer6 Mod                                                                                                | ule Register                                             |                 |              |                |             |       |         | 0000 0000            | 0000 0000                       |

| 41Dh                   | PR6    | Timer6 Peri                                                                                               | od Register                                              |                 |              |                |             |       |         | 1111 1111            | 1111 1111                       |

| 41Eh                   | T6CON  | _                                                                                                         |                                                          | T6OUT           | PS<3:0>      |                | TMR6ON      | T6CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh                   | —      | Unimpleme                                                                                                 | nted                                                     |                 |              |                |             |       |         | _                    | _                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

## 5.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

Internal clock sources are contained internally within the oscillator module. The internal oscillator block has two internal oscillators and a dedicated Phase-Lock Loop (HFPLL) that are used to generate three internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC), 500 kHz (MFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in the Configuration Word 1 to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Timer1 Oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See Section 5.3 "Clock Switching" for more information.

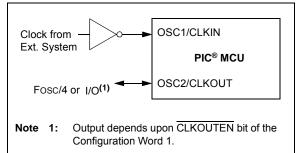

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has 3 power modes to select from through Configuration Word 1:

- High power, 4-32 MHz (FOSC = 111)

- Medium power, 0.5-4 MHz (FOSC = 110)

- Low power, 0-0.5 MHz (FOSC = 101)

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

FIGURE 5-2:

#### EXTERNAL CLOCK (EC) MODE OPERATION

### 5.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 5-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 5-3 and Figure 5-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

# 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Word 1

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Word 1.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch, which may     |

|-------|-------------------------------------------|

|       | occur from Two-Speed Start-up or          |

|       | Fail-Safe Clock Monitor, does not update  |

|       | the SCS bits of the OSCCON register. The  |

|       | user can monitor the OSTS bit of the      |

|       | OSCSTAT register to determine the current |

|       | system clock source.                      |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word 1, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 oscillator.

## 5.3.3 TIMER1 OSCILLATOR

The Timer1 oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See **Section 21.0 "Timer1 Module with Gate Control"** for more information about the Timer1 peripheral.

#### 5.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

#### 6.10 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON register are updated to indicate the cause of the Reset. Table 6-3 and Table 6-4 show the Reset conditions of these registers.

| STKOVF | STKUNF | RMCLR | RI | POR | BOR | то | PD | Condition                                                         |  |

|--------|--------|-------|----|-----|-----|----|----|-------------------------------------------------------------------|--|

| 0      | 0      | 1     | 1  | 0   | x   | 1  | 1  | Power-on Reset                                                    |  |

| 0      | 0      | 1     | 1  | 0   | x   | 0  | x  | Illegal, $\overline{\text{TO}}$ is set on $\overline{\text{POR}}$ |  |

| 0      | 0      | 1     | 1  | 0   | x   | x  | 0  | Illegal, $\overline{PD}$ is set on $\overline{POR}$               |  |

| 0      | 0      | 1     | 1  | u   | 0   | 1  | 1  | Brown-out Reset                                                   |  |

| u      | u      | u     | u  | u   | u   | 0  | u  | WDT Reset                                                         |  |

| u      | u      | u     | u  | u   | u   | 0  | 0  | WDT Wake-up from Sleep                                            |  |

| u      | u      | u     | u  | u   | u   | 1  | 0  | Interrupt Wake-up from Sleep                                      |  |

| u      | u      | 0     | u  | u   | u   | u  | u  | MCLR Reset during normal operation                                |  |

| u      | u      | 0     | u  | u   | u   | 1  | 0  | MCLR Reset during Sleep                                           |  |

| u      | u      | u     | 0  | u   | u   | u  | u  | RESET Instruction Executed                                        |  |

| 1      | u      | u     | u  | u   | u   | u  | u  | Stack Overflow Reset (STVREN = 1)                                 |  |

| u      | 1      | u     | u  | u   | u   | u  | u  | Stack Underflow Reset (STVREN = 1)                                |  |

TABLE 6-3: RESET STATUS BITS AND THEIR SIGNIFICANCE

### TABLE 6-4: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 1 1000             | 00 110x          |

| MCLR Reset during normal operation | 0000h                 | u uuuu             | uu Ouuu          |

| MCLR Reset during Sleep            | 0000h                 | 1 Ouuu             | uu Ouuu          |

| WDT Reset                          | 0000h                 | 0 uuuu             | uu uuuu          |

| WDT Wake-up from Sleep             | PC + 1                | 0 Ouuu             | uu uuuu          |

| Brown-out Reset                    | 0000h                 | 1 luuu             | 00 11u0          |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | 1 Ouuu             | uu uuuu          |

| RESET Instruction Executed         | 0000h                 | u uuuu             | uu u0uu          |

| Stack Overflow Reset (STVREN = 1)  | 0000h                 | u uuuu             | lu uuuu          |

| Stack Underflow Reset (STVREN = 1) | 0000h                 | u uuuu             | ul uuuu          |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

2: If a Status bit is not implemented, that bit will be read as '0'.

| FIGURE 7  | 7-2: I       | NTERRUPT      | LATENCY           |                  |       |             |             |             |

|-----------|--------------|---------------|-------------------|------------------|-------|-------------|-------------|-------------|

|           |              |               |                   |                  |       |             |             |             |

| OSC1      |              |               |                   |                  |       |             |             |             |

| CLKOUT    |              |               | Interru<br>during | pt Sampled<br>Q1 |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | PC            | PC                | +1               | 0004h | 0005h       |             |             |

| Execute   | 1 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP   | Inst(0004h) | L           |             |

|           |              |               |                   |                  |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | PC            | PC+1/FSR<br>ADDR  | New PC/<br>PC+1  | 0004h | 0005h       |             |             |

| Execute-  | 2 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP   | Inst(0004h) |             |             |

|           |              |               |                   | 1                |       |             |             |             |

| Interrupt |              |               |                   |                  |       |             |             |             |

| GIE       |              |               |                   |                  |       |             |             | (           |

| PC        | PC-1         | PC            | FSR ADDR          | PC+1             | PC+2  | 0004h       | 0005h       | )           |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP   | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt |              |               |                   |                  | -     |             |             |             |

| GIE       |              |               |                   |                  |       |             |             |             |

| PC        | PC-1         | РС            | FSR ADDR          | PC+1             | PC    | +2          | 0004h       | 0005h       |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP   | NOP         | NOP         | Inst(0004h) |

|           |              |               |                   |                  |       |             |             |             |

#### 7.6.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 7-2.

| Note: | Bit PEIE of the INTCON register must be |

|-------|-----------------------------------------|

|       | set to enable any peripheral interrupt. |

#### **REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1**

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE  | TMR2IE  | TMR1IE  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:         |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| R = Readab      | le bit      | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | U = Unimplemented bit, read as '0'                    |

| u = Bit is un   | changed     | x = Bit is unknown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is se | et          | '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

| bit 7           |             | Timer1 Gate Interrupt Enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | lo bit                                                |

|                 |             | s the Timer1 Gate Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                       |

|                 |             | es the Timer1 Gate Acquisition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                       |

| bit 6           |             | Converter (ADC) Interrupt E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                     |

|                 |             | s the ADC interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                       |

|                 | 0 = Disable | es the ADC interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

| bit 5           | RCIE: USA   | RT Receive Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e bit                                                 |

|                 |             | s the USART receive interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                                     |

|                 |             | es the USART receive interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                       |

| bit 4           |             | RT Transmit Interrupt Enabl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |

|                 |             | s the USART transmit interries the USART transmit interries the USART transmit interries the USART transmit interries the transmit interr |                                                       |

| bit 3           |             | nchronous Serial Port (MSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |

|                 | •           | s the MSSP interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |