#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1936-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower 8 bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants |             |         |      |

|-----------|-------------|---------|------|

| RETLW     | DATA0       | ;Index0 | data |

| RETLW     | DATA1       | ;Index1 | data |

| RETLW     | DATA2       |         |      |

| RETLW     | DATA3       |         |      |

| my_functi | on          |         |      |

| ; LO      | IS OF CODE. |         |      |

| MOVLW     | LOW cons    | tants   |      |

| MOVWF     | FSR1L       |         |      |

| MOVLW     | HIGH con    | stants  |      |

| MOVWF     | FSR1H       |         |      |

| MOVIW     | 0[FSR1]     |         |      |

| ;THE PROG | RAM MEMORY  | IS IN W |      |

|           |             |         |      |

# 3.2 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-3):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.5** "Indirect Addressing" for more information.

# 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation of the PIC16(L)F1934/6/7. These registers are listed below:

- INDF0

- INDF1

- PCL

- STATUS

- FSR0 Low

- FSR0 High

- FSR1 Low

- FSR1 High

- BSR

- WREG

- PCLATH

- INTCON

Note: The core registers are the first 12 addresses of every data memory bank.

#### **REGISTER 4-1: CONFIGURATION WORD 1**

| R/P-1/1              | R/P-1/1                                                                              | R/P-1/1                                                                                                                                                                                                              | R/P-1/1                                                | R/P-1/1                                 | R/P-1/1              | R/P-1/1           |  |  |  |

|----------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|----------------------|-------------------|--|--|--|

| FCMEN                | IESO                                                                                 | CLKOUTEN                                                                                                                                                                                                             | BOREN1                                                 | BOREN0                                  | CPD                  | CP                |  |  |  |

| oit 13               |                                                                                      | ·                                                                                                                                                                                                                    | •                                                      |                                         |                      | bit               |  |  |  |

| R/P-1/1              | R/P-1/1                                                                              | R/P-1/1                                                                                                                                                                                                              | R/P-1/1                                                | R/P-1/1                                 | R/P-1/1              | R/P-1/1           |  |  |  |

| MCLRE                | PWRTE                                                                                | WDTE1                                                                                                                                                                                                                | WDTE0                                                  | FOSC2                                   | FOSC1                | FOSC0             |  |  |  |

| bit 6                |                                                                                      |                                                                                                                                                                                                                      |                                                        |                                         |                      | bit               |  |  |  |

| Legend:              |                                                                                      |                                                                                                                                                                                                                      |                                                        |                                         |                      |                   |  |  |  |

| R = Readable bit     |                                                                                      | P = Programmab                                                                                                                                                                                                       | le bit                                                 | U = Unimplemente                        | ed bit_read as '1'   |                   |  |  |  |

| '0' = Bit is cleared |                                                                                      | '1' = Bit is set                                                                                                                                                                                                     |                                                        | •                                       | lank or after Bulk E | rase              |  |  |  |

| bit is cleared       |                                                                                      | 1 Dit io oct                                                                                                                                                                                                         |                                                        |                                         |                      |                   |  |  |  |

| bit 13               | 1 = Fail-Safe Clo                                                                    | fe Clock Monitor En<br>ock Monitor is enable<br>ock Monitor is disabl                                                                                                                                                | ed                                                     |                                         |                      |                   |  |  |  |

| bit 12               | 1 = Internal/Exte                                                                    | xternal Switchover b<br>rnal Switchover moo<br>rnal Switchover moo                                                                                                                                                   | de is enabled                                          |                                         |                      |                   |  |  |  |

| bit 11               | 1 = CLKOUT fu                                                                        | ock Out Enable bit<br>nction is disabled. I<br>nction is enabled or                                                                                                                                                  |                                                        | ction on RA6/CLKOU                      | JT                   |                   |  |  |  |

| bit 10-9             | 11 = BOR enable<br>10 = BOR enable                                                   | BOREN<1:0>: Brown-out Reset Enable bits <sup>(1)</sup><br>11 = BOR enabled<br>10 = BOR enabled during operation and disabled in Sleep<br>01 = BOR controlled by SBOREN bit of the PCON register<br>00 = BOR disabled |                                                        |                                         |                      |                   |  |  |  |

| bit 8                |                                                                                      | Protection bit <sup>(2)</sup><br>y code protection is<br>y code protection is                                                                                                                                        |                                                        |                                         |                      |                   |  |  |  |

| bit 7                | -                                                                                    | tion bit <sup>(3)</sup><br>mory code protectio<br>mory code protectio                                                                                                                                                |                                                        |                                         |                      |                   |  |  |  |

| bit 6                | MCLRE: RE3/MG<br>If LVP bit = 1:<br>This bit is igr<br>If LVP bit = 0:<br>1 = RE3/MC | CLR/VPP Pin Function                                                                                                                                                                                                 | on Select bit<br>is <del>MCLR</del> ; Wea <u>k pul</u> | I-up enabled.<br>R internally disabled; | Weak pull-up unde    | r control of WPUE |  |  |  |

| bit 5                | bit<br><b>PWRTE:</b> Power-<br>1 = PWRT disal<br>0 = PWRT enab                       |                                                                                                                                                                                                                      | (1)                                                    |                                         |                      |                   |  |  |  |

| bit 4-3              | WDTE<1:0>: Wa<br>11 = WDT enabl<br>10 = WDT enabl                                    | atchdog Timer Enab                                                                                                                                                                                                   | d disabled in Slee                                     |                                         |                      |                   |  |  |  |

3: The entire program memory will be erased when the code protection is turned off.

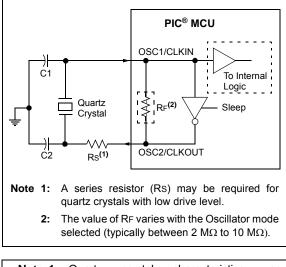

#### FIGURE 5-3:

#### QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

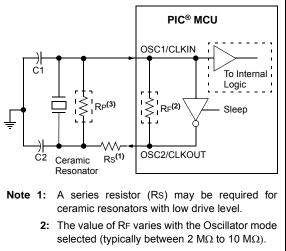

#### FIGURE 5-4: CERAMIC RESONATOR OPERATION

(XT OR HS MODE)

**3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

# 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see **Section 5.4 "Two-Speed Clock Start-up Mode"**).

# 5.2.1.4 4X PLL

The oscillator module contains a 4X PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4X PLL must fall within specifications. See the PLL Clock Timing specifications in the applicable Electrical Specifications Chapter.

The 4X PLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Word 2 to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Word 2 is programmed to a '1', then the value of SPLLEN is ignored.

#### 5.2.2.3 Internal Oscillator Frequency Adjustment

The 500 kHz internal oscillator is factory calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 5-3). Since the HFINTOSC and MFINTOSC clock sources are derived from the 500 kHz internal oscillator a change in the OSCTUNE register value will apply to both.

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number. A value of 0Fh will provide an adjustment to the maximum frequency. A value of 10h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# 5.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). Select 31 kHz, via software, using the IRCF<3:0> bits of the OSCCON register. See **Section 5.2.2.7** "Internal Oscillator **Clock Switch Timing**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<3:0> bits of the OSCCON register = 000) as the system clock source (SCS bits of the OSCCON register = 1x), or when any of the following are enabled:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired LF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

Peripherals that use the LFINTOSC are:

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The Low-Frequency Internal Oscillator Ready bit (LFIOFR) of the OSCSTAT register indicates when the LFINTOSC is running and can be utilized.

### 5.2.2.5 Internal Oscillator Frequency Selection

The system clock speed can be selected via software using the Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register.

The output of the 16 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). The Internal Oscillator Frequency Select bits IRCF<3:0> of the OSCCON register select the frequency output of the internal oscillators. One of the following frequencies can be selected via software:

- 32 MHz (requires 4X PLL)

- 16 MHz

- 8 MHz

- 4 MHz

- 2 MHz

- 1 MHz

- 500 kHz (Default after Reset)

- 250 kHz

- 125 kHz

- 62.5 kHz

- 31.25 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<3:0> bits  |

|-------|------------------------------------------|

|       | of the OSCCON register are set to '0111' |

|       | and the frequency selection is set to    |

|       | 500 kHz. The user can modify the IRCF    |

|       | bits to select a different frequency.    |

The IRCF<3:0> bits of the OSCCON register allow duplicate selections for some frequencies. These duplicate choices can offer system design trade-offs. Lower power consumption can be obtained when changing oscillator sources for a given frequency. Faster transition times can be obtained between frequency changes that use the same oscillator source.

| FIGURE 5-7:              | INTERNAL OSCILLATOR SWITCH TIMING                                  |

|--------------------------|--------------------------------------------------------------------|

| HEINTOSC/                | SINTOSC (SOCH and WOY (Exabled)<br><br>Otartup TimeCoycle Oycc<br> |

| IRCF <3:0>               | $\neq 0$ $\chi = 0$                                                |

| System Clock             |                                                                    |

| NENNIOSCI L<br>MENIIOSC  | FINTOSC (Either FSCM of WDT snabled)                               |

| HFINTOSC/<br>MEINTOSC    | 2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-2-                             |

| LFINTOSC -               |                                                                    |

| IRCF <3:0>               | $\neq 0$ $X = 0$                                                   |

| System Clock             |                                                                    |

| LEINTOSO F<br>LEINTOSO - | IFINTOSC/MFINTOSC                                                  |

| BEENTOSC/<br>MENTOSC     |                                                                    |

| \$PCF <3:0>              | • 6 X # 0                                                          |

| System Crock             |                                                                    |

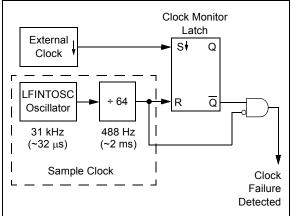

# 5.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word 1. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, EC, Timer1 oscillator and RC).

FIGURE 5-9: FSCM BLOCK DIAGRAM

# 5.5.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 5-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

# 5.5.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR2 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE2 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<3:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

### 5.5.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the SCS bits of the OSCCON register. When the SCS bits are changed, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 5.5.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

Note: Due to the wide range of oscillator start-up times, the Fail-Safe circuit is not active during oscillator start-up (i.e., after exiting Reset or Sleep). After an appropriate amount of time, the user should check the Status bits in the OSCSTAT register to verify the oscillator start-up and that the system clock switchover has successfully completed.

#### 11.3.2 ERASING FLASH PROGRAM MEMORY

While executing code, program memory can only be erased by rows. To erase a row:

- 1. Load the EEADRH:EEADRL register pair with the address of new row to be erased.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD, FREE, and WREN bits of the EECON1 register.

- 4. Write 55h, then AAh, to EECON2 (Flash programming unlock sequence).

- 5. Set control bit WR of the EECON1 register to begin the erase operation.

- 6. Poll the FREE bit in the EECON1 register to determine when the row erase has completed.

See Example 11-4.

After the "BSF EECON1, WR" instruction, the processor requires two cycles to set up the erase operation. The user must place two NOP instructions after the WR bit is set. The processor will halt internal operations for the typical 2 ms erase time. This is not Sleep mode as the clocks and peripherals will continue to run. After the erase cycle, the processor will resume operation with the third instruction after the EECON1 write instruction.

# 11.3.3 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the starting address of the word(s) to be programmed.

- 2. Load the write latches with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 11-2 (block writes to program memory with 8 write latches) for more details. The write latches are aligned to the address boundary defined by EEADRL as shown in Table 11-1. Write operations do not cross these boundaries. At the completion of a program memory write operation, the write latches are reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a block of program memory. These steps are divided into two parts. First, all write latches are loaded with data except for the last program memory location. Then, the last write latch is loaded and the programming sequence is initiated. A special unlock sequence is required to load a write latch with data or initiate a Flash programming operation. This unlock sequence should not be interrupted.

- 1. Set the EEPGD and WREN bits of the EECON1 register.

- 2. Clear the CFGS bit of the EECON1 register.

- Set the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the EEADRH:EEADRL register pair with the address of the location to be written.

- 5. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The write latch is now loaded.

- 7. Increment the EEADRH:EEADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the EECON1 register. When the LWLO bit of the EECON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the EEDATH:EEDATL register pair with the program memory data to be written.

- 11. Write 55h, then AAh, to EECON2, then set the WR bit of the EECON1 register (Flash programming unlock sequence). The entire latch block is now written to Flash program memory.

It is not necessary to load the entire write latch block with user program data. However, the entire write latch block will be written to program memory.

An example of the complete write sequence for eight words is shown in Example 11-5. The initial address is loaded into the EEADRH:EEADRL register pair; the eight words of data are loaded using indirect addressing.

Note: The code sequence provided in Example 11-5 must be repeated multiple times to fully program an erased program memory row.

#### REGISTER 11-1: EEDATL: EEPROM DATA LOW BYTE REGISTER

| R/W-x/u           | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u         | R/W-x/u            | R/W-x/u               | R/W-x/u |

|-------------------|---------|---------------------|---------|-----------------|--------------------|-----------------------|---------|

|                   |         |                     | EEDA    | T<7:0>          |                    |                       |         |

| bit 7             |         |                     |         |                 |                    |                       | bit 0   |

|                   |         |                     |         |                 |                    |                       |         |

| Legend:           |         |                     |         |                 |                    |                       |         |

| R = Readable bit  | t       | W = Writable bit    |         | U = Unimpleme   | ented bit, read as | '0'                   |         |

| u = Bit is unchan | iged    | x = Bit is unknow   | 'n      | -n/n = Value at | POR and BOR/V      | alue at all other Res | sets    |

| '1' = Bit is set  |         | '0' = Bit is cleare | d       |                 |                    |                       |         |

bit 7-0

EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

#### REGISTER 11-2: EEDATH: EEPROM DATA HIGH BYTE REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|

| —     | —   |         | EEDAT<13:8> |         |         |         |         |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

#### REGISTER 11-3: EEADRL: EEPROM ADDRESS LOW BYTE REGISTER

| R/W-0/0            | R/W-0/0 | R/W-0/0              | R/W-0/0 | R/W-0/0         | R/W-0/0            | R/W-0/0              | R/W-0/0 |

|--------------------|---------|----------------------|---------|-----------------|--------------------|----------------------|---------|

|                    |         |                      | EEAD    | R<7:0>          |                    |                      |         |

| bit 7              |         |                      |         |                 |                    |                      | bit 0   |

|                    |         |                      |         |                 |                    |                      |         |

| Legend:            |         |                      |         |                 |                    |                      |         |

| R = Readable bit   |         | W = Writable bit     |         | U = Unimpleme   | ented bit, read as | ʻ0'                  |         |

| u = Bit is unchang | ged     | x = Bit is unknowr   | า       | -n/n = Value at | POR and BOR/V      | alue at all other Re | esets   |

| '1' = Bit is set   |         | '0' = Bit is cleared |         |                 |                    |                      |         |

bit 7-0 EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

#### REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-------------|---------|---------|---------|

| —     |         |         |         | EEADR<14:8> | >       |         |         |

| bit 7 |         |         |         |             |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

| U-0             | R/W-0/0                                                                                         | R/W-0/0                                                                                                           | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|------------------|--------------|--|--|--|--|

| _               | CCP3SEL                                                                                         | T1GSEL                                                                                                            | P2BSEL         | SRNQSEL        | C2OUTSEL         | SSSEL            | CCP2SEL      |  |  |  |  |

| bit 7           |                                                                                                 |                                                                                                                   |                |                |                  |                  | bit 0        |  |  |  |  |

|                 |                                                                                                 |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

| Legend:         |                                                                                                 |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

| R = Readabl     |                                                                                                 | W = Writable                                                                                                      |                | -              | mented bit, read |                  |              |  |  |  |  |

| u = bit is unc  | -                                                                                               | x = Bit is unk                                                                                                    |                | -n/n = Value a | at POR and BOF   | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is se | t                                                                                               | '0' = Bit is cle                                                                                                  | ared           |                |                  |                  |              |  |  |  |  |

| bit 7           | Unimplement                                                                                     | ed: Read as '0                                                                                                    | ,              |                |                  |                  |              |  |  |  |  |

| bit 6           | •                                                                                               | CP3 Input/Out                                                                                                     |                | ion bit        |                  |                  |              |  |  |  |  |

|                 |                                                                                                 | vices (PIC16F                                                                                                     |                |                |                  |                  |              |  |  |  |  |

|                 | 0 = CCP3/P3                                                                                     | BA function is c                                                                                                  | on RC6/TX/CK   | C/CCP3/P3A/SE  | EG9              |                  |              |  |  |  |  |

|                 |                                                                                                 | 1 = CCP3/P3A function is on RB5/AN13/CPS5/CCP3/P3A/T1G/COM1                                                       |                |                |                  |                  |              |  |  |  |  |

|                 | -                                                                                               | For 40-Pin Devices (PIC16F1934/7):                                                                                |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 | 0 = CCP3/P3A function is on RE0/AN5/CCP3/P3A/SEG21<br>1 = CCP3/P3A function is on RB5/AN13/CPS5/CCP3/P3A/T1G/COM1 |                |                |                  |                  |              |  |  |  |  |

| bit 5           | <b>TIGSEL</b> : Timer1 Gate Input Pin Selection bit                                             |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

|                 | 0 = T1G function is on RB5/AN13/CPS5/CCP3/P3A/T1G/COM1                                          |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

|                 | 1 = T1G function is on RC4/SDI/SDA/T1G/SEG11                                                    |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

| bit 4           | P2BSEL: CCP2 PWM B Output Pin Selection bit                                                     |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

|                 | For 28-Pin De                                                                                   | For 28-Pin Devices (PIC16F1936):                                                                                  |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 | 0 = P2B function is on RC0/T1OSO/T1CKI/P2B                                                                        |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 | 1 = P2B function is on RB5/AN13/P2B/CPS5/T1G/COM1                                                                 |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 | For 40-Pin Devices (PIC16F1934/7):<br>0 = P2B function is on RC0/T1OSO/T1CKI/P2B                                  |                |                |                  |                  |              |  |  |  |  |

|                 | 1 = P2B function is on RD2/CPS10/P2B                                                            |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

| bit 3           | SRNQSEL: S                                                                                      | R Latch nQ O                                                                                                      | utput Pin Sele | ction bit      |                  |                  |              |  |  |  |  |

|                 | 0 = SRnQ function is on RA5/AN4/C2OUT/SRnQ/SS/CPS7/SEG5/VCAP                                    |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 |                                                                                                                   |                |                | nQ/SS/SEG12/V    | CAP              |              |  |  |  |  |

| bit 2           |                                                                                                 | C2OUTSEL: Comparator C2 Output Pin Selection bit                                                                  |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 | 0 = C2OUT function is on RA5/AN4/C2OUT/SRnQ/SS/CPS7/SEG5/VCAP                                                     |                |                |                  |                  |              |  |  |  |  |

| bit 1           | 1 = C2OUT function is on RA0/AN0/C12IN0-/C2OUT/SRnQ/SS/SEG12/VCAP                               |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

|                 | SSSEL: SS Input Pin Selection bit<br>0 = SS function is on RA5/AN4/C2OUT/SRNQ/SS/CPS7/SEG5/Vcap |                                                                                                                   |                |                |                  |                  |              |  |  |  |  |

|                 |                                                                                                 |                                                                                                                   |                |                | /SS/SEG12/Vca    | P                |              |  |  |  |  |

| bit 0           |                                                                                                 | CP2 Input/Out                                                                                                     |                |                |                  |                  |              |  |  |  |  |

|                 | 0 = CCP2/P2                                                                                     | 2A function is c                                                                                                  | on RC1/T1OS    | /CCP2/P2A      |                  |                  |              |  |  |  |  |

|                 | 1 = CCP2/P2                                                                                     | 2A function is c                                                                                                  | n RB3/AN9/C    | 12IN2-/CPS3/0  | CCP2/P2A/VLCI    | 03               |              |  |  |  |  |

# REGISTER 12-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELB | _      | —      | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 139                 |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 98                  |

| IOCBF  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 152                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 152                 |

| IOCBP  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 152                 |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 138                 |

TABLE 13-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupt-on-Change.

# 14.3 FVR Control Registers

# REGISTER 14-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 R-q/q                    | R/W-0/0                                                                                                                   | R/W-0/0                                         | R/W-0/0                                                     | R/W-0/0                                                     | R/W-0/0                                                  | R/W-0/0      |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------|--------------|

| FVREN FVRRDY                     | (1) TSEN                                                                                                                  | TSRNG                                           | CDAF                                                        | /R<1:0>                                                     | ADFVI                                                    | R<1:0>       |

| bit 7                            |                                                                                                                           |                                                 | ·                                                           |                                                             |                                                          | bit (        |

|                                  |                                                                                                                           |                                                 |                                                             |                                                             |                                                          |              |

| Legend:                          |                                                                                                                           |                                                 |                                                             |                                                             |                                                          |              |

| R = Readable bit                 | W = Writable                                                                                                              | bit                                             | U = Unimpler                                                | nented bit, read                                            | as '0'                                                   |              |

| u = Bit is unchanged             | x = Bit is unkr                                                                                                           | x = Bit is unknown                              |                                                             | at POR and BOI                                              | R/Value at all c                                         | other Resets |

| '1' = Bit is set                 | '0' = Bit is cle                                                                                                          | ared                                            | q = Value dep                                               | pends on condit                                             | ion                                                      |              |

| 0 = Fixed                        | Fixed Voltage Refe<br>I Voltage Referenc<br>I Voltage Referenc                                                            | e is disabled                                   | bit                                                         |                                                             |                                                          |              |

| 0 = Fixed                        | : Fixed Voltage Ref<br>I Voltage Referenc<br>I Voltage Referenc                                                           | e output is no                                  | t ready or not e                                            | nabled                                                      |                                                          |              |

| 0 = Temp                         | mperature Indicato<br>perature Indicator is<br>perature Indicator is                                                      | s disabled                                      | ()<br>()                                                    |                                                             |                                                          |              |

| 0 = VOUT                         | Temperature Indica<br>= VDD - 2VT (Low<br>= VDD - 4VT (High                                                               | Range)                                          | election bit <sup>(3)</sup>                                 |                                                             |                                                          |              |

| 00 = Com<br>01 = Com<br>10 = Com | <1:0>: Comparato<br>parator and DAC I<br>parator and DAC I<br>parator and DAC I<br>parator and DAC I<br>parator and DAC I | Fixed Voltage<br>Fixed Voltage<br>Fixed Voltage | Reference Per<br>Reference Per<br>Reference Per             | ipheral output is<br>ipheral output is<br>ipheral output is | s off.<br>s 1x (1.024V)<br>s 2x (2.048V) <mark>(2</mark> |              |

| 00 = ADC<br>01 = ADC<br>10 = ADC | 1:0>: ADC Fixed V<br>Fixed Voltage Re<br>Fixed Voltage Re<br>Fixed Voltage Re<br>Fixed Voltage Re<br>Fixed Voltage Re     | ference Perip<br>ference Perip<br>ference Perip | heral output is o<br>heral output is f<br>heral output is f | off.<br>1x (1.024V)<br>2x (2.048V) <b><sup>(2)</sup></b>    |                                                          |              |

|                                  | ways '1' on devices<br>Reference output c                                                                                 | •                                               |                                                             | ).                                                          |                                                          |              |

3: See Section 16.0 "Temperature Indicator Module" for additional information.

#### TABLE 14-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|--------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | CDAFV | R<1:0> | ADFV  | R<1:0> | 156                 |

Legend: Shaded cells are not used with the Fixed Voltage Reference.

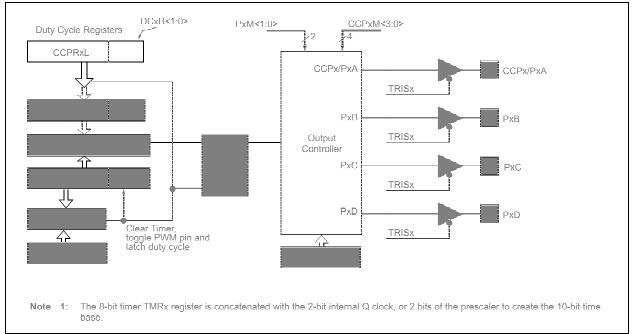

# 23.4 PWM (Enhanced Mode)

The enhanced PWM function described in this section is available for CCP modules ECCP1, ECCP2 and ECCP3, with any differences between modules noted.

The enhanced PWM mode generates a Pulse-Width Modulation (PWM) signal on up to four different output pins with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PRx registers

- TxCON registers

- · CCPRxL registers

- CCPxCON registers

The ECCP modules have the following additional PWM registers which control Auto-shutdown, Auto-restart, Dead-band Delay and PWM Steering modes:

- · CCPxAS registers

- PSTRxCON registers

- PWMxCON registers

The enhanced PWM module can generate the following five PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward Mode

- Full-Bridge PWM, Reverse Mode

- · Single PWM with PWM Steering Mode

To select an Enhanced PWM Output mode, the PxM bits of the CCPxCON register must be configured appropriately.

The PWM outputs are multiplexed with I/O pins and are designated PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Figure 23-5 shows an example of a simplified block diagram of the Enhanced PWM module.

Table 23-9 shows the pin assignments for various Enhanced PWM modes.

- Note 1: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

- 2: Clearing the CCPxCON register will relinquish control of the CCPx pin.

- **3:** Any pin not used in the enhanced PWM mode is available for alternate pin functions, if applicable.

- 4: To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

# FIGURE 23-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

#### 24.6.10 SLEEP OPERATION

While in Sleep mode, the I<sup>2</sup>C slave module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 24.6.11 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

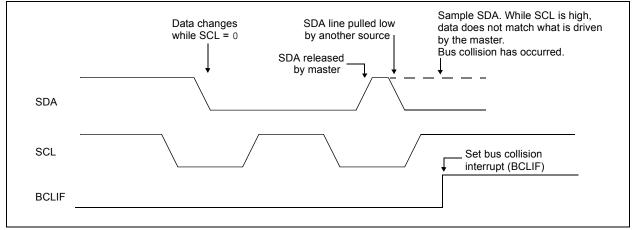

#### 24.6.12 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit of the SSPSTAT register is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the SSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed by hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 24.6.13 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin is '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF, and reset the I<sup>2</sup>C port to its Idle state (Figure 24-31).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 24-32: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

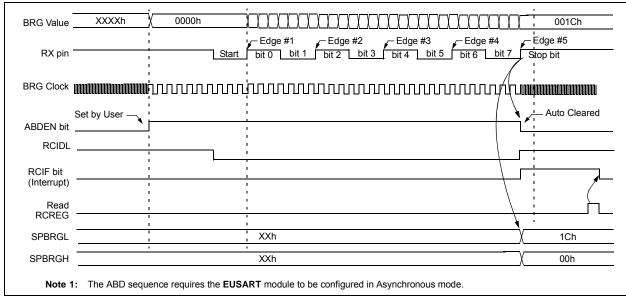

#### 25.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUDCON register starts the auto-baud calibration sequence (Figure 25-6). While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SPBRG begins counting up using the BRG counter clock as shown in Table 25-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SPBRGH, SPBRGL register pair, the ABDEN bit is automatically cleared and the RCIF interrupt flag is set. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded. When calibrating for modes that do not use the SPBRGH register the user can verify that the SPBRGL register did not overflow by checking for 00h in the SPBRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 25-6. During ABD, both the SPBRGH and SPBRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SPBRGH and SPBRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte following the Break character (see Section 25.3.3 "Auto-Wake-up on Break").

- It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at 1. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SPBRGH:SPBRGL register pair.

| TABLE 25-6: | BRG COUNTER CLOCK RATES |

|-------------|-------------------------|

|-------------|-------------------------|

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SPBRGL and SPBRGH registers are both used as a 16-bit counter, independent of BRG16 setting.

# FIGURE 25-6: AUTOMATIC BAUD RATE CALIBRATION

# 27.11 Operation During Sleep

The LCD module can operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Setting the SLPEN bit allows the LCD module to go to Sleep. Clearing the SLPEN bit allows the module to continue to operate during Sleep.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will cease all functions and go into a very low-current Consumption mode. The module will stop operation immediately and drive the minimum LCD voltage on both segment and common lines. Figure 27-20 shows this operation.

The LCD module can be configured to operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Clearing SLPEN and correctly configuring the LCD module clock will allow the LCD module to operate during Sleep. Setting SLPEN and correctly executing the LCD module shutdown will disable the LCD module during Sleep and save power.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will immediately cease all functions, drive the outputs to Vss and go into a very Low-Current mode. The SLEEP instruction should only be executed after the LCD module has been disabled and the current cycle completed, thus ensuring that there are no DC voltages on the glass. To disable the LCD module, clear the LCDEN bit. The LCD module will complete the disabling process after the current frame, clear the LCDA bit and optionally cause an interrupt.

The steps required to properly enter Sleep with the LCD disabled are:

- Clear LCDEN

- Wait for LCDA = 0 either by polling or by interrupt

- Execute SLEEP

If SLPEN = 0 and SLEEP is executed while the LCD module clock source is FOSC/4, then the LCD module will halt with the pin driving the last LCD voltage pattern. Prolonged exposure to a fixed LCD voltage pattern will cause damage to the LCD glass. To prevent LCD glass damage, either perform the proper LCD module shutdown prior to Sleep, or change the LCD module clock to allow the LCD module to continue operation during Sleep.

If a SLEEP instruction is executed and SLPEN = 0 and the LCD module clock is either T1OSC or LFINTOSC, the module will continue to display the current contents of the LCDDATA registers. While in Sleep, the LCD data cannot be changed. If the LCDIE bit is set, the device will wake from Sleep on the next LCD frame boundary. The LCD module current consumption will not decrease in this mode; however, the overall device power consumption will be lower due to the shutdown of the CPU and other peripherals. Table 27-8 shows the status of the LCD module during a Sleep while using each of the three available clock sources.

| Mater | When the LODEN bit is cleared the LOD        |

|-------|----------------------------------------------|

| Note: | When the LCDEN bit is cleared, the LCD       |

|       | module will be disabled at the completion    |

|       | of frame. At this time, the port pins will   |

|       | revert to digital functionality. To minimize |

|       | power consumption due to floating digital    |

|       | inputs, the LCD pins should be driven low    |

|       | using the PORT and TRIS registers.           |

If a SLEEP instruction is executed and SLPEN = 0, the module will continue to display the current contents of the LCDDATA registers. To allow the module to continue operation while in Sleep, the clock source must be either the LFINTOSC or T1OSC external oscillator. While in Sleep, the LCD data cannot be changed. The LCD module current consumption will not decrease in this mode; however, the overall consumption of the device will be lower due to shut down of the core and other peripheral functions.

Table 27-8 shows the status of the LCD module during Sleep while using each of the three available clock sources:

| TABLE 27-8: | LCD MODULE STATUS |

|-------------|-------------------|

|             | DURING SLEEP      |

| Clock Source | SLPEN | Operational<br>During Sleep |

|--------------|-------|-----------------------------|

| T1OSC        | 0     | Yes                         |

| 11030        | 1     | No                          |

| LFINTOSC     | 0     | Yes                         |

| LEINTOSC     | 1     | No                          |

| Fosc/4       | 0     | No                          |

| F05C/4       | 1     | No                          |

| Note: | The LFINTOSC or external T1OSC         |

|-------|----------------------------------------|

|       | oscillator must be used to operate the |

|       | LCD module during Sleep.               |

If LCD interrupts are being generated (Type-B waveform with a multiplex mode not static) and LCDIE = 1, the device will awaken from Sleep on the next frame boundary.

# 27.12 Configuring the LCD Module

The following is the sequence of steps to configure the LCD module.

- 1. Select the frame clock prescale using bits LP<3:0> of the LCDPS register.

- 2. Configure the appropriate pins to function as segment drivers using the LCDSEn registers.

- 3. Configure the LCD module for the following using the LCDCON register:

- Multiplex and Bias mode, bits LMUX<1:0>

- Timing source, bits CS<1:0>

- Sleep mode, bit SLPEN

- 4. Write initial values to pixel data registers, LCDDATA0 through LCDDATA11.

- 5. Clear LCD Interrupt Flag, LCDIF bit of the PIR2 register and if desired, enable the interrupt by setting bit LCDIE of the PIE2 register.

- Configure bias voltages by setting the LCDRL, LCDREF and the associated ANSELx registers as needed.

- 7. Enable the LCD module by setting bit LCDEN of the LCDCON register.

# 27.13 Disabling the LCD Module

To disable the LCD module, write all '0's to the LCDCON register.

# 27.14 LCD Current Consumption

When using the LCD module the current consumption consists of the following three factors:

- Oscillator Selection

- · LCD Bias Source

- Capacitance of the LCD segments

The current consumption of just the LCD module can be considered negligible compared to these other factors.

#### 27.14.1 OSCILLATOR SELECTION

The current consumed by the clock source selected must be considered when using the LCD module. See the applicable Electrical Specifications Chapter for oscillator current consumption information.

#### 27.14.2 LCD BIAS SOURCE

The LCD bias source, internal or external, can contribute significantly to the current consumption. Use the highest possible resistor values while maintaining contrast to minimize current.

# 27.14.3 CAPACITANCE OF THE LCD SEGMENTS

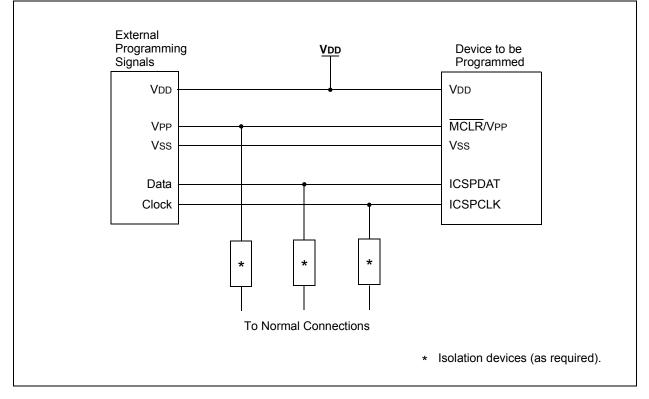

The LCD segments which can be modeled as capacitors which must be both charged and discharged every frame. The size of the LCD segment and its technology determines the segment's capacitance. For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

| SPI Slave Mode (CKE = 1) 408                       |

|----------------------------------------------------|

| Synchronous Reception (Master Mode, SREN) 317      |

| Synchronous Transmission                           |

| Synchronous Transmission (Through TXEN)            |

| Timer0 and Timer1 External Clock 401               |

| Timer1 Incrementing Edge                           |

| Two Speed Start-up                                 |

| Type-A in 1/2 MUX, 1/2 Bias Drive                  |

| Type-A in 1/2 MUX, 1/3 Bias Drive                  |

| Type-A in 1/3 MUX, 1/3 Bias Drive                  |

|                                                    |

| Type-A in 1/3 MUX, 1/3 Bias Drive                  |

| Type-A in 1/4 MUX, 1/3 Bias Drive                  |

| Type-A/Type-B in Static Drive                      |

| Type-B in 1/2 MUX, 1/2 Bias Drive                  |

| Type-B in 1/2 MUX, 1/3 Bias Drive                  |

| Type-B in 1/3 MUX, 1/2 Bias Drive                  |

| Type-B in 1/3 MUX, 1/3 Bias Drive                  |

| Type-B in 1/4 MUX, 1/3 Bias Drive                  |

| USART Synchronous Receive (Master/Slave) 406       |

| USART Synchronous Transmission (Master/Slave). 405 |

| Wake-up from Interrupt                             |

| Timing Diagrams and Specifications                 |

| PLL Clock                                          |

| Timing Parameter Symbology                         |

| Timing Requirements                                |

| I <sup>2</sup> C Bus Data                          |

| I2C Bus Start/Stop Bits                            |

| SPI Mode                                           |

| TMR0 Register                                      |

|                                                    |

| TMR1H Register                                     |

| TMR1L Register                                     |

| TMR2 Register                                      |

| TRIS                                               |

| TRISA Register                                     |

| TRISB                                              |

| TRISB Register 40, 140                             |

| TRISC                                              |

| TRISC Register40, 144                              |

| TRISD 146                                          |

| TRISD Register40, 147                              |

| TRISE                                              |

| TRISE Register                                     |

| Two-Speed Clock Start-up Mode                      |

| TXCON (Timer2/4/6) Register                        |

| TXREG                                              |

| TXREG Register                                     |

| TXSTA Register                                     |

| BRGH Bit                                           |

|                                                    |

| U                                                  |

#### W

| Wake-up on Break                     | 311 |

|--------------------------------------|-----|

| Wake-up Using Interrupts             | 112 |

| Watchdog Timer (WDT)                 |     |

| Associated Registers                 |     |

| Configuration Word w/ Watchdog Timer |     |

| Modes                                | 114 |

| Specifications                       |     |

| WCOL                                 |     |

| WCOL Status Flag 273                 |     |

| WDTCON Register                      |     |

| WPUB Register                        |     |

| Write Protection                     |     |

| WWW Address                          |     |

| WWW, On-Line Support                 |     |

|                                      |     |

# ۷

USART

VREF. SEE ADC Reference Voltage

Synchronous Master Mode