Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 14KB (8K x 14)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1936-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

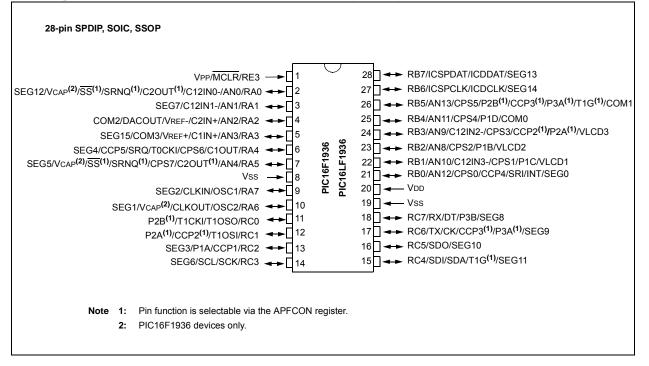

### Pin Diagram – 28-Pin SPDIP/SOIC/SSOP (PIC16(L)F1936)

# TABLE 3-11:PIC16(L)F1934/6/7 MEMORYMAP, BANK 31

|      |      | Bank 31                      |                        |

|------|------|------------------------------|------------------------|

|      | F8Ch |                              |                        |

|      |      | Unimplemented<br>Read as '0' |                        |

|      | FE3h |                              |                        |

|      | FE4h | STATUS_SHAD                  |                        |

|      | FE5h | WREG_SHAD                    |                        |

|      | FE6h | BSR_SHAD                     |                        |

|      | FE7h | PCLATH_SHAD                  |                        |

|      | FE8h | FSR0L_SHAD                   |                        |

|      | FE9h | FSR0H_SHAD                   |                        |

|      | FEAh | FSR1L_SHAD                   |                        |

|      | FEBh | FSR1H_SHAD                   |                        |

|      | FECh | —                            |                        |

|      | FEDh | STKPTR                       |                        |

|      | FEEh | TOSL                         |                        |

|      | FEFh | TOSH                         |                        |

| Lege |      | = Unimplemented data<br>'0'. | memory locations, read |

# 3.2.6 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device            | Bank(s) | Page No. |

|-------------------|---------|----------|

|                   | 0       | 39       |

|                   | 1       | 40       |

|                   | 2       | 41       |

|                   | 3       | 42       |

|                   | 4       | 43       |

|                   | 5       | 44       |

| PIC16(L)F1934/6/7 | 6       | 45       |

|                   | 7       | 46       |

|                   | 8       | 47       |

|                   | 9-14    | 48       |

|                   | 15      | 49       |

|                   | 16-30   | 51       |

|                   | 31      | 52       |

| Address                | Name   | Bit 7                      | Bit 6                                                                                                     | Bit 5           | Bit 4           | Bit 3          | Bit 2       | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|----------------------------|-----------------------------------------------------------------------------------------------------------|-----------------|-----------------|----------------|-------------|-------|---------|----------------------|---------------------------------|

| Bank 8                 |        |                            |                                                                                                           |                 |                 |                |             |       |         |                      |                                 |

| 400h <sup>(2)</sup>    | INDF0  | Addressing<br>(not a physi |                                                                                                           | ses contents o  | of FSR0H/FSF    | ROL to address | data memory | /     |         | XXXX XXXX            | XXXX XXXX                       |

| 401h <sup>(2)</sup>    | INDF1  |                            | Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                 |                 |                |             |       |         |                      | XXXX XXXX                       |

| 402h <sup>(2)</sup>    | PCL    | Program Co                 | ounter (PC) Le                                                                                            | ast Significant | t Byte          |                |             |       |         | 0000 0000            | 0000 0000                       |

| 403h <sup>(2)</sup>    | STATUS | _                          | _                                                                                                         | —               | TO              | PD             | Z           | DC    | С       | 1 1000               | q quuu                          |

| 404h <sup>(2)</sup>    | FSR0L  | Indirect Data              | a Memory Add                                                                                              | Iress 0 Low Po  | ointer          | •              | •           | •     | •       | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(2)</sup>    | FSR0H  | Indirect Data              | a Memory Add                                                                                              | lress 0 High P  | ointer          |                |             |       |         | 0000 0000            | 0000 0000                       |

| 406h <sup>(2)</sup>    | FSR1L  | Indirect Data              | a Memory Add                                                                                              | Iress 1 Low Po  | ointer          |                |             |       |         | 0000 0000            | uuuu uuuu                       |

| 407h <sup>(2)</sup>    | FSR1H  | Indirect Date              | a Memory Add                                                                                              | Iress 1 High P  | ointer          |                |             |       |         | 0000 0000            | 0000 0000                       |

| 408h <sup>(2)</sup>    | BSR    | _                          | —                                                                                                         | —               |                 | E              | BSR<4:0>    |       |         | 0 0000               | 0 0000                          |

| 409h <sup>(2)</sup>    | WREG   | Working Re                 | gister                                                                                                    |                 |                 |                |             |       |         | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1, 2)</sup> | PCLATH | _                          | Write Buffer f                                                                                            | or the upper 7  | bits of the Pre | ogram Counter  | r           |       |         | -000 0000            | -000 0000                       |

| 40Bh <sup>(2)</sup>    | INTCON | GIE                        | PEIE                                                                                                      | TMR0IE          | INTE            | IOCIE          | TMR0IF      | INTF  | IOCIF   | 0000 0000            | 0000 0000                       |

| 40Ch                   |        | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 40Dh                   | _      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 40Eh                   | _      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 40Fh                   | _      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 410h                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 411h                   | _      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 412h                   | _      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 413h                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 414h                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 415h                   | TMR4   | Timer4 Mod                 | ule Register                                                                                              |                 |                 |                |             |       |         | 0000 0000            | 0000 0000                       |

| 416h                   | PR4    | Timer4 Peri                | od Register                                                                                               |                 |                 |                |             |       |         | 1111 1111            | 1111 1111                       |

| 417h                   | T4CON  | _                          |                                                                                                           | T4OUT           | PS<3:0>         |                | TMR40N      | T4CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 418h                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | —                               |

| 419h                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

| 41Ah                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | —                               |

| 41Bh                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | —                               |

| 41Ch                   | TMR6   | Timer6 Mod                 | ule Register                                                                                              |                 |                 |                |             |       |         | 0000 0000            | 0000 0000                       |

| 41Dh                   | PR6    | Timer6 Peri                | od Register                                                                                               |                 |                 |                |             |       |         | 1111 1111            | 1111 1111                       |

| 41Eh                   | T6CON  | _                          |                                                                                                           | T6OUT           | PS<3:0>         |                | TMR6ON      | T6CKF | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh                   | —      | Unimpleme                  | nted                                                                                                      |                 |                 |                |             |       |         | _                    | _                               |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-12

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

#### **TABLE 3-12:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

| Address  | Name                         | Bit 7         | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2         | Bit 1         | Bit 0         | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|----------|------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|----------------------|---------------------------------|

| Bank 15  | (Continued)                  |               |               |               |               |               |               |               |               |                      |                                 |

| 7A6h     | LCDDATA6                     | SEG7<br>COM2  | SEG6<br>COM2  | SEG5<br>COM2  | SEG4<br>COM2  | SEG3<br>COM2  | SEG2<br>COM2  | SEG1<br>COM2  | SEG0<br>COM2  | XXXX XXXX            | uuuu uuuu                       |

| 7A7h     | LCDDATA7                     | SEG15<br>COM2 | SEG14<br>COM2 | SEG13<br>COM2 | SEG12<br>COM2 | SEG11<br>COM2 | SEG10<br>COM2 | SEG9<br>COM2  | SEG8<br>COM2  | XXXX XXXX            | uuuu uuuu                       |

| 7A8h     | LCDDATA8 <sup>(</sup><br>3)  | SEG23<br>COM2 | SEG22<br>COM2 | SEG21<br>COM2 | SEG20<br>COM2 | SEG19<br>COM2 | SEG18<br>COM2 | SEG17<br>COM2 | SEG16<br>COM2 | XXXX XXXX            | uuuu uuuu                       |

| 7A9h     | LCDDATA9                     | SEG7<br>COM3  | SEG6<br>COM3  | SEG5<br>COM3  | SEG4<br>COM3  | SEG3<br>COM3  | SEG2<br>COM3  | SEG1<br>COM3  | SEG0<br>COM3  | XXXX XXXX            | uuuu uuuu                       |

| 7AAh     | LCDDATA1<br>0                | SEG15<br>COM3 | SEG14<br>COM3 | SEG13<br>COM3 | SEG12<br>COM3 | SEG11<br>COM3 | SEG10<br>COM3 | SEG9<br>COM3  | SEG8<br>COM3  | XXXX XXXX            | uuuu uuuu                       |

| 7ABh     | LCDDATA11 <sup>(</sup><br>3) | SEG23<br>COM3 | SEG22<br>COM3 | SEG21<br>COM3 | SEG20<br>COM3 | SEG19<br>COM3 | SEG18<br>COM3 | SEG17<br>COM3 | SEG16<br>COM3 | XXXX XXXX            | uuuu uuuu                       |

| 7ACh     | —                            | Unimplemer    | nted          |               |               |               |               |               |               | -                    | —                               |

| <br>7EFh |                              |               |               |               |               |               |               |               |               |                      |                                 |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred Note 1: to the upper byte of the program counter.

2: These registers can be addressed from any bank.

These registers/bits are not implemented on PIC16(L)F1936 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

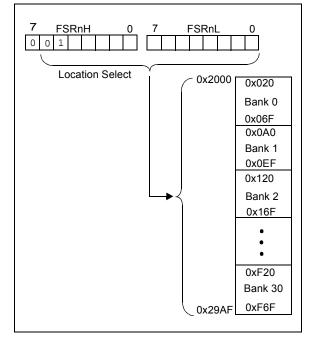

#### 3.5.2 LINEAR DATA MEMORY

The linear data memory is the region from FSR address 0x2000 to FSR address 0x29AF. This region is a virtual region that points back to the 80-byte blocks of GPR memory in all the banks.

Unimplemented memory reads as 0x00. Use of the linear data memory region allows buffers to be larger than 80 bytes because incrementing the FSR beyond one bank will go directly to the GPR memory of the next bank.

The 16 bytes of common memory are not included in the linear data memory region.

FIGURE 3-11: LINEAR DATA MEMORY MAP

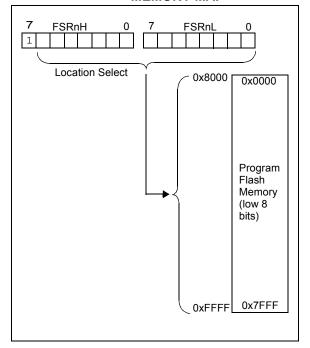

### 3.5.3 PROGRAM FLASH MEMORY

To make constant data access easier, the entire program Flash memory is mapped to the upper half of the FSR address space. When the MSB of FSRnH is set, the lower 15 bits are the address in program memory which will be accessed through INDF. Only the lower 8 bits of each memory location is accessible via INDF. Writing to the program Flash memory cannot be accomplished via the FSR/INDF interface. All instructions that access program Flash memory via the FSR/INDF interface will require one additional instruction cycle to complete.

FIGURE 3-12: PROGRAM FLASH MEMORY MAP

#### **REGISTER 4-1: CONFIGURATION WORD 1 (CONTINUED)**

- bit 2-0

- FOSC<2:0>: Oscillator Selection bits

- 111 = ECH: External Clock, High-Power mode: CLKIN on RA7/OSC1/CLKIN

- 110 = ECM: External Clock, Medium-Power mode: CLKIN on RA7/OSC1/CLKIN

- 101 = ECL: External Clock, Low-Power mode: CLKIN on RA7/OSC1/CLKIN

- 100 = INTOSC oscillator: I/O function on RA7/OSC1/CLKIN

- 011 = EXTRC oscillator: RC function on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT pin and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT pin and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT pin and RA7/OSC1/CLKIN

- Note 1: Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire data EEPROM will be erased when the code protection is turned off during an erase.

- 3: The entire program memory will be erased when the code protection is turned off.

#### REGISTER 15-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x/u                                                                     | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u      |  |  |

|-----------------------------------------------------------------------------|---------|-------------------|---------|--------------|------------------|----------|--------------|--|--|

| —                                                                           | —       | —                 | _       | —            | _                | ADRE     | S<9:8>       |  |  |

| bit 7 bit 0                                                                 |         |                   |         |              |                  |          |              |  |  |

|                                                                             |         |                   |         |              |                  |          |              |  |  |

| Legend:                                                                     |         |                   |         |              |                  |          |              |  |  |

| R = Readable                                                                | bit     | W = Writable      | bit     | U = Unimpler | nented bit, read | l as '0' |              |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value a |         |                   |         |              |                  |          | other Resets |  |  |

| '1' = Bit is set                                                            |         | '0' = Bit is clea | ared    |              |                  |          |              |  |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

#### **REGISTER 15-6:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x/u | R/W-x/u    | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |  |

|---------|------------|---------|---------|---------|---------|---------|---------|--|--|--|

|         | ADRES<7:0> |         |         |         |         |         |         |  |  |  |

| bit 7   | bit 7 bit  |         |         |         |         |         |         |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result

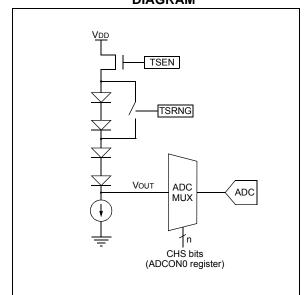

# 16.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

# 16.1 Circuit Operation

Figure 16-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 16-1 describes the output characteristics of the temperature indicator.

## EQUATION 16-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

#### FIGURE 16-1: TEMPERATURE CIRCUIT DIAGRAM

# 16.2 Minimum Operating VDD vs. Minimum Sensing Temperature

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 16-1 shows the recommended minimum VDD vs. range setting.

TABLE 16-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## 16.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 16.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

# 16.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

<sup>© 2008-2011</sup> Microchip Technology Inc.

# 22.5 Timer2/4/6 Control Register

#### REGISTER 22-1: TXCON: TIMER2/TIMER4/TIMER6 CONTROL REGISTER

| U-0            | R/W-0/0                    | R/W-0/0                                        | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|----------------|----------------------------|------------------------------------------------|-----------------|----------------|------------------|------------------|--------------|--|--|--|

|                |                            | TOUTP                                          | S<3:0>          |                | TMRxON           | TxCKP            | S<1:0>       |  |  |  |

| oit 7          |                            |                                                |                 |                |                  |                  | bit (        |  |  |  |

|                |                            |                                                |                 |                |                  |                  |              |  |  |  |

| _egend:        |                            |                                                |                 |                |                  |                  |              |  |  |  |

| R = Readab     | le bit                     | W = Writable                                   | bit             | U = Unimpler   | mented bit, read | l as '0'         |              |  |  |  |

| u = Bit is un  | changed                    | x = Bit is unkr                                | nown            | -n/n = Value   | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| 1' = Bit is se | et                         | '0' = Bit is clea                              | ared            |                |                  |                  |              |  |  |  |

| oit 7          | Unimpleme                  | ented: Read as '                               | 0'              |                |                  |                  |              |  |  |  |

| oit 6-3        | TOUTPS<3                   | :0>: Timer Outpu                               | ut Postscaler S | Select bits    |                  |                  |              |  |  |  |

|                | 0000 = 1:1                 |                                                |                 |                |                  |                  |              |  |  |  |

|                | 0001 = 1:2                 | 0001 = 1:2 Postscaler                          |                 |                |                  |                  |              |  |  |  |

|                |                            | 0010 = 1:3 Postscaler                          |                 |                |                  |                  |              |  |  |  |

|                |                            | 0011 = 1:4  Postscaler                         |                 |                |                  |                  |              |  |  |  |

|                |                            | 0100 = 1:5 Postscaler<br>0101 = 1:6 Postscaler |                 |                |                  |                  |              |  |  |  |

|                | 0101 = 1.6<br>0110 = 1.7   |                                                |                 |                |                  |                  |              |  |  |  |

|                | 0111 = <b>1</b> :8         |                                                |                 |                |                  |                  |              |  |  |  |

|                | 1000 = 1:9                 |                                                |                 |                |                  |                  |              |  |  |  |

|                | 1001 = 1:10                |                                                |                 |                |                  |                  |              |  |  |  |

|                | 1010 <b>= 1:11</b>         | Postscaler                                     |                 |                |                  |                  |              |  |  |  |

|                | 1011 <b>= 1:12</b>         |                                                |                 |                |                  |                  |              |  |  |  |

|                | 1100 = 1:13                |                                                |                 |                |                  |                  |              |  |  |  |

|                | 1101 = 1:14                |                                                |                 |                |                  |                  |              |  |  |  |

|                | 1110 = 1:15<br>1111 = 1:16 |                                                |                 |                |                  |                  |              |  |  |  |

| oit 2          |                            | imerx On bit                                   |                 |                |                  |                  |              |  |  |  |

|                | 1 = Timerx                 |                                                |                 |                |                  |                  |              |  |  |  |

|                | 0 = Timerx                 |                                                |                 |                |                  |                  |              |  |  |  |

| oit 1-0        | TxCKPS<1:                  | : <b>0&gt;:</b> Timer2-type                    | Clock Presca    | le Select bits |                  |                  |              |  |  |  |

|                | 00 = Presca                | ler is 1                                       |                 |                |                  |                  |              |  |  |  |

|                | 01 = Presca                |                                                |                 |                |                  |                  |              |  |  |  |

|                | 10 = Presca                |                                                |                 |                |                  |                  |              |  |  |  |

|                | 11 = Presca                | ler is 64                                      |                 |                |                  |                  |              |  |  |  |

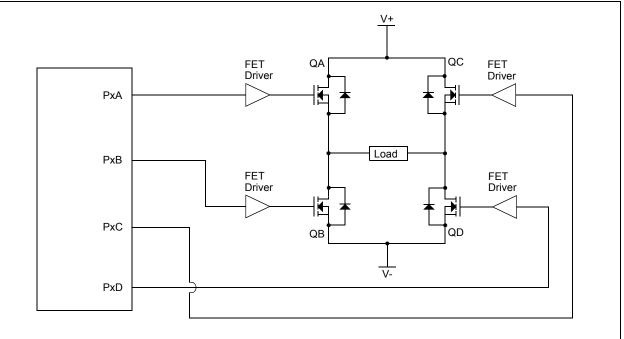

#### 23.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 23-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 23-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 23-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

#### FIGURE 23-10: EXAMPLE OF FULL-BRIDGE APPLICATION

### 24.2 SPI Mode Overview

The Serial Peripheral Interface (SPI) bus is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Slave Select (SS)

Figure 24-1 shows the block diagram of the MSSP module when operating in SPI Mode.

The SPI bus operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

Figure 24-4 shows a typical connection between a master device and multiple slave devices.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions involve two shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new Least Significant bit (LSb) is shifted into the same register.

Figure 24-5 shows a typical connection between two processors configured as master and slave devices.

Data is shifted out of both shift registers on the programmed clock edge and latched on the opposite edge of the clock.

The master device transmits information out on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information out on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

To begin communication, the master device first sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

The master device starts a transmission by sending out the MSb from its shift register. The slave device reads this bit from that same line and saves it into the LSb position of its shift register.

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its shift register (on

its SDO pin) and the slave device is reading this bit and saving it as the LSb of its shift register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its shift register.

After 8 bits have been shifted out, the master and slave have exchanged register values.

If there is more data to exchange, the shift registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data), depends on the application software. This leads to three scenarios for data transmission:

- Master sends useful data and slave sends dummy data.

- Master sends useful data and slave sends useful data.

- Master sends dummy data and slave sends useful data.

Transmissions may involve any number of clock cycles. When there is no more data to be transmitted, the master stops sending the clock signal and it deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line must disregard the clock and transmission signals and must not transmit out any data of its own.

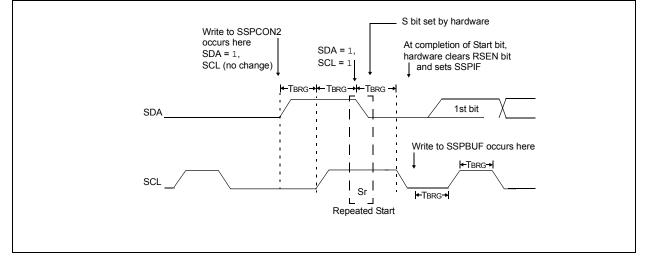

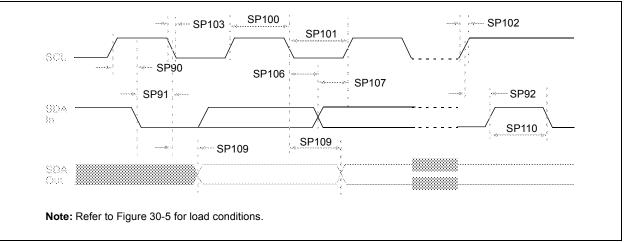

### 24.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit of the SSPCON2 register is programmed high and the Master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## 30.8 AC Characteristics: PIC16(L)F1934/6/7-I/E

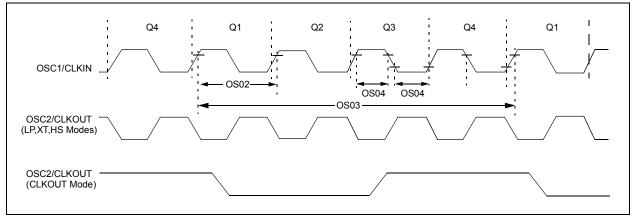

#### FIGURE 30-6: CLOCK TIMING

#### TABLE 30-1: CLOCK OSCILLATOR TIMING REQUIREMENTS

|              | <b>d Operati</b><br>g tempera | ng Conditions (unless otherwise ature $-40^{\circ}C \le TA \le +125^{\circ}C$ | e stated) |        |          |       |                                     |

|--------------|-------------------------------|-------------------------------------------------------------------------------|-----------|--------|----------|-------|-------------------------------------|

| Param<br>No. | Sym.                          | Characteristic                                                                | Min.      | Тур†   | Max.     | Units | Conditions                          |

| OS01         | Fosc                          | External CLKIN Frequency <sup>(1)</sup>                                       | DC        | _      | 0.5      | MHz   | EC Oscillator mode (low)            |

|              |                               |                                                                               | DC        | _      | 4        | MHz   | EC Oscillator mode (medium)         |

|              |                               |                                                                               | DC        | —      | 20       | MHz   | EC Oscillator mode (high)           |

|              |                               | Oscillator Frequency <sup>(1)</sup>                                           | —         | 32.768 | —        | kHz   | LP Oscillator mode                  |

|              |                               |                                                                               | 0.1       | —      | 4        | MHz   | XT Oscillator mode                  |

|              |                               |                                                                               | 1         | —      | 4        | MHz   | HS Oscillator mode                  |

|              |                               |                                                                               | 1         | _      | 20       | MHz   | HS Oscillator mode, VDD > 2.7V      |

|              |                               |                                                                               | DC        | _      | 4        | MHz   | RC Oscillator mode, VDD $\leq 2.0V$ |

| OS02         | Tosc                          | External CLKIN Period <sup>(1)</sup>                                          | 27        | _      | ×        | μs    | LP Oscillator mode                  |

|              |                               |                                                                               | 250       | —      | $\infty$ | ns    | XT Oscillator mode                  |

|              |                               |                                                                               | 50        | —      | $\infty$ | ns    | HS Oscillator mode                  |

|              |                               |                                                                               | 50        | —      | $\infty$ | ns    | EC Oscillator mode                  |

|              |                               | Oscillator Period <sup>(1)</sup>                                              | —         | 30.5   | —        | μs    | LP Oscillator mode                  |

|              |                               |                                                                               | 250       | —      | 10,000   | ns    | XT Oscillator mode                  |

|              |                               |                                                                               | 50        | —      | 1,000    | ns    | HS Oscillator mode                  |

|              |                               |                                                                               | 250       | —      | —        | ns    | RC Oscillator mode                  |

| OS03         | TCY                           | Instruction Cycle Time <sup>(1)</sup>                                         | 200       | TCY    | DC       | ns    | TCY = 4/FOSC                        |

| OS04*        | TosH,                         | External CLKIN High,                                                          | 2         |        | —        | μs    | LP oscillator                       |

|              | TosL                          | External CLKIN Low                                                            | 100       | -      | —        | ns    | XT oscillator                       |

|              |                               |                                                                               | 20        | -      | —        | ns    | HS oscillator                       |

| OS05*        | TosR,                         | External CLKIN Rise,                                                          | 0         |        | $\infty$ | ns    | LP oscillator                       |

|              | TosF                          | External CLKIN Fall                                                           | 0         | —      | $\infty$ | ns    | XT oscillator                       |

|              |                               |                                                                               | 0         | —      | $\infty$ | ns    | HS oscillator                       |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

| Param<br>No. | Symbol                | Characteristic                                               |                                  | Min.     | Тур† | Max. | Units | Conditions |

|--------------|-----------------------|--------------------------------------------------------------|----------------------------------|----------|------|------|-------|------------|

| SP70*        | TssL2scH,<br>TssL2scL | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input                      |                                  | Тсү      |      | —    | ns    |            |

| SP71*        | TscH                  | SCK input high time (Slave mode                              | Tcy + 20                         |          | —    | ns   |       |            |

| SP72*        | TscL                  | SCK input low time (Slave mode                               | )                                | Tcy + 20 | _    | _    | ns    |            |

| SP73*        | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to S                            | 100                              |          | —    | ns   |       |            |

| SP74*        | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SO                            | 100                              |          | —    | ns   |       |            |

| SP75*        | TDOR                  | SDO data output rise time                                    | 3.0-5.5V                         | —        | 10   | 25   | ns    |            |

|              |                       |                                                              | 1.8-5.5V                         | _        | 25   | 50   | ns    |            |

| SP76*        | TDOF                  | SDO data output fall time                                    |                                  | —        | 10   | 25   | ns    |            |

| SP77*        | TssH2doZ              | SS↑ to SDO output high-impeda                                | nce                              | 10       | _    | 50   | ns    |            |

| SP78*        | TscR                  | SCK output rise time                                         | 3.0-5.5V                         | —        | 10   | 25   | ns    |            |

|              |                       | (Master mode)                                                | 1.8-5.5V                         | _        | 25   | 50   | ns    |            |

| SP79*        | TscF                  | SCK output fall time (Master mo                              | de)                              | _        | 10   | 25   | ns    |            |

| SP80*        | TscH2doV,             | SDO data output valid after                                  | 3.0-5.5V                         | _        |      | 50   | ns    |            |

|              | TscL2doV              | SCK edge                                                     | 1.8-5.5V                         | —        | _    | 145  | ns    |            |

| SP81*        | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK e                               | DO data output setup to SCK edge |          | _    | —    | ns    |            |

| SP82*        | TssL2doV              | SDO data output valid after $\overline{\text{SS}}\downarrow$ | _                                |          | 50   | ns   |       |            |

| SP83*        | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                          | 1.5Tcy + 40                      |          | -    | ns   |       |            |

#### TABLE 30-14: SPI MODE REQUIREMENTS

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

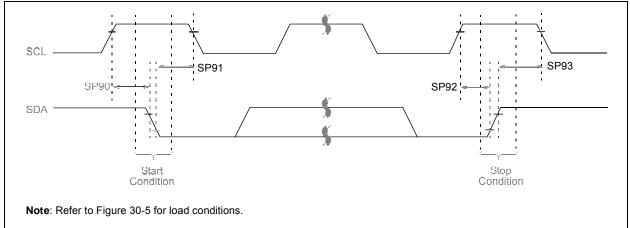

#### **FIGURE 30-20:** I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS TIMING

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                   |  |

|--------------|---------|-----------------|--------------|------|-----|------|-------|------------------------------|--|

| SP90*        | TSU:STA | Start condition | 100 kHz mode | 4700 |     |      | ns    | Only relevant for Repeated   |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | —    |       | Start condition              |  |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 | _   | —    | ns    | After this period, the first |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   | _    |       | clock pulse is generated     |  |

| SP92*        | Tsu:sto | Stop condition  | 100 kHz mode | 4700 | _   |      | ns    |                              |  |

|              |         | Setup time      | 400 kHz mode | 600  | _   | _    |       |                              |  |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 | _   | _    | ns    |                              |  |

|              |         | Hold time       | 400 kHz mode | 600  | _   |      |       |                              |  |

# TABLE 30-15: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

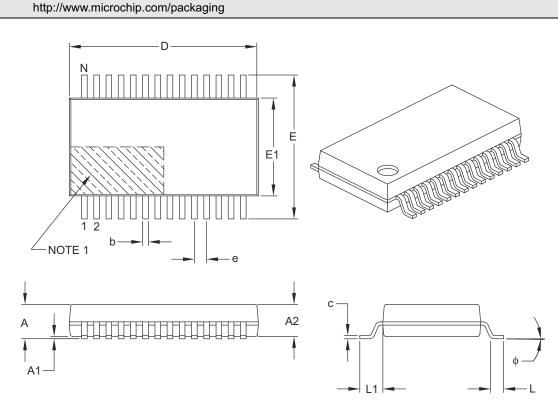

For the most current package drawings, please see the Microchip Packaging Specification located at

### 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | MILLIMETERS |          |          |       |  |

|--------------------------|-------------|----------|----------|-------|--|

| Dimension Limits         |             | MIN      | NOM      | MAX   |  |

| Number of Pins           | N           |          |          |       |  |

| Pitch                    | e           |          | 0.65 BSC |       |  |

| Overall Height           | А           | -        | -        | 2.00  |  |

| Molded Package Thickness |             | 1.65     | 1.75     | 1.85  |  |

| Standoff                 | A1          | 0.05     | -        | -     |  |

| Overall Width            | E           | 7.40     | 7.80     | 8.20  |  |

| Molded Package Width     | E1          | 5.00     | 5.30     | 5.60  |  |

| Overall Length           | D           | 9.90     | 10.20    | 10.50 |  |

| Foot Length              | L           | 0.55     | 0.75     | 0.95  |  |

| Footprint                | L1          | 1.25 REF |          |       |  |

| Lead Thickness           |             | 0.09     | -        | 0.25  |  |

| Foot Angle               |             | 0°       | 4°       | 8°    |  |

| Lead Width               | b           | 0.22     | -        | 0.38  |  |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

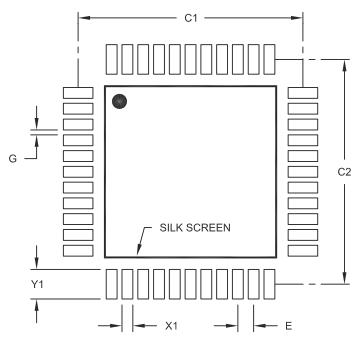

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

**RECOMMENDED LAND PATTERN**

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimension Limits         |             | MIN      | NOM   | MAX  |

| Contact Pitch            | E           | 0.80 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 11.40 |      |

| Contact Pad Spacing      | C2          |          | 11.40 |      |

| Contact Pad Width (X44)  | X1          |          |       | 0.55 |

| Contact Pad Length (X44) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.25     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076A